**Enabling Energy Efficient Solutions**

www.onsemi.com

#### **ON Semiconductor**<sup>®</sup>

# **Compensating a PFC Stage**

# Agenda

- Introduction

- Deriving a small-signal model

- General method

- Practical example: NCP1605-driven PFC stages

- Compensating the loop

- Type-2 compensation

- Influence of the line and power level

- Computing the compensation

- Practical example

- Conclusion

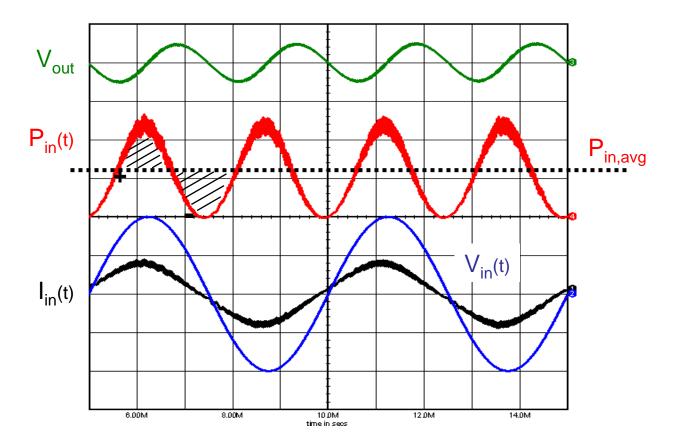

#### **Output Voltage Low Frequency Ripple**

The load power demand is matched in average only

A low frequency ripple is inherent to the PFC function

#### **PFC Stages are Slow Systems...**

□ The output ripple must be filtered to avoid current distortion.

□ In practice, the loop frequency is selected in the range of 20 Hz, which is very low.

Even if the bandwidth is low, the loop must be compensated!

# Agenda

- Introduction

- Deriving a small-signal model

- General method

- Practical example: NCP1605-driven PFC stages

- Compensating the loop

- Type-2 compensation

- Influence of the line and power level

- Computing the compensation

- Practical example

- Conclusion

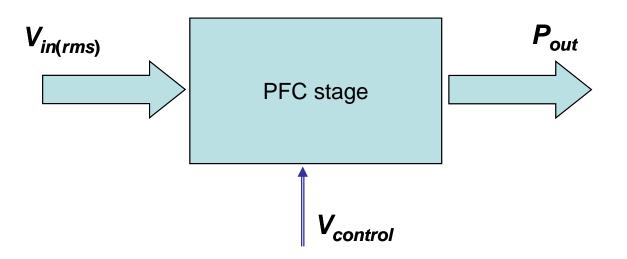

## **A Simple Representation**

• We will consider the PFC stage as a system delivering a power under an input rms voltage and a control signal

- Details of the power processing are ignored:

- Operation mode (CrM, CCM, Voltage or Current mode...)

- 100% efficiency, only the average power contribution of the sinusoidal signals is considered

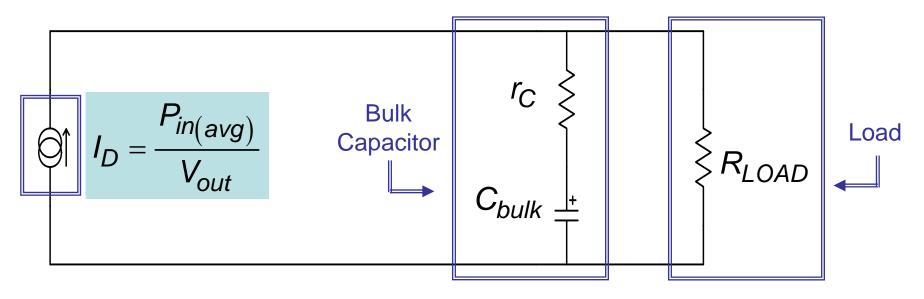

# A Simple Large Signal Model

• Let's represent the PFC stage as a current source delivering the power to the bulk capacitor and the load:

- $P_{in(avg)}$  depends on  $V_{control}$  (always), on  $V_{in(rms)}$  (in the absence of feedforward) and sometimes on  $V_{out}$

- 3 possible sources of perturbations:  $V_{control}$ ,  $V_{out}$  and  $V_{in(rms)}$ .

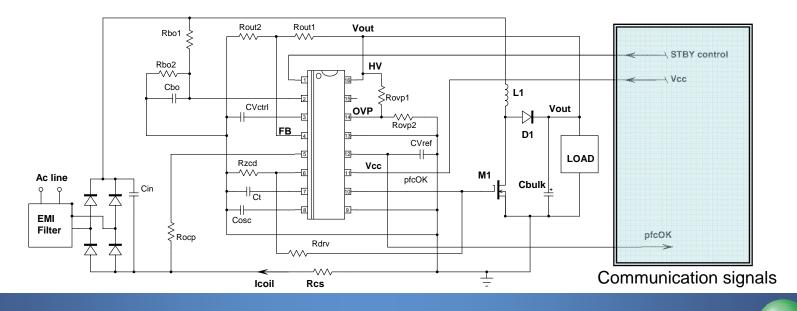

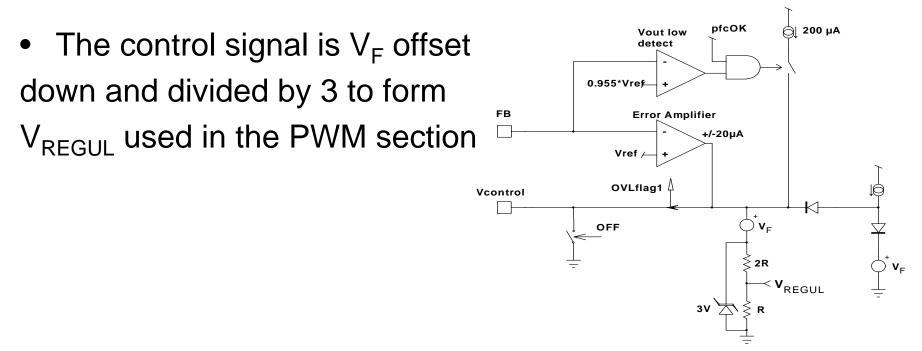

## NCP1605

- Frequency Clamped Critical Conduction Mode (FCCrM)

- Key features for a master PFC:

- High voltage current source, Soft-Skip<sup>™</sup> during standby mode

- "pfcOK" signal, dynamic response enhancer

- Bunch of protections for rugged PFC stages

- Markets: high power AC adapters, LCD TVs

**ON Semiconductor**<sup>\*</sup>

#### NCP1605 – Follower Boost

- Voltage mode operation: the circuit adjusts the power level by modulating the MOSFET conduction time

- The charge current of the timing capacitor is proportional to the FB square and hence to (V<sub>out</sub>)<sup>2</sup>:

$$I_{charge} = I_t \cdot \left(\frac{V_{out}}{V_{out,nom}}\right)^2$$

where :

- *V<sub>out,nom</sub>* is the V<sub>out</sub> regulation voltage

- $I_t$  is a 370-µA current source

- The on-time is inversely proportional to  $(V_{out})^2$  allowing the Follower boost function:

$$t_{on} = \frac{C_t \cdot V_{ton}}{I_t} \cdot \left(\frac{V_{out,nom}}{V_{out}}\right)^2$$

#### **NCP1605 - Power Expression**

Hence due to the follower boost function, the power is inversely dependent on (V<sub>out</sub>)<sup>2</sup>:

$$P_{in(avg)} = \frac{C_t \cdot V_{in(rms)}^2}{2 \cdot L \cdot I_t} \cdot \left(\frac{V_{out,nom}}{V_{out}}\right)^2 \cdot \frac{(V_{control} - V_F)}{3}$$

ON Semiconductor\*

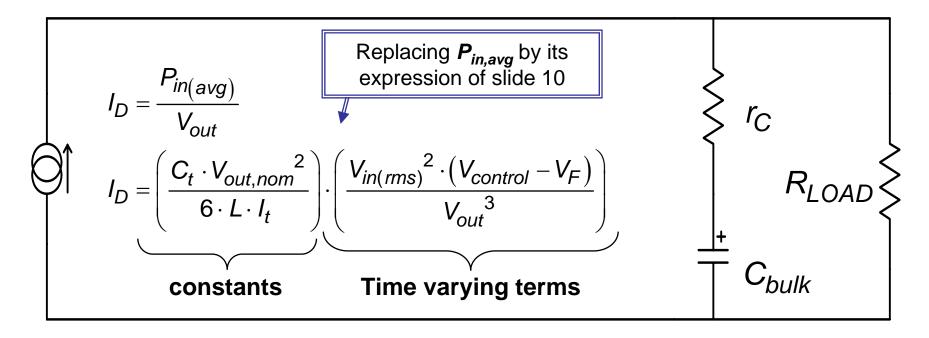

## NCP1605 - Large Signal Model

• Let's represent the PFC stage as a current source delivering the power to the bulk capacitor and the load:

• 3 sources of perturbations:  $V_{CONTROL}$ ,  $V_{out}$  and  $V_{in(rms)}$ .

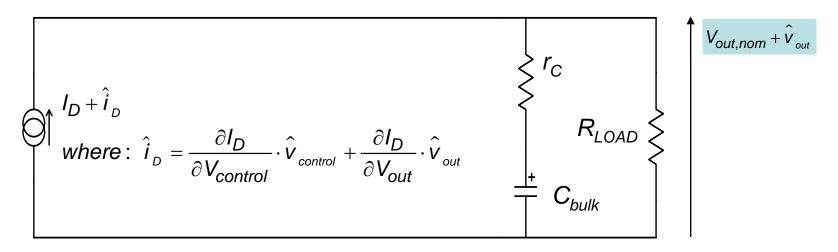

## **Small Signal Model**

- A large signal model is nonlinear because  $I_D$  is formed of the multiplication and division of  $V_{control}$ ,  $V_{in.rms}$  and  $V_{out}$ .

- This model needs to be linearized to assess the AC contribution of each variable

- The model is perturbed and linearized around a quiescient operating point (DC point)

### **Considering Variations Around the DC Value...**

- Let's omit the perturbations of the line magnitude (assumed constant)

- Let's consider small variations around the DC values for  $V_{out}$  and  $V_{control}$ :  $\hat{i}_{D} = \frac{\partial I_{D}}{\partial V_{control}} \cdot \hat{v}_{control} + \frac{\partial I_{D}}{\partial V_{out}} \cdot \hat{v}_{out}$

- We then obtain:

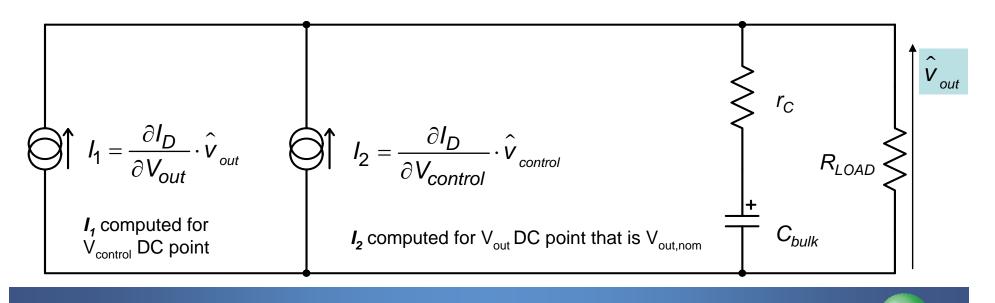

## **Deriving a Small Signal Model...**

- The DC portion can be eliminated

- The partial derivatives are to be computed at the DC point that is for:

- $-V_{control}$  that is the control signal DC value for the considered working point

- $-V_{out,nom}$  that is the nominal (DC) output voltage

- Replacing the derivations by their expression, we obtain:

**ON Semiconductor**<sup>\*</sup>

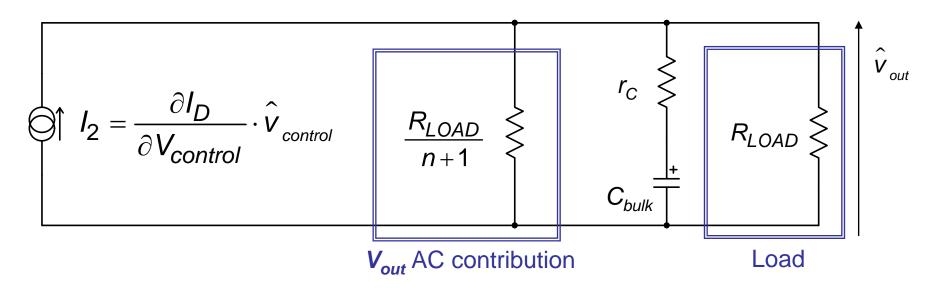

## **Contribution of the** *V<sub>out</sub>* **Perturbations**

• Depending on the controller scheme

$$I_{D} = \frac{P_{in,avg}}{V_{out}} = \frac{f(V_{in(rms)}, V_{control})}{(V_{out})^{n+1}} \quad \text{where } n = 0,1 \text{ or } 2$$

- n=0 for NCP1607

- n=1 for NCP1654 (predictive CCM PFC for which  $P_{in,avg} \propto \frac{V_{control} \cdot V_{in,rms}}{V_{out}}$ )

- n=2 for NCP1605 (follower boost see slide 10)

- At the DC point

$$V_{out} = V_{out,nom}$$

and  $\frac{P_{in(avg)}}{(V_{out,nom})^2} = \frac{1}{R_{LOAD}}$

• Finally:

$$I_{1} = \frac{\partial I_{D}}{\partial V_{out}} \cdot \hat{v}_{out} = -\frac{\left(n+1\right) \cdot f\left(V_{in(rms)}, V_{control}\right)}{\left(V_{out}\right)^{n+2}} \bigg|_{V_{out} = V_{out,nom}} \cdot \hat{v}_{out} = -\frac{\left(n+1\right) \cdot P_{in(avg)}}{\left(V_{out,nom}\right)^{2}} \cdot \hat{v}_{out} = -\frac{\left(n+1\right)}{R_{LOAD}} \cdot \hat{v}_{out}$$

### 2 Resistors...

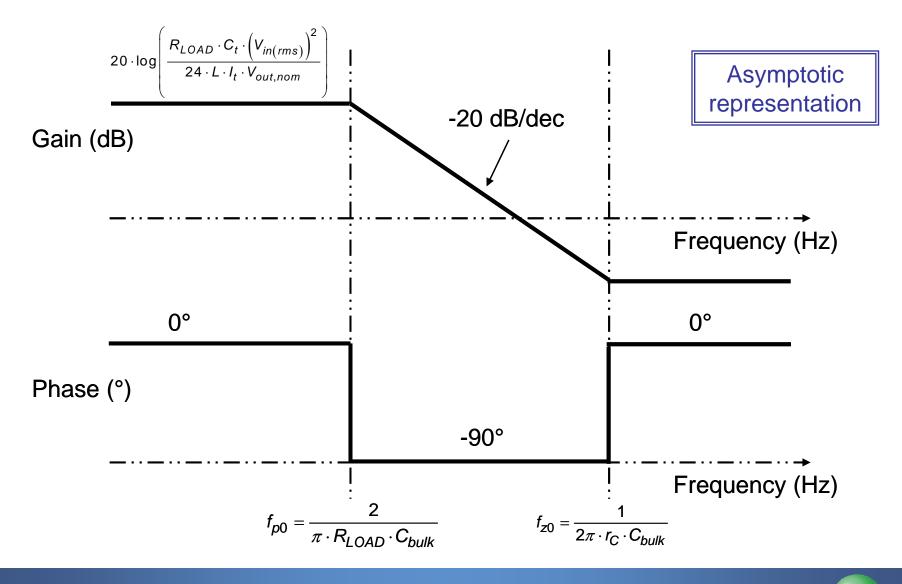

• Hence, the small signal model can be simplified as follows:

• Noting that:  $\frac{R_{LOAD}}{n+1} \square R_{LOAD} = \frac{R_{LOAD}}{n+2}$

the model can be further simplified

ON Semiconductor\*

## Finally...

□ The transfer function is:

$$\frac{\hat{v}_{out}}{\hat{v}_{control}} = \frac{R_{LOAD}}{n+2} \cdot \left(\frac{\partial I_D}{\partial V_{control}}\right) \cdot \frac{1 + s \cdot r_C \cdot C_{bulk}}{1 + s \left(\frac{R_{LOAD} \cdot C_{bulk}}{n+2}\right)}$$

## NCP1605 Example

• The large signal model instructed that:

•

$$I_{D} = \frac{P_{in(avg)}}{V_{out}} = \left(\frac{C_{t} \cdot V_{out,nom}^{2}}{6 \cdot L \cdot I_{t}}\right) \cdot \left(\frac{V_{in(rms)}^{2} \cdot (V_{control} - V_{F})}{V_{out}^{3}}\right)$$

Hence:

$$n = 2$$

$$\frac{\partial I_{D}}{\partial V_{control}} = \frac{C_{t} \cdot \left(V_{in(rms)}\right)^{2}}{6 \cdot L \cdot I_{t} \cdot V_{out,nom}}$$

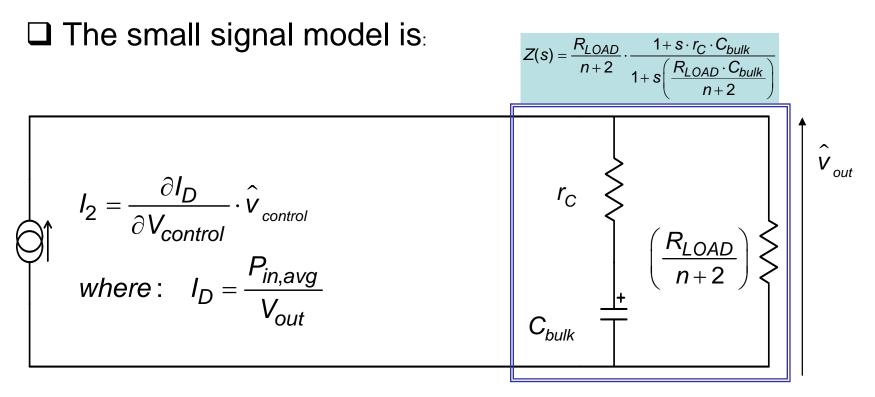

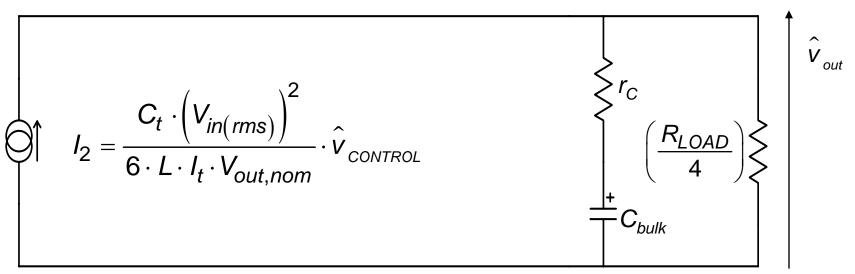

### NCP1605 - Small Signal Model

• Finally:

• The transfer function is:

$$\frac{\hat{v}_{out}}{\hat{v}_{CONTROL}} = \frac{R_{LOAD} \cdot C_t \cdot \left(V_{in(rms)}\right)^2}{24 \cdot L \cdot I_t \cdot V_{out,nom}} \cdot \frac{1 + s \cdot r_C \cdot C_{bulk}}{1 + s \cdot \left(\frac{R_{LOAD} \cdot C_{bulk}}{4}\right)}$$

#### **Power Stage Characteristic – Bode Plots**

**ON**

# Agenda

- Introduction

- Deriving a small-signal model

- General method

- Practical example: NCP1605-driven PFC stages

- Compensating the loop

- Type-2 compensation

- Influence of the line and power level

- Computing the compensation

- Practical example

- Conclusion

## **Compensation Phase Boost**

- The zero brought by the bulk capacitor ESR is too high to bring some phase margin. It is ignored.

- The PFC open loop inherently causes a -360° phase shift:

| <ul> <li>Power stage pole</li> </ul>          | → -90°  |

|-----------------------------------------------|---------|

| <ul> <li>Error amplifier inversion</li> </ul> | → -180° |

| <ul> <li>Compensation origin pole</li> </ul>  | → -90°  |

- The compensation must then provide some phase boost

- A type-2 compensation is recommended

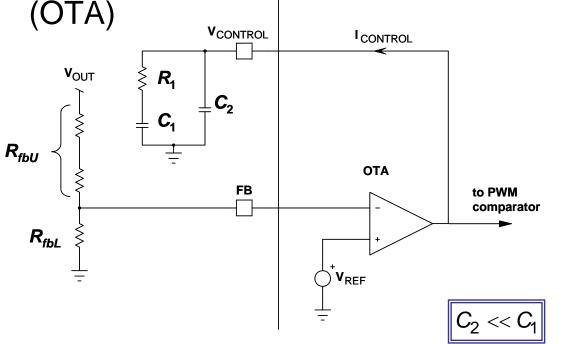

## **Type-2 Compensation**

• The NCP1605 embeds a transconductance error amplifier

- No direct influence of the

- $R_{fbU}$  impedance on the compensation

- Only the feedback scale factor interferes

$f_{Z1} = \frac{1}{2\pi \cdot R_1 \cdot C_1}$   $f_{p2} = \frac{1}{2\pi \cdot R_1 \cdot C_2}$   $f_{p1} = \frac{1}{2\pi \cdot R_0 \cdot C_1}$  pole at the origin  $R_0 = \frac{V_{out,nom}}{V_{ref} \cdot G_{EA}}$

V<sub>ref</sub> is the reference voltage (generally 2.5 V in ON semi devices)

G<sub>EA</sub> is the OTA

(200-µS transconductance gain for NCP1605, NCP1654 and NCP1631)

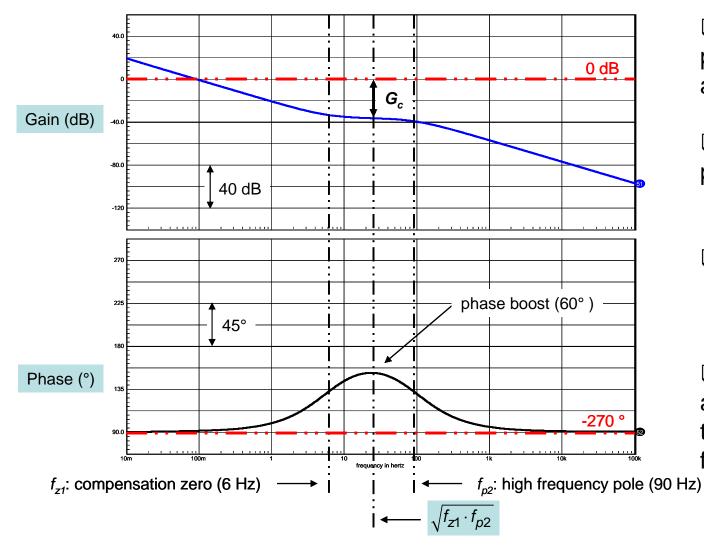

#### **Type-2 Characteristic - Example**

$\Box$   $f_{p2}$  and  $f_{z1}$  set the phase boost magnitude and location (frequency)

□ The phase boost peaks at:  $(f_{PhB} = \sqrt{f_{z1} \cdot f_{p2}})$ that is 27 Hz

The phase boost is:  $f(f_{phB}) = f(f_{phB})$

$\tan^{-1}\left(\frac{f_{phB}}{f_z}\right) - \tan^{-1}\left(\frac{f_{phB}}{f_p}\right)$

□ The origin pole  $f_{p1}$ adjusts the gain  $G_c$  at the phase boost frequency

ΠN

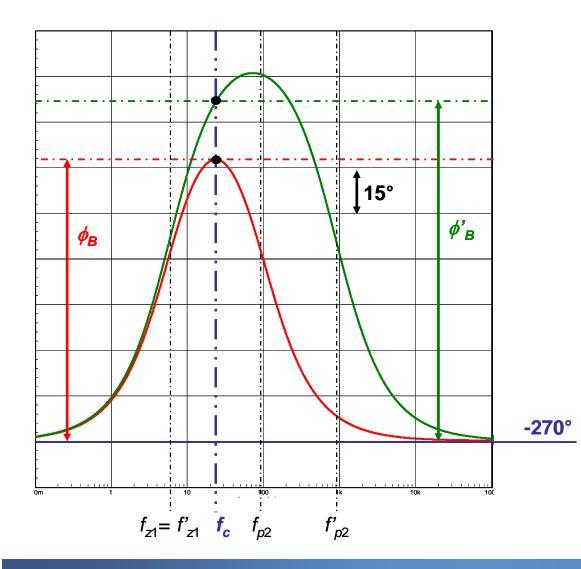

#### Phase Boost at the Crossover Frequency

$$\phi_{B} = \tan^{-1} \left( \frac{f_{c}}{f_{z1}} \right) - \tan^{-1} \left( \frac{f_{c}}{f_{p2}} \right)$$

□ The lower  $f_{z1}$  and/or the higher  $f_{p2}$ , the higher the phase boost (max. value: 90°)

□ Assuming the PFC power stage pole is well below the crossover frequency ( $f_c$ ), the phase boost equates the phase margin ( $\phi_m = \phi_B$ )

□ Target a phase boost between 45° and 75°

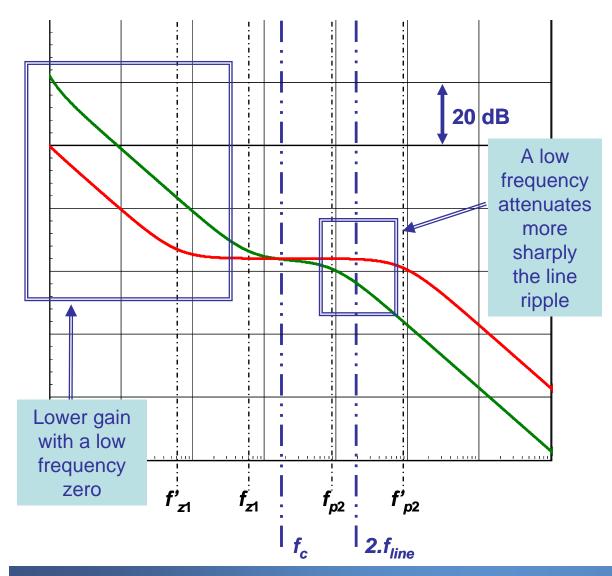

## **Gain Considerations**

- In the red trace, the distance between the zero and the pole frequencies is increased

- Both characteristics generate the same attenuation at the crossover frequency

- The lower the *f<sub>z1</sub>* frequency, the lower the gain in the low frequency region

- The higher *f<sub>p2</sub>*, the lower the (2.*f<sub>line</sub>*) ripple rejection

## **Type-2 Compensator - Summary**

- The zero should not be placed at a too low frequency (not to penalize the low-frequency gain)

- The high frequency pole must be placed at a frequency low enough to attenuate the line ripple

- The phase boost (and phase margin) depends on the zero and high-frequency pole locations

- The origin pole is set to force the open loop gain to zero at the targeted crossover frequency

# Agenda

- Introduction

- Deriving a small-signal model

- General method

- Practical example: NCP1605-driven PFC stages

- Compensating the loop

- Type-2 compensation

- Influence of the line and power level

- Computing the compensation

- Practical example

- Conclusion

## **Compensating for the Full Range?...**

• The static gain depends on the load and if there is no feedforward, on the line magnitude

$$G_{static(dB)} = 20 \cdot \log\left(\frac{R_{LOAD}}{n+2} \cdot \left(\frac{\partial I_D}{\partial V_{control}}\right)\right) = 20 \cdot \log\left(\frac{R_{LOAD} \cdot C_t \cdot \left(V_{in(rms)}\right)^2}{24 \cdot L \cdot I_t \cdot V_{out,nom}}\right)$$

(NCP1605)

• The power stage pole varies as a function of the load:

$$f_{p0} = \frac{n+2}{2\pi \cdot R_{LOAD} \cdot C_{bulk}} = \frac{2}{\pi \cdot R_{LOAD} \cdot C_{bulk}}$$

(NCP1605)

• What is the worst case when closing the loop?

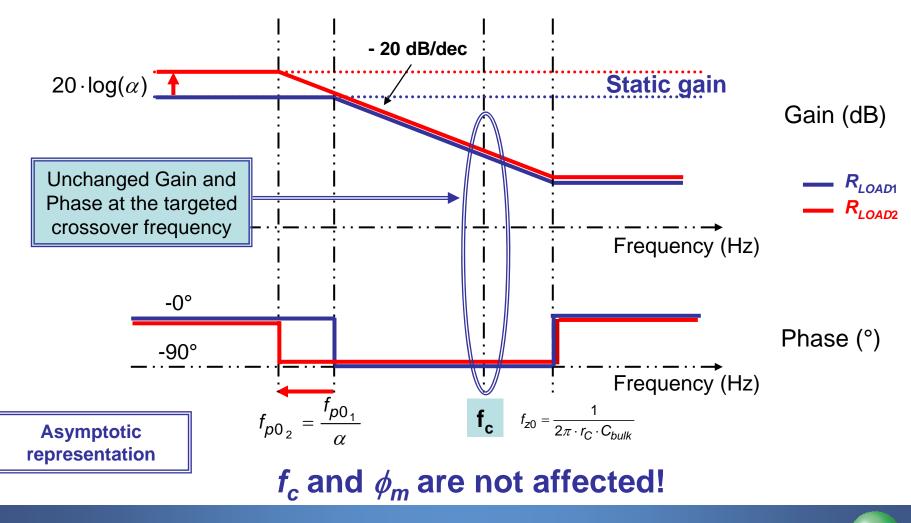

#### Load Influence on the Open Loop Plots

• Let's increase  $R_{LOAD}$   $(R_{LOAD2} = \alpha \cdot R_{LOAD1}$  with  $\alpha > 1)$

**ON Semiconductor\***

ΠN

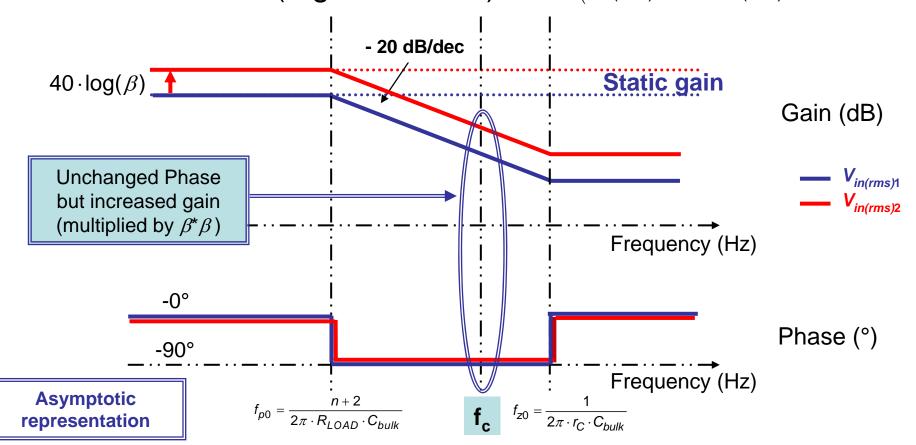

#### Line Influence on the Open Loop Plots

• No feedforward (e.g. NCP1607) and  $(V_{in(rms)2} = \beta \cdot V_{in(rms)1}$  with  $\beta > 1)$

#### The loop crossover frequency is $\beta^2$ increased

**ON Semiconductor\***

## Load and Line Considerations

- Compensate at full load

- Same crossover frequency at lighter loads

- The zero frequency is set optimally (not at a too low frequency)

- Compensate at high line

- High line is the worst case as in the absence of feedforward, the static gain is proportional to  $(v_{in(rms)})^2$

- This leads to:

$$(f_{c})_{HL} = \left(\frac{\left(V_{in(rms)}\right)_{HL}}{\left(V_{in(rms)}\right)_{LL}}\right)^{2} \cdot (f_{c})_{LL}$$

Where HL stands for Highest Line and LL for Lowest Line

- In universal mains applications, the high-line crossover frequency is 9 times higher than the low-line one:  $(265)^2$

$$(f_c)_{HL} = \left(\frac{265}{90}\right)^2 \cdot (f_c)_{LL} \cong 9 \cdot (f_c)_{LL}$$

### **Crossover Frequency Selection**

- In the absence of feedforward,  $(f_c)_{HL} \leq f_{line}$  is a good option

- With feedforward,  $(f_c)_{HL} \leq \frac{f_{line}}{2}$  is rather selected for a better attenuation of the low frequency ripple

- Get sure that on the line range, the PFC boost pole remains lower than the crossover frequency at full load!

$$f_{p0} \leq \left(f_c\right)_{LL}$$

• If not, increase C<sub>bulk</sub>

# Agenda

- Introduction

- Deriving a small-signal model

- General method

- Practical example: NCP1605-driven PFC stages

#### Compensating the loop

- Type-2 compensation

- Influence of the line and power level

- Computing the compensation

- Practical example

- Conclusion

## **Compensation Techniques**

- Several techniques exist:

- manual placement, "k factor" (Venable)...

- + Systematic

- The PFC boost gain is to be computed at  $f_c$

- No flexibility in the zero and high pole locations  $f_c = k \cdot f_{z1} = \frac{t_{p2}}{k}$

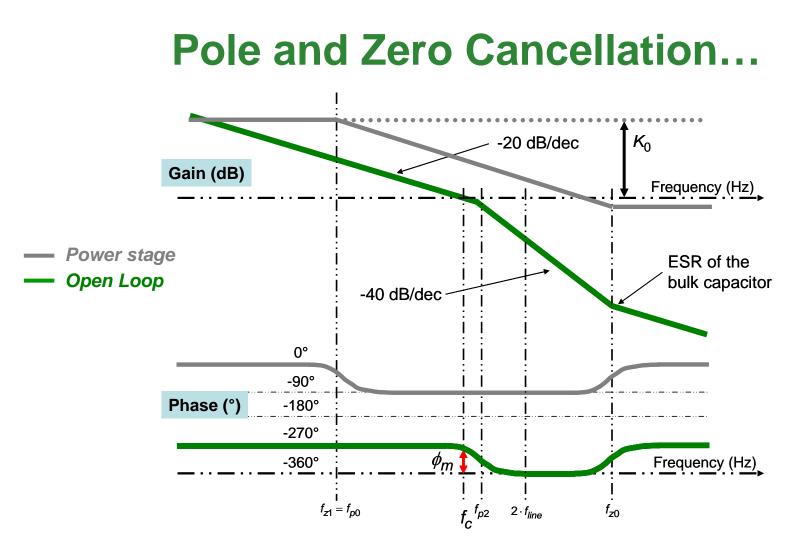

- Pole and zero cancellation:

$\checkmark$  Place the compensation zero so that it cancels the power stage pole:

✓ Force the pole at the origin to cancel the PFC boost gain when  $(f = f_c)$

$\checkmark$  Adjust the phase margin with the high frequency pole

□ The higher  $f_{p2}$ , the larger the phase margin □ The lower  $f_{p2}$ , the better the rejection of the low frequency ripple □  $\phi_m = 45^\circ$  if  $f_{p2} = f_c$ .

**ON Semiconductor\***

**ON**

### **Poles and Zero Placement**

- Design the compensation for full load, high line: RLOAD = RLOAD(min)

- Place the origin pole to cancel  $K_0$ , the static gain at  $f_c$ :

$$f_{p0} = \frac{f_c}{K_0} \quad \text{for} \quad R_{LOAD} = R_{LOAD(\min)}$$

where:  $\frac{\hat{v}_{out}}{\hat{v}_{CONTROL}} = K_0 \cdot \frac{1 + s \cdot r_C \cdot C_{bulk}}{1 + s \cdot \left(\frac{R_{LOAD(\min)} \cdot C_{bulk}}{n + 2}\right)}$

- Place the zero so that it cancels the PFC boost pole  $(f_{z1} = f_{p0})$  for  $R_{LOAD} = R_{LOAD(min)}$

- Place  $f_{p2}$  to obtain the targeted phase margin:  $f_{p2} = \frac{f_c}{\tan(90^\circ \phi_m)}$

## Example

- A wide mains, 150-W application driven by the NCP1605

- $V_{out,nom} = 390 \text{ V}$

- $(V_{in(rms)})_{LL} = 90 V$

- $(V_{in(rms)})_{HL} = 265 \text{ V}$

- *L* = 150 μH

- $C_t = 4.7 \text{ nF}$

- $C_{bulk} = 100 \,\mu\text{F}$

- $r_{\rm C} = 500 \text{ m}\Omega \text{ (ESR)}$

- $f_c = 50 \text{ Hz}$ and  $\Phi_m = 60^\circ$ @ high line (265 V)

$$\begin{aligned} \frac{\hat{v}_{out}}{\hat{v}_{COMTROL}} &= K_0 \cdot \frac{1 + s \cdot t_C \cdot C_{bulk}}{1 + s \cdot \left(\frac{R_{LOAD} \cdot C_{bulk}}{4}\right)} \quad \text{where} : \quad K_0 = \frac{R_{LOAD} \cdot C_l \cdot \left(V_{ln(rms)}\right)^2}{24 \cdot L \cdot l_l \cdot V_{out,nom}} \\ R_{LOAD(\min)} &= \frac{\left(\frac{V_{out,nom}}{P_{out}\right)_{\max}}\right)^2}{\left(\frac{R_{OAD}}{P_{out}\right)_{\max}}} = \frac{390^2}{150} \equiv 1 \ k\Omega \\ R_0 &= \frac{V_{out,nom}}{V_{ref} \cdot G_{EA}} = \frac{390}{2.5 \cdot 200 \cdot 10^{-6}} = 780 \ k\Omega \quad (OTA) \\ C_1 &= \frac{K_{0(\min)}}{2\pi \cdot t_c \cdot R_0} = \frac{R_{LOAD(\min)} \cdot C_l \cdot \left(V_{in(rms)}\right)_{HL}}{2\pi \cdot t_c \cdot R_0 \cdot 24 \cdot L \cdot l_l \cdot V_{out,nom}}} = \frac{10^3 \cdot 4.7 \cdot 10^{-9} \cdot 265^2}{2\pi \cdot 50 \cdot 780k \cdot 24 \cdot 150\mu \cdot 370\mu \cdot 390} \equiv 2.59\mu F \implies 2.2 \ \mu F \\ R_1 &= \frac{R_{LOAD(\min)} \cdot C_{bulk}}{(n+2) \cdot C_1} = \frac{10^3 \cdot 100 \cdot 10^{-6}}{(2+2) \cdot 2.2 \cdot 10^{-6}} \equiv 11.36 \ k\Omega \implies 12 \ k\Omega \\ C_2 &= \frac{\tan(90^\circ - \phi_m)}{2\pi \cdot t_c \cdot R_1} = \frac{\tan(90^\circ - 60^\circ)}{2\pi \cdot 50 \cdot 12 \cdot 10^3} \equiv 153 \ nF \implies 150 \ nF \\ f_{p1} &= \frac{1}{2\pi \cdot R_0 \cdot C_1} = 93 \ mHz \qquad f_{z1} = \frac{1}{2\pi \cdot R_1 \cdot C_1} = 6 \ Hz \qquad f_{z1} = \frac{1}{2\pi \cdot R_1 \cdot C_2} = 88 \ Hz \end{aligned}$$

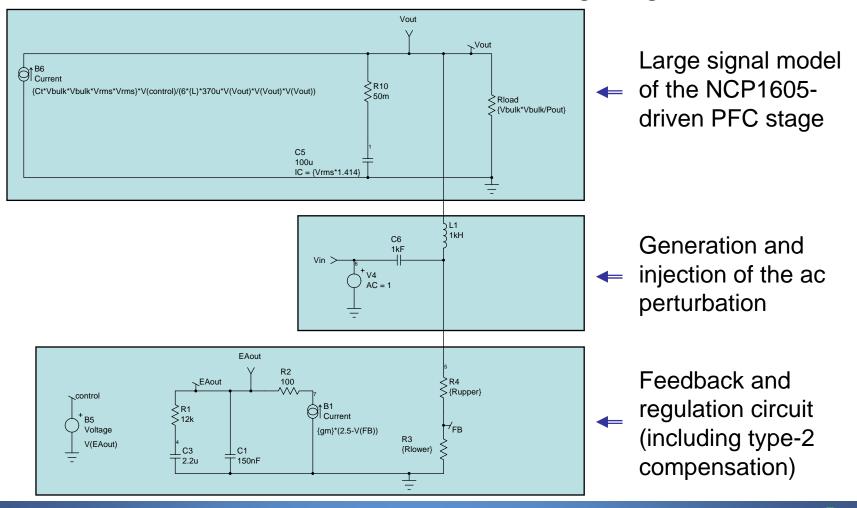

### **Simulation Validation**

• The simulation circuit is based on the large signal model:

ÛN

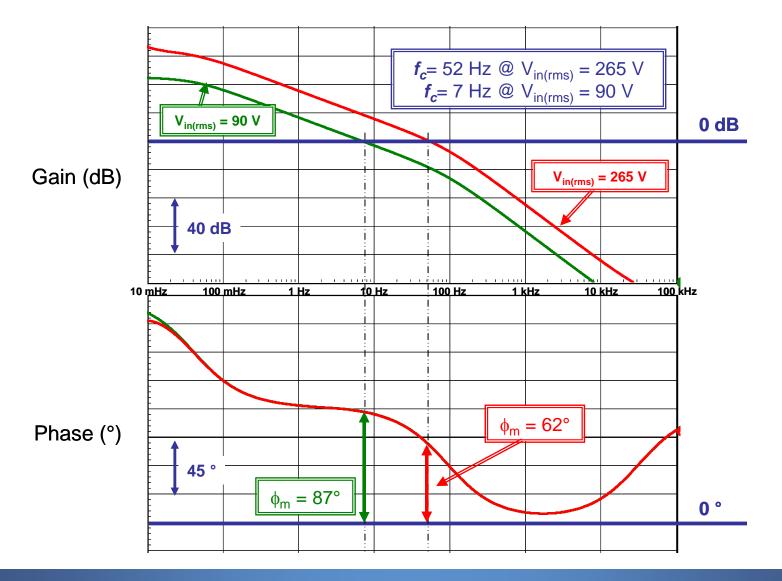

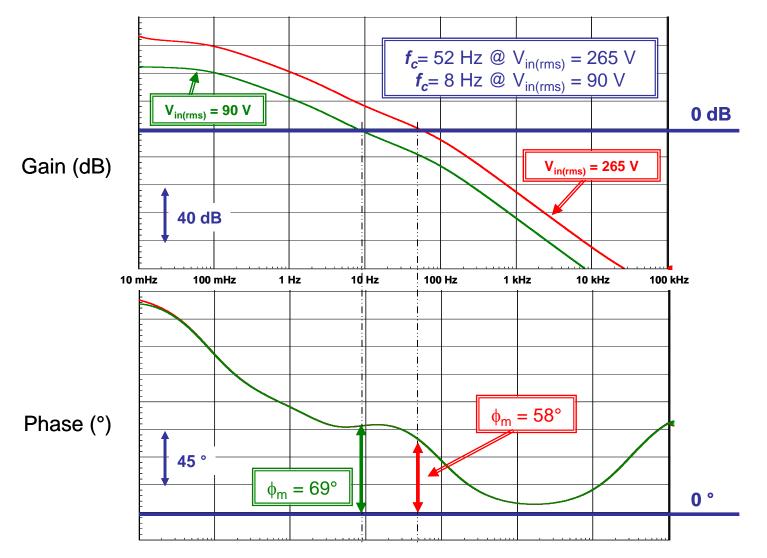

#### **Open Loop Characteristic – Full Load**

ON Semiconductor\*

#### **Open Loop Characteristic – Mid Load**

**ON Semiconductor\***

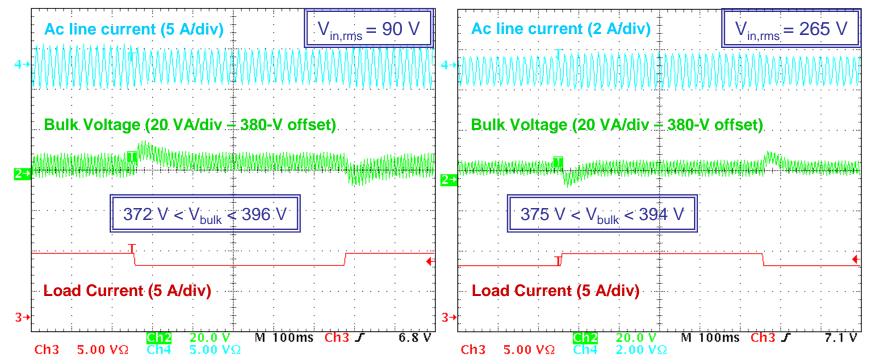

## **Experimental Results at Full Load**

- A 19 V / 7 A loads the PFC stage

- The downstream converter swings between 6.3 A and 7.7 A (+/-10%) with a 2 A/µs slope

The high-line, larger bandwidth reduces the V<sub>bulk</sub> deviations and speedsup the output voltage recovery

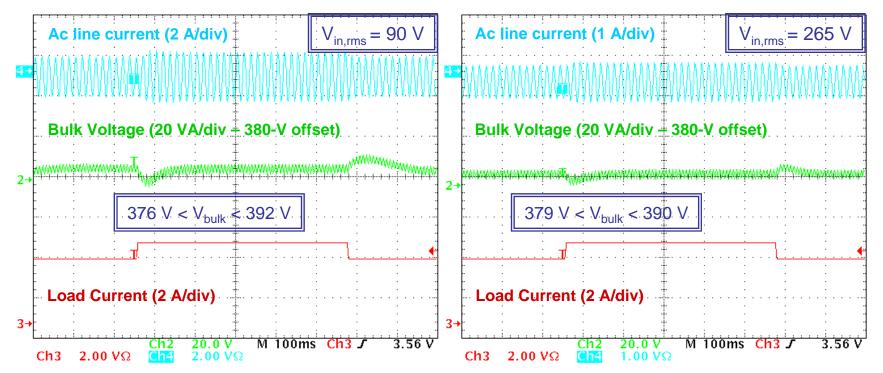

#### **Experimental Results at Medium Load**

- A 19 V / 7 A loads the PFC stage

- The downstream converter swings between 3.1 A and 3.9 A (+/-10%) with a 2 A/µs slope

• The circuit still exhibits a first order response

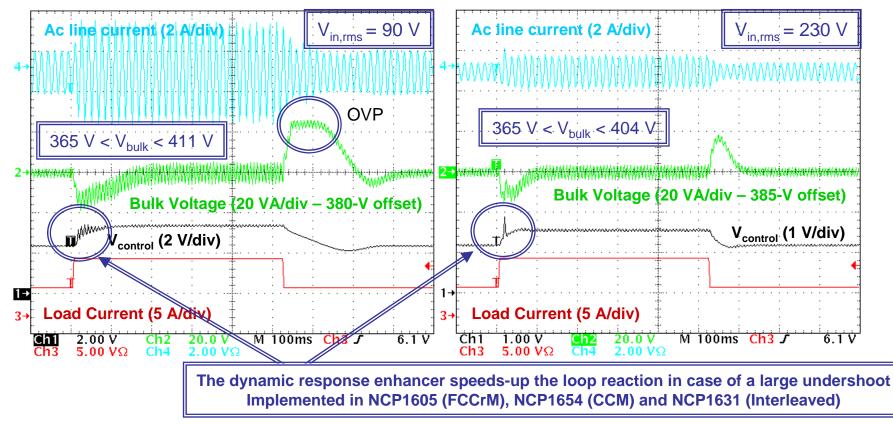

## **Abrupt Load Changes**

- A 19 V / 7 A loads the PFC stage

- The downstream converter swings from 7.0 A to 3.5 A (2 A/µs slope)

• The dynamic response enhancer reduces the undershoot at low line

# Agenda

- Introduction

- Deriving a small-signal model

- General method

- Practical example: NCP1605-driven PFC stages

- Compensating the loop

- Type-2 compensation

- Influence of the line and power level

- Computing the compensation

- Practical example

- Conclusion

## Conclusion

- General considerations were illustrated by the case of NCP1605-driven PFC stages

- A small signal model of PFC boosts can be easily derived

- The proposed method is independent of the operating mode

- A type-2 compensation is recommended

- If no feed-forward is implemented, the loop bandwidth and phase margin vary as a function of the line magnitude

- The crossover frequency does not vary as a function of the load

- A resistive load can be used for the computation even if the PFC stage feeds a power supply (negative impedance) – See back-up

## **For More Information**

- View the extensive portfolio of power management products from ON Semiconductor at <u>www.onsemi.com</u>

- View reference designs, design notes, and other material supporting the design of highly efficient power supplies at <u>www.onsemi.com/powersupplies</u>