# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

## ON Semiconductor®

# Application Note Describing Dual Edge Rails Tuning

ON Semiconductor offers a wide range of voltage regulators for Intel platforms. For multiphase dc-dc solutions dual edge rail architecture is used. This application note discusses the tuning techniques for a dual edge rail.

## **Dual Edge Rails**

The dual edge modulator under discussion in this application note compares the compensated error signal with a number of internally generated interleaved ramps to produce the required PWM duty cycle. The number of ramps is equal to the number of phases per output voltage rail. Dual edge modulation offers advantages such as fast response to load attack and release events, fixed frequency operation allowing for predictable output voltage ripple. The following sections describe tuning of a dual edge voltage rail.

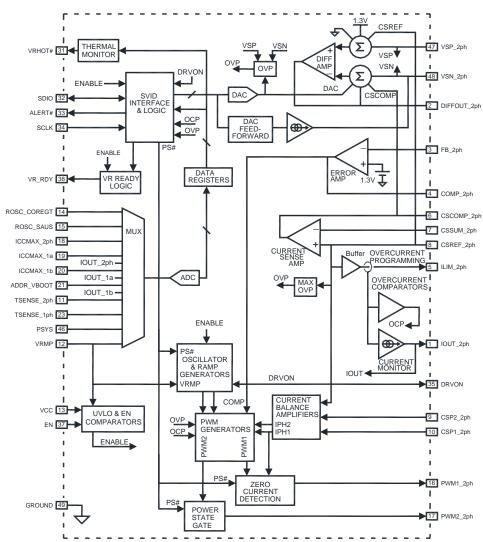

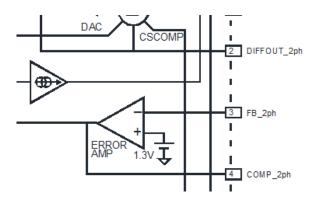

Figure 1: Block Diagram of Dual Edge Architecture

Table 1: Glossary of terms and their values

| Name                    | Description                               | Value  |

|-------------------------|-------------------------------------------|--------|

| LL                      | Loadline                                  | 2 mΩ   |

| f <sub>sw</sub>         | Switching Frequency                       | 600kHz |

| V <sub>IN</sub>         | Maximum input voltage                     | 20V    |

| V <sub>OUT</sub>        | Output voltage                            | 0.9V   |

| V <sub>ov</sub>         | Allowed overshoot                         | 70mV   |

| CCM V <sub>RIPPLE</sub> | Continuous conduction mode voltage ripple | ±10mV  |

| ΔΙ                      | Maximum load step                         | 70A    |

| Ilimit                  | Over current protection trip value        | 80A    |

| IccMax                  | Rail maximum current                      | 70A    |

| Np                      | Number of Phases                          | 3      |

## **LC Selection**

The selection of output stage components is usually the first step in any VR system design. The inductor and capacitor selection directly influences the maximum output current, output voltage ripple and dynamic performance.

The minimum value for an output inductor required can be estimated by the expression below:

$$L_{\min} \geq \frac{V_0 \times LL}{f_{SW} \times V_{RIPPLE}} \times \left[1 - N_p \times \frac{V_0}{V_{in}}\right]$$

Eq.1

$$L_{\min} \ge \frac{0.9V \times 2m\Omega}{600kHz \times 20mV} \times \left\lceil 1 - 3 \times \frac{0.9V}{20V} \right\rceil = 130nH$$

$L_{selected} = 220nH$

The next step is to estimate the output capacitance required. The selected output capacitance can be a

mix of multilayer ceramic capacitors (MLCCs) and electrolytic capacitors.

The value for the required minimum output capacitance can be estimated by the expression below:

$$C_{OUTstarting} = \frac{L_{select} / N_P \times \Delta I}{(LL + \frac{V_{OV}}{\Delta I}) \times V_0}$$

Eq 2

$$C_{OUTstarting} = \frac{220nH/3\times70A}{(2m\Omega + \frac{70mV}{70A})\times0.9V} = 1.9mF$$

Please note  $C_{\text{OUT}}$  may be higher or lower based on board performance. Dynamic testing needs to be completed to reach the optimum value of  $C_{\text{OUT}}$ .

# Discrete Components Selection for Tuning

#### **Differential Current Balance Amplifier**

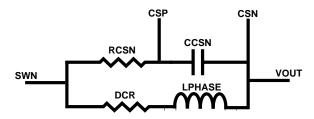

Inductor DCR current sensing method is used to extract accurate per phase current information. For this purpose RCSN and CCSN is connected in parallel to the inductor as shown in Figure 2 below:

Figure 2: DCR current Sensing

Ensure that the CCSN chosen is in the range of 20nF to 470nF, while keeping the RCSN above  $2k\Omega$ . Thus, the expression for RCSN can be written as

$$RCSN = \frac{L_{PHASE}}{CCSN \times DCR}$$

Eq 3

Select  $C_{CSN}$ =0.033 $\mu F$  and by using above expression the value of  $R_{CSN}$  can be calculated as follows:

$$R_{CSN} = \frac{0.22 \mu H}{0.033 \mu F \times 2.76 m\Omega} = 2.415 k\Omega$$

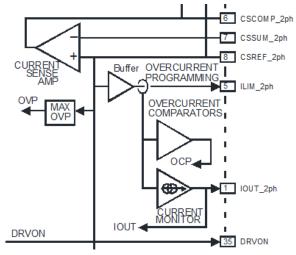

#### **Total Current Sense Amplifier**

The currents from all phases are summed together in a single temperature compensated total current signal.

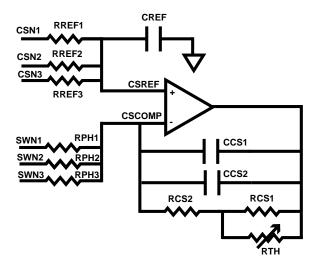

The  $R_{ref}$  resistors average the voltages at the output sides of the inductors to create a low impedance reference voltage CSREF. The  $R_{PH}$  are use to set the gain of the current sense (CS) amplifier and influence the loadline. Figure 3 below is showing an example of a two phase current sense amplifier.

Figure 3: A typical Total Current Sense Amplifier

The DC equation for the current sense is

$$V_{CSCOMP-CSREF} = -\frac{Rcs2 + \frac{Rcs1 * Rth}{Rcs1 + Rth}}{Rph} * (Iout_{Total} * DCR)$$

Eq 4

Taking V<sub>cscomp</sub>-V<sub>csref</sub> divided by lout gives the resulting load line of the rail as follows:

$$LL = \frac{R_{CS}}{R_{DL}} \times DCR$$

Eq 5

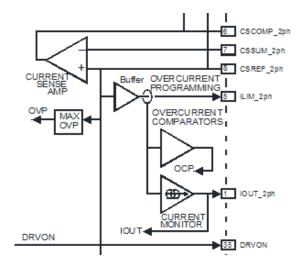

Figure 4: Section of Block Diagram showing CS

Amplifier block

It is recommended to choose Rcs =  $220k\Omega$  and then calculate R<sub>CS1</sub>, R<sub>CS2</sub> and R<sub>TH</sub> as described in the next section and then solve for Rph(x).

#### **DCR Temperature Compensation**

An NTC Thermistor ( $R_{TH}$ ) is placed in the feedback network of total current sense amplifier. The thermistor must be placed near the phase 1 inductor to sense the inductor temperature and compensate both the DC gain and the filter time constant for the DCR change with temperature. The values of  $R_{CS1}$  and  $R_{CS2}$  are set based on the effect of temperature on both the thermistor and inductor.

The following procedure and equations will give rise to the values of  $R_{CS1}$ ,  $R_{CS2}$  and  $R_{TH}$  (at 25°C)

- 1) Select an NTC thermistor close to selected R  $_{CS}.$  In this case an NTC value of  $220k\Omega$  is chosen.

- 2) The next step is to calculate the relative resistance of the selected thermistor at two temperatures. The temperatures that were chosen in this case are 50°C and 90°C. Calculate the relative resistance ratios A and B as follows:

$$A = \frac{R_{TH(50^{\circ}C)}}{R_{TH(25^{\circ}C)}} = \frac{68.411}{220} = 0.311$$

$$B = \frac{R_{TH(90^{\circ}C)}}{R_{TH(25^{\circ}C)}} = \frac{13.962}{220} = 0.0634$$

From the thermistor datasheet that is selected A and B can be calculated as 0.311 and 0.0634 respectively

3) Find the relative value of  $R_{CS}$  required for each of these temperatures. This is based on the percentage temperature change needed, which is initially 0.39% /°C. These are called  $r_1$  and  $r_2$  respectively and can be calculated as follows:

$$r_1 = \frac{1}{1 + TC \times (T_1 - 25^{\circ}C)} \quad r_2 = \frac{1}{1 + TC \times (T_2 - 25^{\circ}C)}$$

Where  $T_1 = 50^{\circ}\text{C}$ ,  $T_2 = 90^{\circ}\text{C}$ ,  $TC = 0.0039^{\circ}\text{C}^{-1}$

Substituting above values and the values of  $r_1$  and  $r_2$  can be calculated as 0.9112 and 0.7978 respectively.

The relative values for  $R_{CS1}$ ,  $R_{CS2}$  and  $R_{TH}$  are called  $r_{CS1}$ ,  $r_{CS2}$  and  $r_{TH}$  respectively. These values are calculated by using the expressions below:

$$r_{CS2} = \frac{(A-B)r_1r_2 - A(1-B)r_2 + B(1-A)r_1}{A(1-B)r_1 - B(1-A)r_2 - (A-B)}$$

$$r_{CS1} = \frac{(1-A)}{\frac{1}{1-r_{cs2}} - \frac{A}{r_1 - r_{cs2}}} \qquad r_{TH} = \frac{1}{\frac{1}{1-r_{cs2}} - \frac{1}{r_{cs1}}}$$

The values of  $r_{CS1}$ ,  $r_{CS2}$  and  $r_{TH}$  are calculated 0.738933, 0.340444 and 1.120791

4) Calculate the required value of R<sub>TH</sub> by using the expression below:

$$R_{TH} = r_{TH} \times R_{CS} = 246.1k\Omega$$

The closest value to 246.574k $\Omega$  is 220k $\Omega$ . Therefore, we select a NTC Thermistor of value 220k $\Omega$ .

5) Compute a scaling factor k based on the ratio of the actual thermistor used relative to the calculated ideal.

$$k = \frac{R_{TH(ACTUAL)}}{R_{TH(CALCULATED)}} = 0.894$$

6) The value of R<sub>CS1</sub> and R<sub>CS2</sub> can be calculated by using equations below:

$$R_{CS1} = R_{CS} \times k \times r_{cs1}$$

$$R_{CS2} = R_{CS} \times ((1-k) + (k \times r_{cs2}))$$

The calculated values of Rcs1 & Rcs2 are  $66.81k\Omega$  and  $168.3k\Omega$  respectively. Finally we can select the closest standard resistor values for R<sub>CS1</sub>=75k $\Omega$  and R<sub>CS2</sub>=165k $\Omega$ .

#### **Loadline Programming**

The gain of the total current sense amplifier is decided by the ratio of  $R_{CS}$  and  $R_{PH.}$  The value of  $R_{CS}$  can be calculated as follows:

$$R_{CS} = R_{CS2} + \frac{R_{CS1} \times R_{TH}}{R_{CS1} + R_{TH}} \label{eq:RCS}$$

Eq 6

Substituting RCS1=75k $\Omega$ , R<sub>CS2</sub>=165k $\Omega$  and R<sub>th</sub>=220k $\Omega$  the calculated value of R<sub>CS</sub> =220.932k $\Omega$ . The corresponding value of RPH=304.88k $\Omega$  can be calculated by using the expression below:

$$R_{PH} = \frac{R_{CS}}{LL} \times DCR = \frac{220k\Omega}{2m\Omega} \times 2.76m\Omega = 304k\Omega$$

Eq. 7

#### **CCS Calculation**

The total current signal is proportional to the component of inductor voltage caused by DCR drop and consequently relative to inductor current. Connecting  $C_{CS2}$  in parallel with  $C_{CS1}$  allows fine tuning of the pole frequency. It is recommended to fine tune this filter frequency during transient testing. The expression for the calculation of CCS is as follows:

$$C_{CS} = \frac{L}{DCR \times R_{CS}}$$

Eq 8

$$C_{CS} = \frac{220nH}{2.76m\Omega \times 220k\Omega} = 362 pF$$

#### **Over Current Protection**

The current limit of the converter is programmed with a resistor  $R_{\text{ILIM}}$  between the ILIM and CSCOMP pins. The expression for the setting of Rilim is as follows:

$$R_{ILIM} = \frac{\frac{R_{CS}}{R_{PH}} \times (I_{OUT} \times DCR)}{10 \mu A}$$

Eq 9

The maximum current limit is 80A.

$$R_{ILIM} = \frac{\frac{220k\Omega}{304k\Omega} \times (80A \times 2.76m\Omega)}{10\mu A} = 16k\Omega$$

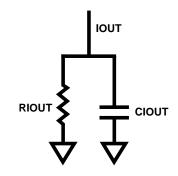

#### **RIOUT Selection**

The IOUT pin sources a current equal to 10 times the ILIM sink current. A resistor to ground on the IOUT pin converts this current to a voltage.  $R_{\text{IOUT}}$  should be scaled such that a load current equal to the rail max current generates a 2V signal.

$$R_{IOUT} = \frac{2 \times R_{ILIM}}{10 \times (\frac{R_{CS}}{R_{PH}} \times DCR) \times I_{OUT \text{ max}}}$$

Eq 10

$R_{\text{IOUT}}$  is calculated as follow for an IOUT max of 70A:

$$R_{IOUT} = \frac{2V \times 16k\Omega}{10 \times (\frac{220k\Omega}{304k\Omega} \times 2.76m\Omega) \times 70A} = 22.8k\Omega$$

A capacitor ( $C_{IOUT}$ ) is selected to filter output ripple current information from the lout reading but must not be so large that it significantly increases the

settling time of the IOUT reading. The  $C_{IOUTSP}$  chosen for this case is 470pF.

Figure 5: RIOUT Network

Figure 6: Section of Block Diagram showing ILIM and IOUT block

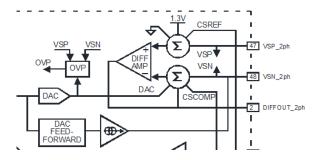

## **DAC Feed Forward Programming**

DAC feed-forward is used to aid the output voltage in tracking the internal DAC during VID up transitions. The DAC feed-forward implementation is realized by having a filter on the VSN pin. Programming RFF sets the gain of the DAC feed-forward and CFF provides the time constant to cancel the time constant of the system per the following equations.

Figure 7: DAC Feed Forward Filter

$$R_{FF} = C_{OUT} * LL * 453.6 \times 10^6$$

Eq 11

$$C_{FF} = \frac{LL * Cout}{R_{FF}}$$

Eq 12

Using Eq 11 and Eq 12 to calculate component values:

$$R_{EE} = 1.9mF * 2m\Omega * 453.6 \times 10^6 = 1.72k\Omega$$

$$C_{FF} = \frac{2m\Omega * 1.9mF}{1.72k\Omega} = 2.2nF$$

Figure 8: Section of Block Diagram DAC feed forward block

### **Voltage Compensation**

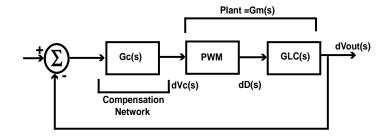

The block diagram of feedback Control Loop for a buck converter is shown below:

Figure 9: Block Diagram of a Control System

The PWM and output filter stages are grouped together as the plant (modulator)  $G_m(s)$ . The compensation network transfer function is  $G_c(s)$ . The open loop transfer functions of the output Vout with respect to duty cycle D(s) can be written as follows:

$$\frac{dV_{out}(s)}{dD(s)} = V_{in} \frac{sR_{ESR}C_{out} + 1}{s^2LC_{out} + s\left[\frac{L}{R_0} + C_{out}(DCR + R_{ESR})\right] + 1}$$

Eq 13

$R_{\text{ESR}}$  = ESR of output capacitor C, L = Inductance of output inductor,  $C_{\text{OUT}}$ = Output capacitance,  $R_0$ =output load

There will be two poles and one zero in the above transfer functions. The poles are created by the resonance of LC output filter while the zero is created by the ESR of the output caps. The double poles are located at

$$f_p = \frac{1}{2\pi\sqrt{L_n C_{OUT}}}$$

Eq 14

Where  $L_n = \frac{L}{n}$  and n= number of phases. The zero is

located at

$$f_0 = \frac{1}{2\pi R_{ESR} C_{OUT}}$$

Eq 15

Figure 10: Section of Block Diagram showing voltage compensation block

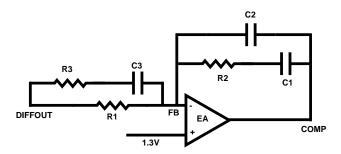

Type III compensation is used optimize the response of the VR. This network provides a pole at the origin with two poles and two zeros.

Figure 11: Type III compensator

The open loop transfer functions of the output Vout with respect to compensation network  $V_{\text{c}}(s)$  can be written as follows:

$$\frac{dV_{out}(s)}{dV_{C}(s)} = \frac{V_{IN}}{V_{M}} \frac{sR_{ESR}C_{OUT} + 1}{s^{2}LC_{out} + s\left[\frac{L}{R_{0}} + C_{OUT}(DCR + R_{ESR})\right] + 1}$$

Substituting V<sub>M</sub>=V<sub>IN</sub>/10

$$\frac{dV_{out}(s)}{dV_C(s)} = 10 \times \frac{sR_{ESR}C_{OUT} + 1}{s^2LC_{OUT} + s\left[\frac{L}{R_0} + C_{OUT}(DCR + R_{ESR})\right] + 1}$$

Eq 16

Example:  $f_C$ =120 kHz, L=220n H,  $N_p$ =3, DCR=2.76m $\Omega$ ,  $C_{out}$ =1.9m F,  $R_0$ =10k $\Omega$ ,  $R_{ESREQ}$ = 30 $\mu\Omega$ , M=Desired Phase Margin=75°

The basic steps to synthesize a type III compensation network are as follows:

1) Choose a cross over frequency and determine the plant gain  $G_{\rm M}$  at the cross over frequency,  $f_{\rm C}$

$$G_{m} = 10 \times \frac{2 \times \pi \times f_{C} \times R_{ESREQ} C_{OUT} + 1}{(2 \times \pi \times f_{C})^{2} L_{n} C_{OUT} + (2 \times \pi \times f_{C}) \left[ \frac{L_{n}}{R_{0}} + C_{OUT} (DCR_{EQ} + R_{ESREQ}) \right] + 1}$$

Substituting the values in the above expression gives

$G_m = 0.128$

2) Determine the LC double pole and ESR zero frequencies  $f_P$  and  $F_Z$  using Eq14 and Eq15 respectively.

$$f_{p} = \frac{1}{2\pi\sqrt{L_{n}C_{out}}} = \frac{1}{2\pi\sqrt{\left[\frac{220nH}{3}*1.9mF\right]}} = 13.5kHz$$

$$f_{z} = \frac{1}{2\pi R_{ESREO}C_{out}} = \frac{1}{2\pi \times 30\mu\Omega \times 1.9mF} = 2.79.MHz$$

3) Determine the plant Phase shift P<sub>m</sub> in degrees at f<sub>c</sub> using the expression below:

$$P_{m} = \left[ Tan^{-1} \left( \frac{f_{C}}{f_{Z}} \right) - 2Tan^{-1} \left( \frac{f_{C}}{f_{P}} \right) \right]$$

Eq 17

Substituting the values in the above expression to calculate plant phase shift gives:

$$P_{m} = \left[ Tan^{-1} \left( \frac{120kHz}{2.79MHz} \right) - 2Tan^{-1} \left( \frac{120kHz}{13.5kJz} \right) \right] = -164.7^{\circ}$$

4) Determine the required compensation network gain G. The gain G is the required compensation gain at  $f_C$  and must be equal to the plant attenuation. Substituting the value of  $G_m$  gives the value of required compensator gain as:

$$G = \frac{1}{0.128} = 7.8125$$

5) Choose the desired phase margin (75°) at f<sub>c</sub>. Calculate the required phase boost by using expression below:

$$\theta_{hoost} = M - Pm - 90^0$$

Eq 18

Substituting the values in the above expression gives phase boost as follows:

$$\theta_{boost} = 75^{\circ} + 165^{\circ} - 90^{\circ} = 149.7^{\circ}$$

6) Determine the K value as follows:

$$K = \tan^2 \left[ \frac{\theta_{boost}}{4} + 45^0 \right]$$

Substituting the values in the above expression gives K as follows:

$$K = \tan^2 \left[ \frac{150^{\circ}}{4} + 45^{\circ} \right] = 56.6$$

7) Choose a value of  $R_1$  between  $500\Omega$  and  $1k\Omega$ . Selecting  $R_1$ = $1k\Omega$  and calculate the values of the components using the K-factor approach expressions below:

$$R_2 = \frac{\sqrt{K}}{K - 1}GR1 = 1.06k\Omega$$

$$R_3 = \frac{R_1}{K - 1} = 18\Omega$$

$$C_1 = \frac{K - 1}{2\pi f_C G R_1} = 9.44 nF$$

$$C_2 = \frac{1}{2\pi f_C G R_1} = 170 \, pF$$

$$C_3 = \frac{1}{2\pi f_C GR_1} \cdot \frac{K-1}{\sqrt{K}} = 1.26nF$$

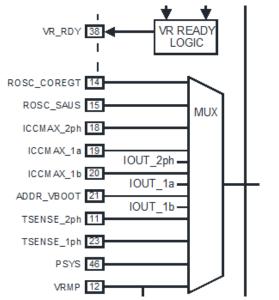

#### **IccMax Setting**

On startup a resistor to ground on the IccMax pin programs the IccMax register value (for details regarding IccMax please consult the relevant datasheet). The value of the register is 1A per LSB.

The exact expression of IccMax can be found in the relevant datasheets

Figure 12: Section of Block showing ICCmax & Tsense block

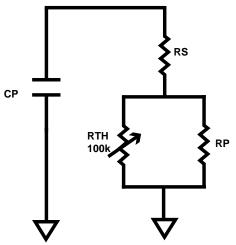

#### **TSENSE Network Tuning**

A temperature monitoring input is provided by the Tsense pin. The voltage on the temperature sense input is sampled by the internal ADC. See the specification table for the thermal sensing voltage thresholds and source current in the corresponding datasheets.

Figure 13: Tsense Network

The steps for the calculation of Tsense network is as follows:

- Select VR\_HOT and ALERT assert threshold voltages form the datasheet.

- 2. Convert the threshold voltages in the datasheet to resistor values using  $I_{\text{bias}}$  current from the datasheet as  $R_1$  and  $R_2$ .

- 3. Select two target temperatures  $T_1$  and  $T_2$  and calculate NTC resistance values at those temperatures as  $R_{n1}$  and  $R_{n2}$  using expression below:

$$R_{nx}=R_{NTC} imes e^{eta(rac{1}{T_x}-rac{1}{T_0})}$$

Eq 19

T<sub>x</sub>= Selected temperature in Kelvin

T<sub>0</sub>= Room temperature in Kelvin

4. Calculate the value of A,B and C as follows:

$$A = (R_{n1} + R_{n2}) - (R_{n2} + R_1) \quad \text{Eq 20}$$

$$B = (R_2 - R_1) \times (R_{n1} + R_{n2}) \quad \text{Eq 21}$$

$$C = (R_2 - R_1) \times (R_{n1} \times R_{n2}) \quad \text{Eq 22}$$

5. Calculate the value of R<sub>P</sub> using the expression below:

$$R_P = \frac{-B \pm \sqrt{B^2 - 4AC}}{2A}$$

Eq 23

6. Calculate the value of Rs using the expression below:

$$R_S = R_1 - \frac{R_{n1}R_P}{R_{n1} + R_P}$$

Eq 24

Example:

For  $I_{bias}$ =120 $\mu$ A, VR\_Hot threshold=468m V, Alert threshold=488m V the values of  $R_1$  and  $R_2$  can be calculated as:

$R_1=3.9k\Omega$ ,  $R_2=4.066k\Omega$

For  $T_1$ =104°C,  $T_2$ =100°C,  $T_0$ =25°C,  $R_{NTC}$ =100k $\Omega$  and  $R_{n2}$  can be calculated as:

$R_{n1}$ =5.049 k $\Omega$ ,  $R_{n2}$ =5.698k $\Omega$

Using Eq 23 R<sub>P</sub> can be calculated as:

$R_P = 5.52k\Omega$

Using Eq 24 R<sub>s</sub> can be calculated as:

$R_S = 1.26k\Omega$

7. The recommended value of  $C_P$  is  $0.1\mu F$ .

#### Conclusion

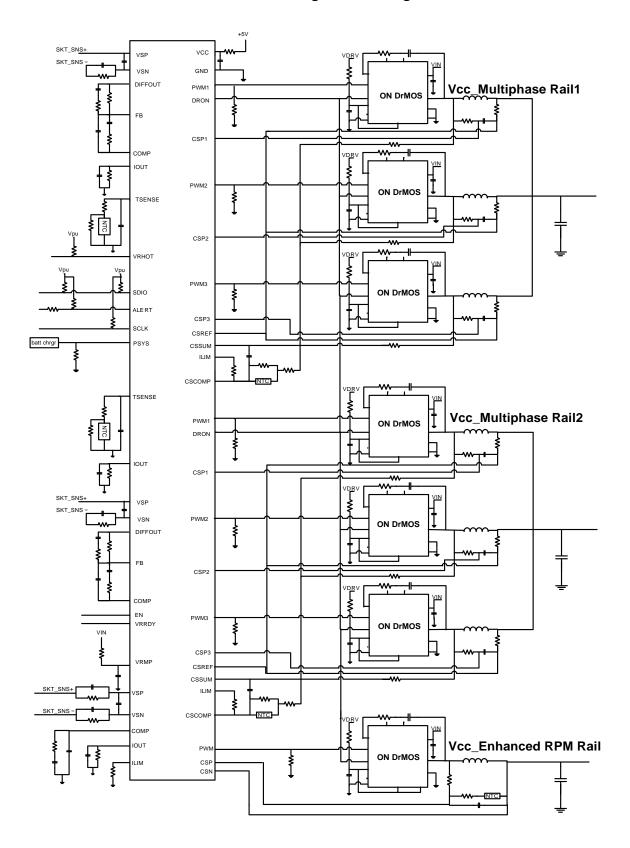

The equations discussed previously are given to aid the platform designer to select the compensation and configuration components for use with ON Semiconductor's multiphase VR controller. An overall example of schematic block diagram is shown in Figure 14 below:

Figure 14: Rails schematic Block Diagram