# **ON Semiconductor**

## Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# Designing Stable Control Loops for High Current Voltage Mode Synchronous Buck Converter with the NCP323X

ON Semiconductor®

www.onsemi.com

## **APPLICATION NOTE**

## Introduction

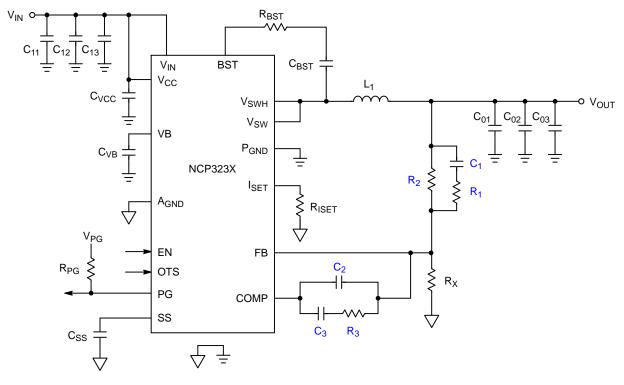

The NCP323X is a high current, high efficiency, voltage-mode synchronous buck converter which operates from 4.5 V to 21 V input and generates output voltages down to 0.6 V at up to 30 A. NCP323X utilizes voltage mode with voltage feed-forward control to respond instantly to  $V_{\rm IN}$  changes and provide for easier compensation over the supply range of the converter. The typical application circuit is shown in Figure 1.

Despite the NCP323X's control loop is typical type III voltage feedback compensation, its design can't be overlooked, especially in telecom application. This article will show how to carry out the feedback compensation design.

To further ease the work of the design engineer, ON Semiconductor has developed a design tool CompCalc3 which is based on LabVIEW<sup>®</sup> Runtime Engine. The software plots the various ac responses based on the design component values.

Figure 1. Typical Application Circuit with the NCP323X

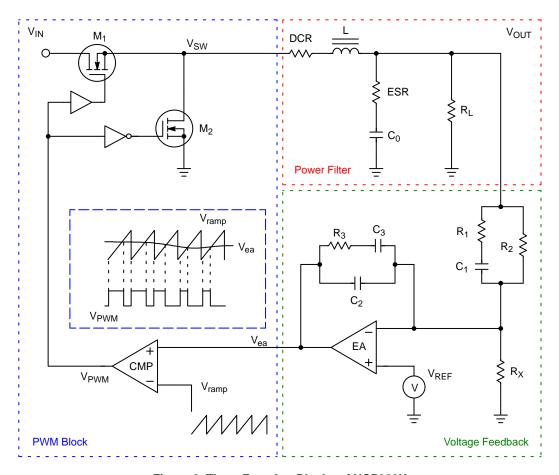

Figure 2 presents a simplified diagram of a closed-loop controlled NCP323X. The converter is divided into three functional blocks for the convenience of modeling: the power stage, PWM block, and voltage feedback circuit.

Each functional block can be transformed into the respective small-signal model using various modeling techniques. The small-signal models of the three functional blocks are later merged to yield a complete small-signal model for the closed-loop controlled PWM converter.

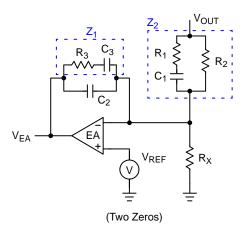

The output voltage  $V_{out}$  is fed to a voltage feedback circuit, consisting of an op-amp, reference voltage  $V_{ref}$ , and two R–C impedance blocks. The output of the voltage feedback circuit is the control voltage,  $V_{ea}$ , which is used as the input signal for the PWM block. The voltage feedback circuit operates based on the principle of the negative feedback.

Table 1 list all products of NCP323X family and their feedback control loop design parameters.

Figure 2. Three Function Blocks of NCP323X

Table 1. NCP323X FAMILY PARAMETERS RELATED TO FEEDBACK CONTROL LOOP DESIGN

| Part Number | V <sub>ramp</sub> Amplitude | EA Parameters                | Operation Condition                                                      |

|-------------|-----------------------------|------------------------------|--------------------------------------------------------------------------|

| NCP3231A    | V <sub>IN/</sub> 6.6        | Typ. GDB: 85 dB              | $F_S = 500 \text{ kHz}, 25 \text{ A}$                                    |

| NCP3231     | V <sub>IN</sub> /6.6        | Min. GDB: 60 dB UGBW: 24 MHz | F <sub>S</sub> = 500 kHz, 25 A                                           |

| NCP3232N    | V <sub>IN</sub> /6.6        |                              | F <sub>S</sub> = 500 kHz, 15 A                                           |

| NCP3230     | V <sub>IN</sub> /6.3        |                              | $F_S = 500 \text{ kHz}, 30 \text{ A}$                                    |

| NCP3233     | V <sub>IN</sub> /5.4        |                              | $V_{INX} = GND, F_S = 300/500 \text{ kHz/1 MHz}, 20 \text{ A}$           |

|             | V <sub>IN</sub> /1.4        |                              | $V_{INX} = 3.3 \text{ V}, F_S = 300/500 \text{ kHz/1 MHz}, 20 \text{ A}$ |

| NCP3235     | V <sub>IN</sub> /6.5        |                              | $F_S = 550 \text{ kHz/1 MHz}, 15 \text{ A}$                              |

#### **PWM Block**

The PWM block in Figure 2 illustrates the operation of PWM control. The PWM block compares the control signal  $V_{ea}$  against the saw-tooth ramp signal,  $V_{ramp}$ , to generate the pulse-width modulated switch drive sign.

The constant small-signal gain of the PWM block is termed as the PWM gain or modulator gain  $F_m$ . The PWM gain is given by the inverse of the height of the ramp signal:

$$F_{m} = \frac{V_{SW}}{V_{ea}} = \frac{V_{IN}}{V_{p}}$$

(eq. 1)

Where  $V_p$  is the amplitude of  $V_{ramp}$ .

This simple result is the outcome of the fundamental assumption that the control voltage  $V_{ea}$  does not vary widely within one switching period and only changes slowly over several switching periods (the switch would produce the open-circuit, rail-to-rail square wave  $V_{sw} = D \cdot V_{IN}$  with the duty cycle  $D = V_{ea}/V_p$ , or in total  $V_{sw} = (V_{IN}/V_p) \cdot V_{ea})$ .

NCP323X employs the input voltage feed-forward control method that makes the ramp signal amplitude is proportional to the input voltage, i.e.  $F_m$  is CONSTANT.

The input voltage feed-forward control method provides two main advantages: firstly the gain of the loop does not depend on the input voltage, the converter's behavior maintains the same for various input voltage; secondly higher ramp signal amplitude can mitigate the parasitic pulses due to the higher noise induced by higher input voltage switching.

## **Power Filter**

The power filter is the well-known double pole single zero LC filter. Its transfer function is:

$$G_{LC\_Filter} = \frac{1 + \frac{s}{\omega_{esr}}}{1 + \frac{s}{Q\omega_0} + \frac{s^2}{\omega_0^2}}$$

(eq. 2)

Where,

$$\omega_{\rm esr} = \frac{1}{C_0 \cdot {\sf ESR}}$$

(eq. 3)

$$Q = R_L \cdot \sqrt{\frac{C_0}{I}}$$

(eq. 4)

$$\omega_0 = \frac{1}{\sqrt{L \cdot C_0}}$$

(eq. 5)

#### **Open Loop Power Stage**

The small-signal transfer function of open loop power stage which from the control input  $V_{ea}$  to the output  $V_{out}$  is:

$$G_{\text{open\_loop}} = F_{\text{m}} \cdot \frac{1 + \frac{s}{\omega_{\text{esr}}}}{1 + \frac{s}{Q\omega_{0}} + \frac{s^{2}}{\omega_{0}^{2}}}$$

(eq. 6)

Note that for  $\omega << \omega_{esr}$ , the LC structure exhibits the familiar second-order low-pass response LHP. However, at high frequencies, where C acts as a short circuit compared to its own ESR, the structure turns into a first-order LR circuit.

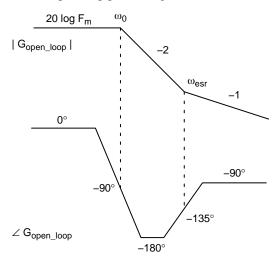

The borderline between the two cases is the frequency at which  $|ZC(j\omega_{esr})| = DCR$ . Aptly referred to as left-half-plane zero (LHPZ) frequency,  $\omega_{esr}$  marks the point where slope changes from -40 dB/dec to -20 dB/dec, and phase is on its way to get boosted by  $+90^{\circ}$ . Figure 3 shows the effect of the LHPZ on open loop power stage.

Figure 3. The Bode Plot of Open Loop Power Stage

#### Voltage Feedback

The negative feedback control is used through the feedback network, EA compensator network, and PWM to alleviate the variation caused by the disturbances.

A simple method that ensures the stable operation of the voltage-mode buck converter without modifying EA compensation is the use of an output capacitor with a high ESR value. Placing the ESR zero below the unit gain frequency can help improve the phase margin. If the ESR zero is placed at lower frequencies, a larger phase margin can be obtained to increase the stability. However, its low DC gain indicates poor load regulation and low output voltage accuracy, and the current flowing in or out of the capacitor induces a voltage drop across the ESR. A large voltage ripple and undershoot/overshoot voltage occur because of the IR drop voltage formed by the current variations across the ESR. Using the ESR zero can certainly simplify the compensation technique at the cost of regulation performance.

The voltage feedback network is composed of two feedback resistors  $R_2$  and  $R_X$ . Using the feedback network, the output voltage information is fed back as error signal. The error signal between the feedback voltage and the reference voltage is amplified by the EA, which contains the compensation network.

In frequency compensation design, the crucial task is to design the compensated EA. Generally, achieving high DC gain at low frequencies, a 45° phase margin, and at least a 10 dB gain margin is demanded.

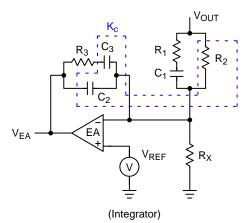

High DC gain and large bandwidth are need for regulation performance and fast transient response concurrently. To improve the regulation performance, an integrator can used to increase the DC gain. After using an integrator, the loop transfer function contains three poles (one pole at the origin is formed by the ideal integrator and two LHP poles, i.e. LC double poles). Then two additional LHP zeros are needed below the crossover frequency to increase the phase margin when a high DC gain is required at the same time. Type III compensation, which is commonly used in voltage-mode buck converters, is introduced to have two LHP zeros.

#### Type III Compensation

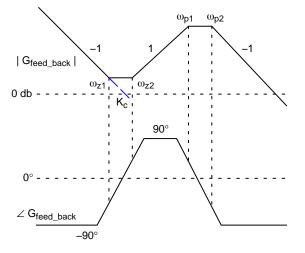

Type III compensation containing three LHP poles and two LHP zeros to obtain a high DC gain and a large bandwidth at the same time.

The small-signal transfer function of Type III compensation is:

$$G_{\text{feed\_back}} = \frac{K_c}{s} \cdot \frac{\left(1 + \frac{s}{\omega_{z1}}\right) \cdot \left(1 + \frac{s}{\omega_{z2}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right) \cdot \left(1 + \frac{s}{\omega_{p2}}\right)} \quad \text{(eq. 7)}$$

Where:

$$K_c = \frac{1}{R_2 \cdot (C_2 + C_2)}$$

(eq. 8)

$$\begin{split} &\omega_{z1} = \frac{1}{R_3 \cdot C_3} \;, \qquad \omega_{z2} = \frac{1}{\left(R_1 + R_2\right) \cdot C_1} \\ &\omega_{p1} = \frac{1}{R_1 \cdot C_1} \;, \qquad \omega_{p1} = \frac{1}{R_3 \cdot \frac{C_2 \cdot C_3}{C_2 + C_3}} \end{split} \tag{eq. 9}$$

For the pole/zero pair, the phase boost is obtained from:

boost =

$$\tan^{-1} \left( \frac{f}{f_{z1}} \right) + \tan^{-1} \left( \frac{f}{f_{z2}} \right)$$

$$- \tan^{-1} \left( \frac{f}{f_{p1}} \right) - \tan^{-1} \left( \frac{f}{f_{p2}} \right)$$

(eq. 10)

The gain or attenuation G at crossover must have to compensate the close loop gain to 0-dB. Then the 0-dB crossover pole position is at

$$K_c = G \cdot \omega_{z1} \cdot \frac{\sqrt{1 + \left(\frac{f}{f_{p1}}\right)^2} \sqrt{1 + \left(\frac{f}{f_{p2}}\right)^2}}{\sqrt{1 + \left(\frac{f}{f_1}\right)^2} \sqrt{1 + \left(\frac{f}{f_{z2}}\right)^2}} \qquad \text{(eq. 11)}$$

Figure 4. The Bode Plot of Type III Compensation

Figure 4 shows the asymptotic plot of the type III feedback compensation. The exact locations of the zeros and poles must be determined in consideration of their impacts on stability margins and closed-loop transfer functions.

With the type III compensation, the closed loop transfer function is expressed by

$$\begin{split} G_{system} &= G_{open\_loop} \cdot G_{feed\_back} & \text{(eq. 12)} \\ &= F_m \cdot \frac{K_c}{s} \cdot \frac{\left(1 + \frac{s}{\omega_{esr}}\right) \! \left(1 + \frac{s}{\omega_{z1}}\right) \! \left(1 + \frac{s}{\omega_{z2}}\right)}{\left(1 + \frac{s}{Q\omega_0} + \frac{s^2}{\omega_0^2}\right) \! \left(1 + \frac{s}{\omega_{p1}}\right) \! \left(1 + \frac{s}{\omega_{p2}}\right)} \end{split}$$

The typical type III compensation design guideline established as follows:

1. Select a crossover frequency  $f_c$  that is at least three to five times away from the resonating peak  $f_0$  and at most one fifth away from the switching frequency  $f_s$ , i.e.  $3\sim5$   $f_{LC} \le f_c \le 0.2$   $f_s$ .

Figure 5. EA Design with Type III Compensation

2. Look the open loop transfer function  $G_{open\_loop}$  and extract the gain deficiency  $G_{de}$  and phase PH at crossover frequency  $f_c$ . Then get compensator's amplification and phase boost with phase margin PM need provide: boost = PM – PH –90

- 3. Place the double zero pair near the LC network resonance frequency, usually between half of  $f_{LC}$  and  $f_{LC}$ , i.e.  $0.5~f_{LC} \le f_{z12} \le f_{LC}$ .

- 4. If the ESR-linked zero appears before crossover, neutralize it by placing a pole right at its location. If the zero appears far away from the bandwidth, simply place the pole at half of the switching frequency. This first pole can then be moved to adjust the phase margin at the wanted value if necessary.

- 5. To force gain decrease at high frequency and ensure gain margin exists, place a second pole sufficiently high so that its presence does not hamper phase margin. It is usually placed at half of the switching frequency.

- 6. The 0-dB crossover pole K<sub>c</sub> is computed in the integral term, which naturally depends on the wanted gain G at crossover.

- 7. Compute the compensation network (see Figure 5) components R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>.

$$R_{3} = \frac{GR_{2}f_{p2}}{f_{p2} - f_{z1}} \cdot \frac{\sqrt{1 + \left(\frac{f_{c}}{f_{p1}}\right)^{2}} \sqrt{1 + \left(\frac{f_{c}}{f_{p2}}\right)^{2}}}{\sqrt{1 + \left(\frac{f_{z1}}{f_{c}}\right)^{2}} \sqrt{1 + \left(\frac{f_{c}}{f_{p2}}\right)^{2}}} \quad \text{(eq. 13)}$$

8. Simulation and test the whole system bode plot with the compensation network components.

#### **Design Example**

This example describes the compensation design procedure for buck converter using NCP3231A. A design aid that allows users to determine component values quickly is available at <a href="https://www.onsemi.com">www.onsemi.com</a>.

#### DESIGN STEP 1:

**Define Convertor Parameters**

| $V_{IN}$   | 12 V                                           |

|------------|------------------------------------------------|

| $V_{OUT}$  | 0.8 V                                          |

| $I_{OUT}$  | 20 A                                           |

| IC         | NCP3231A                                       |

| $V_{ramp}$ | $V_{IN}/6.6$                                   |

| $F_{S}$    | 500 kHz                                        |

| $C_{O}$    | 470 μF                                         |

| ESR        | $0.5~\mathrm{m}\Omega$                         |

| L          | 330 nH                                         |

| DCR        | $0.5~\mathrm{m}\Omega$                         |

| PM         | 60°                                            |

|            | VOUT IOUT IC V <sub>ramp</sub> FS CO ESR L DCR |

#### **DESIGN STEP 2:**

Select Crossover Frequency,  $f_c$ , at which the final closed loop crosses 0-dB. Identify the open loop gain deficiency,  $G_{de}$ , and the phase, PH, at  $f_c$ .

$$\begin{split} f_{LC} &= 12.78 \text{ kHz} \\ f_c &= 60 \text{ kHz} \\ G_{de} &= -10.13 \text{ dB} \\ PH &= -166.16^{\circ} \end{split}$$

Compensator's amplification and phase boost at fc need is

G = 10.13 dB

$boost = 136.16^{\circ}$

**DESIGN STEP 3:**

Place zeros, fz1, fz2.

$f_{z1} = 0.5 \cdot f_{LC} = 6.39 \text{ kHz}$

$f_{z2} = 1 \cdot f_{LC} = 12.78 \text{ kHz}$

$f_{esr} = 677.26 \text{ kHz}$

Due to  $f_{esr} > f_s$ , then place first pole at half of  $f_s$ .

$f_{p1} = 0.5 \cdot f_s = 250 \text{ kHz}$

DESIGN STEP 4:

Compute the second pole,  $f_{p2}$ , by phase boost requirement.

$f_{p1} = 285.42 \text{ kHz}$

The 0-dB crossover pole K<sub>c</sub> is computed.

$K_c = 4.47 \text{ kHz}$

**DESIGN STEP 5:**

Compute the compensation components (choose R2 as feedback component).

$R_2 = 20 \text{ k}\Omega$

$R_3=14.34\;k\Omega$

$C_3 = 1.74 \text{ nF}$

$C_2 = 45.55 \text{ pF}$

$R_1 = 937 \Omega$

$C_1 = 594.8 \text{ pF}$

Replace this calculated values with standard resisters and capacitors.

$R_2 = 20 \; k\Omega$

$R_3 = 14.3 \text{ k}\Omega$

$C_3 = 1.8 \text{ nF}$

$C_2 = 47 \text{ pF}$

$R_1 = 931 \Omega$

$C_1 = 560 \text{ pF}$

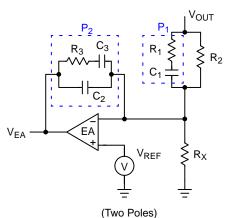

The bode plot of type III system example is present in Figure 6 which includes open loop, feed-back, EA and close loop curves. The 60 kHz@60° requirement can be met.

Figure 6. The Bode Plot of Type III System Example

Figure 7. The Bode Plot of Type III System of 100 kHz Bandwidth

Figure 8. The Bode Plot of Revised Type III System of 100 kHz Bandwidth

Figure 9. The Bode Plot of Type III System of 100 kHz Bandwidth and 80° Phase Margin

## **Discussion and Tips**

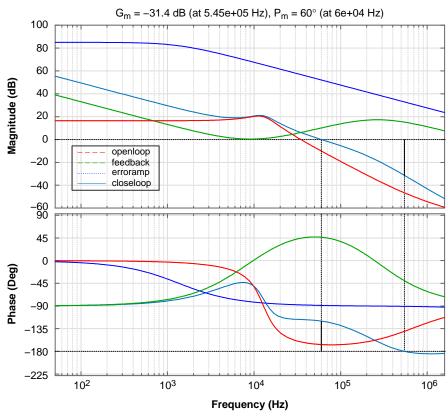

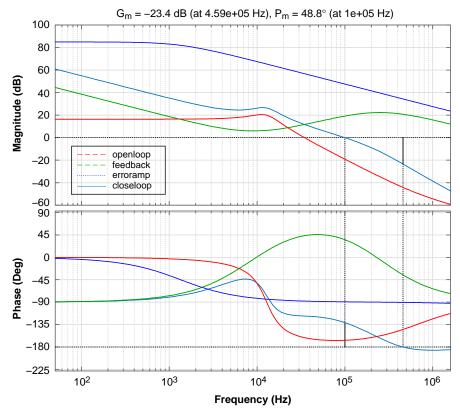

Figure 7 present the bode plot with 100 kHz@60° requirement and the compensation components is

$R_2 = 20 \text{ k}\Omega$

$R_3 = 27.4 \text{ k}\Omega$

$C_3 = 1 \text{ nF}$

$C_2 = 24 \text{ pF}$

$R_1=1.07\;k\Omega$

$C_1 = 560 \text{ pF}$

With zeros and poles

$f_{z1} = 0.5 \cdot f_{LC} = 6.39 \text{ kHz}$

$f_{z2} = 1 \cdot f_{LC} = 12.78 \text{ kHz}$

$f_{p1} = 0.5 \cdot f_s = 250 \text{ kHz}$

$f_{p2} = 0.5 \cdot f_s = 250 \text{ kHz}$

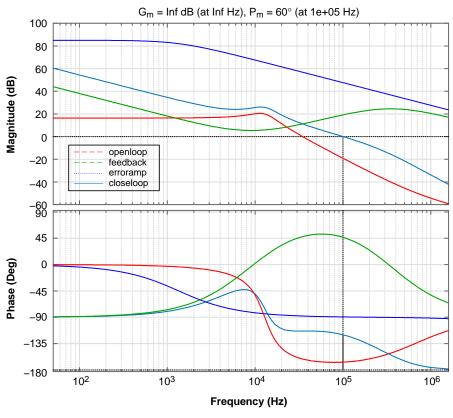

The result show that phase margin is 48.8° which can't meet 60° requirement. The improvement method is enlarging the separate distance of zeros and poles. One of the implement actions is setting the double poles to higher frequency positions and keep other parameters same, i.e.

$f_{n1} = 288 \text{ kHz}$

$f_{p2} = 425 \text{ kHz}$

The revised compensation components is

$R_2 = 20 \text{ k}\Omega$

$R_3=25.5\;k\Omega$

$C_3 = 1 \text{ nF}$

$C_2 = 15 \text{ pF}$

$R_1 = 931 \Omega$

$C_1 = 560 \text{ pF}$

Figure 8 present the revised bode plot which meet 100 kHz@60° requirement. Another implementation such as setting the double zeros to lower frequency positions also can get a similar PASS result which meet the requirement.

However, both of setting poles to higher frequency zone and frequency zeros to lower frequency zone have their drawbacks. Higher frequency poles degrade the noise immunity performance at high frequency zone; Lower frequency zeros make the loop gain smaller at low frequency zone which degrade the regulate accuracy and enlarge output voltage ripple.

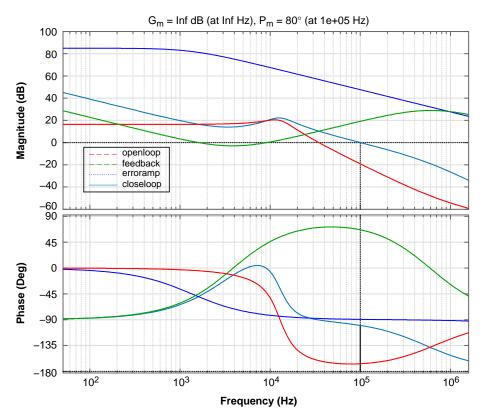

Can this app-note's design method generate reasonable value for some people pursued so-called HIGHER PERFORMANCE requirement such as 100 kHz bandwidth and 80° phase margin? The answer is NOT SURE. We can have a try! Take implement action of both higher frequency poles and lower frequency zeros

$f_{z1} = 0.3 \cdot f_{LC} = 3.83 \text{ kHz}$

$f_{z2} = 0.3 \cdot f_{LC} = 3.83 \text{ kHz}$

$f_{p1} = 1.2 \cdot f_s = 600 \text{ kHz}$

$\hat{f}_{p2} = 1.2 \cdot f_s = 600 \text{ kHz}$

The compensation components is

$R_2 = 20 \text{ k}\Omega$

$R_3 = 7.15 \text{ k}\Omega$

$C_3 = 5.6 \text{ nF}$

$C_2 = 36 \text{ pF}$

$R_1 = 127 \Omega$

$C_1 = 2.2 \text{ nF}$

Figure 9 present the theoretic bode plot with this setting. It seems meet the requirement. BUT, the green compensation gain curve encroach on the blue EA's open-loop gain curve (85 dB@24 MHz UGBW for NCP3231A) at the high frequency zone. This means the limit of the EA's gain has been reached and there is no more gain is available. The feedback function will roll off with one or more poles. The result will be that the desired loop

compensation is not achieved, and the crossover and phase margin will be less than anticipated.

The compensation design is a tradeoff between bandwidth and phase margin which is related to the internal EA's performance. The poles and zeros placement for converter is also a tradeoff between speed and regulation performance. The beauty of loop compensation design is exactly this tradeoffs.

LabVIEW is a registered trademark of National Instruments Corporation. The products described herein (NCP3231A) may be covered by one or more of the following U.S. patents: 6,362,067, 5,359,281, 5,073,850. There may be other patents pending.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor nexee the right to make changes without further notice to any products herein. ON Semiconductor andse no warranty, representation or guarantee regarding the suitability of its products on any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Se

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative