# Single-Pulse Unclamped Inductive Switching: A Rating System

### AN-7514/D

#### Summary

Unexpected transients in electrical circuits are a fact of life. The most potentially damaging transients enter a circuit on the power source lines feeding the circuit. Power control and conversion circuits are vulnerable because of their close proximity to the incoming lines. The circuit designer must provide protection or face frequent field failures. onsemi offers power MOSFET devices that are avalanche-failureresistant. Some semiconductor devices are intolerant of voltage transients in excess of their breakdown rating. Avalanche-capable devices are designed to be robust. The onsemi's POWERTRENCH® product line typifies rugged power devices. To assist the designer in their use, onsemi has devised an application-specific rating. This application note is intended to explain and illustrate the use of the single-pulse Unclamped Inductive Switching (UIS) rating curves.

#### **Failure Mechanisms**

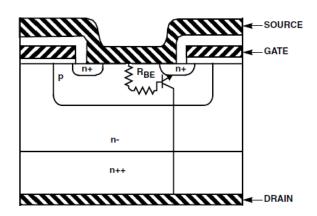

Early power MOSFET devices, not designed to be rugged, failed when the parasitic bipolar transistor indigenous to the vertical DMOS process turned on. Figure 1 is a cross-section of a unit cell from an N-channel enhancement mode device.

When a unit is in avalanche, the bipolar transistor is in a  $V_{CER}$  mode and heats rapidly. The avalanche-induced base-emitter voltage rises because of a positive resistive temperature coefficient. Simultaneously, the base emitter voltage, where the transistor becomes forward biased,

decreases because of its negative temperature coefficient. If a forward-bias condition is reached, device failure occurs. Blackburn's<sup>[1]</sup> measurements showed that this failure mode is a function of avalanche current and junction temperature; it is not energy related.

Ruggedness improvement technology has advanced to such a level that devices fail via a different mechanism. Devices are being designed and manufactured in which the parasitic bipolar turn—on is effectively suppressed. Device failure is thermally induced and current is distributed uniformly across the die. In this case, the failure occurs because the device junction temperature reaches the point at which the thermally generated carrier concentration (in the n—region) becomes comparable to the background doping (also in the n—region). At this point, the effective charge (sum of the fixed charge from the doping concentration plus the thermally generated carriers) in the epi layer becomes too large to support the applied voltage.

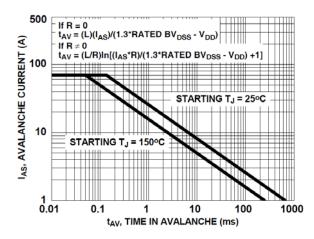

**onsemi**'s POWERTRENCH<sup>®</sup> MOSFET families epitomizes devices having UIS robustness. UIS capability testing of these devices shows that the failure current versus the time in avalanche closely approximates a negative one–half slope when the locus of device destruction point is plotted on a log–log graph. Device failure is not inversely proportional to current only, as it would be in the case of constant energy. **onsemi** supplies rating curves at starting junction temperatures of 25°C and 150°C (see Figure 2).

Figure 1. VDMOS Structure with Parasitic Bipolar Transistor

Figure 2. FDB8444 Unclamped-Inductive-Switching Safer Operating Area Curve (Single-Pulse UIS SOA)

#### **Test Circuit Equations**

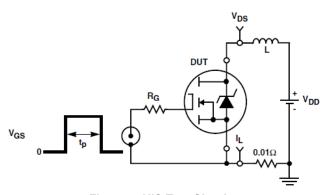

The circuit model (see Figure 3) used to describe a UIS test is a simple, lumped parameter series inductor / resistor circuit in which both the power supply and device avalanche voltage are presumed to be constant. All the equations that result from the mathematical analysis are listed in Table 1 by the  $V_{\rm DD}$ ; R conditions commonly referenced in the test method and commercial datasheets. The equations in row 1 are for the general case. The factor K is the ratio of the net voltage across the inductor and resistor to the resistor voltage drop. When K is large (K >30), the equations in row 1 reduce to those in rows 2 and 3. This can be accomplished mathematically by substituting the series expansion:  $\ln (1+X) = X - X2/2 +$ . Only the first term is needed for  $t_{\rm AV}$ , while two terms are required for  $E_{\rm AS}$  and  $P_{\rm AS}({\rm AVE})$ . Time in avalanche,  $t_{\rm AV}$ , is the important parameter for a rugged

device. Reviewing the expressions for  $t_{AV}$  in Table 1, the following observations can be made:

- Series circuit resistance reduces the device avalanche stress.

- A supply voltage approaching the device avalanche voltage increases t<sub>AV</sub>. Stress increases and the allowable avalanche current is reduced.

- When the supply voltage is zero, t<sub>AV</sub> varies inversely with the device avalanche voltage.

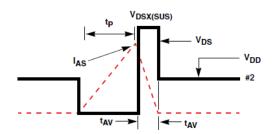

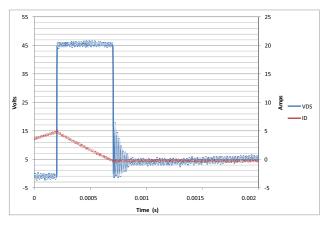

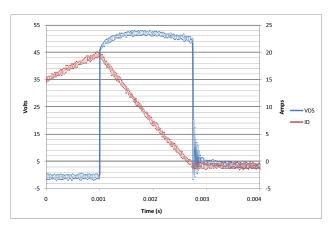

The equations of Table 1 presume that the device avalanche voltage is constant. In an actual test, it is not. Experiments have been performed using devices with similar low-current room temperature BVpss readings. Vdd, L, R, Ias, and tav were carefully measured and the avalanche breakdown was calculated. All units yielded similar results. The effective avalanche voltage in all cases was 30% larger than BVpss when avalanched near rated capability (see Figure 5 and Figure 6). Vdsx(sus) is the effective voltage referenced in the JEDEC test method<sup>[2]</sup>. onsemi has chosen to list Vdsx(sus) in the tav equations on the rating curves for these devices as 1.3 times the rated low-current breakdown voltage.

- IAS peak current reached during device avalanche

- t<sub>AV</sub> time duration of device avalanche

- V<sub>DSX(SUS)</sub> effective (constant) device breakdown voltage during avalanche (approximately 1.3 · BV<sub>DSS</sub>)

- L Inductance

- R Resistance

- V<sub>DD</sub> output circuit supply voltage

- K (V<sub>DSX(SUS)</sub>-V<sub>DD</sub>)/(I<sub>AS</sub>R) ratio of the inductor plus the resistor voltage to the resistor voltage drop

Figure 3. UIS Test Circuit

Figure 4. UIS Waveforms

**Table 1. MATHEMATICAL ANALYSIS**

| Row# | Circuit<br>Condition |   | Time in Avalanche                                           | Avalanche Energy                        | Average Avalanche Power                                  |

|------|----------------------|---|-------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------|

|      | $V_{DD}$             | R | t <sub>AV</sub>                                             | E <sub>AS</sub>                         | $P_{AS(AVE)} = (E_{AS}/t_{rep}), t_{rep \ge t_{AV}}$     |

| 1    | $V_{DD}$             | R | (L/R)In(1+1/K)                                              | $(LI_{AS}V_{DSX(SUS)}/R)[1-Kln(1+1/K)]$ | $[I_{AS}V_{DSX(SUS)}].[(1/ln(1+1/K))-K)(t_{AV}/t_{rep})$ |

| 2    | $V_{DD}$             | 0 | LI <sub>AS</sub> /(V <sub>DSX(SUS)</sub> -V <sub>DD</sub> ) | $LI_{AS}^2/[2(1-V_{DD}/V_{DSX(SUS)})]$  | $(I_{AS}V_{DSX(SUS)}/2)(t_{AV}/t_{rep})$                 |

| 3    | 0                    | 0 | LI <sub>AS</sub> /V <sub>DSX(SUS)</sub>                     | LI <sub>AS</sub> <sup>2</sup> /2        | $(I_{AS}V_{DSX(SUS)}/2)(t_{AV}/t_{rep})$                 |

Figure 5. FDB8444  $V_{DSX(SUS)}$ , L = 5 mH,  $I_{AS}$  = 5 A, Initial  $T_{.1}$  = 25°C

Figure 6.  $V_{DSX(SUS)}$ , L = 5 mH,  $I_{AS}$  = 20 A, Initial  $T_{.1}$  = 25°C

Single–point avalanche–energy ratings at  $T_J = 25^{\circ}\mathrm{C}$  are not application specific nor are they useful for comparing similar devices offered by different manufacturers. To highlight the difficulty, a hypothetical example is in order.

## Application Example: Operating Margin for a Single-Pulse UIS Event

Determine the safe single-pulse avalanche current for an application that uses L=1 mH and  $V_{DD}=0$  V for **onsemi**'s FDB8444. Datasheet information is as follows (reference the UIS rating curve in Figure 2):

$E_{AS} = 307 \text{ mJ Maximum}$

$T_J = 25^{\circ}C$  (Starting)

$BV_{DSS} = 40 \text{ V}$

$L = 200 \, \mu H$

$V_{DD} = 0 V$  during avalanche

$I_{AS}$  = 56 A (Effective  $I_{AS}$  calculates to 55.4 A because  $R \neq 0 \Omega$  and a non-constant  $V_{DSX(SUS)}$  as a result of self-heating, (see Figure 5)

$t_{AV} = 477 \,\mu s$  (calculated using effective  $I_{AS} = 55.4 \,A$ )

Only a starting junction temperature of 25°C can be assessed. For a starting temperature other than that described in **onsemi** datasheets (usually 25°C and 150°C), additional analysis is required to extrapolate the duration and amplitude limits of the avalanche event.

#### Parasitic Bipolar Turn-on

Assuming the parasitic bipolar transistor is suppressed, it need not be considered for state-of-the-art devices.

#### **Constant Energy**

To use the relationship  $E_{AS} = L \ I^2_{AS}/(2(1-V_{DD}/V_{DSX(SUS)}))$ , use  $V_{DSX(SUS)} = 1.3 \cdot BV_{DSS}$ . For a constant energy of 307 mJ, the predicted safe  $I_{AS}$  (for L=1 mH) would equal 24.8 A ( $t_{AV}=477~\mu s$ ). This data point is located beneath the 25°C Figure 2 UIS rating curve.

#### Thermal ( $I_{AS}^2$ t<sub>AV</sub> = Constant)

#### $T_{JS} = 25^{\circ}C$

Again using  $V_{DSX(SUS)} = 1.3 \cdot BV_{DSS}$  in the relationship  $t_{AV} = L I_{AS}/(V_{DSX(SUS)} - V_{DD})$  for the intended application (L = 1 mH), predicted  $t_{AV}$  and  $I_{AS}$  are:

$I_{AS}^3 = 0.654 (V_{DSX(SUS)} - V_{DD})/L$

where:

L = 1 mH

$V_{DD} = 0 V$

$V_{DSX(SUS)} = 1.3 \cdot BV_{DSS}$

$t_{AV} = 623 \mu s$ , and

$I_{AS} = 32.4 A.$

It is a simple matter to establish the safe avalanche current for an **onsemi** POWERTRENCH<sup>®</sup> devise when supplied with rating curves.

#### $T_{JS} = 150$ °C

Datasheet  $I^2_{AS}$   $t_{AV} = 0.25$ . At the maximum rated starting junction temperature,  $t_{AV} = 452~\mu s$  and  $I_{AS} = 23.5~A$ . The safe avalanche current for any starting  $T_J$  can be established from the **onsemi** rating curves. Stoltenburg<sup>[3]</sup> showed that for avalanche–rated devices, avalanche failure was a linear function of starting  $T_J$  for a fixed inductor. This is also true for a constant  $t_{AV}$ . It is a simple matter then to establish the  $I^2_{AS}$   $t_{AV}$  = constant for any starting  $T_J$ .  $T_{JS} = 100^{\circ} C$  is a common operating temperature for a practical application.

Entering the **onsemi** curves at any convenient  $t_{AV}$ , in this case; 0.6 ms; the  $I_{AS}$  temperature sensitivity is  $(20 \text{ A}-33 \text{ A})/+125^{\circ}\text{C}$  or -104 mA/°C. Therefore,  $I_{AS} = 33-(0.104)(100^{\circ}\text{C}-25^{\circ}\text{C}) = 25.2 \text{ A}$  for  $t_{AV} = 0.6 \text{ ms}$  and  $I_{AS}^2 t_{AV} = 0.381$ .

For the example application where L=1 mH, using  $I^3_{AS}=0.381$  ( $V_{DSX(SUS)}-V_{DD}$ )/L; a maximum avalanche current of  $I_{AS}=27.1$  A for a starting  $T_J=100^{\circ}$ C.

#### AN-7514/D

#### **Related Datasheets**

For onsemi documents available on the internet, see website <a href="https://www.onsemi.com">https://www.onsemi.com</a>

- [1] D. L. Blackburn, "Power MOSFET Failure Revisited", Proc. 1988 IEEE Power Electronics Specialists Conference, pp 681–688, April 1988.

- [2] "Single-Pulse Unclamped Inductive Switching (UIS) Avalanche Test Method", JEDEC Standard JESD24-5, October 2002.

- [3] Rodney R. Stoltenburg, "Boundary of Power–MOSFET, Unclamped Inductive–Switching (UIS) Avalanche–Current Capability", Proc. 1989 Applied Power Electronics Conference, pp 359–364, March 1989.

- [4] Miroslav Glogolja, "Ruggedness Test-Claims Demand Another Careful Look", Powertechnics Magazine, pp 23–28, July 1986.

- [5] S. K. Ghandhi, "Semiconductor Power Devices", John Wiley & Sons, New York, pp 15–29, 1977.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales