**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# Terminations for Advanced CMOS Logic

# Introduction

Advanced CMOS logic such as ON Semiconductor's FACT<sup>®</sup> logic, has extended CMOS performance to the level of advanced bipolar technologies. While high-performance design rules that are currently utilized for bipolar designs are also applicable to CMOS, power consumption becomes a new area of concern in high-performance system designs.

One advantage of using advanced CMOS logic is its low power consumption. However careless circuit design can increase power consumption, possibly by several orders of magnitude. A simple FACT gate typically consumes  $625 \,\mu$ W/MHz of power; at 10 MHz, this translates to  $6.25 \,\mu$ W. A 50 W parallel termination on the line will use over 361 mW with a 50% duty cycle.

The use of high-performance system board design guidelines is important when designing with advanced CMOS families. Because of advanced CMOS logic edge rates (less than 3 ns - 4 ns), many signal traces will exhibit transmission line characteristics.

A PCB trace begins to act as a transmission line when the propagation delay  $(t_{PD})$  across the trace approaches one third of the driver's edge rate. For advanced CMOS, lines as short as 6 to 8 inches may exhibit these effects. This rule encompasses many traces on a standard PCB. With older CMOS technologies which have lower edge rates, this critical length is much longer: 18 inches for 74HC and 5 feet for CD4000 series and 74C devices. A transmission line terminating into a mismatched impedance could result in transient noise which adversely affects signal integrity.

The FACT family also features guaranteed line driving capability. The  $I_{OLD}$  /  $I_{OHD}$  specifications guarantee that a FACT device can drive incident wave voltage steps into line impedances as low as 50  $\Omega$ . The  $I_{OLD}$  specifications do not guarantee incident wave switching into bipolar level inputs since the input low thresholds are 500 mV to 850 mV lower than CMOS. Due to the relatively linear behavior of the outputs below 1 V, CMOS devices can drive incident voltages, adequate for bipolar inputs, into line impedances as low as 80  $\Omega$ . For line impedances lower than 80  $\Omega$ , termination can be used to provide adequate input levels.

# **ON Semiconductor®**

### www.onsemi.com

# **APPLICATION NOTE**

Thus besides reducing noise transients, terminations could also be used to interface between devices from different technologies.

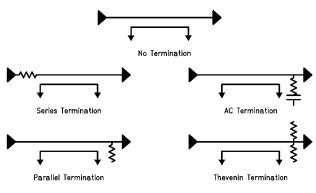

Five possible termination schemes are presented with their impact on power dissipation and noise reduction. Figure 1 illustrates these schemes.

Figure 1. Termination Schemes

# **No Termination**

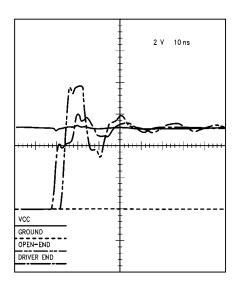

No termination is the lowest cost option and features the easiest design. For line lengths 8 inches or less, this is often the best choice. For lines longer than 8 inches, transmission line effects (line delays and ringing) may exist. Figure 2 illustrates the effect of a FACT device driving a 3-foot open-ended coaxial line. Clamp diodes at the inputs of most logic devices tend to reduce the ringing and overshoots. Often, these clamp diodes are sufficient to insure reliable system operation. Figure 3 illustrates the impact of these diodes on the same 3-foot coaxial line. However, it is not uncommon to find logic devices like DRAMs, D-to-A converters and PLDs, that have no input clamp diodes.

Figure 2. Transmission Line Effects FACT Driving 3 Foot Open-Ended Coax

Figure 3. Effects of Input Clamp Diodes FACT Driving FACT with No Termination

# **Parallel Termination**

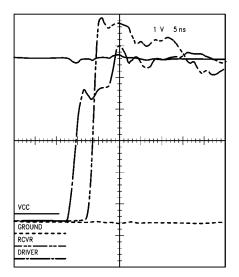

Parallel termination provides an AC and DC current path back to the power supply for switching currents. While it effectively reduces ringing (Figure 4), the DC path to ground or to  $V_{CC}$  will dissipate power. The power consumption for this type of a termination scheme has some important implications. For proper impedance matching the value of this terminating resistor should be equal to the characteristic impedance of the line.

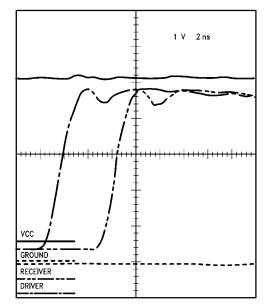

Figure 4. FACT Driving FACT with Parallel Termination

The DC component to the power consumption is a function of the signal duty cycle. Signals with lower duty cycles will dissipate less DC power. Since the load seen by the driving device is resistive, not capacitive, load capacitance does not affect power consumption. Therefore, parallel termination dissipates less AC power. Because of this lower AC power at high frequencies, parallel terminations may consume less power than no termination. Depending upon the load capacitance, signal duty cycle, and line impedance, this frequency can be as low as 40 MHz.

There are drawbacks associated with parallel termination. The maximum DC current allowed into or out of any FACT output is 50 mA. This limits the allowable resistor values to greater than 100  $\Omega$ . Even though this ringing may not be excessive, imperfect impedance matching may cause ringing on lines with an impedance less than 100  $\Omega$ . However, because the high–power dissipation of this termination scheme negates the advantages of advanced CMOS logic, this is not an intended advanced CMOS application.

Parallel termination tends to unbalance CMOS outputs. Using a resistor to ground, the CMOS device will achieve a 0.0 V output low voltage ( $V_{OL}$ ). But due to the high DC load in the logic HIGH state, the output high voltage ( $V_{OH}$ ) will be degraded (Figure 4). This degraded high level output will be above the input high voltage ( $V_{IH}$ ) of both CMOS and bipolar inputs due to the guaranteed dynamic current ( $V_{OHD}$ ) specifications (75 mA @ 3.85 V,  $V_{CC}$  = 5.5 V). This lower  $V_{OH}$  level may cause an increase in I<sub>CC</sub> if the driven device is CMOS; however, this increase should be minimal.

# **Thevenin Termination**

The venin termination is similar to parallel termination, except that both pull–up and pull–down resistors are used. Power consumptions are also similar for both of these schemes. The difference is that the DC power consumption is a function of duty cycle and resistor ratios. If the resistors are matched, DC power consumption is not dependent upon duty cycle. One advantage Thevenin termination has over parallel termination is that lines with impedances as low as 50  $\Omega$  can be terminated in their characteristic impedances. For proper impedance matching, the equivalent thevenin resistance should be the same as the line characteristic impedance.

Thevenin termination does not create unbalanced CMOS outputs, although it reduces the output swing (Figure 5). This limited output swing may increase current consumption in a driven CMOS device however this increase is minimal.

Figure 5. FACT Driving FACT with Thevenin Termination

Busses using Thevenin termination should not be left floating. A floating bus level is determined by the ratio of the resistors. If this level is close to any input threshold, output oscillations and  $I_{CC}$  increase may occur. If the bus must be left floating, the resistor ratio should be chosen so that an adequate noise margin is insured. The bus could be left floating by either turning off the driver or by placing the bus in a high impedance state.

Other terminations which do not introduce DC current paths may be more suitable to CMOS systems. These include series and AC parallel terminations.

# **Series Termination**

Series termination works by limiting the current that is put into a line. While other termination circuits dissipate extra power, series termination reduces power consumption and dissipates less energy than no termination. This is a recommended termination scheme for the FACT family because of its low power dissipation.

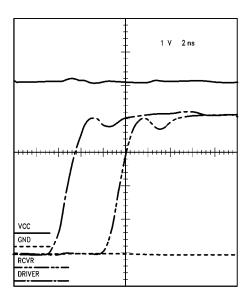

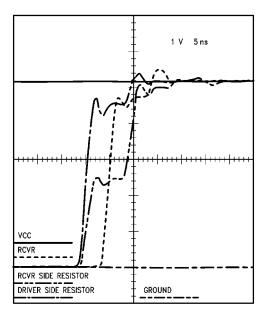

Series termination assumes that any voltage step driven into a transmission line will double at the receiver. Therefore, the initial voltage step driven into the line is one-half of the receiver input voltage. The resistor value can be computed by  $R_S = Z_O - R_D$ , where  $R_S$  is the resistor value,  $Z_O$  is the line impedance and  $R_D$  is the driver resistance. Figure 6 illustrates the waveforms associated with series termination.

Figure 6. FACT Driving FACT with Series Termination

While the device output produces a full output step, only half of that is driven into the line. At the receiver end, the edge doubles, thus recreating the full output swing. The initial step then reflects back, fixing the full output voltage applied on the entire line. A voltage plateau is created at the input to the line whose width will be twice the line t<sub>pd</sub>.

Series termination is well suited for lines with a single driver receiver pair. Series termination limits the initial voltage step, which offers several benefits: reduced power consumption and decreased cross-coupled radiated noise.

One possible drawback to series termination is that any other receiver located near the driver will see the voltage plateau. Because the plateau level may be very close to the typical CMOS threshold (50% of  $V_{CC}$ ), any such input could see multiple input switching. Combinatorial outputs may oscillate, or clocked inputs may experience multiple clocking.

One solution is to choose the resistor value that keeps the initial voltage step away from the input thresholds. Larger resistor values will require one or more reflections to settle out, while still maintaining valid  $V_{IN}$  levels at the inputs. Smaller values will generate overshoot and undershoot.

# **AC Parallel Termination**

AC Parallel termination is another technique which blocks the DC path to ground. A capacitor in series with the parallel termination resistor blocks the DC path, while maintaining the AC path. This is a highly recommended termination scheme for the FACT family because of its negligible DC power consumption.

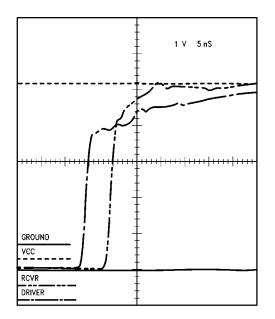

After the initial voltage step, the capacitor will charge up to the rail voltage at a rate determined by the RC time constant of the circuit (Figure 7).

Figure 7. FACT Driving FACT with AC Termination

The capacitor value needs to be carefully determined. If the RC time constant is too small, the RC circuit will act as an edge generator and will create overshooting and undershooting. While increasing the capacitor reduces overshoot, it also increases power consumption. As a rule, the RC time constant should be greater than 3 times the line delay.

When driving TTL-level inputs, the same threshold concerns arise as with no termination. The  $I_{OLD}$  current specifications guarantee incident wave switching into CMOS inputs on line impedances as low as 50  $\Omega$ . For TTL-level inputs, this minimum line impedance rises to 80  $\Omega$ . When the line impedance is less than 80  $\Omega$ , a termination value greater than the line impedance will increase the amplitude of the initial voltage step; this can be used to guarantee incident wave switching into both TTL and CMOS-level inputs. Large resistor values will cause ringing on the line, but the amplitude should be small and not present any problems.

At lower frequencies, this termination capacitance increases the total signal trace impedance; therefore, it also increases the slope of the power consumption curve. At higher frequencies, the capacitor is unable to fully charge or discharge, and the slope of the curve falls off. At very high frequencies, AC parallel termination acts like a parallel resistor tied to an intermediate voltage supply, with the voltage level determined by the signal duty cycle. The slope of the power consumption curve is dependent on  $C_{PD}$ (Power dissipation capacitance) of the device. The power crossover point between no termination and AC termination may be as low as 15 MHz, depending upon the system capacitive loading and the signals' duty cycle.

### Power Consumption

The use of one of these termination schemes will affect the power consumption of the system. Power consumption depends upon the circuit used, signal frequency, device and signal trace loads, signal duty cycle, system  $V_{CC}$  and component values.

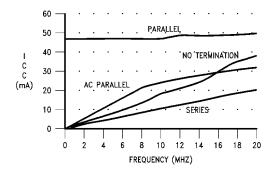

Figure 8 shows the power consumption of each type of termination circuit over a frequency range. For low frequency signals, termination circuits without DC components will usually use less power (no termination, series termination and AC parallel termination). At higher frequencies, parallel termination or AC termination may consume less power because of lower AC power consumption. The AC power consumption of these two termination schemes is a function of the device C<sub>PD</sub>, while the AC power consumption of the other termination schemes is a function of both the device CPD and the system capacitive loading ( $C_I$ ). The AC power consumption of AC parallel termination at low frequencies also includes the termination capacitance. The signal used for these curves has a 50% duty cycle. The DC power consumption of the parallel termination will drop as duty cycles drops. For very low duty cycle signals, this scheme may consume the least amount of power.

For low frequencies, the slope of the AC parallel termination curve is greater than any other. This is because it is a function of the device  $C_{PD}$ , the capacitive loading ( $C_L$ ), and the termination capacitance ( $C_T$ ). But at higher frequencies where the pulse width is less than the RC time constant, the slope drops off. At some frequency less than that of parallel termination, AC parallel termination will use less power than using no termination. At some higher frequency, this circuit uses less power than series termination.

#### Summary

With new advanced CMOS logic families, power consumption has become an important issue in high-performance systems. Because of the need to use termination, system designers need to be aware of how these circuits affect the power consumption of their systems. The power consumption of the termination scheme will vary, depending upon frequency, duty cycle, line impedance, loading and other factors (Figure 8).

Figure 8. Power Consumption

Power consumption is not the only concern when choosing a termination circuit. Part-count and board space are also important concerns. It is up to system designers to choose which, if any, termination circuit is best suited to their circuit. Table 1 shows the recommended values for the various termination schemes. It is highly recommended that the designer use these values as a starting point and adapt it for the most feasible and optimum results.

#### Table 1. RECOMMENDED TERMINATION VALUES

| Parallel:   | Resistor = Z <sub>O</sub>           |

|-------------|-------------------------------------|

| • Thevenin: | Resistor = 2 x Z <sub>O</sub>       |

| • AC:       | Resistor = Z <sub>O</sub>           |

|             | Capacitor = $C \ge \frac{3td}{Z_0}$ |

| Active:     | Resistor = $2 \times Z_0$           |

FACT is registered trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

ON Semiconductor and 💷 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="http://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights not the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

For additional information, please contact your local Sales Representative