Is Now Part of

OR NEW DESIGN

# **IN Semiconductor®**

# To k an more about CH Semiconductor, please visit our website at

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="mailto:www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild questions@onsemi.com">Fairchild questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor referses, employees, subsidiaries, and lisofficers, and designed, intended, or authorized for uses, and reasonable attorney fees arising out or, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an eg

January 2005 Revised August 2005

# USB1T1105A **Universal Serial Bus Peripheral Transceiver** with Voltage Regulator

### **General Description**

The USB1T1105A is an Universal Serial Bus Specification Rev 2.0 compliant transceiver. The device provides an USB interface for Full-Speed (12Mbit/s) USB applications. The USB1T1105A provides excellent flexibility, allowing differential and single ended inputs while an integrated voltage regulator sets the I/O level to 1.65V to 3.6V. Utilizing an integrated 5.0V to 3.3V voltage regulator, the part can be powered directly from the USB host (V<sub>BUS</sub>) to minimize the power consumed from the local sources while used in devices with low supply voltages.

The USB1T1105A provides 15kV ESD protection on the USB bus pins (D+/D-). This eliminates the need for any external ESD devices while providing excellent protection to larger and more expensive ASICs and USB controllers.

### **Features**

- Complies with Universal Serial Bus Specification 2.0

- Integrated 5V to 3.3V voltage required or top wering VBus

speed data rates

- Utilizes digital inputs and out its to ansmit ind receive USB cable data

- Supports full spee 2ML

- Ideal for por le elec nic

- 15kV co. ct F M ESE rotection on bus pins

- laat is pullinge 3

- ndu. vistan. ..d HBCC inotprint is RMATH

### Ap, 'ications

- Cell phone FDA

- 🖪 Ligital can era

- MΓ3

## Ordering ( Jae:

**USB1T1105A**

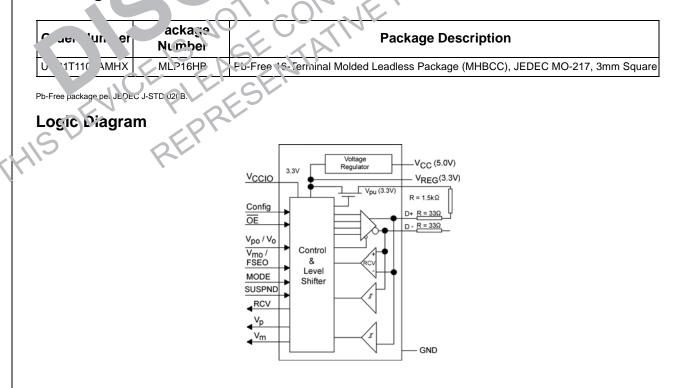

### **Connection Diagram**

# **Terminal Descriptions**

| Terminal Terminal I/O |                                  |              |                                                                                                                                                                                                                                                      |  |  |  |

|-----------------------|----------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Terminal<br>Number    | Terminal<br>Name                 | I/O          | Termina Desci tio.                                                                                                                                                                                                                                   |  |  |  |

| 1                     | ŌĒ                               | Ι            | Output Enable: Active LOW is to transmit data on the bus. When not active the transceive in the mode (CN OS level is relative to V <sub>CCIO</sub> )                                                                                                 |  |  |  |

| 2                     | RCV                              | 0            | Receive Data Over to Non-erte CMOS level on tput for USP thiferential inplit (CMOS output level is state to V <sub>CC</sub> . Driven LO V when SUSP's 's fillGH' RCV output is stable indirectived during SE0 condition.                             |  |  |  |

| 3                     | V <sub>p</sub>                   | 0            | Sing receive output V <sub>P</sub> (CMOS lovel relative to V <sub>CCIC</sub> ):<br>Used e. detection of SEO, error conditions, speed of connected device;<br>D. In TH when no supply connected to V <sub>CC</sub> and V <sub>REG</sub> .             |  |  |  |

| 4                     | V <sub>m</sub>                   | 0            | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                |  |  |  |

| 5                     | S' ND                            |              | Suspend:<br>Enables a low covier state (CMGS level is relative to V <sub>CCIO</sub> ). While the SUSPND pin is<br>octive (HIGH) it will drive the RCV pin to logic "0" state.                                                                        |  |  |  |

|                       | MODE                             | SNO          | MODE input (CMCS 'evol is relative to V <sub>CCIO</sub> ). A HIGH selects the differential input MODE (V <sub>po</sub> , V <sub>nc</sub> ) whereas a LOW enables the single-ended MODE (V <sub>o</sub> , V <sub>FSEO</sub> ) see Table 2 and Table 3 |  |  |  |

| 7                     | 7000                             |              | Surply Volage for digital I/O pins (1.65V to 3.6V):<br>when not connected the D+ and D- pins are in 3-STATE. This supply bus is totally<br>independent of $V_{CC}$ (5V) and $V_{REG}$ (3.3V).                                                        |  |  |  |

| Ø                     | NC                               | N°           |                                                                                                                                                                                                                                                      |  |  |  |

| 10, 9                 | D+, D-                           | <u> 41/O</u> | Data +, Data -: Differential data bus conforming to the USB standard.                                                                                                                                                                                |  |  |  |

| 11                    | V <sub>po</sub> / V <sub>c</sub> |              | Driver Data Input (CMOS level is relative to $V_{\mbox{CCIO}}$ ); Schmitt trigger input; see Table 2 and Table 3                                                                                                                                     |  |  |  |

| 12                    | $V_{mo}$ / $F_{SEO}$             | Ι            | Driver Data Input (CMOS level is relative to $V_{\mbox{CCIO}}$ ); Schmitt trigger input; see Table 2 and Table 3                                                                                                                                     |  |  |  |

| 13                    | V <sub>REG</sub> (3.3V)          |              | Internal Regulator Option:<br>Regulated supply output voltage (3.0V to 3.6V) during 5V operation;<br>decoupling capacitor of at least 0.1 $\mu$ F is required.                                                                                       |  |  |  |

| 14                    | V <sub>CC</sub> (5.0V)           |              | Internal Regulator Option:<br>Used as supply voltage input (4.0V to 5.5V); can be connected directly to USB line<br>Vbus.                                                                                                                            |  |  |  |

USB1T1105A

| Terminal<br>Number | Terminal<br>Name       | I/O | Terminal Description                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                 | V <sub>PU</sub> (3.3V) |     | Pull-up Supply Voltage $(3.3V \pm 10\%)$ :<br>Connect an external $1.5k\Omega$ resistor on D+ (FS data rate);<br>Pin function is controlled by Config input pin:<br>Config = LOW – V <sub>PU</sub> (3.3V) is floating (High Impedance) for zero pull-up current.<br>Config = HIGH – V <sub>PU</sub> (3.3V) = 3.3V; internally connected to V <sub>REG</sub> (3.3V). |

| 16                 | Config                 | Ι   | USB connect or disconnect software control input. Configures 3.3V to external 1.5k $\Omega$ resistor on D+ when HIGH.                                                                                                                                                                                                                                               |

| Exposed<br>Diepad  | GND                    | GND | GND supply down bonded to exposed diepad to be connected to the PCB GND.                                                                                                                                                                                                                                                                                            |

### **Functional Description**

The USB1T1105A transceiver is designed to convert CMOS data into USB differential bus signal levels and to convert USB differential bus signal to CMOS data.

To minimize EMI and noise the outputs are edge rate controlled with the rise and fall times controlled and defined for full speed data rates. The rise, fall times are balanced between the differential pins to minimize skew.

Table 1 describes the specific pin functionality election. Collig

2, Table 3, and Table 4

Scribe he s, for the s, for the state of the state

The USB1T11 A also s the collity of various power supply configuration to supply t mixed voltage supply applications (see Table and wer upply Configurations and Options for deta task. tions.

### **Functional Tables**

|        |    |                     | T∕ BL⊂ 1             | nction lect                                                       |

|--------|----|---------------------|----------------------|-------------------------------------------------------------------|

| SUSPND | OE | D+, D-              | ۲С۷                  | V Vm Function                                                     |

| L      | L  | Drivin<br>Rec /ing  | rtive                | Active Normal Oriving<br>(Differential Receiver Active)           |

| L      | н  | Rec ring<br>(Not.   | Active               | Active Receiving                                                  |

| Н      | L  | E ring              | Inactive<br>(Note 2) | Antive Driving during Suspend<br>(Differential Receiver Inactive) |

| Н      |    | 3-STATE<br>(Ncte 1) | Inacuve<br>(Note 2)  | Active Low Power State                                            |

1: Signa (els) notion of connection and/or poll-up/pull-down resistor ?.

Not. For SI PND = HIG I mode the differential receiver is incluse ind the output RCV output is forced LOW. The out-of-suspend signaling (K) is detected via the singleended or outputs of the V<sub>1</sub> and V<sub>m</sub> pins.

TAE (F 2. Driver Function ( $\overline{OE} = L$ ) using Differential Input Interface Mode Pin = H

|              | V <sub>mo</sub> | V <sub>po</sub> | Data                 |

|--------------|-----------------|-----------------|----------------------|

| 1            | S <sup>L</sup>  | L               | SE0 (Note 3)         |

| <pre>N</pre> | L               | Н               | Differential Logic 1 |

|              | Н               | L               | Differential Logic 0 |

|              | Н               | Н               | Illegal State        |

Note 3: SE0 = Single Ended Zero

### TABLE 3. Driver Function ( $\overline{OE} = L$ ) using Single-ended Input Interface Mode Pin = L

| FSE0 | Vo | Data                 |

|------|----|----------------------|

| L    | L  | Differential Logic 0 |

| L    | Н  | Differential Logic 1 |

| Н    | L  | SE0 (Note 4)         |

| Н    | Н  | SE0 (Note 4)         |

Note 4: SE0 = Single Ended Zero

TABLE 4. Receiver Function ( $\overline{OE} = H$ )

| D+, D-               | RCV | V <sub>p</sub> | V <sub>m</sub> |

|----------------------|-----|----------------|----------------|

| Differential Logic 1 | Н   | Н              | L              |

| Differential Logic 0 | L   | L              | Н              |

| SE0                  | Х   | L              | L              |

| Sharing Mode         | L   | Н              | Н              |

X = Don't Care

### **Power Supply Configurations and Options**

The three modes of power supply operation are:

- Normal Mode: Regulated Output and Regulator Bypass

- Regulated Output: V<sub>CCIO</sub> is connected and V<sub>CC</sub> (5.0) is connected to 5V (4.0V to 5.5V) and the internal voltage regulator then produces 3.3V for the USB connections.

- 2. Internal Regulator Bypass Mode:  $V_{CCIO}$  is connected and both  $V_{CC}(5.5)$  and  $V_{REG}(3.3)$  are connected to a 3.3V source (3.0V to 3.6V).

In both cases for normal mode the  $V_{CCIO}$  is an independent voltage source (1.65V to 3.6V) that is a function of the e<sup>v</sup> nal circuit configuration.

• Sharing Mode:  $V_{CCIO}$  is only supply connected.  $V_{c}$  and  $V_{REG}$  are not connected. In this mode the D+ c pin are

3-STATE and the USB1T1105A a" is explanal signals up to 3.6V to share the D+ and D- bus is. Interplay the circuit y limits leakage from D+ ar is D- pin 'maxim m 10  $\mu$ A) and V<sub>CCIO</sub> such that device is in ' is point uspended's state. Terminals Vbusme and is are force a LOW as a hindication of this mode v. VL more using ignared during this state.

• Disable In the: The indicate of the connected v<sub>CC</sub> is connected, or  $V_{L} \rightarrow V_{K}$ , are the connected 0.4 to 3.3V in this mode D+ and D- e to TE and  $V_{PU}$  is HIGH Impedance (switch is rine off). The USE171105A allow, external signals up to 5.4 to have the D+ and D- birs in estimation of the circuitry lim. leakage from D+ and D- technicals (maximum 10µA).

summary of the Supply Contigurations is described in Table 5.

|                                                                                                      |                             | Power Supriy                    | Mode Configuration                 |                                                                              |

|------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|------------------------------------|------------------------------------------------------------------------------|

| Pins                                                                                                 | harir                       | Disable                         | Normal<br>(Regulated Output)       | Normal<br>(Regulator Bypass)                                                 |

| V <sub>C</sub><br>(5V)                                                                               | < 3.6V                      | Connected<br>to 5V Spurce       | Connected to 5V Source             | Connected to V <sub>REG</sub> (3.3V)<br>[max drop of 0.3V]<br>(2.7V to 3.6V) |

| V <sub>REG</sub> (3V)                                                                                | Pulled LOW<br>Regulator OFF | 3 3V 300 μA<br>Regulated Output | 3.3V, 300 μA<br>Regulated Output   | Connected<br>to 3.3V Source                                                  |

| Vccio                                                                                                | 1.65% is 3.6% Source        | Not Connected                   | 1.65V to 3.6V Source               | 1.65V to 3.6V Source                                                         |

| V <sub>⊵U</sub> (?.3V)                                                                               | 3-STATE (O'f)               | 3-STATE (Off)                   | 3.3V Available if<br>Config = HIGH | 3.3V Available if<br>Config = HIGH                                           |

| D+, D-                                                                                               | 2-STATE                     | 3-STATE                         | Function of Mode Set Up            | Function of Mode Set Up                                                      |

| V <sub>p</sub> , V <sub>m</sub>                                                                      | Н                           | Invalid                         | Function of Mode Set Up            | Function of Mode Set Up                                                      |

| RCV                                                                                                  | L                           | Invalid                         | Function of Mode Set Up            | Function of Mode Set Up                                                      |

| OE, SUSPND,<br>Config, V <sub>po</sub> /V <sub>o</sub> ,<br>V <sub>mo</sub> /F <sub>SEO</sub> , MODE | Hi-Z                        | Hi-Z                            | Function of Mode Set Up            |                                                                              |

### TABLE . Perer Supply Configuration Options

Note 5: Hi-Z or forced LOW.

**USB1T1105A**

| Absolute Maximum Ratir                          |                                      | Recommended Operation                                                                                   | ng Conditions                        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|

| Supply Voltage (V <sub>CC</sub> )(5V)           | -0.5V to +6.0V                       | DC Supply Voltage V <sub>CC</sub> (5V)                                                                  | 4.0V to 5.5V                         |

| I/O Supply Voltage (V <sub>CCIO</sub> )         | -0.5V to $+4.6V$                     | I/O DC Voltage V <sub>CCIO</sub>                                                                        | 1.65V to 3.6V                        |

| Latch-up Current (I <sub>LU</sub> )             |                                      | DC Input Voltage Range (V <sub>I</sub> )                                                                | 0V to V <sub>CCIO</sub> + 0.5V       |

| $V_{I} = -1.8V$ to +5.4V                        | 150 mA                               | DC Input Range for AI/O (V <sub>IA/O</sub> )                                                            | 0V to 3.6V                           |

| DC Input Current (I <sub>IK</sub> )             |                                      | Pins D+ and D-                                                                                          | 0V to 3.6V                           |

| V <sub>1</sub> < 0                              | –18 mA                               | Operating Ambient Temperature                                                                           |                                      |

| DC Input Voltage (V <sub>I</sub> )              |                                      | (T <sub>AMB</sub> )                                                                                     | -40°C to +85°C                       |

| (Note 7)                                        | -0.5V to V <sub>CCIO</sub><br>+0.5V  |                                                                                                         |                                      |

| DC Output Diode Current (I <sub>OK</sub> )      |                                      |                                                                                                         |                                      |

| $V_{O} > V_{CC}$ or $V_{O} < 0$                 | ±18 mA                               |                                                                                                         |                                      |

| DC Output Voltage (V <sub>O</sub> )             |                                      |                                                                                                         |                                      |

| (Note 7)                                        | –0.5V to V <sub>CCIO</sub> +<br>0.5V |                                                                                                         | NEW DES                              |

| Output Source or Sink Current (I <sub>O</sub> ) |                                      |                                                                                                         | IE V                                 |

| $V_{O} = 0$ to $V_{CC}$                         |                                      |                                                                                                         |                                      |

| Current for D+, D– Pins                         | ±12 mA                               |                                                                                                         |                                      |

| Current for RCV, $V_m/V_p$                      | ±12 m                                |                                                                                                         |                                      |

| DC V <sub>CC</sub> or GND Current               |                                      | NDEDFORS                                                                                                |                                      |

| (I <sub>CC</sub> , I <sub>GND</sub> )           | ±; ∖mA                               |                                                                                                         | Vb,                                  |

| ESD Immunity Voltage (V <sub>ESD</sub> );       |                                      | CALIK 2                                                                                                 |                                      |

| Contact HBM                                     |                                      | Note 6: The Absulute Maximum Ratings are those                                                          | values beyond which the safety of    |

| Pins D+, D–, and GND                            | 15k∖                                 | the device call not be guaranteed. The device sho<br>The parametric values defined in the Electrical Ch | uld not be operated at these limits. |

| All Other Pins                                  | 2.5k\                                | teed at the absolute maximum rating. The "Rec                                                           | ommended Operating Conditions"       |

| Storage Temperature (T <sub>S1</sub>            | −40°C †J + 125°C                     | table will define the conditions for actual device op                                                   |                                      |

| Power Dissipat (PTOT)                           | 1KUNI                                | Note 7: O Abrol <sup>1</sup> te Maximum Rating must be obs                                              | served.                              |

| I <sub>CC</sub> (5V,                            | 48 mW                                |                                                                                                         |                                      |

|                                                 | 9 m/v (                              | //                                                                                                      |                                      |

**D** Elev rical Characteristics (Supply Plas) Over reconded range of rupply voltage and operating free Virtual temperature (unless otherwise noted).  $V_{CC}$  (5  $_{J}$  = 4.0V to 5.5V or  $V_{RFG}$  (3.5V) = 3.0V to 5.6V,  $V_{CCIO}$  = 1.65V to 3.6V

|                         |                                                |                                                      |                  | Limits         |           |       |

|-------------------------|------------------------------------------------|------------------------------------------------------|------------------|----------------|-----------|-------|

| દvmt ol                 | Parem.ste:                                     | Conditions                                           |                  | -40°C to +85°C |           | Units |

| <b>D</b>                | 0E                                             |                                                      | Min              | Тур Мах        |           |       |

| V <sub>REG</sub> (3.3V) | Regulated S oply Output                        | Internal Regulator Option;                           | 3.0              | 3.3            | 3.6       | v     |

|                         |                                                | $I_{LOAD} \le 300 \ \mu A$                           | (Note 8)(Note 9) |                |           | v     |

| Icc                     | Operating Supply Current (V <sub>CC</sub> 5.0) | Transmitting and Receiving at                        |                  | 4.0            | 8.0       | mA    |

|                         |                                                | 12 Mbits/s; $C_{LOAD}$ = 50 pF (D+, D-)              |                  | (Note 10)      |           | mA    |

| I <sub>CCIO</sub>       | I/O Operating Supply Current                   | Transmitting and Receiving at                        |                  | 1.0            | 2.0       | mA    |

|                         |                                                | 12 Mbits/s                                           |                  | (Note 10)      |           | mA    |

| I <sub>CC (IDLE)</sub>  | Supply Current during                          | IDLE: $V_{D+} \geq 2.7 V, \ V_{D-} \leq 0.3 V;$      |                  |                | 500       | ٨     |

|                         | FS IDLE and SE0 ( $V_{CC}$ 5.0)                | SE0: $V_{D+} \leq 0.3 V \text{, } V_{D-} \leq 0.3 V$ |                  |                | (Note 11) | μA    |

| ICCIO (STATIC)          | I/O Static Supply Current                      | IDLE, SUSPND or SE0                                  |                  |                | 20.0      | μA    |

| I <sub>CC(SUSPND)</sub> | Suspend Supply Current                         | SUSPND = HIGH                                        |                  |                | 25.0      |       |

|                         | USB1T1105A                                     | OE = HIGH                                            |                  |                | (Note 11) | μA    |

|                         |                                                | $V_m = V_p = OPEN$                                   |                  |                |           |       |

| ICCIO(SHARING)          | I/O Sharing Mode Supply Current                | V <sub>CC</sub> (5V) Not Connected                   |                  |                | 20.0      | μA    |

### DC Electrical Characteristics (Continued)

| Symbol               | Parameter                                     | Conditions                         |     | Units |      |      |

|----------------------|-----------------------------------------------|------------------------------------|-----|-------|------|------|

|                      |                                               |                                    | Min | Тур   | Max  |      |

| ID±(SHARING)         | Sharing Mode Load Current on                  | V <sub>CC</sub> (5V) Not Connected |     |       | 40.0 |      |

|                      | D+/D- Pins                                    | Config = LOW; $V_{D\pm}$ = 3.6V    |     |       | 10.0 | μΑ   |

| V <sub>CCTH</sub>    | V <sub>CC</sub> Threshold Detection Voltage   | $1.65V \leq V_{CCIO} \leq 3.6V$    |     |       |      |      |

|                      |                                               | Supply Lost                        |     |       | 3.6  | V    |

|                      |                                               | Supply Present                     | 4.1 |       |      |      |

| V <sub>CCHYS</sub>   | V <sub>CC</sub> Threshold Detection           | V <sub>CCIO</sub> = 1.8V           |     | 70.0  |      | mV   |

|                      | Hysteresis Voltage                            |                                    |     | 70.0  |      | IIIV |

| V <sub>CCIOTH</sub>  | V <sub>CCIO</sub> Threshold Detection Voltage | $2.7V \leq V_{REG} \leq 3.6V$      |     |       |      |      |

|                      |                                               | Supply Lost                        |     |       | 0.5  | v    |

|                      |                                               | Supply Present                     | 1.4 |       |      | S    |

| V <sub>CCIOHYS</sub> | V <sub>CCIO</sub> Threshold Detection         | V <sub>REG</sub> = 3.3V            |     |       |      |      |

|                      | Hysteresis Voltage                            |                                    |     |       |      |      |

### DC Electrical Characteristics (L Tuc.

| VCCIOHYS                          | V <sub>CCIO</sub> Threshold Detection                           | $V_{\text{REG}} = 3.3V$                                          |                                                     |          | m       |

|-----------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|----------|---------|

|                                   | Hysteresis Voltage                                              |                                                                  |                                                     |          | V       |

|                                   |                                                                 |                                                                  |                                                     |          |         |

| ote 8: I <sub>LOAD</sub> inclu    | ides the pull-up resistor current via pin V <sub>PI</sub>       | L                                                                |                                                     | NK.      |         |

| ote 9: The minim                  | um voltage in Suspend mode is 2.7V.                             |                                                                  | 2                                                   |          |         |

| ote 10: Not teste                 | d in production, value based on characteri                      | zation.                                                          |                                                     |          |         |

| ote 11: Excludes                  | any current from load and $\mathrm{V}_{\mathrm{PU}}$ current to | the 1.5k $\Omega$ resistor.                                      |                                                     |          | 17      |

| ote 12: Includes                  | current between $V_{pu}$ and the 1.5k internal                  | pull-up resistor.                                                | 0, 6                                                | emi      | )`      |

| ote 13: When V <sub>C</sub>       | $_{CIO}$ < 2.7V, minimum value for V <sub>REGTH</sub> = 2       | 2.0V for supp <sub>1</sub> resent cor. n.                        |                                                     |          |         |

|                                   |                                                                 |                                                                  |                                                     | Nr.      |         |

| C Elect                           | rical Characteristics                                           | د الد الد excludes J+, D- Pins)                                  | 110 02                                              | 14       |         |

| ver recommende                    | d range of supply voltage and or uting fr                       | e ten rature (unless of orwise noted). VCCIO                     | = 1.0V to 3.6V                                      |          |         |

|                                   |                                                                 |                                                                  | Lir                                                 | nits     |         |

| Symbol                            | Parameter                                                       | Ter & Cond. tions                                                | -40°C 1                                             | to +85°C | Units   |

|                                   |                                                                 |                                                                  | Min                                                 | Max      |         |

| Input Levels                      |                                                                 | <u> Rovinso</u>                                                  | 1                                                   | Г – Г    |         |

| VIL                               | it Voitage                                                      |                                                                  |                                                     | 0.3      | V       |

| VIH                               | HIGH Level ' ut Voltage                                         |                                                                  | 0.6*V <sub>CCIO</sub>                               |          | V       |

| V                                 | 'yste voltage P11 + P1∠                                         | $Pins V_{n0}/V_{1.0}, V_{CCIO} = 3.3V$                           | 0.3                                                 | 0.7      | V       |

| 'put Leve                         | 19.5                                                            |                                                                  | ·                                                   |          |         |

| V <sub>o.</sub>                   |                                                                 |                                                                  |                                                     | 0.4      | V       |

| ۷O.                               | LOW Level Output Voltage                                        | $D_L = 2 \text{ mA}$                                             |                                                     | 0.4      |         |

| vo.                               | LOW Level Output Voltage                                        | <sub>DL</sub> = 2 mA<br>I <sub>OL</sub> = 100 μA                 |                                                     | 0.15     |         |

|                                   | LOW Luve' Output Voltage                                        |                                                                  | V <sub>CCIO</sub> - 0.4                             | -        | V       |

|                                   | 10 V                                                            | I <sub>OL</sub> = 100 μA                                         | V <sub>CCIO</sub> - 0.4<br>V <sub>CCIO</sub> - 0.15 | -        | V       |

| V <sub>OH</sub>                   | HIGH Level Oursut Voitage                                       | l <sub>OL</sub> = 100 μA<br>l <sub>OH</sub> = 2 mA               |                                                     | -        | V       |

| V <sub>OH</sub><br>Loakayo Curren | HIGH Level Oursut Voitage                                       | l <sub>OL</sub> = 100 μA<br>l <sub>OH</sub> = 2 mA               |                                                     | -        | V<br>μA |

|                                   | HIGH Level Oursut Voitage                                       | $I_{OL} = 100 \ \mu A$ $I_{OH} = 2 \ m A$ $I_{OH} = 100 \ \mu A$ |                                                     | 0.15     |         |

Note 14: If  $V_{CCIO} \geq V_{REG}$  then leakage current will be higher than specified.

| Symbol            |                                  |                                         | I                      | _imits               |       |

|-------------------|----------------------------------|-----------------------------------------|------------------------|----------------------|-------|

|                   | Parameter                        | Test Condition                          | -40°                   | C to +85°C           | Units |

|                   |                                  |                                         | Min                    | Typ Max              |       |

| Input Levels – D  | Differential Receiver            |                                         |                        |                      |       |

| V <sub>DI</sub>   | Differential Input Sensitivity   | V <sub>I(D+)</sub> - V <sub>I(D-)</sub> | 0.2                    |                      | V     |

| V <sub>CM</sub>   | Differential Common Mode Voltage |                                         | 0.8                    | 2.5                  | V     |

|                   | Single-ended Receiver            |                                         |                        |                      |       |

| V <sub>IL</sub>   | LOW Level Input Voltage          |                                         |                        | 0.8                  | V     |

| V <sub>IH</sub>   | HIGH Level Input Voltage         |                                         | 2.0                    |                      | V     |

| V <sub>HYS</sub>  | Hysteresis Voltage               |                                         | 0.4                    | 0.7                  | V     |

| Output Levels     |                                  |                                         |                        |                      |       |

| V <sub>OL</sub>   | LOW Level Output Voltage         | $R_L = 1.5 k\Omega$ to 3.6V             |                        | 0.                   | VC    |

| V <sub>OH</sub>   | HIGH Level Output Voltage        | $R_L = 15k\Omega$ to GND                | 2.8 (No <sup>+</sup> ) |                      |       |

| Leakage Currer    |                                  |                                         |                        |                      |       |

|                   | Input Leakage Current Off State  | OE = H                                  |                        | ±1.0                 | μΑ    |

| Capacitance       | 1/0.0                            |                                         |                        |                      |       |

| C <sub>I/O</sub>  | I/O Capacitance                  | Pin to GND                              |                        | 20.0                 | pF    |

| Resistance        |                                  |                                         |                        |                      |       |

| Z <sub>DRV</sub>  | Driver Output Impedance          |                                         | 34.0                   | 41.0 44.0<br>lote 10 | 2     |

| Z <sub>IN</sub>   | Driver Input Impedance           |                                         | 10.0                   | SUIT                 | MΩ    |

| R <sub>SW</sub>   | Switch Resistance                |                                         |                        | 10.0                 | Ω     |

| V <sub>TERM</sub> | Termination Voltage              | Up am Port                              | :.0<br>(, rote 17)     | 3.6                  | V     |

|                   | vor je is z.7V in tu experimode. | s. CONCE                                |                        |                      |       |

|                   |                                  |                                         |                        |                      |       |

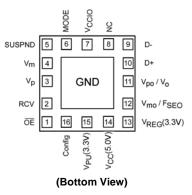

### AC Electrical Characteristics (A I/O Pins Full Speed)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC}$  = 4.0V to 5.5V or  $V_{REG}$  = 3.0V to 3.6V,  $V_{CCIO}$  = 1.65V to 3.6V,  $C_L$  = 50 pF;  $R_L$  = 1.5K on D+ to  $V_{PU}$

| Symbol           | Parameter                                    | Test Conditions                                           |       | Limits<br>-40°C to +85°C    |       |       |

|------------------|----------------------------------------------|-----------------------------------------------------------|-------|-----------------------------|-------|-------|

| Symbol           |                                              |                                                           |       |                             | Max   | Unit  |

| Driver Character | ristics                                      |                                                           | Min   | Тур                         | IVIdX |       |

| t <sub>FR</sub>  | Output Rise Time                             | C <sub>L</sub> = 50 – 125 pF                              | 4.0   |                             | 20.0  |       |

| Ϋ́́              |                                              | 10% to 90%                                                | 4.0   |                             | 20.0  | ns    |

| t <sub>FF</sub>  | Output Fall Time                             | Figures 1, 5                                              | 4.0   |                             | 20.0  | 113   |

| frfM             | Rise/Fall Time Match                         | t <sub>F</sub> / t <sub>R</sub> Excludes First Transition |       |                             | 2010  |       |

|                  |                                              | from Idle State                                           | 90.0  |                             | 111.1 | %     |

| / <sub>CRS</sub> | Output Signal Crossover Voltage              | Excludes First Transition from                            |       |                             |       |       |

| Note 19)         |                                              | Idle State see Waveform                                   | 1.3   |                             |       | V     |

| Driver Timing    |                                              |                                                           |       |                             |       |       |

| PLH              | Propagation Delay                            |                                                           |       |                             |       |       |

| ЧL               | $(V_p/V_{po}, V_m/V_{mo} \text{ to } D_+/D)$ | Figures 2, 5                                              |       |                             | 18.0  | ns ns |

| ΉZ               | Driver Disable Delay                         | Firmer 4.0                                                |       |                             |       |       |

| LZ               | (OE to D+/D-)                                | Figures 4, 6                                              |       | -                           | 15.0  | ns    |

| ZH               | Driver Enable Delay                          |                                                           |       | 2                           | 45.0  |       |

| ZL               | (OE to D+/D-)                                | Figures 4, 6                                              |       | $\mathcal{N}_{\mathcal{L}}$ | 15.0  | ns    |

| eceiver Timing   | - •<br>1                                     |                                                           |       | -                           |       | 14    |

| LH               | Propagation Delay (Diff)                     |                                                           |       | SC                          | 15.0  |       |

| ЧL               | (D+/D- to Rev)                               | Figu 3, 7                                                 |       |                             | 12.0  | ns    |

| ĽH               | Single Ended Receiver Propagation Delay      | , 0, re 7                                                 | .0.   |                             | 18.0  | ns    |

| ЧL               | (D+/D- to $V_p/V_{po}$ , $V_m/V_{mo}$ )      | ,5                                                        |       | ~~                          | 10.0  | 115   |

|                  | NCE IS NOT                                   | RECONTREFO                                                | 2112. |                             |       |       |

**USB1T1105A**

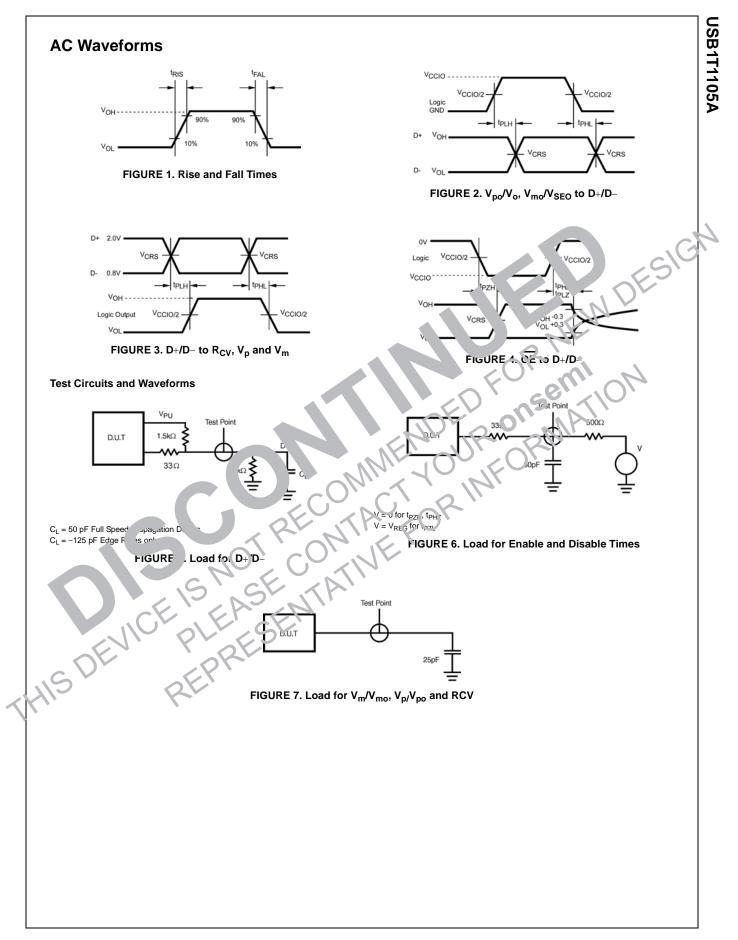

## **Tape and Reel Specification**

### Tape Format for MHBCC

| Package    | Таре               | Number    | Cavity | Cover Tape<br>Status |  |

|------------|--------------------|-----------|--------|----------------------|--|

| Designator | Section            | Cavities  | Status |                      |  |

|            | Leader (Start End) | 125 (typ) | Empty  | Sealed               |  |

| MHX        | Carrier            | 2500/3000 | Filled | Sealed               |  |

|            | Trailer (Hub End)  | 75 (typ)  | Empty  | Sealed               |  |

### TAPE DIMENSIONS inches (millimeters)

### DISCLAIMER

FOR NEW DESIGN FAIRCHILD SEMICONDUTER RESIDENT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IPROVER LITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY PRODUCTS HEREIN TO IPROVE RE LITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE A PLICAT IN OR USE OF ANY PROLUCTION CLICCTIC DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LUGE UPER FOR TAICHTS, NOR THE RIGHTS OF OTHERS.

### LIFE S VP. *`OLICY* **.**

STATE OF A CONTRACTION OF A CONTRACTION OF A CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES SYSTEM VITEOUT THE EXPRESS VIGITIEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION FAI

used h ein:

e sur ort devices or systems are devices or systems in , are intended for surgical implant into the body, or 1. whic (b) support or sustain life or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                                                  |  |  |

|--------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product develop-<br>ment. Specifications may change in any manner without notice.                                                                                     |  |  |

| Preliminary              | First Production       | This datasheet contains preliminary data, and supplementary data will<br>be published at a later date. Fairchild Semiconductor reserves the right<br>to make changes at any time without notice in order to improve design. |  |  |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                             |  |  |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been dis-<br>continued by Fairchild Semiconductor. The datasheet is printed for ref-<br>erence information only.                                               |  |  |

# **PRODUCT STATUS DEFINITIONS**

finition of torm

NOT RECONNENDED FOR MENDESIGN ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC