# **Test Procedure for the NCN4555GEVB**

12/27/2005

**Table 1: Required Equipment**

| Description        | Main Features                   | Example of Equipment (1)         | Qty. |

|--------------------|---------------------------------|----------------------------------|------|

| Regulated Power    | 200 mA DC current capability    | Tektronix PS2520G                | 2    |

| Supply             |                                 |                                  |      |

| Multimeter         |                                 | Keitley 2000 or 2001             | 2    |

| Sourcemeter        |                                 | Keitley 2400                     | 1    |

| Oscilloscope       | 500 MHz Bandwidth, four channel | Tektronix TDS744, 754 or 784 /   | 1    |

| ·                  | scope, min 1Mbit memory per     | TDS5054 series or Lecroy WR5060  |      |

|                    | channel (2)                     |                                  |      |

| Voltage probe      | 4 probes 500 MHz Bandwidth      | Tektronix or Lecroy              | 4    |

| Waveform generator | 10 MHz, CMOS logic signals      | Agilent 81104A 80 MHz or HP8110A | 1    |

|                    |                                 | 150 MHz 2 outputs                |      |

| SMB Cable          |                                 | External Clock Input             | 1    |

- 1. Equipment used in this test procedure.

- 2. Scope memory per channel is relevant because it offers better resolution. The scopes voltage probe should have a picofarad rating of between 11 and 30 pF.

### **Test Procedure:**

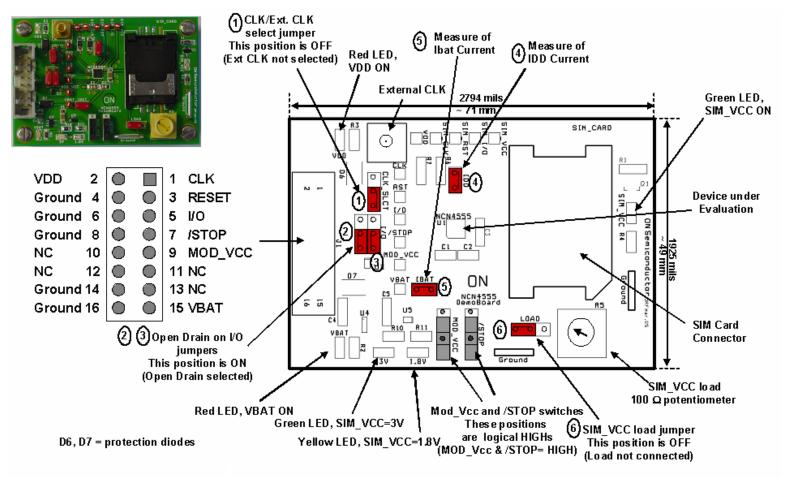

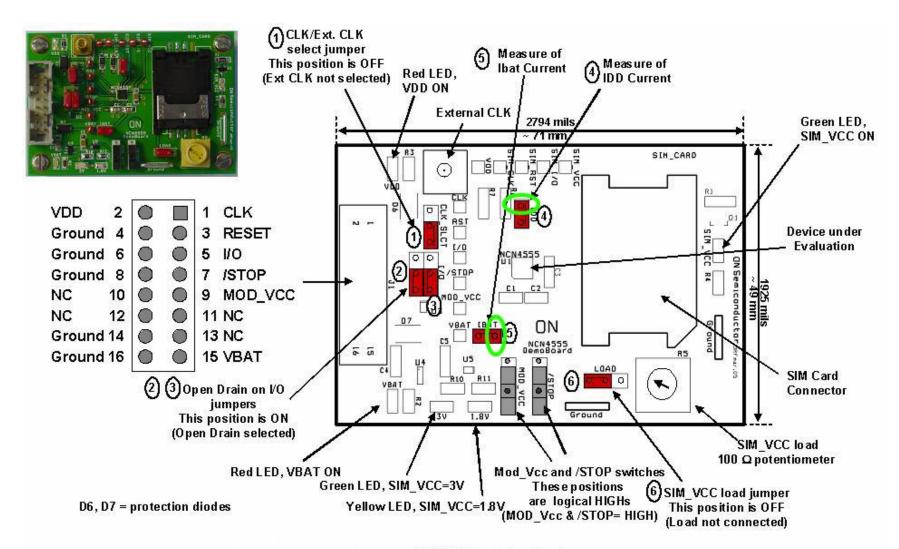

All the positions of switches given below refer strictly to the logical positions (High or Low) indicated Figure 1.

Figure 1: NCN4555 Evaluation Board Details

### 1. Setup NCN4555GEVB as follows (Figure 1):

- Turn-off the /STOP switch (position LOW).

- Set the MOD\_VCC switch also in a position LOW (SIM\_VCC = 1.8V).

- As a precaution, turn the 100  $\Omega$  potentiometer button fully to the right. The resistor output value is 100  $\Omega$  in this case.

- Jumpers:

**Jumper 1**: as shown in Figure 1, internal clock selected (through HE10 connector).

**Jumpers 2 and 3**: Jumpers in off position contrary to Figure 1 where the position is on. The Open Drain will then be unconnected and the I/O signal will be applied directly to the I/O NCN4555 input through the HE10 connector.

Jumper 4: plugged as in Figure 1.

**Jumper 5**: plugged as in Figure 1.

**Jumper 6**: 100  $\Omega$  potentiometer not connected, as in Figure 1.

### 2. Connect DC power supplies:

Two power supplies are used to bias the demo board.  $V_{BAT}$  is the input voltage of the DC/DC converter;  $V_{DD}$  is the "digital" power supply which biases the input stages of the NCN4555 device (control and signal inputs).  $V_{DD}$  and  $V_{BAT}$  must be connected to the board for correct operation.

- Connect the ground of the V<sub>DD</sub> & V<sub>BAT</sub> power supplies to the ground of the board (2 GND jumpers are available on the board)

- Connect the V<sub>DD</sub> power supply using the HE10 connector or the V<sub>DD</sub> test point.

- Connect the V<sub>BAT</sub> power supply through the HE10 connector or using the V<sub>BAT</sub> test point.

- Warning: If V<sub>DD</sub> and V<sub>BAT</sub> are applied through the HE10 connector the operating power supply voltages must be checked at the test points because of the voltage drops (~ 0.6 V / 0.7 V) introduced by the protection diodes D6 and D7.

- Power up  $V_{DD}$  in the range 1.8 V 5.5 V. The corresponding red LED light should be on.

- Power up  $V_{BAT}$  in the range 2.7 V 5.5 V. The corresponding red LED light should be on.

- The MOD\_V<sub>CC</sub> switch selects CRD-V<sub>CC</sub> 1.8 V or 3.0 V. When CRD\_V<sub>CC</sub> delivers 1.8 V the yellow LED is turned on and the MOD\_V<sub>CC</sub> switch is in the logical position LOW. When CRD\_V<sub>CC</sub> provides 3 V the green LED is turned on and the MOD\_V<sub>CC</sub> switch is HIGH.

By using the /STOP switch you select either the operating mode or the shutdown mode. In this last case, the SIM V<sub>CC</sub> voltage being null, the SIM\_V<sub>CC</sub> green LED is off.

### 3. Power Supply Section Evaluation:

With this evaluation board the following measurements can be made (see NCN4555 datasheet):

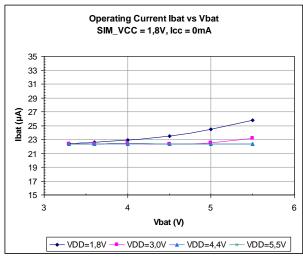

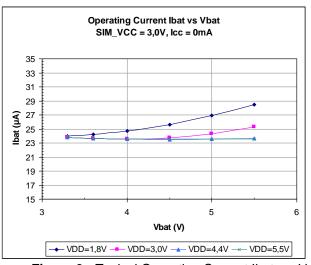

- 1. Operating and shutdown currents both on V<sub>DD</sub> and V<sub>BAT</sub>. See Figures 2 and 3

- 2. Under voltage Lockout (V<sub>DD</sub>)

- 3. Short Circuit Current (I<sub>SIM VCC SC</sub>)

- 4. Max I<sub>SIM VCC</sub> current. (Figure 4)

- 5. dc/dc Converter Turn-on and Turn-off times (Figures 6-9)

## Measurement implementation:

- The evaluation board is powered up at the V<sub>BAT</sub> and V<sub>DD</sub> voltages specified by the application.

- The switch /STOP is in position HIGH (operating mode)

- The switch MOD V<sub>CC</sub> is fixed according to the value required by the application

- Connect CLK and RST inputs to GND in order to avoid floating nodes.

- Connect the oscilloscope probe and the voltmeter as follow:

Analog ground (voltmeter and scope) Demo board's GROUND jumper.  $\rightarrow$ Channel 1: 1MΩ and voltmeter  $\rightarrow$

Test point SIM\_V<sub>CC</sub> (Smart card operating voltage).

- Connect the amp meter using jumpers 4 and 5 to measure I<sub>DD</sub> and I<sub>BAT</sub>.

- Using the SIM  $V_{CC}$  load jumper the user can connect the SIM  $V_{CC}$  output to a 100  $\Omega$  potentiometer and pull up the nominal I<sub>SIM VCC</sub> current to 50 mA. See figure on next page for current meter connection points. This potentiometer can also be used to measure the I<sub>SIM VCC</sub> Short Circuit and maximum allowable currents. See Figure 4.

NCN4555 Evaluation Board

**Figure 2:** Typical Operating Current lbat vs.  $V_{BAT}$  /  $SIM\_V_{CC} = 3$  V,  $I_{CC} = 0$  mA & Temp = 25°C

Figure 3: Typical Operating Current Ibat vs.  $V_{BAT}$  /  $SIM_{CC} = 3 \text{ V}$ ,  $I_{CC} = 0 \text{ mA } \& \text{Temp} = 25 ^{\circ}\text{C}$

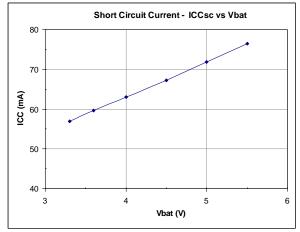

Figure 4: Short-Circuit Current / SIM\_V<sub>CC</sub> = 3 V (idem with 1.8 V), Temp = 25°C

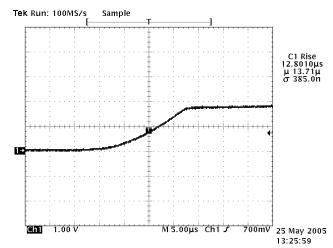

Figure 5: LDO's Turn-on time / SIM\_V<sub>CC</sub> = 1.8 V,  $V_{DD}$  = 1.8 V,  $V_{BAT}$  = 5.5 V & Temp = 25°C Tek Run: 25.0MS/s Sample

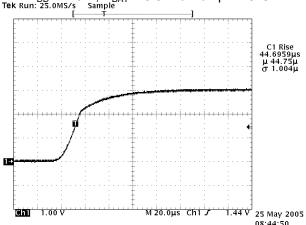

Figure 7: LDO's Turn-on time / SIM\_V<sub>CC</sub> = 3.0 V,  $V_{DD}$  = 1.8 V,  $V_{BAT}$  = 5.5 V & Temp = 25°C

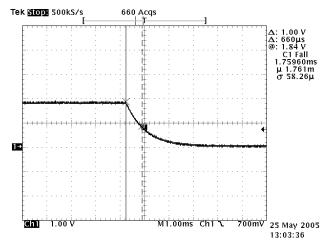

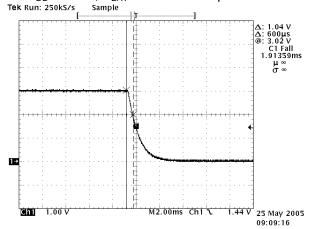

Figure 6: LDO's Turn-off time to 1 V / SIM\_V<sub>CC</sub> = 1.8 V,  $V_{DD}$  = 1.8 V,  $V_{BAT}$  = 5.5 V & Temp = 25°C

Figure 8: LDO's Turn-off time to 1V / SIM\_V<sub>CC</sub> = 3.0 V,  $V_{DD} = 1.8 \text{ V}, V_{BAT} = 5.5 \text{ V \& Temp} = 25^{\circ}\text{C}$

#### 4. Level Shifter Test:

Considering the level shifter function with this evaluation board the following measurements can be made.

- 1. Signal rise and fall times

- 2. Signal levels High and Low

- 3. Clock duty cycle

- 4. Frequency performance

## Measurement implementation:

- The evaluation board is powered up at VBAT and VDD voltages specified by the application.

- The switch /STOP is in position HIGH (operating mode).

- The switch MOD Vcc is fixed according to the value required by the application.

## SIM\_CLK signal:

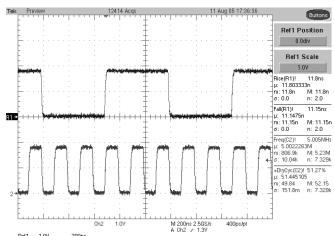

- CLK and SIM\_CLK are clock signals (Figures 9 and 10).

- Connect the RST input to the Ground or to VDD in order to avoid floating nodes.

- To evaluate SIM\_CLK a clock signal has to be connected either using the external clock input (SMB connector) or through the HE10 connector. The selection is done using the corresponding jumper (See Figure 1). The max clock frequency will be 5 MHz and the signal will have to accommodate the specifications provided in the datasheet; the clock signal is a 50% duty cycle square wave with a peak to peak of 3.3 V and an offset of 1.65 V (this will be the clock input used for all measurements). Note the rise and fall times for SIM\_CLK; they should be < 18 ns.</li>

### SIM\_RST signal:

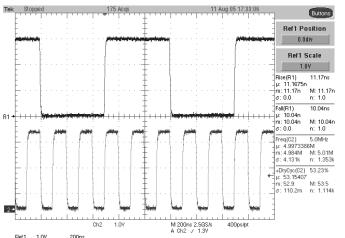

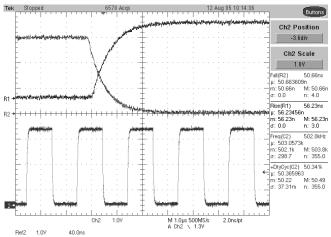

- RST and SIM\_RST are Boolean-like signals (Figures 11 and 12).

- Connect the CLK input to the Ground or to VDD in order to avoid floating nodes.

- To evaluate SIM\_RST, a RST signal accommodating the datasheet specifications will be applied either using the HE10 connector or through the corresponding test point.

## SIM\_I/O signal:

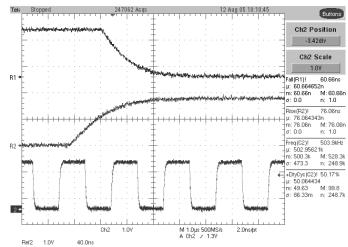

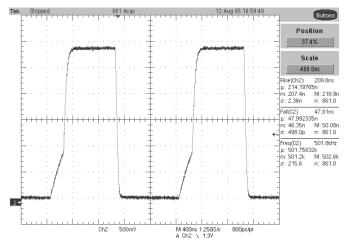

• I/O and SIM\_I/O are data signals (Figures 13 and 14).

• To evaluate SIM\_I/O, an I/O signal accommodating the datasheet specifications will be applied directly to the NCN4555 I/O device input (using either the HE10 connector or the corresponding test point and placing jumpers 2 and 3 in OFF position) or through the open drain circuit (using the pin third down on the right on the HE10 connector only and placing the I/O jumper in ON position). Typically 9600 bauds data are used through the I/O – SIM\_I/O bidirectional channel. The open drain condition on the input corresponds to a worst-case situation regarding the rise and fall times and frequency performance.

For the three different signals, connect the oscilloscope probes as follow, these signals can be considered independently (in that case be careful with the floating nodes) or together. SIM VCC will be connected to the oscilloscope's channel 1.

Analog ground

- → GROUND jumper on the demo board.

- Channel 2, Channel 3, Channel 4: 1 M $\Omega \rightarrow$

- Corresponding Test points

Switch MOD\_VCC to obtain alternatively 1.8 V CMOS logic levels or 3 V CMOS logic levels on SIM\_I/O, SIM\_CLK and SIM\_RST.

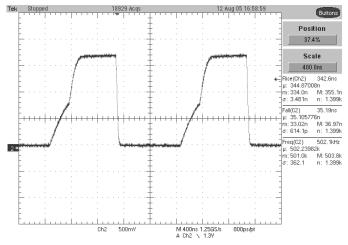

**Figure 9:** SIM\_CLK waveforms at 1 MHz (Top) and 5 MHz (Bottom) / SIM\_V<sub>CC</sub> = 1.8 V & C<sub>OUT</sub> > 33 pF

Figure 10: SIM\_CLK waveforms at 1 MHz (Top) and 5 MHz (Bottom) / SIM\_ $V_{CC}$  = 3.0 V &  $C_{OUT}$  > 33 pF

Figure 11: SIM\_RST waveforms / SIM\_V<sub>CC</sub> = 1.8 V &  $C_{OUT} > 33 \text{ pF}$

Figure 13: SIM\_I/O waveforms / on-board Open-Drain configuration, SIM\_ $V_{CC}$  =1.8 V &  $C_{OUT}$  > 33 pF

Figure 12: SIM\_RST waveforms / SIM\_V<sub>CC</sub> =  $3.0 \text{ V} \& C_{\text{OUT}} > 33 \text{ pF}$

Figure 14: SIM\_I/O waveforms / on-board Open-Drain configuration, SIM\_ $V_{CC}$  =3 V &  $C_{OUT}$  > 33 pF