# JN Semiconductor®

To kara more about Old Semiconductor, please visit our website at

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

May 2024

# FAN7711 Ballast Control Integrated Circuit

#### **Features**

- Floating Channel for Bootstrap Operation to +600V

- Low Start-up and Operating Current: 120µA, 3.2mA

- Under-Voltage Lockout with 1.8V of Hysteresis

- Adjustable Run Frequency and Preheat Time

- Internal Active ZVS Control

- Internal Protection Function (Latch Mode)

- Internal Clamping Zener Diode

- High Accuracy Oscillator

- Soft-Start Functionality

**Description**

The FAN7711, developed with Fairchild's unique high-voltage process, is a ballast control integrated circuit (IC) for a fluorescent lamp. FAN7711 incorporates a preheating / ignition function, controlled by an elected external capacitor, to increase lamp life. The F. 17711 detects switch operation from affigure in most through an internal active Zero-Y age Switcin (ZVS) control circuit. This control is enabled the FAN7711 to detect an open-lam, convicion without the expense of external circuit and even distribution from that the expense of external circuit and even distribution around a common-most carry and even distribution.

## 8-5017

S-DIP

# **Applications**

■ Electronic Ballast

# Ordering Inf ma on

| Part N nb | Package | Pb-l're() | Operating Temperature Range | Packing Method |

|-----------|---------|-----------|-----------------------------|----------------|

| '77'      | 8-D;'P  | 7 0 7     |                             | Tube           |

| FAN, 11N  | 8-SOP   | Yes       | -25°C ~ 125°C               | Tube           |

| N7 IMX    | 0-30F   | CH!       |                             | Tape & Reel    |

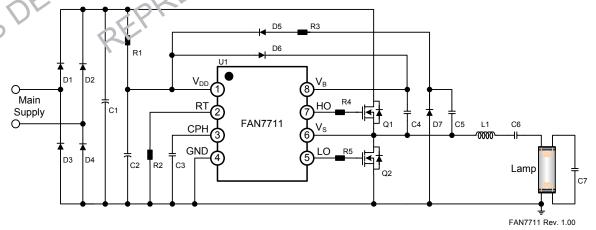

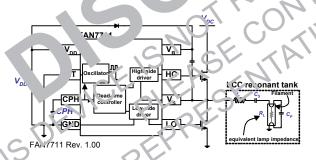

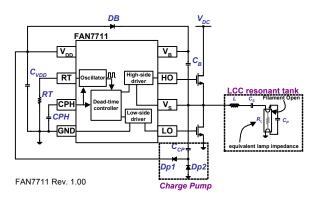

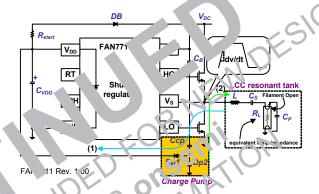

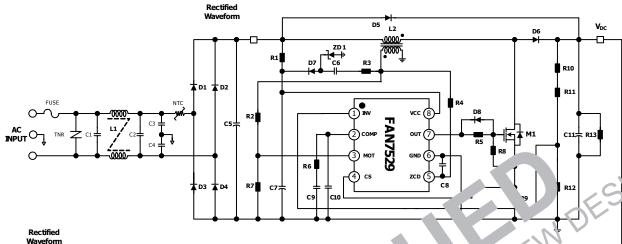

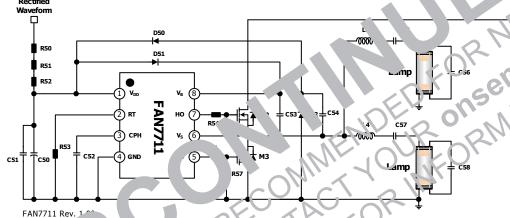

# Typical Application

Figure 1. Typical Application Circuit for Compact Fluorescent Lamp

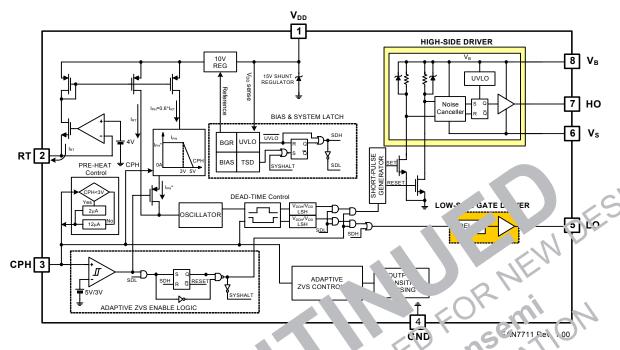

# **Internal Block Diagram**

Figure 2. unctio. Block Diagram

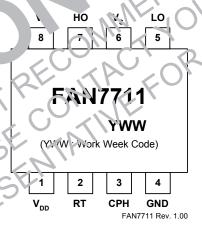

# **Pin Configuration**

Figure 3. Pin Configuration (Top View)

# **Pin Definitions**

| Pin # | Name           | Description                       |  |

|-------|----------------|-----------------------------------|--|

| 1     | $V_{DD}$       | Supply voltage                    |  |

| 2     | RT             | Oscillator frequency set resistor |  |

| 3     | CPH            | Preheating time set capacitor     |  |

| 4     | GND            | Ground                            |  |

| 5     | LO             | Low-side output                   |  |

| 6     | V <sub>S</sub> | High-side floating supply return  |  |

| 7     | НО             | High-side output                  |  |

| 8     | V <sub>B</sub> | High-side floating supply         |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A=25^{\circ}C$  unless otherwise specified.

| Symbol              | Parameter                            |                           |      | Тур.  | Max.        | Unit |

|---------------------|--------------------------------------|---------------------------|------|-------|-------------|------|

| V <sub>B</sub>      | High-side floating supply            | High-side floating supply |      |       | 625         | V    |

| V <sub>S</sub>      | High-side floating supply return     |                           | -0.3 |       | 600         | V    |

| V <sub>IN</sub>     | RT, CPH pins input voltage           |                           | -0.3 |       | 8           | V    |

| I <sub>CL</sub>     | Clamping current level               |                           |      |       | 25          | mA   |

| dV <sub>S</sub> /dt | Allowable offset voltage slew rate   |                           |      | 50    |             | V/ns |

| T <sub>A</sub>      | Operating temperature range          |                           | -25  |       | <u>``</u> 5 | °C   |

| T <sub>STG</sub>    | Storage temperature range            |                           |      |       | <i>i</i> 0  | °C   |

| P <sub>D</sub>      | Power dissipation                    | 8-SOP<br>8-F ?            |      | 0.625 | W.          | W    |

| $\theta_{JA}$       | Thermal resistance (junction-to-air) | SO <sub>1</sub>           |      | 100   |             | °C/W |

#### Note:

1. Do not supply a low-impedance voltage source to me "ternal comping Zerier cliode between the CND and the V<sub>DD</sub> pin of this device.

### **Electrical Characteristics**

$V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS}$ ) = 14.0V,  $T_{A}$  = 25°C, unless otherwise specified.

| Symbol                           | Characteristics                                                                                  | Conditions                                                         | Min.           | Тур.  | Max. | Unit |

|----------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------|-------|------|------|

| Supply Volt                      | age Section                                                                                      |                                                                    |                |       |      |      |

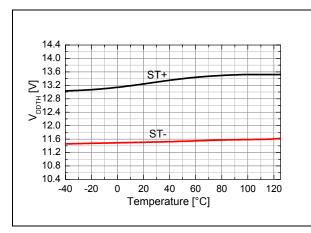

| $V_{DDTH(ST+)}$                  | V <sub>DD</sub> UVLO positive going threshold                                                    | V <sub>DD</sub> increasing                                         | 12.4           | 13.4  | 14.4 |      |

| V <sub>DDTH(ST-)</sub>           | V <sub>DD</sub> UVLO negative going threshold                                                    | V <sub>DD</sub> decreasing                                         | 10.8           | 11.6  | 12.4 | V    |

| $V_{\mathrm{DDHY}(\mathrm{ST})}$ | V <sub>DD</sub> -side UVLO hysteresis                                                            |                                                                    |                | 1.8   |      | V    |

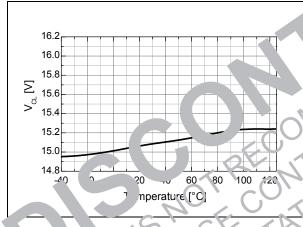

| $V_{CL}$                         | Supply clamping voltage                                                                          | I <sub>DD</sub> =10mA                                              | 14.8           | 15.2  |      |      |

| I <sub>ST</sub>                  | Start-up supply current                                                                          | V <sub>DD</sub> = 10V                                              |                | 120   |      | μА   |

| I <sub>DD</sub>                  | Dynamic operating supply current                                                                 | 50kHz, C <sub>L</sub> = 1nF                                        |                | 22    |      | mA   |

| High-Side S                      | supply Section (V <sub>B</sub> -V <sub>S</sub> )                                                 |                                                                    |                |       |      |      |

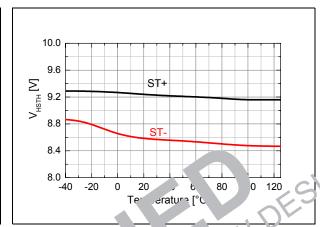

| V <sub>HSTH(ST+)</sub>           | High-side UVLO positive going threshold                                                          | V <sub>BS</sub> increasing                                         | 8.5            | 9.2   | 10.0 | 10   |

| V <sub>HSTH(ST-)</sub>           | High-side UVLO negative going threshold                                                          | V <sub>BS</sub> decreasing                                         | 9              |       | 9.5  | У    |

| V <sub>HSHY(ST)</sub>            | High-side UVLO hysteresis                                                                        |                                                                    |                | 0.6   |      |      |

| I <sub>HST</sub>                 | High-side quiescent supply current                                                               | V <sub>BS</sub> = 14V                                              |                | 50    | 7    | μА   |

| I <sub>HD</sub>                  | High-side dynamic operating supply current                                                       | 50kHz, C <sub>L</sub> = 1                                          | 7              | ZZ    |      | mA   |

| I <sub>LK</sub>                  | Offset supply leakage current                                                                    | V <sub>P</sub> = V <sub>2</sub> ~V                                 | (2)            | *     | 45   | μА   |

| Oscillator S                     | ection                                                                                           | 7177                                                               | <del>) `</del> | 4/1   | 10   | 7    |

| V <sub>MPH</sub>                 | CPH pin preheating voltage range                                                                 |                                                                    | 2.5            | 3.0   | 3.5  | V    |

| I <sub>PH</sub>                  | CPH pin charging current during prehea 'g                                                        |                                                                    | 1.25           | 1:.00 | 2.85 |      |

| I <sub>IG</sub>                  | CPH pin charging current during                                                                  | V <sub>CPH</sub> = 4''                                             | 8              | 12    | 16   | μΑ   |

| V <sub>MO</sub>                  | CPH pin voltage level at TmL 3                                                                   | IN OUT                                                             |                | 7.0   |      | V    |

| f <sub>PRE</sub>                 | Preheating frequency                                                                             | R <sub>1</sub> = 80kΩ, V <sub>DP1</sub> = 2V                       | 72             | 85    | 98   | kHz  |

| f <sub>OSC</sub>                 | Running frec                                                                                     | $R_T = 801\Omega$                                                  | 48.7           | 53.0  | 57.3 | kHz  |

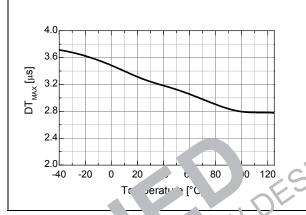

| DT <sub>MAX</sub>                | Maximum c ad time                                                                                | V <sub>CFH</sub> = 1V, V <sub>S</sub> = GND during reneat mode     |                | 3.1   |      | μS   |

| DT <sub>MIN</sub>                | ad time                                                                                          | $V_{CCH} = 6V' V_S = GND$ during run moa :                         |                | 1.0   |      | μS   |

| O' Sec                           | TO SOR                                                                                           | //                                                                 |                |       |      |      |

| I <sub>OH+</sub>                 | h-side driver sourcing current                                                                   | PW = 10μs                                                          | 250            | 350   |      |      |

| JH-                              | High-side driver sinking current                                                                 | PW = 10μs                                                          | 500            | 650   |      | A    |

| 10_+                             | Laviside driver sourcing current                                                                 | PW = 10μs                                                          | 250            | 350   |      | mA   |

| I <sub>OL</sub> -                | ow-side driver sink currout                                                                      | PW = 10μs                                                          | 500            | 650   |      |      |

| l <sub>I</sub> IOP               | High-side driver 'urı-cn rising time                                                             | C <sub>L</sub> = 1nF, V <sub>BS</sub> = 15V                        |                | 45    |      |      |

| <b>S</b> t <sub>HOL</sub>        | High-side driver furn-off rising time                                                            | C <sub>L</sub> = 1nF, V <sub>BS</sub> = 15V                        |                | 25    |      |      |

| t <sub>LOR</sub>                 | Low-side driver turn-on rising time                                                              | ow-side criver turn-on rising time $C_L = 1nF$ , $V_{BS} = 15V$ 45 |                |       | ns   |      |

| t <sub>LOL</sub>                 | Low-side driver turn-off rising time $C_L = 1nF, V_{BS} = 15V$                                   |                                                                    |                | 25    |      |      |

| V <sub>S</sub> <sup>(2)</sup>    | Maximum allowable negative V <sub>S</sub> swing range for signal propagation to high-side output |                                                                    |                | -9.8  |      | V    |

| Protection S                     | Section                                                                                          |                                                                    |                | •     |      |      |

| V <sub>CPHSD</sub>               | Shutdown voltage                                                                                 | // = 0 offer run made                                              | 2.6            |       |      | V    |

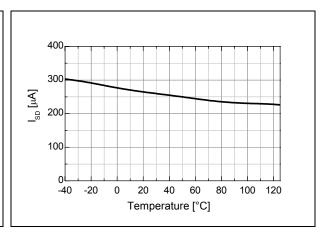

| I <sub>SD</sub>                  | Shutdown current                                                                                 | V <sub>RT</sub> = 0 after run mode                                 |                | 250   | 450  | μА   |

| TSD                              | Thermal shutdown <sup>(2)</sup>                                                                  |                                                                    |                | 165   |      | °C   |

#### Note:

2. This parameter, although guaranteed, is not 100% tested in production.

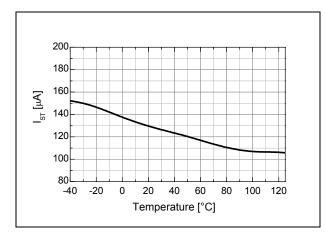

# **Typical Characteristics**

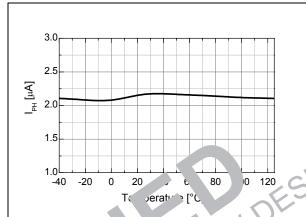

Figure 4. Start-Up Current vs. Temp.

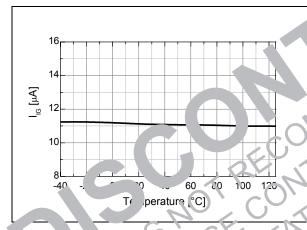

Figur 5. Pre Jurrent vs Temp.

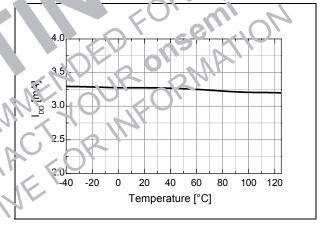

jure 6. Ignition Current vs. Temp

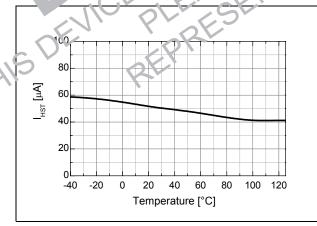

Figure 7. Operating Current vs. Temp.

Figure 8. Start-Up Current vs. Temp.

Figure 9. Shutdown Current vs. Temp.

# Typical Characteristics (Continued)

Figure 10.  $V_{DD}$  UVLO vs. Temp.

F ure 1: 'BS \_O vs. Temp.

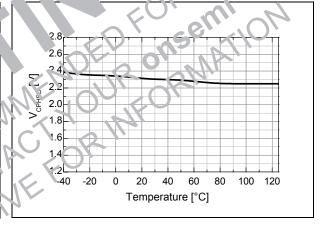

Fig e 1∠. V<sub>DD</sub> Clamp Voltage s. Temp.

Figure 13. Shutdown Voltage vs. Temp.

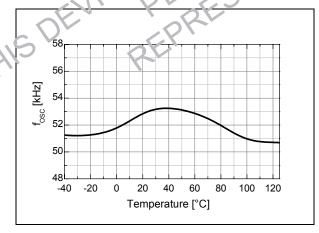

Figure 14. Running Frequency vs. Temp.

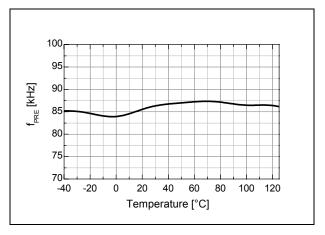

Figure 15. Preheating Frequency vs. Temp.

# **Typical Characteristics** (Continued)

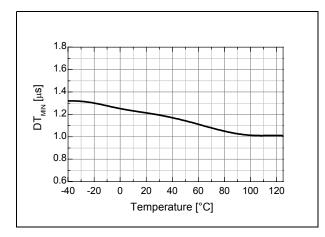

Figure 16. Minimum Dead Time vs. Temp.

Figure 7. Max nun ad Time vs. Temp.

## **Typical Application Information**

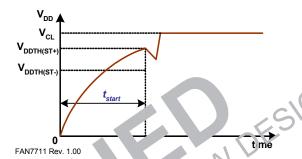

#### 1. Under-Voltage Lockout (UVLO) Function

The FAN7711 has UVLO circuits for both high-side and low-side circuits. When  $V_{DD}$  reaches  $V_{DDTH(ST+)}$ , UVLO is released and the FAN7711 operates normally. At UVLO condition, FAN7711 consumes little current, noted  $I_{ST}$ . Once UVLO is released, FAN7711 operates normally until  $V_{DD}$  goes below  $V_{DDTH(ST-)}$ , the UVLO hysteresis. At UVLO condition, all latches that determine the status of the IC are reset. When the IC is in the shutdown mode, the IC can restart by lowering  $V_{DD}$  below  $V_{DDTH(ST-)}$ .

FAN7711 has a high-side gate driver circuit. The supply for the high-side driver is applied between  $V_B$  and  $V_S$ . To protect the malfunction of the driver at low supply voltage, between  $V_B$  and  $V_S$ , FAN7711 provides an additional UVLO circuit between the supply rails. If  $V_B$ - $V_S$  is under  $V_{HSTH(ST+)}$ , the driver holds low-state to turn off the high-side switch, as shown in Figure 18. As long as  $V_B$ - $V_S$  is higher than  $V_{HSTH(ST-)}$  after  $V_B$ - $V_S$  exceeds  $V_{HSTH(ST+)}$ , operation of the driver continues.

#### 2. Oscillator

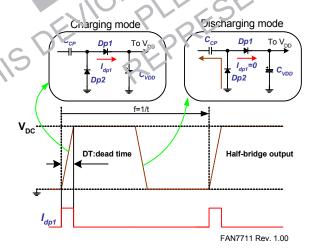

The ballast circuit for a fluorescent lamp is base. In the LCC resonant tank and a half-bridge invession of the shown in Figure 18. To accomplish a rose in the Switching (ZVS) of the half-bridge investing the cuit, the LCC is driven at a higher frequency that its a sonant frequency, which is determed to L. C. C. C. and R. where R. is the equivalent lamp's improvince

Figure 18. Resonant Inverter Circuit Based on LCC Resonant Tank

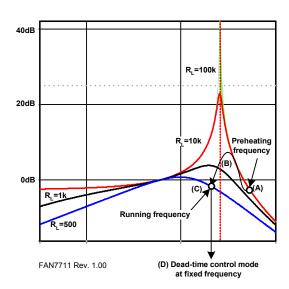

The transfer function of LCC resonant tank is heavily dependent on the lamp impedance,  $R_L$ , as illustrated in Figure 19. The oscillator in FAN7711 generates effective driving frequencies to assist lamp ignition and improve lamp life longevity. Accordingly, the oscillation frequency is changed in the following sequence:

Preheating freq.->Ignition freq.-> Normal running freq.

Before the lamp is ignited, the lamp impedance is very high. Once the lamp is turned on, the lamp impedance significantly decreases. Since the resonant peak is very high due to the high-resistance of the lamp at the instant of turning on the lamp, the lamp must be driven at higher frequency than the resonant frequency, shown as (A) in Figure 19. In this mode, the current supplied by the inverter mainly flows through  $C_P$ .  $C_P$  connects both filaments and makes the current path to ground. As a result, the current warms up the filament for easy ignition. The amount of the current can be adjusted by controlling the oscillation frequency changing the capacitance of  $C_P$ . The driving a quency  $f_{PRE}$ , is called preheating frequency and duerive by:

$$f_{PRE} = 6 \times (EQ 1)$$

Ifter the rm-up, the FAN7711 decreases the nue v, shown as (B) of Figure 19. This action includes the voltage of the ramp and helps the fluor cent lamp ignite. The ignition frequency is described as a function in CPH voltage, as follows:

$$f_G = \left[0.3 \times (5 - V_{CLL}) + 1\right] \times f_{OSC}$$

(EQ 2)

where V<sub>CPH</sub> is the voltage of CPH capacitor.

Equatior 2 is valid only when  $V_{CPH}$  is between 3V to 5V before FAN7711 enters running mode. Once  $V_{CPH}$  reaches 5V, the internal latch records the exit from ignition mode. Unless  $V_{DD}$  is below  $V_{DDTH(ST-)}$ , the preheating and ignition modes appear only once during lamp start transition.

Finally, the lamp is driven at a fixed frequency by an external resistor,  $R_T$ , shown as (C) of Figure 19. If  $V_{DD}$  is higher than  $V_{DDTH(ST+)}$  and UVLO is released, the voltage of  $R_T$  pin is regulated to 4V. This voltage adjusts the oscillator's control current according to the resistance of  $R_T$ . Because this current and an internal capacitor set the oscillation frequency, the FAN7711 does not need any external capacitors.

The proposed oscillation characteristic is given by:

$$f_{OSC} = \frac{4 \times 10^9}{RT}$$

(EQ 3)

Even in the active ZVS mode, shown as (D) in Figure 19, the oscillation frequency is not changed. The dead-time is varied according to the resonant tank characteristic.

Figure 19. LCC Transfer Function in Terms of Lamp Impedance

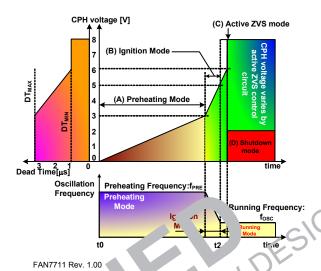

#### 3. Operation Modes

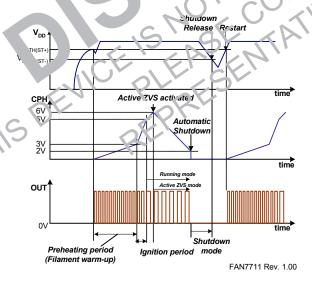

FAN7711 has four operation modes: (A) pre ating mode, (B) ignition mode, (C) active ZVS r and (D) shutdown mode, depicted in Figure 20 The no. automatically selected by the volt ,e or 7H apacitor, shown in Figure 20. In modes (A) nd (B), e C H actor as a timer to determine the least and linear nition times. After the preheating an ignition me ine role of the CPH is changed to smilize to active 21/3 control circuit. In this node, the last time of the inverter is selected high the good of CPH. Only when FAN7/11 is in active Z ? mode is possible to shut of the whole sy Jun ing 'Program Pulling the CPH pin below 2V in ive Z in de, causes the FAN7711 to enter sh down lode. In shutdown mode, all active operation is sum a, except UVLO and some bias circuitry. The shutdown mode is triggered by the external CPH control or the active ZVS circuit. The active ZVS circuit automatically detects larup removal (open-lamp rendition) and decreases CPH voltage below 2V to protect the inverter switches from damage.

igure O. r., on Modes

#### 3.1 hea g h. (c0~t1)

her.  $I_{DD}$  eeds  $V_{\rm DDTH(ST+)}$ , the FAN7711 starts of atic. At this time, an interred current source ( $I_{PH}$ ) char, s CPH. CPH voltage increases from UV to 3V in preheating needs. Accordingly, the oscillation frequency rollows the Equation 4. In this mode, the lamp is not ignited but warmed up for besy ignition. The preheating time depends on the size of CPH:

$$f_{p, \text{ pheat}} = \frac{3 \times CPH}{I_{PH}}$$

[Sec.] (EQ 4)

According to preheating process, the voltage across the lamp to ignite is reduced and the lifetime of the lamp is increased. In this mode, the dead time is fixed at its maximum value.

#### 3.2 Ignition Mode (t1~t2)

When the CPH voltage exceeds 3V, the internal current source to charge CPH is increased about six times larger than  $I_{PH}$ , noted as  $I_{IG}$ , causing rapid increase in CPH voltage. The internal oscillator decreases the oscillation frequency from  $f_{PRE}$  to  $f_{OSC}$  as CPH voltage increases. As depicted in Figure 20, lowering the frequency increases the voltage across the lamp. Finally, the lamp ignites. Ignition mode is defined when CPH voltage lies between 3V and 5V. Once CPH voltage reaches 5V, the FAN7711 does not return to ignition mode, even if the CPH voltage is in that range, until the FAN7711 restarts from below  $V_{DDTH(ST-)}$ . Since the ignition mode continues when CPH is from 3V to 5V, the ignition time is given by:

$$t_{ignition} = \frac{2 \times CPH}{I_{IG}}$$

[Sec.] (EQ 5)

In this mode, dead time varies according to the CPH voltage.

# 3.3 Running and Active Zero-Voltage Switching (AZVS) Modes (t2~)

When CPH voltage exceeds 5V, the operating frequency is fixed to f<sub>OSC</sub> by R<sub>T</sub>. However, active ZVS operation is not activated until CPH reaches ~6V. The FAN7711 prepares for active ZVS operation from the instant CPH exceeds 5V during t2 to t3. When CPH becomes higher than ~6V at t3, the active ZVS operation is activated. To determine the switching condition, FAN7711 detects the transition time of the output (V<sub>S</sub> pin) of the inverter by using VB pin. From the output-transition information, FAN7711 controls the dead time to meet the ZVS condition. If ZVS is satisfied, the FAN7711 slightly increases the CPH voltage to reduce the dead time and to find optimal dead time, which increases the efficiency and decreases the thermal dissipation and EMI of the inverter switches. If ZVS fails, the FAN7711 decreases CPH voltage to increase the dead time. CPH voltage is adjusted to meet optimal ZVS operation. During the active ZVS mode, the amount of the charging/ discharging current is the same as I<sub>PH</sub>. Figure 21 depicts normal operation waveforms.

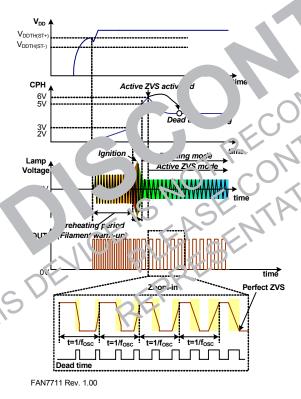

Figure 21. Typical Transient Waveform from Preheating to Active ZVS Mode

#### 3.4 Shutdown Mode

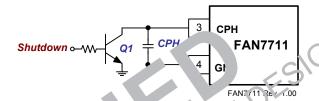

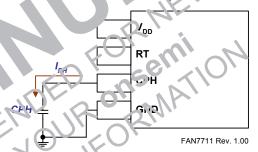

If the voltage of capacitor CPH is decreased below  $\sim 2.6 \text{V}$  by an external application circuit or internal protection circuit, the IC enters shutdown mode. Once the IC enters shutdown mode, this status continues until an internal latch is reset by decreasing  $V_{DD}$  below  $V_{DDTH(ST-)}$ . Figure 22 shows an example of external shutdown control circuit.

Figure 22. E. ern Chatdown Chicuit

The property of the Card charging current is the same as a possible to shut off the IC using small signal ansistor FAN7711 are rides active ZVS ope. From the ling the Card time according to the voltage of CPH. If ZVS fails even at the maximum dead time, FAN7711 stops driving the inverter.

The FAN7711 thermal shudown circuit senses the lanction emperature of the IC. If the temperature exceeds 160°C, the thermal shutdown circuit stops operation of the FAN7711.

The curren usages of shutdown mode and undervoltage lockout status are different. In shutdown mode, some circuit blocks, such as bias circuits, are kept alive. Therefore, the current consumption is slightly higher than during under-voltage lockout.

#### 4. Automatic Open-Lamp Detection

FAN7711 can automatically detect the open-lamp condition. When the lamp is opened, the resonant tank fails to make a closed-loop to the ground, as shown in Figure 23. The supplied current from the  $V_{\rm S}$  pin is used to charge and discharge the charge pump capacitor,  $C_{\rm P}$ . Since the open-lamp condition means resonant tank absence, it is impossible to meet ZVS condition. In this condition, the power dissipation of the FAN7711, due to capacitive load drive, is estimated as:

$$P_{Dissipation} = \frac{1}{2} \times C_P \times V_{DC}^2 \times f \quad [W]$$

(EQ 6)

where f is driving frequency and  $V_{DC}$  is DC-link voltage.

Figure 23. Current Flow When the Lamp is Open

Assuming that  $C_P$ ,  $V_{DC}$ , and f are 1nF, 311V, and 50kHz, respectively; the power dissipation reaches about 2.4W and the temperature of FAN7711 is increased rapidly. If no protection is provided, the IC can be damaged by the thermal attack. Note that hard-switching condition during the capacitive-load drive causes lots of EMI.

Figure 24 illustrates the waveforms during the operamp condition. In this condition, the charging and discharging current of  $C_P$  is directly determined by FAN7711 and considered hard-switching controls. The FAN7711 tries to meet ZVS conditions by Facing CPH voltage to increase dead time of ZVL fails and CPH goes below 2V, even though the lead time realness its maximum value, FAN77 and of the D to protect against damage. To relate that FAN77 and the Delow  $V_{DDTH(S^T)}$  less an internal latch circuit, which remembers the status of the

Figure 24. CPH Voltage Variation in Open-Lamp Condition

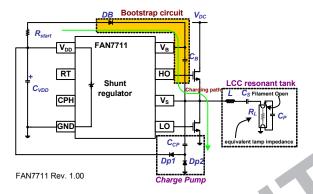

#### 5. Power Supply

When  $V_{DD}$  is lower than  $V_{DDTH(ST+)}$ , it consumes very little current,  $I_{ST}$ , making it possible to supply current to the  $V_{DD}$  pin using a resistor with high resistance ( $R_{start}$  in Figure 25). Once UVLO is released, the current consumption is increased and whole circuits are operated, which requires additional power supply for stable operation. The supply must deliver at least several mA. A charge pump circuit is a cost-effective method to create an additional power supply and allows  $C_P$  to be used to reduce the EMI.

Figure 25. Local Fower Supply for V<sub>DD</sub> Using a Charge Pump Circuit

As presented in Figure 25, when  $V_S$  is high, the inductor current and  $C_{CP}$  create an output transition with the slope of dv/ct. The rising edge of  $V_S$  charges  $C_{CP}$  At that time, the current that flows through  $C_{CP}$  is:

$$I \cong C_{CP} \times \frac{dv}{dt}$$

(EQ 7)

This current flows along the path (1). It charges  $C_{VDD}$ , which is a bypass capacitor to reduce the noise on the supply rail. If  $C_{VDD}$  is charged over the threshold voltage of the internal shunt regulator, the shunt regulator is turned on and regulates  $V_{DD}$  with the trigger voltage.

When  $V_S$  is changing from high to low state,  $C_{CP}$  is discharged through Dp2, shown as path (2) in Figure 26. These charging/discharging operations are continued until FAN7711 is halted by shutdown operation. The charging current, I, must be large enough to supply the operating current of FAN7711.

The supply for the high-side gate driver is provided by the boot-strap technique, as illustrated in Figure 26. When the low-side MOSFET connected between  $V_S$  and GND pins is turned on, the charging current for  $V_B$  flows through  $D_B$ . Every low  $V_S$  gives the chance to charge the  $C_B$ . Therefore  $C_B$  voltage builds up only when FAN7711 operates normally.

When  ${\rm V_S}$  goes high, the diode  ${\rm D_B}$  is reverse-biased and  ${\rm C_B}$  supplies the current to the high-side driver. At this time, since  ${\rm C_B}$  discharges,  ${\rm V_{B^{-}}V_{S}}$  voltage decreases. If  ${\rm V_{B^{-}}V_{S}}$  goes below  ${\rm V_{HSTH(ST^{-})}}$ , the high-side driver cannot operate due to the high-side UVLO protection circuit.  ${\rm C_B}$  must be chosen to be large enough not to fall into UVLO range due to the discharge during a half of the oscillation period, especially when the high-side MOSFET is turned on.

Figure 26. Implementation of Floating Power Supply

Using the Bootstrap Method

### **Design Guide**

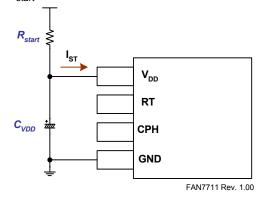

#### 1. Start-up Circuit

The start-up current ( $I_{ST}$ ) is supplied to the IC through the start-up resistor,  $R_{start}$ . Once operation starts, the power is supplied by the charge pump circuit. To reduce the power dissipation in  $R_{start}$ , select  $R_{start}$  as high as possible, considering the current requirements at start-up. For  $220V_{AC}$  power, the rectified voltage by the full-wave rectifier makes DC voltage, as shown in Equation 8. The voltage contains lots of AC component due to poor regulation characteristic of the simple full-wave rectifier:

$$V_{DC} = \sqrt{2} \times 220[V] \cong 311[V]$$

(EQ 8)

Considering the selected parameters, R<sub>start</sub> must satisfy the following equation:

$$\frac{V_{DC} - V_{DDTH(ST+)}}{R_{start}} > I_{ST}$$

(EQ 9)

From Equation 9, R<sub>start</sub> is selected as:

$$\frac{V_{DC} - V_{DDTH(ST+)}}{I_{ST}} > R_{start}$$

(EC )

Note that if choosing the maximum  $R_{start}$  takes and time for  $V_{DD}$  to reach  $V_{DDTH(st+)}$ . Considering  $V_{DD}$  at time,  $R_{start}$  must be selected as shown in the run 30.

Another important concerns runosing  $R_{start}$  is the available power rating  $R_{start}$ . To a commercially available, low-consisted  $R_{start}$  must obey the following rule:

$$\frac{(V_{\text{DC}} - V_{\text{Coll}})^2}{v_{\text{coll}}} < \frac{1}{4} - |W|$$

(EQ 11)

A uming  $V_{DC}$ =311V and  $V_{CL}$ =15V the minimum results of  $R_{start}$  is about 35 Jk $\Omega$ .

When the IC operates in shutdown mode due to thermal protection, open-lamp protection, or hard-switching protection, the IC consumes shutdown current,  $I_{SD}$ , which is larger than  $I_{S1}$  To prevent restart during this mode,  $R_{start}$  must be selected to cover  $I_{SD}$  current consumption. The following equation must be satisfied:

$$\frac{V_{DC} - V_{DDTH(ST+)}}{I_{SD}} > R_{start}$$

(EQ 12)

From Equations 10 - 12; it is possible to select R<sub>start</sub>:

(1) For safe start-up without restart in shutdown mode:

$$4(V_{DC} - V_{CL})^2 < R_{start} < \frac{V_{DC} - V_{DDTH(ST+)}}{I_{SD}}$$

(EQ 13)

(2) For safe start-up with restart from shutdown mode:

$$\frac{V_{DC} - V_{DDTH(ST+)}}{I_{SD}} < R_{start} < \frac{V_{DC} - V_{DDTH(ST+)}}{I_{ST}}$$

(EQ 14)

If  $R_{start}$  meets Equation 14, restart operation is possible. However, it is not recommended to choose  $R_{start}$  at that range because  $V_{DD}$  rising time could be long and it increases the lamp's turn-on delay time, as depicted in Figure 27.

Figure 7. Lan Build-up

Figure 28 how the equivalent circuit for estimating than circuit analysis, V<sub>DD</sub> variation versus time nive by:

$$V_{DD}(t) = (V_{DC} - R_{start} \cdot I_{ST}) \left( e^{-I/(R_{start} \cdot C_{VDL})} \right)$$

(EQ 15)

where  $C_{1DD}$  is the total capacitance of the bypass capacitors connected between  $V_{DD}$  and GND.

From Equation 15, it is possible to calculate  $t_{start}$  by substituting  $V_{DD(t)}$ , with  $V_{DDTH(ST+)}$ :

$$t_{start} = -R_{st,rt} \cdot C_{VDD} \cdot \ln \frac{V_{DC} - R_{start} \cdot I_{ST} - V_{DDTH(ST+)}}{V_{DD} - R_{start} \cdot I_{ST}} \quad (EQ 16)$$

In general, Equation 16 can be simplified as:

$$t_{start} \approx \frac{R_{start} \cdot C_{VDD} \cdot V_{DDTH(ST+)}}{V_{DC} - R_{start} \cdot I_{ST} - V_{DDTH(ST+)}}$$

(EQ 17)

Accordingly,  $t_{start}$  can be controlled by adjusting the value of  $R_{start}$  and  $C_{VDD}$ . For example, if  $V_{DC}$ =311V,  $R_{start}$ =560k,  $C_{VDD}$ =10 $\mu$ F,  $I_{st}$ =120 $\mu$ A, and  $V_{DDTH(ST+)}$ =13.5V,  $t_{start}$  is about 0.33s.

Figure 28. Equivalent Circuit During Start

#### 2. Current Supplied by Charge Pump

For the IC supply, the charge pump method is used in Figure 29. Since  $C_{CP}$  is connected to the half-bridge output, the supplied current by  $C_{CP}$  to the IC is determined by the output voltage of the half-bridge.

When the half-bridge output shows rising slope,  $C_{CP}$  is charged and the charging current is supplied to the IC. The current can be estimated as:

$$I = C_{CP} \frac{dV}{dt} \approx C_{CP} \frac{V_{DC}}{DT}$$

(EQ 18)

where DT is the dead time and dV/dt is the voltage variation of the half-bridge output.

When the half-bridge shows falling slope,  $C_{CP}$  is discharged through Dp2. Total supplied current,  $I_{total}$ , to the IC during switching period, t, is:

$$I_{total} = I \cdot DT = C_{CP} \cdot V_{DC}$$

(EQ 19)

From Equation 19, the average current,  $I_{avg}$ , supplied to the IC is obtained by:

$$I_{avg} = \frac{I_{total}}{t} = \frac{C_{CP} \cdot V_{DC}}{t} = C_{CP} \cdot V_{DC} \cdot f$$

For the stable operation, I must be his er than the required current. If I avg is deeds the shunt regulator implemented in the chip which can cause unwanted heat generation. Fore, C<sub>CC</sub> must be selected considering table operation and thermal generation.

exame e, rep=0.5nf- V<sub>DC</sub>=311V, and f=50kHz, ravg is 7.8mA is enough current for stable operation.

Figure 29. Charge Pump Operation

#### 3. Lamp Turn-on Time

The turn-on time of the lamp is determined by supply build-up time  $t_{start}$ , preheating time, and ignition time; where  $t_{start}$  has been obtained by Equation 17. When the IC's supply voltage exceeds  $V_{DDTH(ST+)}$  after turn-on or restart, the IC operates in preheating mode. This operation continues until CPH pin's voltage reaches ~3V. In this mode, CPH capacitor is charged by  $I_{PH}$  current, as depicted in Figure 30. The preheating time is achieved by calculating:

$$t_{preheat} = 3 \frac{CPH}{I_{Ph}}$$

(EQ 21)

The preheating time is all ad to it in life (especially filament); therefore, he charact stics of a given lamp should be confidence there woosing the time.

Figure 30. Preheating Timer

Compared to the preheating time, it is almost impossible to exactly predict the ignition time, whose definition is the time from the end of the preheating time to ignition. In general, the lamp ignites during the ignition mode. Therefore, assume that the maximum ignition time is the same as the duration of ignition mode, from 3V until CPH reaches 5V. Thus, ignition time can be defined as:

$$t_{ignition} = (5-3)\frac{CPH}{I_{IG}} = 2\frac{CPH}{I_{IG}}$$

(EQ 22)

Note that, at ignition mode, CPH is charged by  $I_{IG}$ , which is six times larger than  $I_{PH}$ . Consequently, total turn-on time is approximately:

VDD Build-Time + Preheating Time + Ignition Time =

$$t_{ignition} = (5-3)\frac{CPH}{I_{IG}} = 2\frac{CPH}{I_{IG}}$$

[Sec.] (EQ 23)

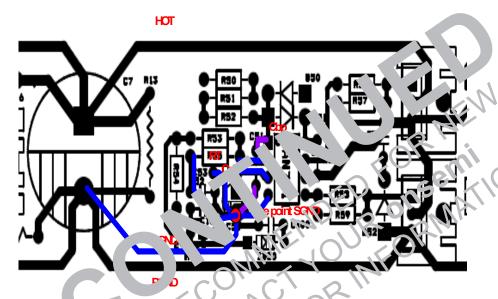

#### 4. PCB Guideline

Component selection and placement on PCB is important when using power control ICs. Bypass the  $V_{CC}$  to GND as close to the IC terminals as possible with a low-ESR/ESL capacitor, as shown in Figure 31. This bypassed capacitor ( $C_{BP}$ ) can reduce the noise from the power supply parts, such as start-up resistor and charge pump.

The signal GND must be separated from the power GND. So, the signal GND should be directly connected to the rectify capacitor using an individual PCB trace.

In addition, the ground return path of the timing components ( $C_{PH}$ ,  $R_{T}$ ) and  $V_{DD}$  decoupling capacitor should be connected directly to the IC GND lead and not via separate traces or jumpers to other ground traces on the board. These connection techniques prevent high-current ground loops from interfering with sensitive timing component operations and allow the control circuit to reduce common-mode noise due to output switching.

Figure 31 Prefigating Times

# Typical Application Diagram

Figure 32. Application Circuit of J2W Two Lamps

# **Component List for 32W Two Lamps**

| Part    | Value                     | Note                   | Part          | Value           | Note                    |

|---------|---------------------------|------------------------|---------------|-----------------|-------------------------|

| Resisto |                           | r                      | C55 15nF/630V |                 | Miller Capacitor        |

| R1      | 330kΩ 1/2W                |                        | C56           | 2.7nF/1kV       | Miller Capacitor        |

| R2      | 750kΩ                     | 1/4W                   | C57           | 15nF/630V       | Miller Capacitor        |

| R3      | 100Ω                      | 1/2W                   | C58           | 2.7nF/1kV       | Miller Capacitor        |

| R4      | 20kΩ                      | 1/4W                   |               | Diode           | )                       |

| R5      | 47Ω                       | 1/4W                   | D1            | 1N4007          | 1kV,1A                  |

| R6      | 10kΩ                      | 1/4W                   | D2            | 1N4007          | 1kV,1A                  |

| R7      | 50kΩ                      | 1/4W                   | D3            | 1N4007          | ¹kV,1A                  |

| R8      | 47kΩ                      | 1/4W                   | D4            | 1N4007          | i /,1A                  |

| R9      | 0.3Ω                      | 1W                     | D5            | UF400           | tre ust,1kV,1A          |

| R10     | 1ΜΩ                       | 1/4W                   | D6            | UF 707          | Ulura Fast, 1kV,1A      |

| R11     | 1ΜΩ                       | 1/4W                   | D7            | 1N4'1 3         | 100V,1A                 |

| R12     | 12.6kΩ                    | 1/4W,1%                | D8            | N414            | 100V,1A                 |

| R13     | 220kΩ                     | 2W                     | D.            | Ur-1007         | Ultra Fast,1kV,1A       |

| R50     | 150kΩ                     | 1/4W                   | 51            | UF4007          | Utro Fast.10V.1A        |

| R51     | 150kΩ                     | 1/4W                   |               | JF4007          | Ultra Fast.1kV,1A       |

| R52     | 150kΩ                     | 1/4W                   | ZD1           | IN4746A         | Zener 18V, 1W           |

| R53     | 90kΩ                      | 1/ ^/                  |               | MOSF            | 2///                    |

| R54     | 10Ω                       | 1/4                    | M1            | FOPF5N60C       | 500V,6A                 |

| R55     | 47Ω                       | 4W                     | M2            | FQPF5N50C       | 500V,5A                 |

| R56     | 47kΩ                      | ./4W                   | î/J3          | FQPF5N50C       | 500V,5A                 |

| R57     | 47Ω                       | 1/4///                 |               | Fuse            |                         |

| R58     | 47kQ                      | 1/4W                   | Fuse          | 3A/250V         |                         |

|         | apacito                   |                        |               | TNR             |                         |

| 01      | 471                       | Pux Capacitor          | TNR           | 471             |                         |

| C2      | 1.J0nF/275V <sub>AC</sub> | BDX Capacitor          |               |                 |                         |

| 3       | 220UpF/3kV                | Cerartic Capacitor     |               | NTC             |                         |

| C4      | 22u0pF/3kV                | Cerarnic Capacitor     | NTC           | 10D-09          |                         |

| C5      | 0.22µF/630V               | Miller Capacitor       |               | Line Filt       | ter                     |

| Ct      | 12nF/50∀                  | Ceramic Capacitor      | LF1           | 40mH            |                         |

| C7      | 22µF/5ύ∀                  | Electrolytic Capacitor |               | Transfor        | mer                     |

| C8      | 39pF/50V                  | Ceramic Capacitor      | L1            | 0.94mH(75T:10T) | El2820                  |

| C9      | 1μF/50V                   | Ceramic Capacitor      |               | Inductor        |                         |

| C10     | 0.1µF/50V                 | Ceramic Capacitor      | L2            | 3.2mH(130T)     | El2820                  |

| C11     | 47μF/450V                 | Electrolytic Capacitor | L3            | 3.2mH(130T)     | El2820                  |

| C50     | 10μF/50V                  | Electrolytic Capacitor |               | IC              |                         |

| C51     | 1μF/50V                   | Ceramic Capacitor      | U1            | FAN7711         | Fairchild Semiconductor |

| C52     | 0.47µF/25V                | Ceramic Capacitor,5%   | U2            | FAN7529         | Fairchild Semiconductor |

| C53     | 100nF/50V                 | Ceramic Capacitor      |               |                 |                         |

| C54     | 470pF/1kV                 | Ceramic Capacitor      |               |                 |                         |

# **Component List for 20W CFL**

| Part | Value      | Note                   | Part     | Value                                | Note                   |

|------|------------|------------------------|----------|--------------------------------------|------------------------|

|      | Resistor   |                        |          | Diode                                |                        |

| R1   | 470kΩ      | 1/4W                   | D1       | D1 1N4007 1kV/1A                     |                        |

| R2   | 90kΩ       | 1/4W                   | D2       | 1N4007                               | 1kV/1A                 |

| R3   | 10Ω        | 1/4W                   | D3       | 1N4007                               | 1kV/1A                 |

| R4   | 47Ω        | 1/4W                   | D4       | 1N4007                               | 1kV/1A                 |

| R5   | 47Ω        | 1/4W                   | D5       | UF4007                               | 1kV/1A,Ultra Fast      |

|      |            |                        | D6       | UF4007                               | 1'1A,Ultra Fast        |

|      | Capacitor  |                        | D7       | UF4007                               | 1kV/1 Ultra Fast       |

| C1   | 22µF/250V  | Electrolytic Capacitor | Ir actor |                                      |                        |

| C2   | 10μF/50V   | Electrolytic Capacitor | L1       | 2.5m <sup>L</sup> (28 <sup>¬</sup> ) | E16.6S                 |

| C3   | 470nF/25V  | Miller Capacitor       |          | MC 7F                                |                        |

| C4   | 100nF/25V  | Miller Capacitor       | Q1       | PF1N. C                              | 500V,1A                |

| C5   | 470pF/630V | Miller Capacitor       | C        | FQ1 .50C                             | 500V,1A                |

| C6   | 33nF/630V  | Miller Capacitor       |          | IC                                   | M-1/m                  |

| C7   | 3.3nF/1kV  | Miller Capacite        |          | FAN7711                              | Carchild Semiconductor |

#### Note:

3. Refer to the typical application circuit production in igure 1.

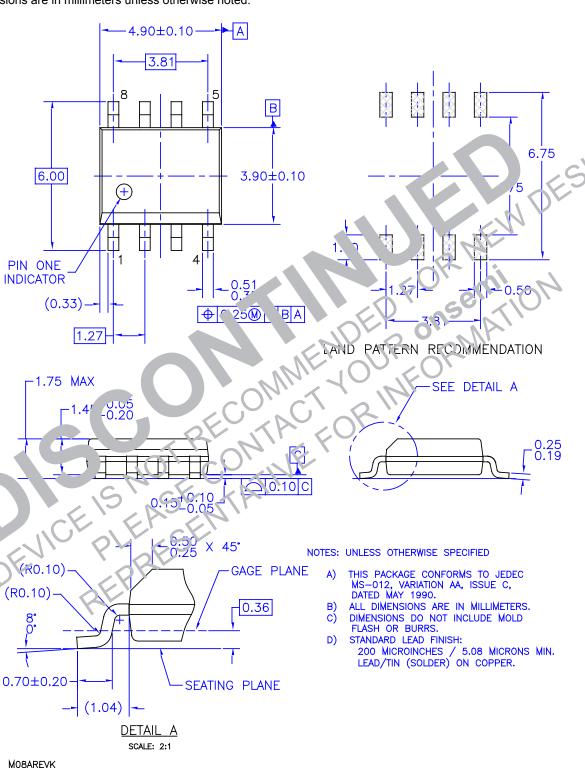

# **Package Dimensions**

#### 8-SOP

Dimensions are in millimeters unless otherwise noted.

Figure 33. 8-Lead Small Outline Package (SOP)

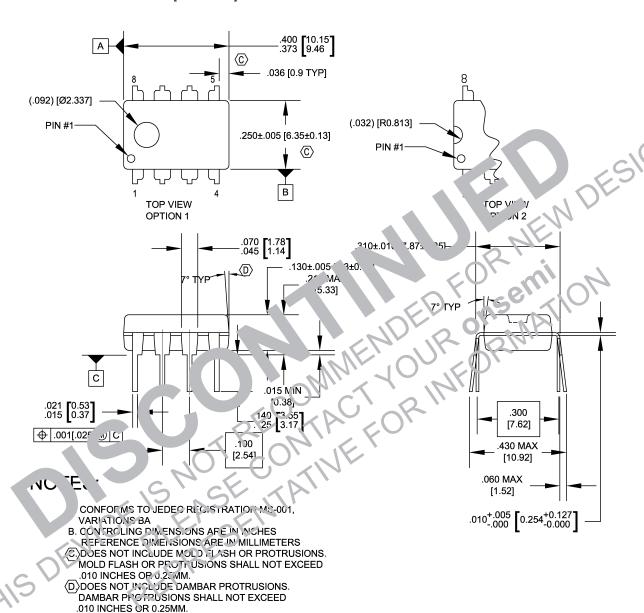

# **Package Dimensions**

#### 8-DIP

Dimensions are in inches and [millimeters] unless otherwise noted.

# N08EREVG

E. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

Figure 34. 8-Lead Dual In-Line Package (DIP)

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

Power-SPM™ HiSeC™ TinyBuck™ Across the board. Around the world.™ PowerTrench® TinyLogic<sup>®</sup> i-Lo™  $TINYOPTO^{TM}$ ActiveArray™ ImpliedDisconnect™ Programmable Active Droop™ **QFĔT** TinyPower™ Bottomless™ IntelliMAX™ Build it Now™ ISOPLANAR™  $QS^{\text{TM}}$ TinvWire™ CoolFET™ QT Optoelectronics™ TruTranslation™ MICROCOUPLER™ CorePLUS™ Quiet Series™ MicroPak™ μSerDes™ RapidConfigure™  $CROSSVOLT^{\text{TM}}$ MICROWIRE™ ORNEW DESI **CTL™** RapidConnect™ L ₹ET™ Motion-SPM™ Current Transfer Logic™ ScalarPump™  $MSX^{TM}$ DOME™ SMART START™  $MSXPro^{\scriptscriptstyle\mathsf{TM}}$ E<sup>2</sup>CMOS™ SPM<sup>®</sup>  $OCX^{TM}$ EcoSPARK® STEALTH™  $OCXPro^{TM}$ EnSigna™ OPTOLOGIC® SuperFET™ FACT Quiet Series™ SuperSOT1-3 OPTOPLANAR® **FACT**® SuperSOT  $\mathsf{PACMAN}^\mathsf{TM}$ FAST® PDP-SPM™ Sup FASTr™

FRFET® Power247® 'wo GlobalOptoisolator™ PowerEdge™ GTO™

POP™

Power220®

PowerSaver™

#### **DISCLAIMER**

FPS™

FAIRCHILD SEMICONDUCTOR RESEF LISTH. YIG: TO MAKE C.: A IGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, F ICTION, ₹ DŁ.JGN. F.\RCHILD DOEC YOTASSUMF, ANY LIABILITY ARISING OUT OF THE OD TORC CUIT DESCRIBED HERLIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS APPLICATION OR USE OF AN" PATENT RIGHTS, NOR THE JIGHTS OF J. THESE SPECIFICATIONS DO NOTEXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND ONDITIONS, SPECIFICALLY THE WARRANTY THEREIN WHICH COVERS THESE PRODUCTS.

mci

**1**TM

TinyBoost

#### LIFE SUPPORT YOU'S

RE NOT A JTH ORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR FAIRCHILD PRODUCTS \*\* Wi OUT THE EXPRECS WAS TEN APPROVALOR FAIRCHILD SEMICONDUCTOR CORPORATION.

- used h∈

- Life silport devices or systems are devices or systems rich (a) are intended for surgical implant into the body or (L. Jupport or sustain life, and (c) whose railure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                   |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev 127

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative