**Description**

# **NCV7703C Triple Half-Bridge Driver with SPI Control Evaluation Board User's Manual**

The NCV7703C is a triple half-bridge driver for automotive applications targeted for use as a side-view mirror control in an automobile. X-Y mirror control is accomplished by using a common node for the dual motors.

Communication to the device is through a SPI bus using the

SPI defined communication input pins SI, SO, SCLK, and

The two on-board motors display the mirror application in action. Circuit setups for short to battery and to ground are

Each of the 3 NCV7703C output drivers is designed in

a half-bridge configuration for 500 mA with an overcurrent

minimum threshold of 1.1 A. Concurrent turn-on of the

high-side and low-side devices is not allowed, and attempts

provided as well as underload conditions.

are recorded and reported.

ON Semiconductor®

www.onsemi.com

## **EVAL BOARD USER'S MANUAL**

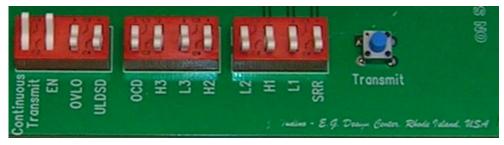

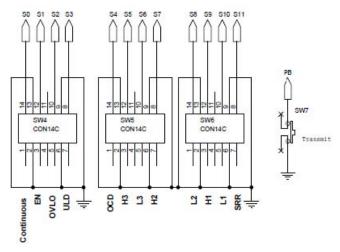

Interface to the board is through DIP switches whose positions are displayed on the board LCD display and communicated to the NCV7703C using a microprocessor when the Transmit button is depressed.

#### **Features**

- X–Y Motor Mirror Control Display

- Option for External Motor Connections

- SPI Input Switch Control

- Fault Setting and Reporting

- SPI Pin Isolation Capability from Microprocessor

(Bottom View)

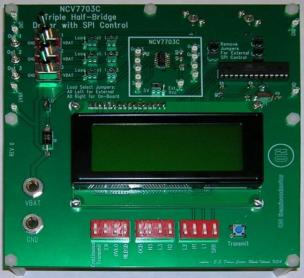

Figure 1. NCV7703C Evaluation Board

## **Application**

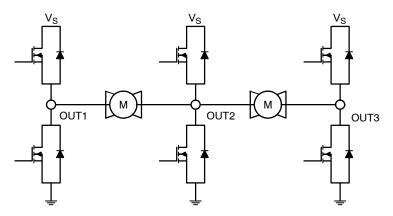

The NCV7703C provides three output pins set up in a half-bridge configuration. The intended operation is to drive motors by turning on one of the high-side drivers and one of the low-side drivers with a motor load between the two drivers (Figure 2). Using these three half bridges set up in this configuration allows for full-bridge operation of two motors allowing for polarity changes in drive capability for forward and reverse operation.

Primary target load are motors used for automotive side-view mirrors. In a side-view mirror one motor typically drives the mirror on the x-axis while the other mirror typically drives the mirror on the y-axis. The bottom of the eval board (Figure 1) shows the 2 motors in the top left of the photo.

Figure 2. Cascaded Application

#### Communication

The NCV7703C utilizes SPI (Serial Peripheral Interface) protocol for all communication. SPI uses 4 pins for this communication.

- SI Serial Input

- SO Serial Output

- SCLK Clock

- CSB Chip Select Bar

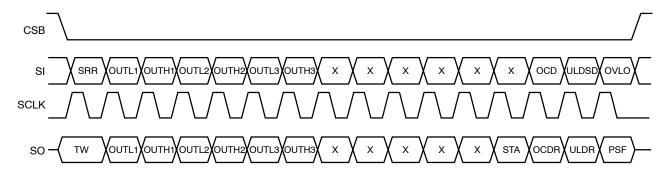

Figure 3 shows the format of the 16 bit waveforms used in the NCV7703C.

#### **SPI Operation**

Chip select bar goes low indicating data is about to be transferred into the NCV7703C. Data is clocked into the NCV7703C (SI) at the same time the output register information is being clocked out (SO). Each bit of the input waveform corresponds to device control. It's important to note data (on SI) is clocked in on the negative edge of the clock. Data is clocked out (on SO) on the positive edge of the clock. These edges must match if devices are to be used in a daisy chain configuration. See NCV7703C/D for further information.

Figure 3. SPI Communication Frame Format

A transcription of input SPI commands is shown in Table 1. Input SPI commands provide Output Drive definition and programmable attribute designation.

## **Table 1. INPUT SPI COMMANDS**

|            | Input Data                                     |              |  |  |  |  |  |

|------------|------------------------------------------------|--------------|--|--|--|--|--|

| Bit Number | Bit Description                                | Bit Status   |  |  |  |  |  |

| 15         | Over Voltage Lock Out Control (OVLO)           | 0 = Disable  |  |  |  |  |  |

|            |                                                | 1 = Enable   |  |  |  |  |  |

| 14         | Under Load Detection Shut Down Control (ULDSD) | 0 = Disable  |  |  |  |  |  |

|            |                                                | 1 = Enable   |  |  |  |  |  |

| 13         | Over Current Detection Shut Down Control (OCD) | 0 = 200 μs   |  |  |  |  |  |

|            |                                                | 1 = 25 μs    |  |  |  |  |  |

| 12         | Not Used                                       |              |  |  |  |  |  |

| 11         | Not Used                                       |              |  |  |  |  |  |

| 10         | Not Used                                       |              |  |  |  |  |  |

| 9          | Not Used                                       |              |  |  |  |  |  |

| 8          | Not Used                                       |              |  |  |  |  |  |

| 7          | Not Used                                       |              |  |  |  |  |  |

| 6          | OUTH3                                          | 0 = Off      |  |  |  |  |  |

|            |                                                | 1 = On       |  |  |  |  |  |

| 5          | OUTL3                                          | 0 = Off      |  |  |  |  |  |

|            |                                                | 1 = On       |  |  |  |  |  |

| 4          | OUTH2                                          | 0 = Off      |  |  |  |  |  |

|            |                                                | 1 = On       |  |  |  |  |  |

| 3          | 3 OUTL2                                        |              |  |  |  |  |  |

|            |                                                | 1 = On       |  |  |  |  |  |

| 2          | OUTH1                                          | 0 = Off      |  |  |  |  |  |

|            |                                                | 1 = On       |  |  |  |  |  |

| 1          | OUTL1                                          | 0 = Off      |  |  |  |  |  |

|            |                                                | 1 = On       |  |  |  |  |  |

| 0          | Status Register Reset (SRR)                    | 0 = No Reset |  |  |  |  |  |

|            |                                                | 1 = Reset    |  |  |  |  |  |

A transcription of output SPI data is shown in Table 2. Output SPI data provides output status and fault reporting.

## **Table 2. OUTPUT SPI COMMANDS**

|            | Output Data                                    |                |  |  |  |  |  |

|------------|------------------------------------------------|----------------|--|--|--|--|--|

| Bit Number | Bit Description                                | Bit Status     |  |  |  |  |  |

| 15         | Power Supply Fail Signal                       | 0 = No Fault   |  |  |  |  |  |

|            | (PSF for ÓVLO or UVLO)                         | 1 = Fault      |  |  |  |  |  |

| 14         | Under Load Detection Reporting Signal (ULDR)   | 0 = No Fault   |  |  |  |  |  |

|            |                                                | 1 = Fault      |  |  |  |  |  |

| 13         | Over Current Detection Reporting Signal (OCDR) | 0 = No Fault   |  |  |  |  |  |

|            |                                                | 1 = Fault      |  |  |  |  |  |

| 12         | Shoot-Through Attempt (STA)                    | 0 = No Attempt |  |  |  |  |  |

|            |                                                | 1 = Attempt    |  |  |  |  |  |

| 11         | Not Used                                       |                |  |  |  |  |  |

| 10         | Not Used                                       |                |  |  |  |  |  |

| 9          | Not Used                                       |                |  |  |  |  |  |

| 8          | Not Used                                       |                |  |  |  |  |  |

| 7          | Not Used                                       |                |  |  |  |  |  |

| 6          | OUTH3                                          | 0 = Off        |  |  |  |  |  |

|            |                                                | 1 = On         |  |  |  |  |  |

| 5          | OUTL3                                          | 0 = Off        |  |  |  |  |  |

|            |                                                | 1 = On         |  |  |  |  |  |

| 4          | OUTH2                                          | 0 = Off        |  |  |  |  |  |

|            |                                                | 1 = On         |  |  |  |  |  |

| 3          | OUTL2                                          | 0 = Off        |  |  |  |  |  |

|            |                                                | 1 = On         |  |  |  |  |  |

| 2          | OUTH1                                          | 0 = Off        |  |  |  |  |  |

|            |                                                | 1 = On         |  |  |  |  |  |

| 1          | OUTL1                                          | 0 = Off        |  |  |  |  |  |

|            |                                                | 1 = On         |  |  |  |  |  |

| 0          | Thermal Warning (TW)                           | 0 = Not in TW  |  |  |  |  |  |

|            |                                                | 1 = In TW      |  |  |  |  |  |

The NCV7703CGEVB is capable of demonstrating.

- Turning Outputs On and Off

- Reporting Underload Detection

- Reporting Overcurrent Detection

- Shoot-through Attempts

- Power Supply Failure (OVLO or UVLO)

- Thermal Warning

The operation of the NCV7703C evaluation board works as a standalone presentation for the customer highlighting

H-Bridge operation with motor loads used typically in automotive mirror control systems. Dip switches provide the user programmability for the output control and programmability of overvoltage lockout, underload shut down control, and overcurrent detection shutdown control. Jumpers provide convenient access to external SPI inputs and the external 5 V regulator. Jumpers are also included to direct external loads and fault creation. A toggle switch provides short circuit simulation.

The user must adhere to the absolute maximum ratings when using off-board connections.

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                | Value       | Unit |

|---------------------------------------------------------------------------------------|-------------|------|

| VBAT Supply Voltage to Board (14 VDC) (Using On-board Motors)                         | -0.3 to 16  | V    |

| VBAT Supply Voltage to Board (14 VDC) (Setting Load Jumpers Left for External Motors) | -0.3 to 40  | V    |

| OUTx (Setting Load Jumpers Left for External Motors)                                  | -0.3 to 40  | V    |

| Logic Pin Voltage EN, SI, SO, SCLK, CSB (Removing Jumpers to Pins)                    | -0.3 to 5.5 | V    |

| VCC (ext.)                                                                            | -0.3 to 5.5 | V    |

| Junction Temperature (NCV7703C)                                                       | -40 to 150  | °C   |

| Junction Temperature (Evaluation Board)                                               | -40 to 105  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 4. RECOMMENDED OPERATING CONDITIONS**

| Parameter                        | Min | Max | Unit |

|----------------------------------|-----|-----|------|

| External Supply Voltage (14 VDC) | -   | 16  | V    |

| Junction Temperature (NCV7703C)  | -40 | 150 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 5. PIN FUNCTION DESCRIPTION**

| Connector   | Pin Number | Terminal Name        | Description                                                                                                                       |  |

|-------------|------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Power       | J4         | UVLO                 | Connection to Power Supply input (VS) C1 = 0.1 $\mu$ F to GND This capacitance may need modification for increased external loads |  |

|             | GND        | GND                  | Ground                                                                                                                            |  |

| Test Points | J1         | ULD                  | Series connection to OUT1 for underload testing                                                                                   |  |

|             | J2         | ULD                  | Series connection to OUT2 for underload testing                                                                                   |  |

|             | J3         | ULD                  | Series connection to OUT3 for underload testing                                                                                   |  |

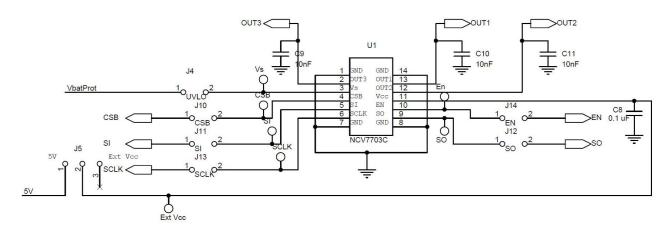

|             | J5         | 5V/Ext. Vcc          | Selection jumper for onboard 5 V or off-board 5 V                                                                                 |  |

|             | J6, J7, J9 | Load Select<br>OUT x | Selection jumper for onboard motor load or off-board pin for OUT1, OUT2, and OUT3                                                 |  |

|             | J8         | N/A                  | N/A                                                                                                                               |  |

|             | J10-J13    | CSB                  | SPI jumpers CSB, SI, SO, SCLK                                                                                                     |  |

|             | J14        | EN                   | Enable input pin                                                                                                                  |  |

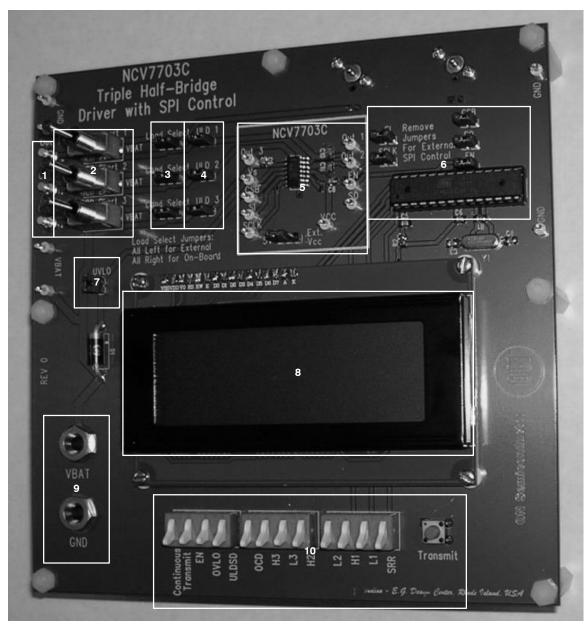

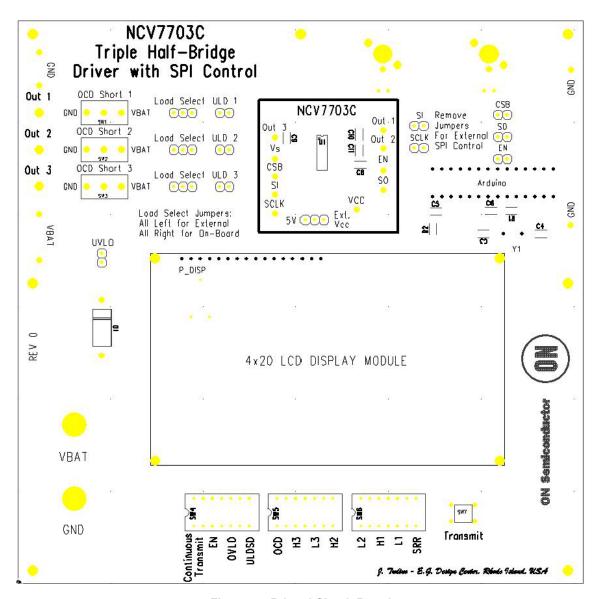

#### **User Interface Locations**

Figure 4 shows all the user interface locations. This lists all the user options available on the evaluation board.

- 1. OUT1-3 External Post Connections

- 2. Short Circuit to GND/VBAT toggle switches

- 3. Load Select Jumpers

- 4. Underload (ULD1-3) Jumpers

- 5. NCV7703C with 5V Jumper and posts for EN, SI, SO, SCLK, CSB, VS, OUT1-3, VCC

- 6. Microprocessor with isolation jumpers for SPI

- 7. Undervoltage Lockout jumper (UVLO)

- 8. User interface display

- 9. 14 V VBAT power supply input

- 10. SPI input dip switches with transmit button

Figure 4. User Interface Locations

#### Using the NCV7703C Evaluation Board

Start with all jumpers connected on the board with the Load Select jumpers to the right and the jumper in the NCV7703C box set to the left for on-board 5 V regulation. This will set the board up for use with the onboard motors in normal mode with the on-board 5 V regulator (NCV4274A).

When you 1<sup>st</sup> turn the power on the eval board, the splash screen will appear.

Figure 5. Display Splash

After 3 seconds the splash screen will disappear and the control screen will appear.

Figure 6. Control Screen

The SI and SO registers will appear at the bottom of the screen.

The top of the screen displays PUOS which indicates bit 15 – bit 12 descriptions for the Output Register for the 4 bits on the output register (SO). They appear directly above the bits in the output register to which they designate.

- Bit 15 P– Power Supply Fail Signal

- Bit 14 U Under Load Detection Reporting

- Bit 13 O Over Current Detection

- Bit 12 S Shoot-through Attempt

Figure 7. Output Faults

Beneath "PUOS" is "SLCT" which indicates "select" for 332211Th of the input register (SI). Above 332211Th are the polarity identifiers for each output bit and the Thermal Warning bit (TW indicated as Th). When not enabled, a "D" will be displayed for "disable" at the top left of the screen.

Figure 8. Output Selection

#### **Programming the SPI Commands**

The NCV7703C SPI commands are all encoded using the dip switches at the bottom of the board. A low is designated by the dip switch down while a high is designated by the dip switch high. The user is given access to all 10 NCV7703C SPI input bits directly (6 of the 16 SPI input bits are unused).

Two modes of sending signals are provided.

- 1. Transmit.

- a. This allows you to set the dip switches prior to sending the command. Simply set the switches and press the Transmit button.

- 2. Continuous Transmit.

- a. This allows a repitition of commands as dictated by the dip switches. This allows the user to see an immediate response on the display screen.

NOTE: All commands for any activation of the NCV7703C eval board will require EN to be high. The EN (enable) pin is controlled by the microprocessor.

Figure 9. SPI Programming

#### **Turning Output Drivers ON**

Each of the three outputs can operate individually in either high-side or low-side mode. To demonstrate H-Bridge operation, the user should connect one terminal of the load device to one of the NCV7703C's outputs and the other terminal to a different output.

#### Example of Operation on the Eval Board

Referencing the motor schematic shown in Figure 2, turning on the  $1^{st}$  motor,

- 1. Set the EN dip switch high.

- 2. Set the H1 dip switch high.

- 3. Set the L2 dip switch high.

- 4. Press the transmit switch.

Multiple combinations of half-bridge drivers will turn the two motors on in different directions.

Braking the motors is recommended for system design (i.e. bringing the motors to a stop before changing direction) although it is unlikely any damage will occur on the eval board if accidently exercised without braking.

#### **External SPI and Logic Control**

Normal communication to the NCV7703C is provided by the on-board microprocessor shown in Figure 10. To communicate with an external device, remove the SI, SCLK, CSB, SO, and EN jumpers and connect the communication to the posts shown in Figure 11.

Figure 10.

#### **Logic Power Supply Input**

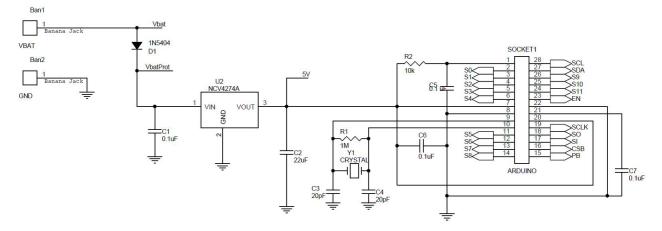

The NCV7703C is powered by a 5 V regulator to pin 11 ( $V_{\rm CC}$ ). The evaluation board supplies 5 V from an on-board 5 V regulator IC (NCV4274A) located under the board powered through VBAT. Figure 11 shows the jumper to use the on-board regulator. To use an external regulator, move the jumper to the right, and connect your external regulator to the  $V_{\rm CC}$  post.

Figure 11.

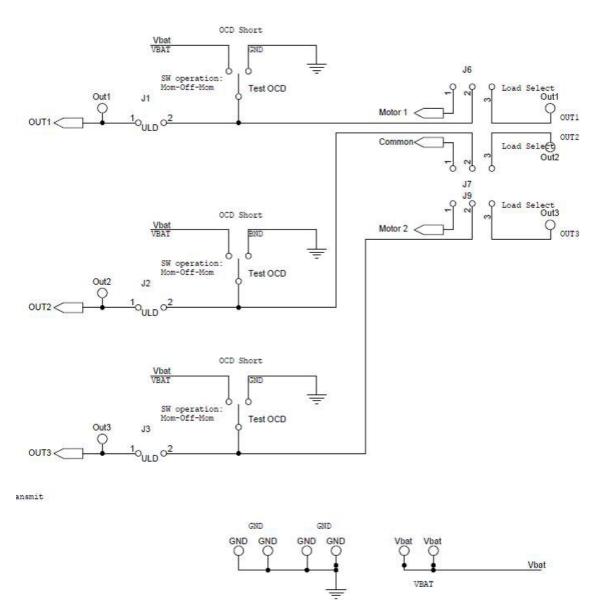

#### **Creating Faults On-Board**

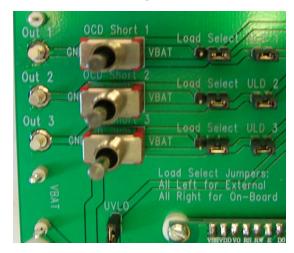

Faults can be created on the board using the setup shown in Figure 12. Additionally, the output loads can be directed off-board here using the Load Select Jumpers. The Load Select Jumpers to the right as shown in Figure 12 utilize the two motor loads of the board. Move the jumpers to the left to use the posts Out 1, Out 2, and Out 3 on the left of Figure 12.

#### Underload

Remove the ULD x jumpers while OUTx is turned on to remove the load connected to the output. With ULDSD set high, the output will latch off. With ULDSD set low, the output will not latch off.

#### Overcurrent

Use the toggle switch to create a setup for short to GND (left) for high-side mode or short to VBAT (right) for low-side mode while the output is turned on.

Figure 12. Fault Creating

#### **Other Faults**

#### Shoot-Through Attempt

Attempting to turn on a channel high-side driver and low-side driver at the same time will be sensed by the NCV7703C and not allowed to happen. This will be reported in bit number 12 of the output register.

#### Power Supply Failure

$V_S$  power supply faults are reported on bit 15 of the output register. An undervoltage condition can be simulated by removing the UVLO jumper. Overvoltage conditions are reported directly from the VBAT input voltage. Overvoltage conditions are not allowed on this eval board using the on-board motors. External loads should be used during overvoltage testing of the NCV7703C.

#### Thermal Warning

IC Thermal Warning is provided on Bit 0 of the output register should the IC temperature reach 140°C (typ).

#### Loads

The Load Select jumpers shown in Figure 12 direct the outputs (OUTx) to the on-board motors (jumper to the right) or to the posts (jumper to the left) shown on the left of Figure 12.

#### Status Register Reset (SRR)

The Status Register Reset bit is Bit 0 in the input register.

- The PSF (Power Supply Fail Bit) fault is reset with SRR

- The STA (Shoot-Through Attempt Bit) fault is reset with SRR.

- An OCD (overcurrent event) requires SRR=1 to turn a driver back on and clear the error bit.

- A ULD (underload) fault is reset with SRR.

- A TW (thermal warning) fault is reset with SRR after the IC cools below its' TW threshold.

- Proceeding Thermal Shutdown, SRR is required with a turn-on command for operation.

Figure 13. NCV7703C Evaluation Board Schematic - Integrated Circuit

Figure 14. NCV7703C Evaluation Board Schematic - SPI DIP Switch Interface

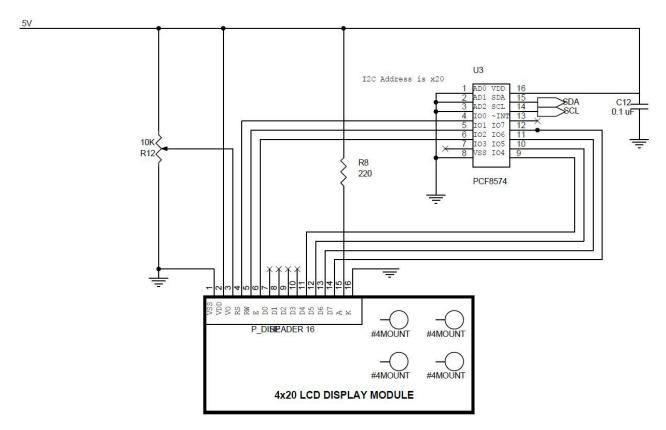

Figure 15. NCV7703C Evaluation Board Schematic - User Display

Figure 16. NCV7703C Evaluation Board Schematic - Motor Loads

Figure 17. NCV7703C Evaluation Board Schematic - 5 V Regulator and Microprocessor

Figure 18. NCV7703C Evaluation Board Schematic – Output Faults and Load Select

Figure 19. Printed Circuit Board

## **Bill of Materials**

## Table 6. NCV7703C EVALUATION BOARD BILL OF MATERIALS

| Designator                    | Qty. | Description                          | Value         | Tolerance | Footprint        | Manufacturer                       | Manufacturer Part Number | Substitution<br>Allowed |

|-------------------------------|------|--------------------------------------|---------------|-----------|------------------|------------------------------------|--------------------------|-------------------------|

| VBAT                          | 1    | Banana Jack                          | _             | -         | BANANA           | CINCH<br>CONNECTIVITY<br>SOLUTIONS | 108-0740-001             | Yes                     |

| GND                           | 1    | Banana Jack                          | -             | -         | BANANA           | CINCH<br>CONNECTIVITY<br>SOLUTIONS | 108-0740-001             | Yes                     |

| C3, C4                        | 2    | Oscillator Load<br>Capacitors        | 20 pF         | 5%        | 0805             | KEMET                              | C0805C200J5GACTU         | Yes                     |

| C1, C6,<br>C7, C5,<br>C8, C12 | 6    | Bypass<br>Capacitors                 | 0.1 μF        | 10%       | 0805             | KEMET                              | C0805C104K5RACTU         | Yes                     |

| C2                            | 1    | 5 V Regulator<br>Output<br>Capacitor | 22 μF         | 20%       | 1206             | KEMET                              | C1206C226M4PAC7800       | Yes                     |

| C9, C10,<br>C11               | 3    | Output<br>Capacitors                 | 0.01 μF       | 10%       | 0805             | KEMET                              | C0805C103K5RACTU         | Yes                     |

| D1                            | 1    | Reverse Battery<br>Diode             | 3 A,<br>400 V | -         | 1N540X           | ON Semiconductor                   | 1N5404RLG                | Yes                     |

| J1-J4,<br>J10-J14             | 9    | Jumper Posts<br>100 mil, 2 Post      | -             | -         | JMP              | ЗМ                                 | 961102-6404-AR           | Yes                     |

| J5, J6, J7,<br>J9             | 4    | Jumper Posts<br>100 mil, 3 Post      | -             | _         | JP3              | ЗМ                                 | 961103-6404-AR           | Yes                     |

| N/A                           | 13   | Jumper Shunts<br>100 mil Spacing     | _             | -         | N/A              | SULLINS<br>CONNECTOR<br>SOLUTIONS  | QPC02SXGN-RC             | Yes                     |

| R1                            | 1    | Oscillator Bias<br>Resistor          | 1 ΜΩ          | 1%        | 0805             | VISHAY DALE                        | CRCW08051M00FKEA         | Yes                     |

| R2                            | 1    | Pull-Up Resistor                     | 10 kΩ         | 1%        | 0805             | VISHAY DALE                        | CRCW080510K0FKEA         | Yes                     |

| R8                            | 1    | LCD Backlight<br>Resistor            | 220 Ω         | 1%        | 0805             | VISHAY DALE                        | CRCW0805220RFKEA         | Yes                     |

| R12                           | 1    | Thumbwheel<br>Potentiometer          | 10 kΩ         | 20%       | 3352E_POT        | BOURNS INC                         | 3352E-1-103LF            | Yes                     |

| SW1,<br>SW2,<br>SW3           | 3    | SPDT<br>Mom-Off-Mom                  | -             | _         | MINITOGGLE_LARGE | E-SWITCH                           | 100SP4T1B1M2QEH          | Yes                     |

| SW4,<br>SW5,<br>SW6           | 3    | Programming<br>DIP Switches          | -             | -         | DIP14            | GRAYHILL                           | 76STC04T                 | No                      |

| SW7                           | 1    | Transmit<br>Pushbutton               | -             | -         | SW_6x6_TACTILE   | TE<br>CCONNECTIVITY<br>ALCOSWITCH  | 1–1825910–0              | Yes                     |

| TURRET<br>1, 2, 3             | 3    | Off-Board Load<br>Turrets            | -             | -         | TURRET           | MIL-MAX                            | 2501-2-00-44-00-00-07-0  | Yes                     |

| TP1-TP16                      | 16   | Test Points                          | -             | -         | TP               | KEYSTONE<br>ELECTRONICS            | 5012                     | Yes                     |

| U1                            | 1    | NCV7703C<br>Triple<br>Half-Bridge    | -             | -         | SOIC14_N         | ON Semiconductor                   | NCV7703CD2G              | No                      |

| U2                            | 1    | NCV4274A 5 V<br>Regulator            | -             | -         | DPAK3_SMD        | ON Semiconductor                   | NCV4274ADT50RKG          | Yes                     |

| U3                            | 1    | PCF8574T I/O<br>Expander             | -             | -         | SOIC16_W         | NXP<br>SEMICONDUCTOR               | PCF8574T                 | No                      |

| Y1                            | 1    | 16 MHz<br>Microprocessor<br>Crystal  | 20 pF         | 30 ppm    | XTAL             | CTS-FREQUENCY<br>CONTROLS          | ATS16A                   | Yes                     |

| Arduino                       | 1    | Arduino-Based<br>SPI Conroller       | -             | -         | N/A              | ATMEL                              | ATMEGA328P-PU            | No                      |

| SOCKET1                       | 1    | 28 Pin DIP<br>Socket for<br>Arduino  | -             | -         | DIP28            | ON SHORE<br>TECHNOLOGY<br>INC      | ED281DT                  | Yes                     |

## Table 6. NCV7703C EVALUATION BOARD BILL OF MATERIALS (continued)

| Designator  | Qty. | Description                     | Value | Tolerance | Footprint         | Manufacturer                      | Manufacturer Part Number | Substitution<br>Allowed |

|-------------|------|---------------------------------|-------|-----------|-------------------|-----------------------------------|--------------------------|-------------------------|

| LCD         | 1    | 20 x 4 LCD<br>Module            | -     | -         | N/A               | COFUFU                            | LCM TM204A               | Yes                     |

| P_DISP      | 1    | 16 Pin Header<br>for LCD Module | -     | -         | SIP-16P           | SULLINS<br>CONNECTOR<br>SOLUTIONS | PRPC016SAAN-RC           | Yes                     |

| MG1,<br>MG2 | 2    | 12 V DC Motor                   | -     | -         | FK-050SHB-07295-R | NICHIBO TAIWAN                    | FK-050SHB-07295-R        | No                      |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

The evaluation board/kit (research and development board/kit) (hereinafter the "board") is not a finished product and is not available for sale to consumers. The board is only intended for research, development, demonstration and evaluation purposes and will only be used in laboratory/development areas by persons with an engineering/technical training and familiar with the risks associated with handling electrical/mechanical components, systems and subsystems. This person assumes full responsibility/liability for proper and safe handling. Any other use, resale or redistribution for any other purpose is strictly prohibited.

THE BOARD IS PROVIDED BY ONSEMI TO YOU "AS IS" AND WITHOUT ANY REPRESENTATIONS OR WARRANTIES WHATSOEVER. WITHOUT LIMITING THE FOREGOING, ONSEMI (AND ITS LICENSORS/SUPPLIERS) HEREBY DISCLAIMS ANY AND ALL REPRESENTATIONS AND WARRANTIES IN RELATION TO THE BOARD, ANY MODIFICATIONS, OR THIS AGREEMENT, WHETHER EXPRESS, IMPLIED, STATUTORY OR OTHERWISE, INCLUDING WITHOUT LIMITATION ANY AND ALL REPRESENTATIONS AND WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, NON-INFRINGEMENT, AND THOSE ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE CUSTOM OR TRADE PRACTICE.

onsemi reserves the right to make changes without further notice to any board.

You are responsible for determining whether the board will be suitable for your intended use or application or will achieve your intended results. Prior to using or distributing any systems that have been evaluated, designed or tested using the board, you agree to test and validate your design to confirm the functionality for your application. Any technical, applications or design information or advice, quality characterization, reliability data or other services provided by **onsemi** shall not constitute any representation or warranty by **onsemi**, and no additional obligations or liabilities shall arise from **onsemi** having provided such information or services.

onsemi products including the boards are not designed, intended, or authorized for use in life support systems, or any FDA Class 3 medical devices or medical devices with a similar or equivalent classification in a foreign jurisdiction, or any devices intended for implantation in the human body. You agree to indemnify, defend and hold harmless onsemi, its directors, officers, employees, representatives, agents, subsidiaries, affiliates, distributors, and assigns, against any and all liabilities, losses, costs, damages, judgments, and expenses, arising out of any claim, demand, investigation, lawsuit, regulatory action or cause of action arising out of or associated with any unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of any products and/or the board.

This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and may not meet the technical requirements of these or other related directives.

FCC WARNING – This evaluation board/kit is intended for use for engineering development, demonstration, or evaluation purposes only and is not considered by **onsemi** to be a finished end product fit for general consumer use. It may generate, use, or radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment may cause interference with radio communications, in which case the user shall be responsible, at its expense, to take whatever measures may be required to correct this interference.

onsemi does not convey any license under its patent rights nor the rights of others.

LIMITATIONS OF LIABILITY: **onsemi** shall not be liable for any special, consequential, incidental, indirect or punitive damages, including, but not limited to the costs of requalification, delay, loss of profits or goodwill, arising out of or in connection with the board, even if **onsemi** is advised of the possibility of such damages. In no event shall **onsemi**'s aggregate liability from any obligation arising out of or in connection with the board, under any theory of liability, exceed the purchase price paid for the board, if any.

The board is provided to you subject to the license and other terms per **onsemi**'s standard terms and conditions of sale. For more information and documentation, please visit www.onsemi.com.

#### **ADDITIONAL INFORMATION**

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales