## **ON Semiconductor**

## Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# AR0330CS Evaluation Board User's Manual

ON Semiconductor®

www.onsemi.com

#### **Evaluation Board Overview**

The evaluation boards are designed to demonstrate the features of image sensors products from ON Semiconductor. This headboard is intended to plug directly into the Demo 3 system. Test points and jumpers on the board provide access to the clock, I/Os, and other miscellaneous signals.

#### **Features**

- Clock Input

- ◆ Default 27 MHz Crystal Oscillator

- Optional Demo 3 Controlled MClk

- Two-wire Serial Interface

- Selectable Base Address

- Parallel Interface

- ROHS Compliant

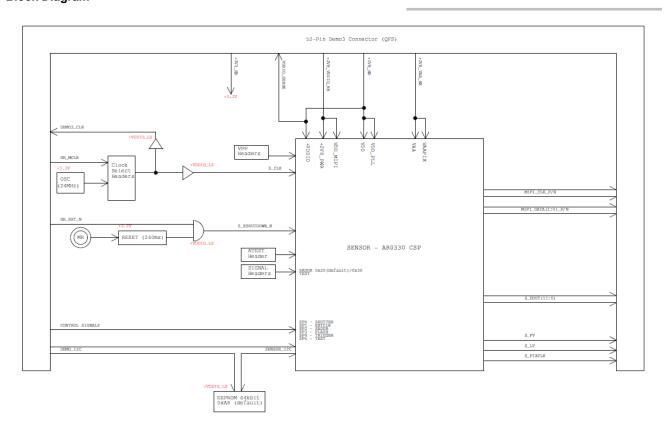

### Block Diagram

## **EVAL BOARD USER'S MANUAL**

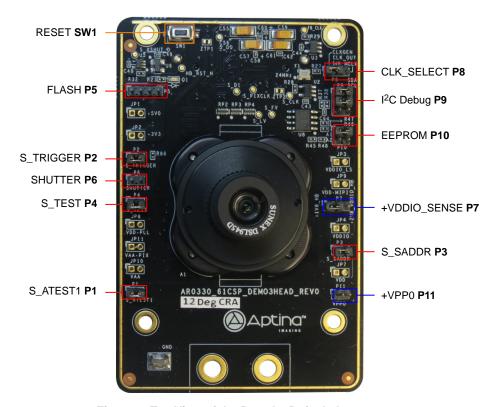

Figure 1. AR0330CS Evaluation Board

Figure 2. Block Diagram of AR0330CS1C12SPKAH3-GEVB

#### **Top View**

Figure 3. Top View of the Board - Default Jumpers

#### **Bottom View**

Figure 4. Bottom View of the Board - Connector

#### **Jumper Pin Locations**

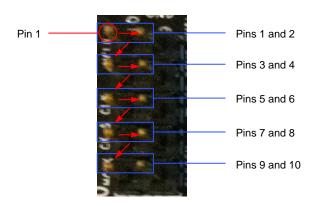

The jumpers on headboards start with Pin 1 on the leftmost side of the pin. Grouped jumpers increase in pin size with each jumper added.

Figure 5. Pin Locations for a Single Jumper. Pin 1 is Located at the Leftmost Side and Increases as it Moves to the Right

Figure 6. Pin Locations and Assignments of Grouped Jumpers.

Pin 1 is Located at the Top-Left Corner and Increases in a Zigzag Fashion Shown in the Picture

#### **Jumper/Header Functions & Default Positions**

**Table 1. JUMPERS AND HEADERS**

| Jumper/Header No. | Jumper/Header Name | Pins             | Description                                             |

|-------------------|--------------------|------------------|---------------------------------------------------------|

| P1                | S_ATEST1           | Closed (Default) | ATEST1 Pin is Connected to GND                          |

|                   |                    | Open             | External Test Signal can be Provided for Analog Test    |

| P2                | S_TRIGGER          | Closed (Default) | TRIGGER Pin is Connected to GND                         |

|                   |                    | Open             | For Connection to External Trigger for Frame Rate Sync. |

| P3                | S_SADDR            | 1-2 (Default)    | I <sup>2</sup> C Address Set to 0x20                    |

|                   |                    | Open             | I <sup>2</sup> C Address Set to 0x30                    |

| P4                | S_TEST             | 1-2 (Default)    | Normal Mode Operation                                   |

|                   |                    | Open             | Test Mode Operation                                     |

| P5                | FLASH              | 1                | +5V0                                                    |

|                   |                    | 2                | GND                                                     |

|                   |                    | 3                | FLASH                                                   |

|                   |                    | 4                | +3V3                                                    |

| P6                | SHUTTER            | Open (Default)   | For Connection to External Shutter                      |

| P7                | +VDDIO_SENSE       | 1-2 (Default)    | 1.8 V Operation of Sensor                               |

|                   |                    | 2–3              | 2.8 V Operation of Sensor                               |

| P8                | CLK_SELECT         | 1-2 (Default)    | On-board Oscillator (24MHz)                             |

|                   |                    | 2–3              | Demo 3 Headboard MCLK                                   |

Table 1. JUMPERS AND HEADERS (continued)

| Jumper/Header No. | Jumper/Header Name     | Pins                            | Description                                               |

|-------------------|------------------------|---------------------------------|-----------------------------------------------------------|

| P9                | I <sup>2</sup> C Debug | 1-2, 3-4 (Default)              | Demo SCL & SDA Connected to Sensor SCL & SDA Respectively |

| P10               | LSC EEPROM             | 1-2 Open,<br>3-4 Open (Default) | EEPROM Address Set to 0xAC                                |

|                   |                        | 1–2 Open,<br>3–4 Closed         | EEPROM Address Set to 0xA4                                |

|                   |                        | 1–2 Closed,<br>3–4 Open         | EEPROM Address Set to 0xA8                                |

|                   |                        | 1–2 Closed,<br>3–4 Closed       | EEPROM Address Set to 0xA0                                |

| P11               | +VPP0                  | Open (Default)                  | OTPM Programming Voltage Not Supplied                     |

| SW1               | RESET                  | N/A                             | When Pushed, 240 ms Reset Signal will be Sent to AR0330CS |

#### Interfacing to ON Semiconductor Demo 3 Baseboard

The ON Semiconductor Demo 3 baseboard has a similar 52-pin connector which mates with J1 of the headboard. The four mounting holes secure the baseboard and the headboard with spacers and screws.

#### **Shorted Jumpers for Power Measurement**

Different supplies to the evaluation board are provided by trace shorted jumper, for any voltage and power measurements. To conduct current for current measurement on a given power rail, cut the trace between the two pins of their respective JP, and insert an ammeter prior to powering up the system. The figure below shows where the trace to cut is located.

## Table 2. SHORTED JUMPERS FOR POWER MEASUREMENT

| Jumper                 | Voltage (V) |

|------------------------|-------------|

| JP1 (from Demo 3)      | 5.0         |

| JP2 (Peripheral 3.3 V) | 3.3         |

| JP3 (VDDIO_LS)         | 1.8         |

| JP4 (VDDIO)            | 1.8         |

| JP7 (VDD)              | 1.8         |

| JP8 (VDD_SLVS)         | 1.8         |

| JP9 (VDD_PLL)          | 2.8         |

| JP10 (VAA)             | 2.8         |

| JP11 (VAA_PIX)         | 2.8         |

Figure 7. Top and Bottom View of Shorted Jumper.

The Bottom View Shows the Trace Location to Cut for Current Measurement

ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative