## NCP4305FBDAP Evaluation Board User's Manual

# 65 W Off-Line Adapter with Synchronous Rectification and Featuring Very Low No-Load Power Consumption

#### Overview

The presented design demonstrates a switching mode AC/DC adapter with high efficiency through whole load range including no load consumption. The design utilizes a primary controller NCP1249C/D, secondary side CVCC and off-mode controller NCP4354A and last but not least synchronous rectification controller NCP4305.

The NCP1249 is fixed frequency current mode flyback controller featuring a peak power excursion, high-voltage start-up, off-mode and X2 capacitor discharging feature. Secondary side controller NCP4354A features two OTAs that are used to provide constant voltage and constant current regulator, very light load condition detection, off-mode control and indication LED driver. NCP4354A communicates with primary controller featuring off-mode through regulation optocoupler. Secondary side synchronous controller NCP4305 is used to control a MOSFET transistor that is used in place of a rectification diode on the secondary side.

The NCP4035 controller turns the synchronous rectifier transistor on in time for current to flow from the transformer to adapter output. Since the voltage drop on the transistor is lower than the voltage drop over a diode this leads to a higher overall efficiency adapter. The NCP4305 monitors the voltage across the synchronous rectification transistor and according to its magnitude and value; it turns the transistor on and off. This controller also includes feature light load detection that is used to modulate the driver output for smooth transitions between medium and light loads. In very light loads the light load detection feature will disable the controller to eliminate switching losses. ON Semiconductor's newest synchronous rectifier has a 4 A drive and an 8 A sink driver. The strong and robust driver of the NCP4305 allows for a very fast, controlled and accurate turn on and turn off to maximize conduction period. The strong sink on the NCP4305 allows this controller to operate in CCM. To further improve efficiency the NCP4305 has incorporated an ultra fast trigger. The trigger pin can be used to help reduce cross conduction, and improve efficiency, during CCM. Information about primary side turn-on can be transferred to NCP4305's TRIG pin on the secondary side that immediately turns-off the SR transistor.

#### **Key Features**

- Synchronous Rectification

- Constant Voltage Constant Current Regulation (CCCV)

- Very Low Input Power at Light and No Load

- High Efficiency Across the Entire Load Range

- Overpower Protection

- Universal Mains Operation

ON Semiconductor®

www.onsemi.com

#### **EVAL BOARD USER'S MANUAL**

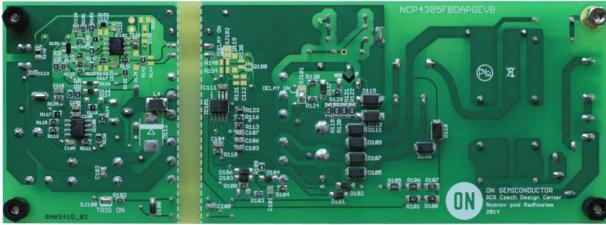

Figure 1. Evaluation Board Photo

#### **Circuit Description**

The primary side uses a flyback topology, providing the advantage of a cost effective power stage design. The power stage operates in both CCM (continuous conduction mode) and DCM (discontinuous conduction mode), allowing it to accept a wide universal input voltage range. The CCM operation provides desired full load performance with good efficiency and low ripple of primary current. The DCM operation then permits an increase of efficiency under the light load conditions, by decreasing the switching losses. The device switches at 65 kHz which represents a good trade-off between switching losses and magnetic core size.

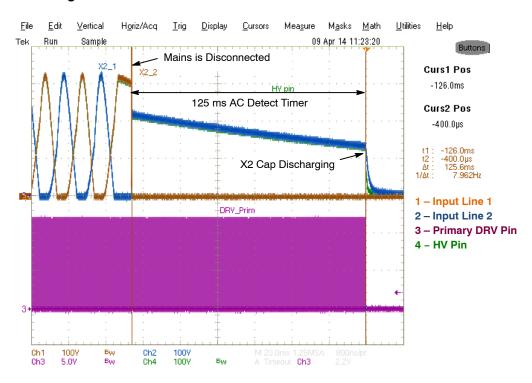

The adapter's primary side consists of several important sections. The first is an input EMI filter to reduce the conducted EMI to the ac line at the input of the adapter. The EMI filter is formed by common-mode inductor L2 and capacitors C1, C4, C5 and C12 with differential mode inductor L1. The varistor R7 is used to protect the adapter against the line overvoltage peaks. When the power supply is disconnected from the AC mains, X capacitors C4, C12 and Y capacitors C1 and C5 are discharged through HV pin via the following path: rectifying diodes D108, D110 and limiting and surge protection R100 and R101. This feature replaces commonly used discharging resistors and saves approximately 25 mW of input power consumption at 230 Vac.

The next block is the rectifier with bulk capacitor. The main power stage of the flyback converter utilizes the low  $R_{DSon}$  MOSFET SPP11N60C3 along with a custom designed transformer TR1 KA5037–BL from Coilcraft. The detailed design procedure of a flyback adapter can be found in the application note  $\underline{AND8461/D}$ .

The secondary side rectification is done in with a MOSFET Q2 controlled by NCP4305. The voltage across the transistor is sensed through resistor R126 at the CS pin. The transistor is driven directly from ON Semiconductor's

new NCP4305. The NCP4305 is powered from the output voltage and charge is held by VCC capacitors C108 and C109. The minimum on and off times are set by resistors R112 and R115. The light load detection circuit, comprised of diode D116, resistors R125, R127, R128, and capacitors C105 and C110, compares the charge on capacitors C105 and C110 to the VCC capacitors and provides information about output power to LLD pin. Also the SR controller can be triggered from the primary side driver through solder jumper SJ100, R102, pulse transformer TR2, C100. A simple RC snubber R5 and C9 across the secondary synchronous rectifier transistor damps the high frequency ringing caused by the unclamped leakage inductance of the secondary side of the transformer and the rectification diode capacitance. There is also a small inductance C4 connected between transformer and SR transistor that helps fight against a high amplitude voltage peak on the SR transistor that is produced in CCM.

Another IC on the secondary side is the NCP4354A controller which provides the output voltage and output current regulation. The output voltage is set by voltage divider R133, R137, R147 and R152, and the output current is sensed at sense resistor R146. The regulation output is coupled to the primary side controller via the optocoupler. The NCP4354 secondary controller also detects very light load condition via R145, R148, R151 and C118. The signal from the transformer has to be inverted to this network because the secondary side rectifier is not in the positive path, but in the return path. This inversion is accomplished by diodes D118, Q101, R135 and R136. When light load condition is detected, the primary controller is switched into OFF mode by an ON/OFF current sink to the DRIVE pin via an optocoupler. The built in LED driver indicates that the primary side operation (when SMPS is not in OFF mode). The LED driver switches with 1 kHz frequency and 12% duty to further improve efficiency.

**Table 1. GENERAL PARAMETERS**

| Parameter                                               | Symbol                 | Value         | Unit            |

|---------------------------------------------------------|------------------------|---------------|-----------------|

| Input Voltage                                           | V <sub>IN</sub>        | 85–265        | V <sub>AC</sub> |

| Input Frequency                                         | f <sub>IN</sub>        | 30–80         | Hz              |

| Output Voltage                                          | V <sub>OUT</sub>       | 12.0          | V               |

| Nominal Output Current                                  | Гоитном                | 5.5           | Α               |

| Output Current Limit                                    | I <sub>OUTLIM</sub>    | 5.9           | Α               |

| Efficiency I <sub>OUT</sub> > 3% I <sub>OUTMAX</sub>    | η                      | > 85          | %               |

| Efficiency I <sub>OUT</sub> > 25% I <sub>OUTMAX</sub>   | η                      | > 89          | %               |

| No-Load Power Consumption V <sub>IN</sub> = 115 V/60 Hz | P <sub>IN</sub>        | 11.1          | mW              |

| No-Load Power Consumption V <sub>IN</sub> = 230 V/50 Hz | P <sub>IN</sub>        | 20.5          | mW              |

| Output Voltage Ripple I <sub>OUT</sub> = 5.5 A          | V <sub>OUT_PK-PK</sub> | 30            | mV              |

| Load Regulation I <sub>OUT</sub> = 50 mA – 5.5 A        | LOAD <sub>REG</sub>    | 12.5          | mV/A            |

| Maximal Load Resistance to Stay in On-Mode              | R <sub>OUTON</sub>     | 1.3           | kΩ              |

| Minimal Load Resistance to Activate Off-Mode            | R <sub>OUTOFF</sub>    | 1.9           | kΩ              |

| Board Dimension                                         |                        | 165 × 60 × 27 | mm              |

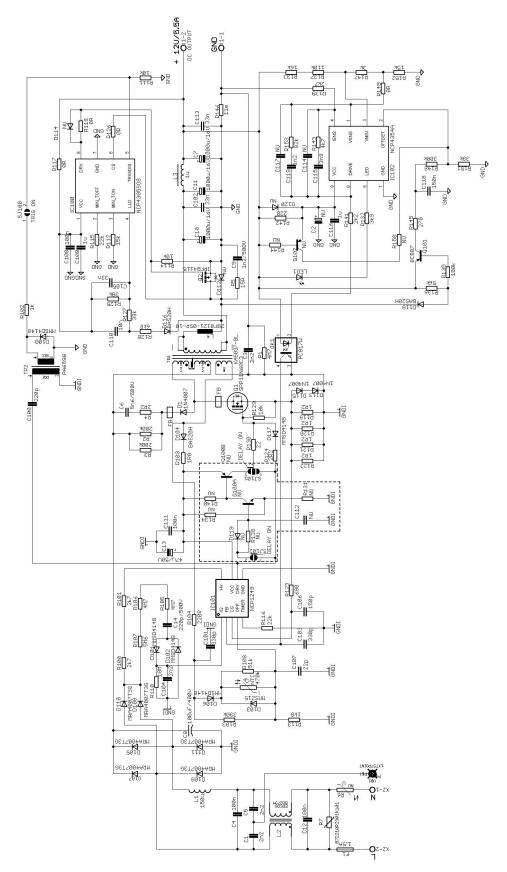

## **Evaluation Board Schematic**

Figure 2. Evaluation Board Schematic

#### **No Load Input Power Consumption**

Input power consumption was measured by Yokogawa WT210 power meter. Input power was integrated for 20 minutes and averaged from 4 measurements.

**Table 2. NO LOAD INPUT POWER CONSUMPTION**

| Input Voltage | Input Power |

|---------------|-------------|

| 115 V; 60 Hz  | 7.0 mW      |

| 230 V; 50 Hz  | 12.2 mW     |

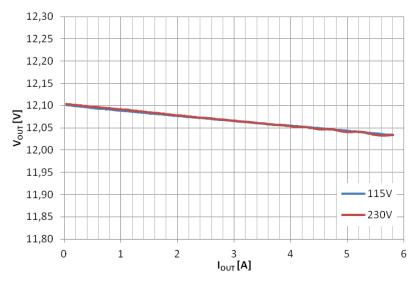

#### **Load Regulation**

The main impact on load regulation is the current sense resistor R146 that makes drop of 62.5 mV at full load and 0 mV at no load.

Figure 3. Load Regulation is 12.5 mV/A

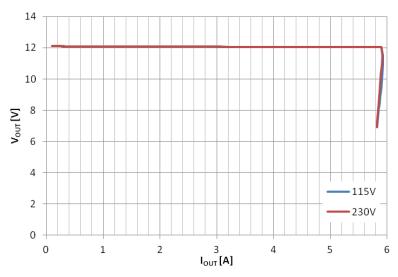

#### **Load Characteristic**

The following load characteristic shows how current limitation works. When the output current reaches 5.9 A, the

output voltage starts to become limited to keep the current at a level given by the sense resistor R146 and voltage threshold of 62.5 mV at current OTA sensing pin ISNS.

Figure 4. Load Characteristic

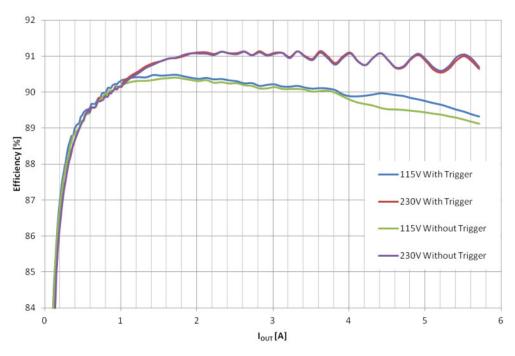

## **Efficiency**

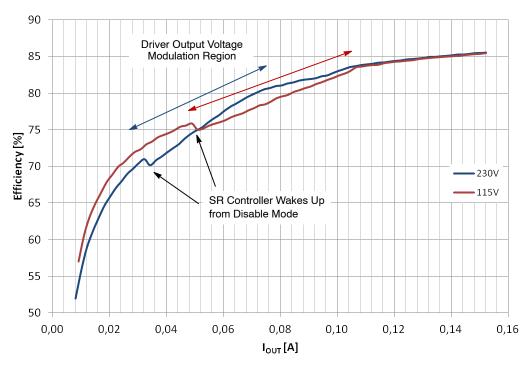

Figure 5. Adapter Efficiency for Low and High Line with or without Triggering

Figure 6. Adapter Efficiency for Low and High Line at Very Low Output Currents, Drop at Efficiency is Caused by Wake Up of Synchronous Rectification Controller

## **Operation at Full Power**

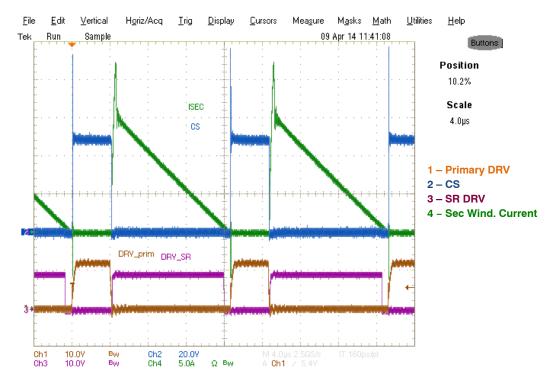

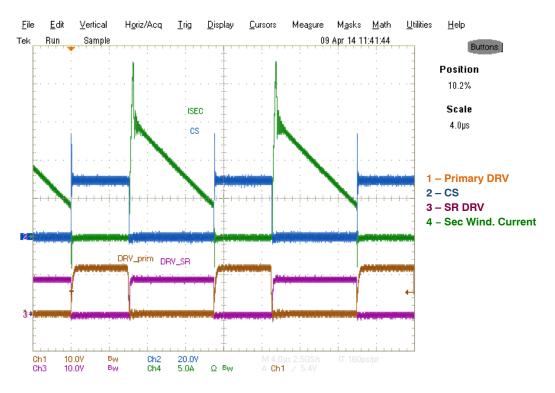

Figure 7.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A, DCM Operation

Figure 8.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A, CCM Operation

## **Output Voltage Ripple**

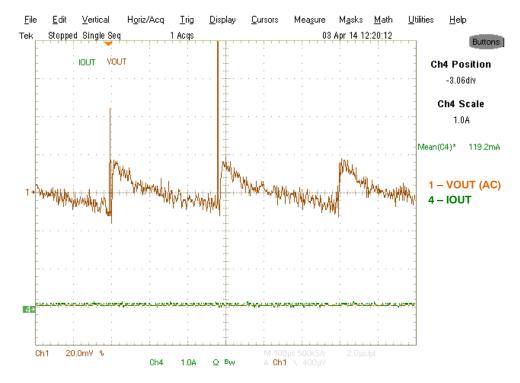

Figure 9.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 100 mA, Primary Controller is in Skip Mode,  $\Delta V_{OUTPK-PK}$  = 30 mV

Figure 10.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 1 A,  $\Delta V_{OUTPK-PK}$  = 20 mV

Figure 11. V<sub>IN</sub> = 230 V<sub>AC</sub>, I<sub>OUT</sub> = 2.5 A,  $\Delta$ V<sub>OUTPK-PK</sub> = 35 mV

Figure 12.  $V_{IN}$  = 230  $V_{AC},\,I_{OUT}$  = 5.5 A,  $\Delta V_{OUTPK-PK}$  = 30 mV

#### **Synchronous Rectification Controller**

The synchronous rectification controller monitors the voltage across the SR transistor (drain to source). When the drain voltage is negative, current flows from the source to the drain through transistor's body diode and the SR controller should turn-on the SR transistor to minimize the voltage drop across it. Eventually the current through the transistor decreases and the voltage drop across the SR transistor falls to zero. When the voltage across the SR

transistor is zero then the SR controller turns-off transistor. The SR transistor can also be turned off when the Trig signal is used.

#### Guard Intervals (min-ton, min-toff times)

There has to be applied guard intervals after the transistor turns-on or turns-off since ringing appears after these transitions. Guard intervals have to be longer than this ringing to assure correct operation.

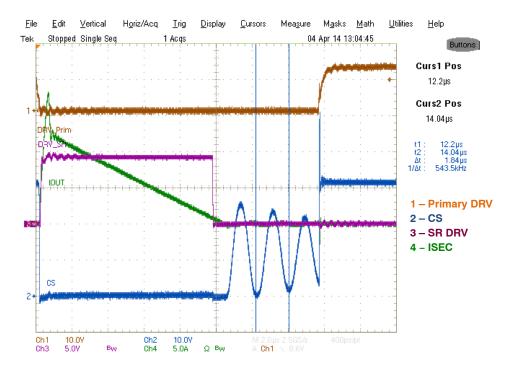

Figure 13.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A – Turn-on Ringing at SR MOSFET, this Time has to be Covered by Guard Interval of min-ton to Secure that SR MOSFET would be Not Turned-off Incorrectly.

Application has Set min-ton to 1.5  $\mu$ s that is Long Enough

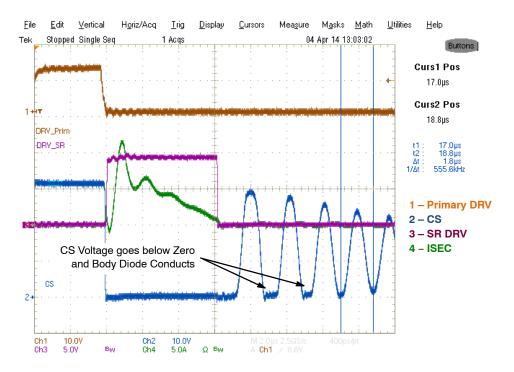

Figure 14.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 3 A, after Demagnetization Ringing Period is 1.8  $\mu$ s. Min-toff has to be Set to Longer Time than this Period to Avoid Incorrect Turn-on when CS Voltage Drops below Turn-on Threshold. Evaluation Board has Set this Time to 2.2  $\mu$ s

Figure 15.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 0.1 A, after Demagnetization Ringing. If Incorrect min-toff is Set SR Transistor may be Turn-on for at Least min-ton that may Lead in to SR Oscillation

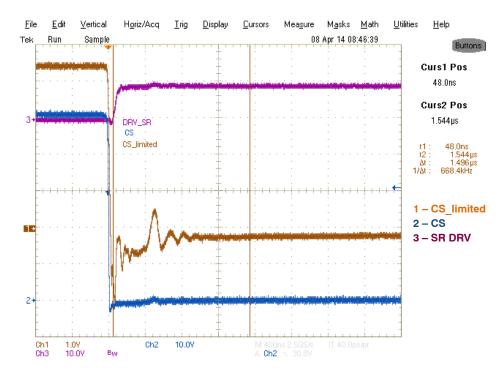

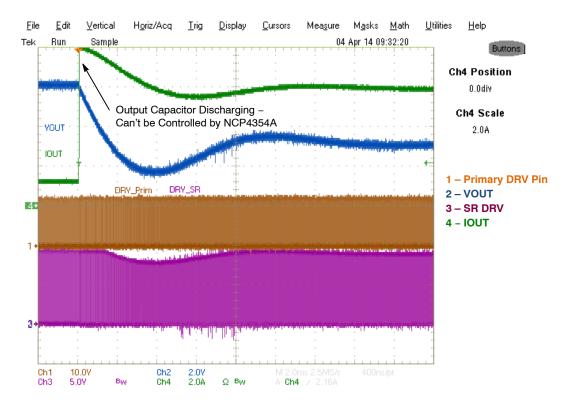

#### Start Up

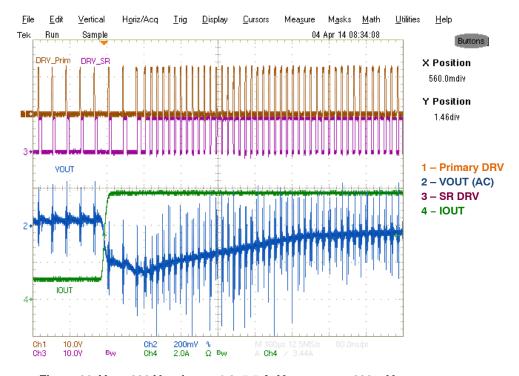

Figure 16.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A, Start-up, SR Controller Starts to Operate Immediately after UVLO Level is Crossed

## **Output Short**

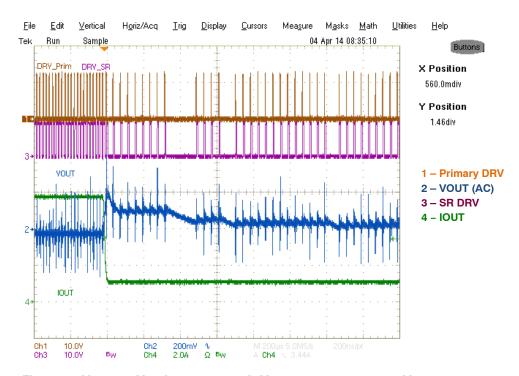

Figure 17.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A to Short, SR Controller Operates Correctly until it has Enough VCC Voltage

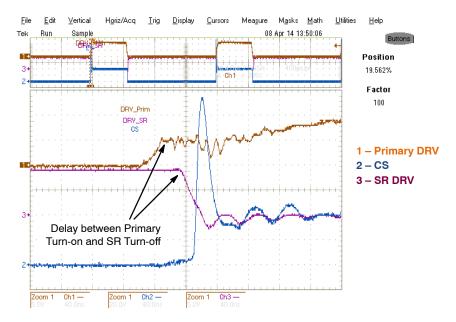

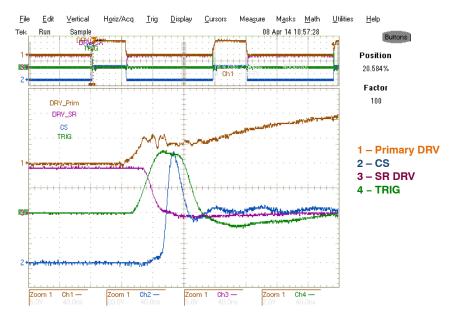

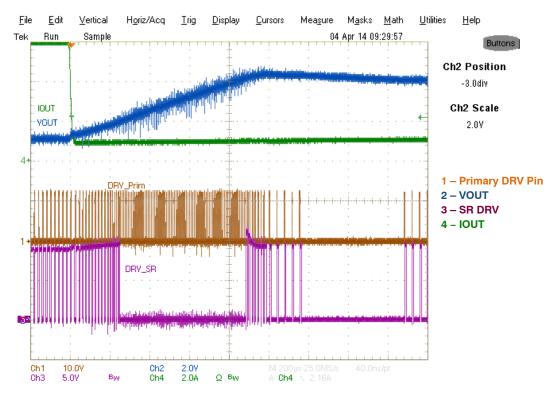

#### Synchronization (Triggering)

This evaluation board includes an option for SR controller synchronization (triggering) with the primary side that may be helpful in CCM operation. The primary switch is turned on sooner than secondary side current drops to the zero in CCM. Typically the SR controller detects zero voltage drop (zero current) through SR transistor to turn the SR transistor off, but in CCM this happens very fast, right after the primary switch is turned on (current changes its direction). To prevent cross—conduction from happening there exists an

option that transfers information about primary switch turn-on to secondary side where the SR controller immediately turns off SR transistor before zero current is detected. This improves efficiency and decreases voltage peak at SR transistor. It may be advantageous to send information to the secondary side about primary turn-on in advance, but this information is not easily accessible. One way is to postpone the pulse to the primary switch and send an un-delayed pulse to the secondary side.

Figure 18.  $V_{IN}$  = 180  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A, SR Transistor is Turned-off after Primary Side is Turned-on and Shot through Condition Occurs

Figure 19.  $V_{IN}$  = 180  $V_{AC}$ ,  $I_{OUT}$  = 5.8 A, Information about Primary Turn-on is Transferred to Secondary Side through Small Pulse Transformer to TRIG Pin that Immediately Turns SR Off and Minimize Shot Through Time (Higher Efficiency, Lower Voltage Peak)

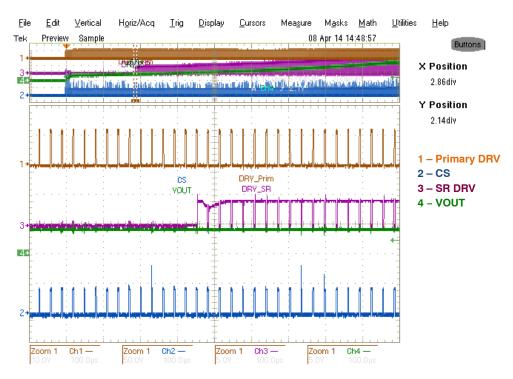

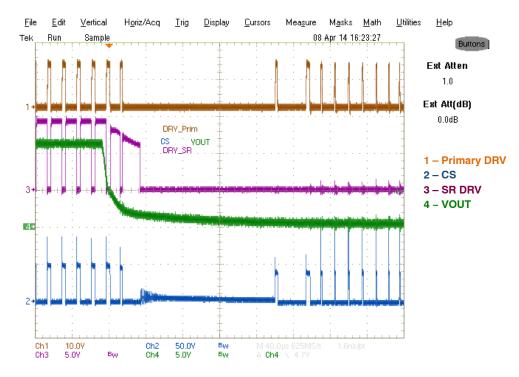

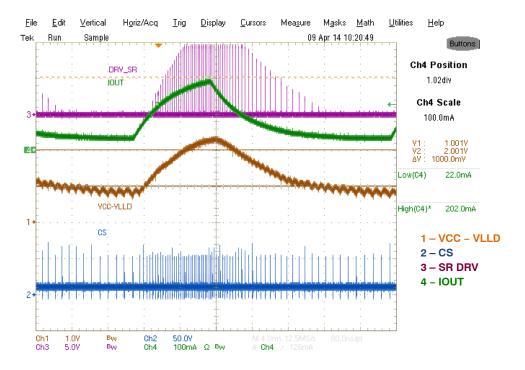

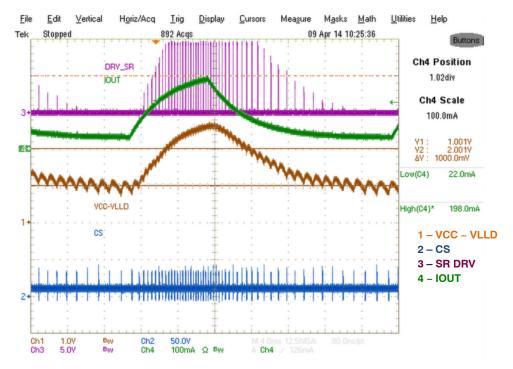

#### **Driver Voltage Modulation**

Figure 20.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 22–202 mA, SR Controller Driver Output Voltage is Modulated Accordingly to Load Current through LLD Pin. Regulation Range is 1 to 2 V. NCP4305 Enters Disable Mode where its Consumption Significantly Decreases when  $V_{CC} - V_{LLD}$  is below 1 V

Figure 21.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 22–202 mA, Thanks to Lower  $V_{IN}$  Operation is Slightly Different so Driver Voltage is Higher at Same Load than for  $V_{IN}$  = 230 V

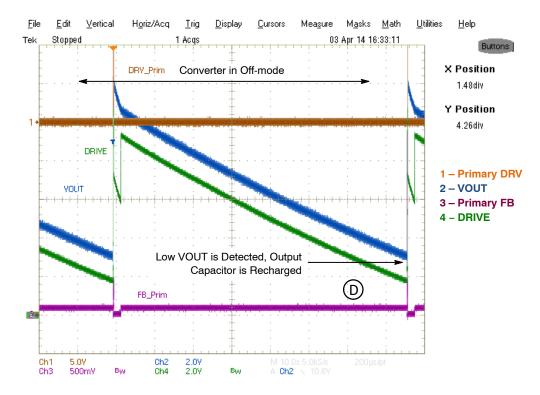

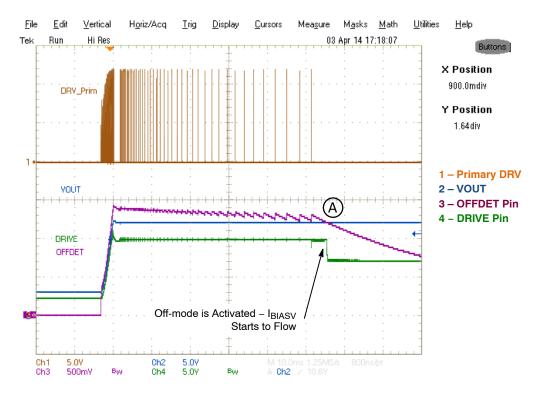

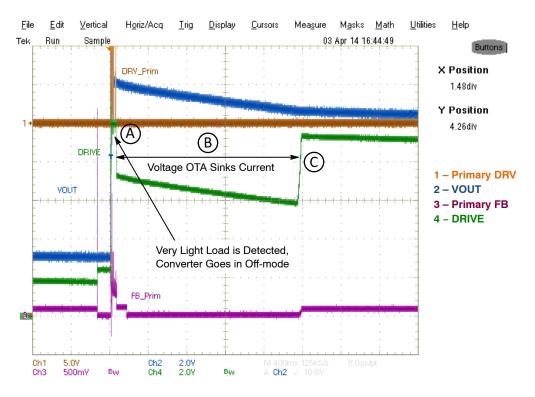

#### **OFF Mode**

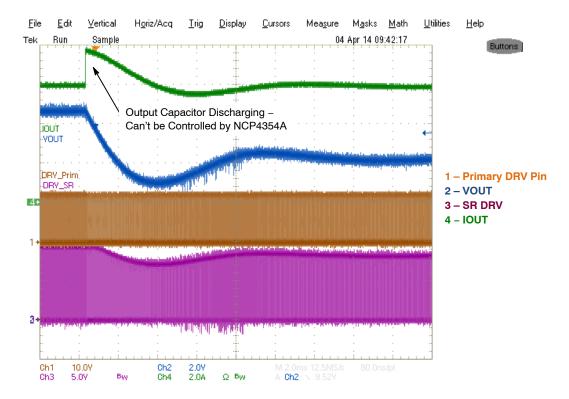

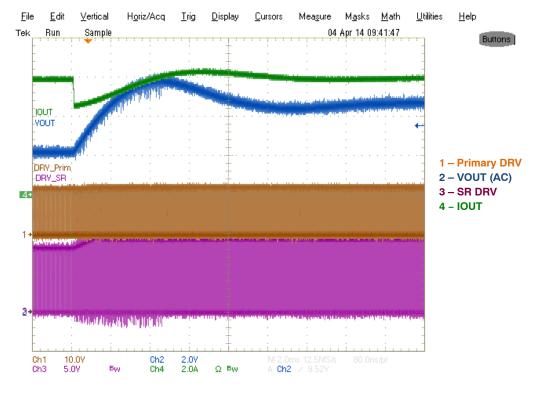

Off-mode is activated, when the output current is below a set level. In this design, the off-mode threshold is set to approximately 3.5 mA. This condition is detected by OFFDET comparator through polarity inverter D118, Q101, R135, R136 with bulk capacitor (C118) and voltage divider (R148 and R151). C118 charging current is limited by R145 to avoid full recharge of C118 by short and sporadic pulses in deep skip mode. When very light load is detected, ONOFF current starts to be sunk by the DRIVE pin. The internal pull up current source is connected to VSNS pin and increases its voltage (Figure 23 A). Thanks to this current, voltage OTA starts to sink limited current to help ONOFF current pull the

primary FB voltage below the off mode detection level (Figure 24 B). When the primary side detects off mode, FB pull up current is decreased to save energy. After that the FB pull down current through optocoupler can be lower. The secondary side stops sinking additional current by voltage OTA after VSNS voltage drops below  $V_{REF}$  to save output capacitor energy (Figure 24 C). Off mode is interrupted when  $V_{OUT}$  falls below the  $V_{MIN}$  threshold that is detected by VMIN comparator (Figure 22 D). ONOFF current then disappears and primary side FB voltage increases. When primary FB voltage is within operation range, the primary controller starts to operate. The output capacitor is then recharged to nominal output voltage.

Figure 22. V<sub>IN</sub> = 230 V<sub>AC</sub>, I<sub>OUT</sub> = 0 A, Off-mode Period t<sub>OFFMODE</sub> = 77 s, V<sub>OUTMIN</sub> = 3 V

Figure 23.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 0 A, Off-mode is Detected when OFFDET Pin Voltage Drops below 1/10 of  $V_{CC}$  =  $V_{OUT}$

Figure 24.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 0 A, ON-mode to OFF-mode Transition. The Voltage Drop on the DRIVE Pin Indicates the Higher Voltage OTA Sink Current (1.5 mA). During this Time, the VSNS Pin is Connected to a 10  $\mu$ A Pull Up Current Source, which Increases the Voltage at VSNS Pin. The OTA Stops Sinking Current 1,900 ms after Transition to Off-mode, because  $V_{SNS}$  Voltage Drops below  $V_{REF}$ . There is only ONOFF current sunk through OPTO after  $V_{SNS} < V_{REF}$

## **Active X2 Capacitor Discharge**

Figure 25.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 1.0 A, when the AC Mains is Disconnected, 125 ms Detection Timer is Started. After this Time, the X2 Cap is Discharged. Discharging Time is much Shorter than Required by Safety Standards (~150 ms << 1 s)

## **Transient Response**

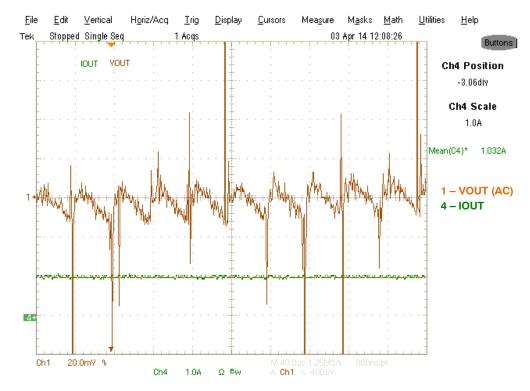

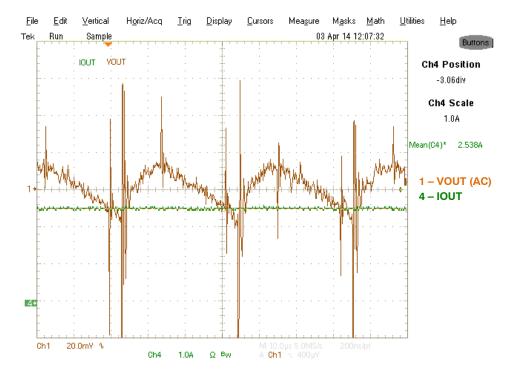

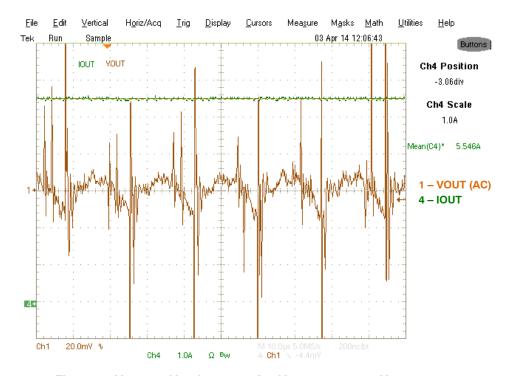

## **Output Current Transients**

Current slew rate is 125 mA/1 µs for all transients.

Figure 26.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 1.0–5.5 A,  $V_{OUT\_DROP}$  = 220 mV

Figure 27.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.5–1.0 A,  $V_{OUT\_OVERSHOOT}$  = 250 mV

## **Output Voltage Transients**

Figure 28.  $V_{IN} = 230 V_{AC}$ ,  $I_{OUT} = 10.5-8.0 A$

Figure 29.  $V_{IN} = 230 V_{AC}$ ,  $I_{OUT} = 8.0-10.5 A$

#### **Output Voltage to Current Transient**

Figure 30. V<sub>IN</sub> = 230 V<sub>AC</sub>, R<sub>OUT</sub> = 10  $\Omega$  to 1.5  $\Omega$

Figure 31. V<sub>IN</sub> = 230 V<sub>AC</sub>, R<sub>OUT</sub> = 1.5  $\Omega$  to 10  $\Omega$

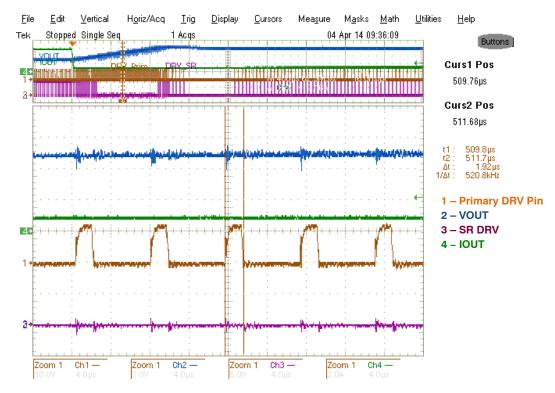

Figure 32.  $V_{IN}$  = 230  $V_{AC}$ ,  $R_{OUT}$  = 1.5  $\Omega$  to 10  $\Omega$  – Detail Shows why SR is Not Turned On. It is Not Turned-on, because Primary On-time is Shorter than Secondary Side Min-off Time (in CCM they Correspond Each Other)

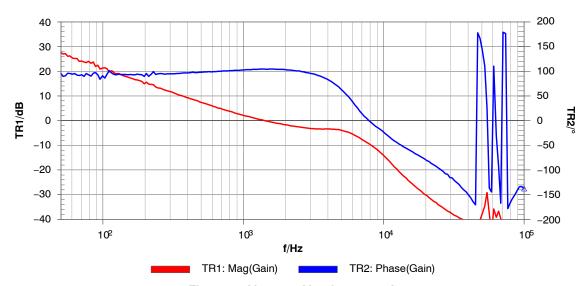

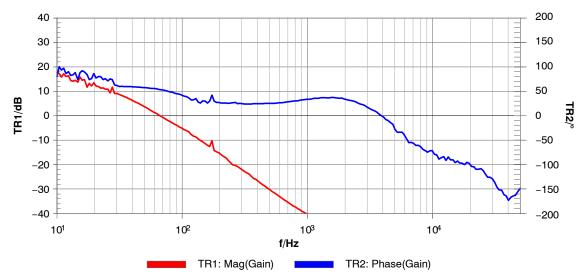

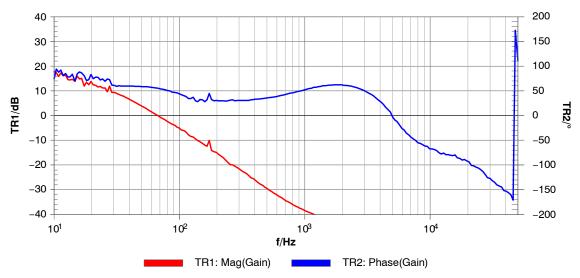

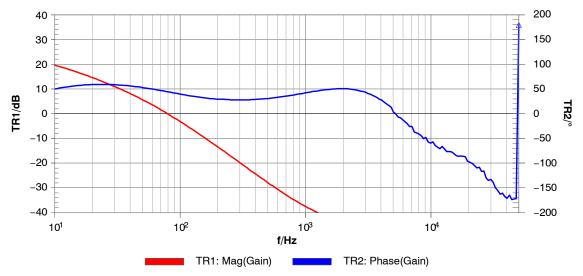

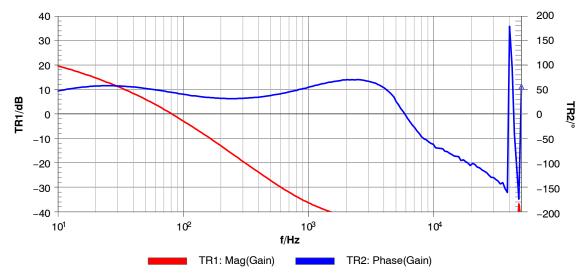

## **Open Loop Transfer Characteristics**

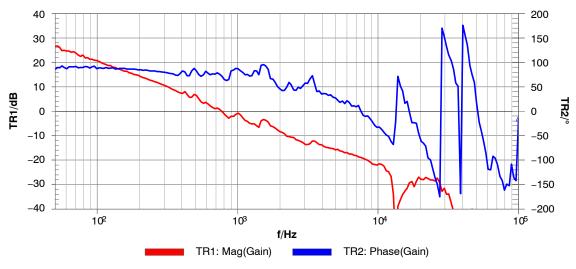

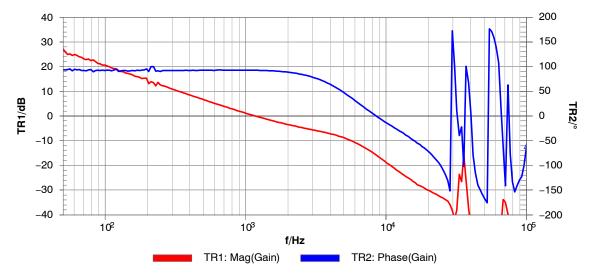

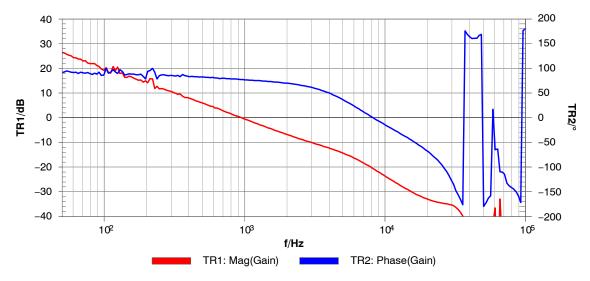

#### **Voltage Control Loop Transfer Characteristic**

- Phase Margin is Never Lower than 70°

- Gain Margin is Never Lower than 10 dB

- Crossover Frequency is between 0.75–1.5 kHz

Figure 33.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 100 mA

Figure 34.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 2.0 A

Figure 35.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 5.5 A

Figure 36.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 100 mA

Figure 37.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 2.0 A

Figure 38.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.5 A

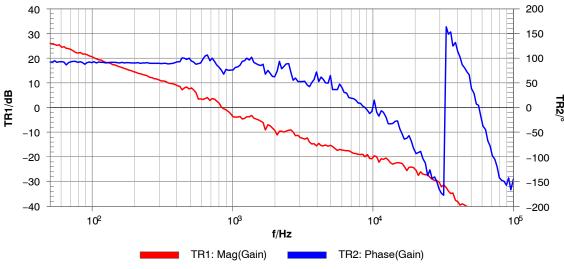

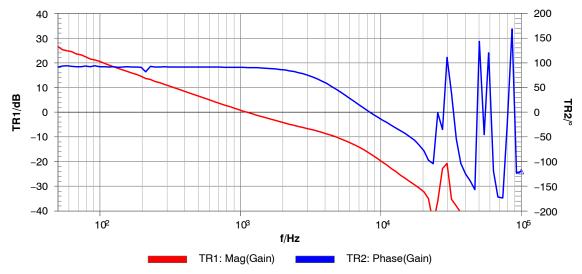

## **Current Control Loop Transfer Characteristic**

- Phase Margin is Never Lower than 43°

- Gain Margin is More than 40 dB

- Crossover Frequency is between 65–100 Hz

Figure 39.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 5.9 A,  $V_{OUT}$  = 10 V

Figure 40.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.9 A,  $V_{OUT}$  = 10 V

Figure 41.  $V_{IN}$  = 115  $V_{AC}$ ,  $I_{OUT}$  = 5.9 A,  $V_{OUT}$  = 8 V

Figure 42.  $V_{IN}$  = 230  $V_{AC}$ ,  $I_{OUT}$  = 5.9 A,  $V_{OUT}$  = 8 V

## **Result Summary**

The NCP4305 with NCP1249 and NCP4354 controllers enables the future of cost effective, easy to design and high efficiency power supplies with very low standby power consumption.

Special thanks go to the companies Coilcraft, Epcos and Würth that provided samples of their components for this demoboard.

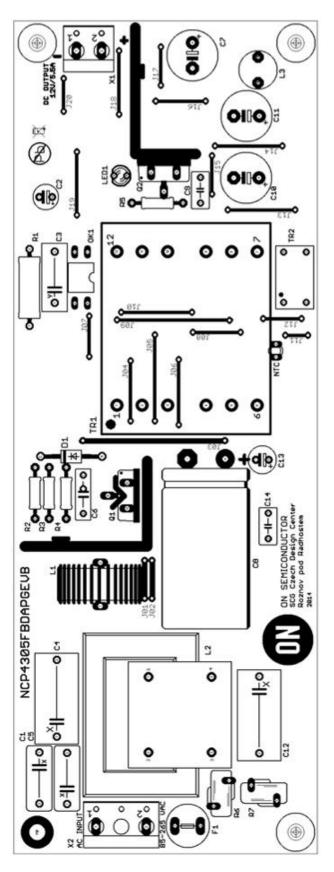

## **Top Side Assembly**

Figure 43. Top Side Assembly

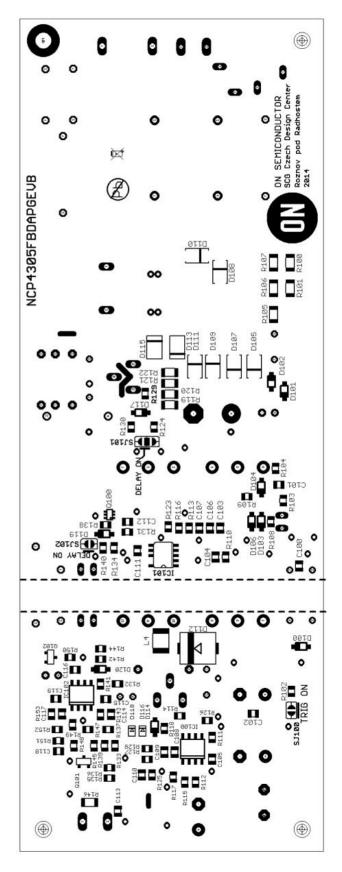

## **Bottom Side Assembly**

Figure 44. Bottom Side Assembly

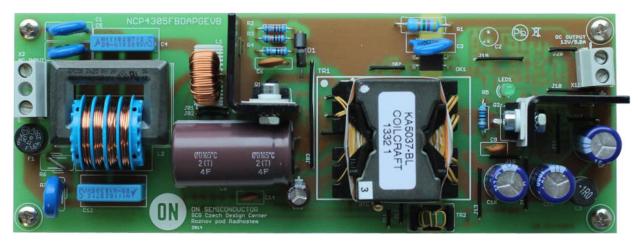

## **Evaluation Board Photo**

Figure 45. Evaluation Board Photo

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

The evaluation board/kit (research and development board/kit) (hereinafter the "board") is not a finished product and is not available for sale to consumers. The board is only intended for research, development, demonstration and evaluation purposes and will only be used in laboratory/development areas by persons with an engineering/technical training and familiar with the risks associated with handling electrical/mechanical components, systems and subsystems. This person assumes full responsibility/liability for proper and safe handling. Any other use, resale or redistribution for any other purpose is strictly prohibited.

THE BOARD IS PROVIDED BY ONSEMI TO YOU "AS IS" AND WITHOUT ANY REPRESENTATIONS OR WARRANTIES WHATSOEVER. WITHOUT LIMITING THE FOREGOING, ONSEMI (AND ITS LICENSORS/SUPPLIERS) HEREBY DISCLAIMS ANY AND ALL REPRESENTATIONS AND WARRANTIES IN RELATION TO THE BOARD, ANY MODIFICATIONS, OR THIS AGREEMENT, WHETHER EXPRESS, IMPLIED, STATUTORY OR OTHERWISE, INCLUDING WITHOUT LIMITATION ANY AND ALL REPRESENTATIONS AND WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, NON-INFRINGEMENT, AND THOSE ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE CUSTOM OR TRADE PRACTICE.

onsemi reserves the right to make changes without further notice to any board.

You are responsible for determining whether the board will be suitable for your intended use or application or will achieve your intended results. Prior to using or distributing any systems that have been evaluated, designed or tested using the board, you agree to test and validate your design to confirm the functionality for your application. Any technical, applications or design information or advice, quality characterization, reliability data or other services provided by **onsemi** shall not constitute any representation or warranty by **onsemi**, and no additional obligations or liabilities shall arise from **onsemi** having provided such information or services.

onsemi products including the boards are not designed, intended, or authorized for use in life support systems, or any FDA Class 3 medical devices or medical devices with a similar or equivalent classification in a foreign jurisdiction, or any devices intended for implantation in the human body. You agree to indemnify, defend and hold harmless onsemi, its directors, officers, employees, representatives, agents, subsidiaries, affiliates, distributors, and assigns, against any and all liabilities, losses, costs, damages, judgments, and expenses, arising out of any claim, demand, investigation, lawsuit, regulatory action or cause of action arising out of or associated with any unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of any products and/or the board.

This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and may not meet the technical requirements of these or other related directives.

FCC WARNING – This evaluation board/kit is intended for use for engineering development, demonstration, or evaluation purposes only and is not considered by **onsemi** to be a finished end product fit for general consumer use. It may generate, use, or radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment may cause interference with radio communications, in which case the user shall be responsible, at its expense, to take whatever measures may be required to correct this interference.

onsemi does not convey any license under its patent rights nor the rights of others.

LIMITATIONS OF LIABILITY: **onsemi** shall not be liable for any special, consequential, incidental, indirect or punitive damages, including, but not limited to the costs of requalification, delay, loss of profits or goodwill, arising out of or in connection with the board, even if **onsemi** is advised of the possibility of such damages. In no event shall **onsemi**'s aggregate liability from any obligation arising out of or in connection with the board, under any theory of liability, exceed the purchase price paid for the board, if any.

The board is provided to you subject to the license and other terms per **onsemi**'s standard terms and conditions of sale. For more information and documentation, please visit www.onsemi.com.

#### **ADDITIONAL INFORMATION**

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales