## Bi-CMOSIC 1-chip Tuner IC with built-in FLL for Home Stereo System

#### Overview

The LV23401V is a AM/FM one-chip tuner IC for home stereo system.

#### **Functions**

- AM tuner

- FM tuner

- MPX stereo decoder

- FLL tuning system

#### Features

- All the adjustment work of external parts is unnecessary.

- CCB control with easy command base

- External parts are reduced by LOW-IF frequency (FM=225kHz, AM=53kHz) adoption.

- The high sensitivity reception is achieved in low noise MIX input circuit.

- All bands of Japan-U.S.-Euro can be received by the soft program change (76MHz to 108MHz).

- With built-in FLL(Frequency Locked Loop) tune function

- Soft mute and stereo blend function (seven stages programmed control possible)

- With built-in adjacent channel obstruction removal function

- With built-in stereo pilot cancellation function

- For EN55020-S1 standard (European immunity)

- With built-in power save function

#### **Specifications**

#### **Maximum Ratings** at $Ta = 25 \ ^{\circ}C$

| Parameter                   | Symbol                | Conditions                   | Ratings        | Unit |

|-----------------------------|-----------------------|------------------------------|----------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max   | Analog block supply voltage  | 10.0           | V    |

| Maximum output voltage      | V <sub>O</sub> max    | Digital block supply voltage | 4.5            | V    |

| Maximum input voltage       | V <sub>IN</sub> 1 max | CE, DI, CL                   | *1) Vref2+0.35 | V    |

|                             | V <sub>IN</sub> 2 max | CLK IN                       | 4.5            | V    |

| Allowable power dissipation | Pd max                | Ta ≤ 70 °C *2)               | 450            | mW   |

| Operating temperature       | Topr                  |                              | -20 to +70     | °C   |

| Storage temperature         | Tstg                  |                              | -40 to +125    | °C   |

\*1) Vref2 = 22 pin voltage

\*2) When mounted on the specified printed circuit board (114.3mm × 76.1mm × 1.6mm), glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Operating Condition** at Ta = 25 °C

| Parameter                      | Symbol             | Conditions                    | Ratings    | Unit |

|--------------------------------|--------------------|-------------------------------|------------|------|

| Recommended supply voltage     | Vcc                | Analog block supply voltage   | 9.0        | V    |

| Operating supply voltage range | V <sub>CC</sub> op | Resister 1Eh Bit 1(LEVSHIF)=0 | 4.5 to 6.5 | V    |

|                                |                    | Resister 1Eh Bit 1(LEVSHIF)=1 | 8.5 to 9.5 | V    |

\* Stabilize the service voltage so as not to cause the voltage charge by the noise etc.

#### Interface block allowable operation range at Ta = -20 to $+70^{\circ}C$ , $V_{SS} = 0V$

| Deservation                    | Querrahad         | bol Conditions                                  |          | Ratings |       |      |  |

|--------------------------------|-------------------|-------------------------------------------------|----------|---------|-------|------|--|

| Parameter                      | Symbol            | Conditions                                      | min      | typ     | max   | Unit |  |

| Input "H" level voltage        | V <sub>I</sub> H1 | CE, DI, CL                                      | 2.3      |         | 3.435 | V    |  |

|                                | V <sub>I</sub> H2 | CLK IN                                          | 2.3      |         | 3.435 | V    |  |

| Input "L" level voltage        | V <sub>I</sub> L1 | CE, DI, CL                                      | 0        |         | 0.5   | V    |  |

|                                | V <sub>I</sub> L2 | CLK IN                                          | 0        |         | 0.3   | V    |  |

| Output voltage                 | VO                | D0                                              | 0        |         | 4.0   | V    |  |

| Crystal frequency              | fIN               | CLK IN                                          |          | 32.768  |       | kHz  |  |

| Crystal frequency deflection   | f devi1           | For the standard European immunity              | -50      |         | +50   | ppm  |  |

|                                | f devi2           | When standard non-corresponds European immunity | -150     |         | +150  | ppm  |  |

| Crystal vibrator load capacity | CL                | *                                               | * 4 12.5 |         | pF    |      |  |

\* The evaluation request to the crystal maker is recommended because it changes by the substrate and the circuit constant used.

#### **Operating Characteristics** at Ta = 25°C, $V_{CC}$ = 9.0V with the designated circuit.

| Descentes                                                  | O maked                     | Conditions                                                  |              | Ratings               |           | Unit                  |  |

|------------------------------------------------------------|-----------------------------|-------------------------------------------------------------|--------------|-----------------------|-----------|-----------------------|--|

| Parameter                                                  | Symbol                      | Conditions                                                  |              | typ                   | max       | Unit                  |  |

| Current drain                                              | I <sub>CC</sub> FM          | No input in FM mode. 15 pin supply current.                 | 25           | 35                    | 45        | mA                    |  |

| (at no input)                                              | ICCAM                       | No input in AM mode. 15 pin supply current.                 | 14           | 24                    | 34        | mA                    |  |

| Power save current drain                                   | I standby                   | 15 pin supply current<br>power save : Register 1Fh_bit0 = 0 |              | 0.25                  | 0.7       | mA                    |  |

| V <sub>DD</sub> output voltage                             | V <sub>DD</sub>             | 22 pin voltage (reference value)                            | (2.772)      | 3.3                   | (3.435)   | V                     |  |

| V <sub>DD</sub> drop-out voltage                           |                             |                                                             |              | 0.15                  |           | V                     |  |

|                                                            |                             | = off, Resister 1Eh Bit 1(LEVSHIF) = 1, 9 pin outp          | out, IHF-BPF | 17                    | 24        | dDuil/                |  |

|                                                            |                             | 37.5kHz dev., Pilot = 7.5kHz dev.                           |              |                       |           |                       |  |

| S/N 50dB Sensitivity                                       | SN50                        | Input level that becomes S/N=50dB                           |              | 17                    | 24        | dBµV                  |  |

| /N 30dB Sensitivity SN30 Input level that becomes S/N=30dB |                             |                                                             |              |                       |           |                       |  |

| ,                                                          |                             | Input level that becomes S/N=30dB                           |              | 12                    | 18        | dBµV                  |  |

| IHF Sensitivity                                            | IHF                         | Input level that becomes S/N=30dB                           |              | 12<br>12              | 18<br>20  | dBµV<br>dBµV          |  |

| IHF Sensitivity<br>Signal-to-noise ratio                   |                             |                                                             | 62           |                       |           |                       |  |

|                                                            | IHF                         | Input level that becomes THD=3%                             | 62<br>58     | 12                    |           | dBµV                  |  |

|                                                            | IHF<br>SN                   | Input level that becomes THD=3%<br>MONO                     |              | 12<br>70              |           | dBµV<br>dB            |  |

| Signal-to-noise ratio                                      | IHF<br>SN<br>SN-ST1         | Input level that becomes THD=3%<br>MONO<br>STEREO           |              | 12<br>70<br>66        | 20        | dBµV<br>dB<br>dB      |  |

| Signal-to-noise ratio                                      | IHF<br>SN<br>SN-ST1<br>THD1 | Input level that becomes THD=3%<br>MONO<br>STEREO<br>MONO   |              | 12<br>70<br>66<br>0.5 | 20<br>1.5 | dBµV<br>dB<br>dB<br>% |  |

Continued on next page.

| Parameter                                    | Symbol                           | Conditions                                                                                                      |       | Ratings |       | Unit  |

|----------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|---------|-------|-------|

| Farameter                                    | Symbol                           | Conditions                                                                                                      | min   | typ     | max   | Unit  |

| Demodulation output                          | V <sub>O</sub> 0                 | MONO, V <sub>O</sub> L = 0 (reference value)                                                                    | (218) | (327)   | (489) | mVrms |

|                                              | V <sub>O</sub> 1                 | MONO, V <sub>O</sub> L = 1 (reference value)                                                                    | (291) | (436)   | (652) | mVrms |

|                                              | V <sub>O</sub> 2                 | MONO, V <sub>O</sub> L = 2 (reference value)                                                                    | (366) | (549)   | (821) | mVrms |

|                                              | V <sub>O</sub> 3                 | MONO, V <sub>O</sub> L = 3 (reference value)<br>*In-house management = Typ ± 3.0dB                              | 518   | 775     | 1160  | mVrms |

| MPX output                                   | V <sub>O</sub> _MPX              | 6 pin output                                                                                                    | 100   | 200     | 300   | mVrms |

| Channel balance                              | СВ                               | 10 pin output / 9 pin output                                                                                    | -1    | 0       | +0    | dB    |

| SD operation level                           | SD                               | FS_S = 4                                                                                                        | 17    | 25      | 33    | dBµV  |

| Stereo operation level                       | ST                               | FS_S = 4                                                                                                        | 17    | 25      | 33    | dBµV  |

| Stereo separation                            | Sep                              | Both channels of 9 pins and 10 pins are<br>measured.<br>*In-house management value ≥25dB                        | 25    | 40      |       | dB    |

| De-emphasis deflection                       | Deemp50                          | fm = 10kHz, 15kHz LPF OFF                                                                                       | -12.5 | -10     | -7.5  | dB    |

|                                              | Deemp75                          | fm = 10kHz, 15kHz LPF OFF                                                                                       |       | -13     |       | dB    |

| Carrier leakage                              | CL                               | STEREO S/N, 15kHz LPF OFF                                                                                       | 30    | 40      |       | dB    |

| Pilot margin<br>(Pilot lighting sensitivity) | ST-ON   L+R = 67.5kHz, Pilot-mod |                                                                                                                 | 0.6   |         | 5.5   | %     |

| AM suppression ratio                         | AMR                              | 400Hz AM 30% mod.                                                                                               | 40    | 65      |       | dB    |

| Mute attenuation                             | MUTE                             |                                                                                                                 | 60    | 75      |       | dB    |

|                                              |                                  | JBμV, fm = 400Hz, 30% mod, IF = 53kHz, BW = 50<br>Bit 1(LEVSHIF) = 1, 9 pin output, 15kHz LPF OFF               | %     |         |       |       |

| S/N 20dB Sensitivity                         | SN20                             | Input level that becomes S/N=20dB                                                                               |       | 49      | 65    | dBµV  |

|                                              | SN20-L                           | fc = 603kHz (reference value)                                                                                   |       | (55)    | (65)  | dBµV  |

|                                              | SN20-H                           | fc = 1404kHz (reference value)                                                                                  |       | (49)    | (65)  | dBµV  |

| Signal-to-noise ratio                        | SN                               |                                                                                                                 | 42    | 50      |       | dB    |

| Total harmonic distortion                    | THD1                             |                                                                                                                 |       | 0.6     | 2.8   | %     |

|                                              | THD2                             | V <sub>IN</sub> = 104dBµV                                                                                       |       | 0.8     | 2.8   | %     |

| Detected output                              | V <sub>O</sub> 0                 | VOL = 0 (reference value)                                                                                       | (55)  | (78)    | (109) | mVrms |

|                                              | V <sub>O</sub> 1                 | VOL = 1 (reference value)                                                                                       | (69)  | (98)    | (138) | mVrms |

|                                              | V <sub>O</sub> 2                 | VOL = 2 (reference value)                                                                                       | (87)  | (123)   | (173) | mVrms |

|                                              | V <sub>O</sub> 3                 | VOL = 3                                                                                                         | 110   | 155     | 218   | mVrms |

| Channel balance                              | СВ                               | 10 pin output / 9 pin output                                                                                    | -1    | 0       | +1    | dB    |

| AGC response                                 | AGC1                             | Input level difference that output level becomes<br>-10dB. Soft mute = 3 (reference value)                      | (52)  | (62)    |       | dB    |

|                                              | AGC2                             | Soft mute = 4                                                                                                   | 47    | 57      |       | dB    |

| _                                            | Hi-cut                           | fm = 4kHz                                                                                                       | -22   | -17     | -12   | dB    |

| Frequency response                           |                                  | i de la constanción d |       |         |       |       |

| SD operation level                           | SD                               | AGC = ON, FS = 4<br>*In-house management =46 to 65dBµV                                                          | 46    | 54      | 65    | dBµV  |

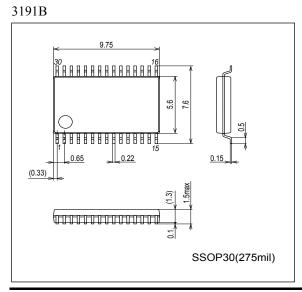

## Package Dimensions

#### **Pin function**

| pin | pin name            | Description                    | Remark                                                                                 | DC_bias |

|-----|---------------------|--------------------------------|----------------------------------------------------------------------------------------|---------|

| 1   | AM ANT              | AM antenna                     | It connects it to 2pin through the matching coil or the bar antenna.                   |         |

| 2   | AM ref              | AM reference voltage           | It connects it to 1pin through the matching coil or the bar antenna.                   | 2.0V    |

| 3   | AM CAP              | AM capacitor bank              | It connects it to GND through an external inductor of recommendation 240µH.            |         |

| 4   | GND1                | AM antenna GND                 | Connect to GND                                                                         |         |

| 5   | Vref1               | Analog reference voltage       | It connects it to GND through the capacitor of 1µF.                                    |         |

| 6   | MPX OUT             | Detected output                | LC72725 and connection when RDS is used                                                |         |

| 7   | AM AGC              | AM AGC                         | It connects it to GND through the capacitor of $4.7\mu F$                              |         |

| 8   | GND2                | Analog GND                     | Connect to GND                                                                         |         |

| 9   | L OUT               | L-ch audio output              | The DC level changes by setting Resistor 1Eh bit1 (LEVSHIF) to adjust the output level |         |

| 10  | R OUT               | R-ch audio output              | according to the $V_{CC}$ potential.                                                   |         |

| 11  | V <sub>CC</sub> Low | Low voltage mode               | It is short with 15pin when using it with $V_{CC} < 6.0V$ or less.                     |         |

| 12  | AM LCF              | AM low cutting filter          | It connects it to GND through the capacitor of $0.047 \mu F$                           |         |

| 13  | SD OUT              | SD detecting phase output      |                                                                                        |         |

| 14  | ST OUT              | ST detecting phase output      |                                                                                        |         |

| 15  | V <sub>CC</sub>     | Supply voltage                 |                                                                                        |         |

| 16  | CLK IN              | Reference clock input          | The crystal is recommended to be used.                                                 |         |

|     |                     |                                | It is also possible to input directly clock signals (square wave GND standard).        |         |

| 17  | ST ADJ              | Pilot margin adjustment pin    | It connects it to GND through $180 k\Omega$                                            |         |

| 18  | CE                  | address/data switching         |                                                                                        |         |

|     |                     | timing                         |                                                                                        |         |

| 19  | CL                  | Communication clock            |                                                                                        |         |

| 20  | DI                  | Data input                     |                                                                                        |         |

| 21  | DO                  | Data output                    | It connects it to 22 pin through $10k\Omega$                                           |         |

| 22  | Vref2               | V <sub>DD</sub> voltage output | 3.3V voltage output pin.                                                               |         |

|     |                     |                                | It is also possible to supply the current to other IC up to 10mA.                      |         |

| 23  | GND3                | Logic GND                      | Connect to GND                                                                         |         |

| 24  | L1                  | Local oscillation circuit      | It connects it to 25 pin through 33nF.                                                 |         |

| 25  | Vref3               | Reference voltage for local    | It connects it to GND through the capacitor of $100\mu F$                              |         |

|     |                     | oscillation circuit            |                                                                                        |         |

| 26  | L2                  | Local oscillation circuit      | It connects it to 25 pin through 33nF.                                                 |         |

| 27  | SD ADJ              | SD = ON sensitivity            | It connects it to GND through $22k\Omega$                                              |         |

|     |                     | adjustment pin                 |                                                                                        |         |

| 28  | FLL CAP             | FLL low pass filter            | It connects it to 25 pin through 0.1µF.                                                |         |

| 29  | GND4                | FM antenna GND                 | Connect to GND                                                                         |         |

| 30  | FM ANT              | FM antenna                     | Input impedance $75\Omega$ .                                                           |         |

|            | ription of Pin F   |                                               | Internal Equivalent Circuit                                              | Demoder                                                                                                                |

|------------|--------------------|-----------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| <u>No.</u> | Pin name<br>AM-ANT |                                               |                                                                          | Remarks       AM antenna input pin.       The AM antenna coil is connected between 2pin.       R = 100Ω                |

| 2          | AM-REF             | 2.2V                                          | (15<br>2.2V<br>Regulator<br>(2)                                          | AM standard bias pin.                                                                                                  |

| 3          | AM-CAP             | -                                             |                                                                          | AM Tuning for tune pin.<br>(AM Capacitor Bank)                                                                         |

| 4          | GND1               | 0V                                            |                                                                          | Analog (AM_FE) GND pin.                                                                                                |

| 5          | VREF1              | 4.3V                                          | (15<br>4.3V<br>Regulator<br>5                                            | Analog (tuner area) standard bias pin.<br>VREF = 4.3V                                                                  |

| 6          | MPX-OUT            | 2.5V                                          |                                                                          | FM demodulation output pin.<br>R1 = $100\Omega$<br>R2 = $23k\Omega$<br>R3 = $1k\Omega$                                 |

| 7          | AM RF-AGC          | -                                             | $\begin{array}{c} R2 \\ R2 \\ R4 \\ R1 \\ R3 \\ m \\ m \\ m \end{array}$ | AGC pin for AM-RF department Gain control<br>R1 = $2M\Omega$<br>R2 = $5k\Omega$<br>R3 = $250\Omega$<br>R4 = $1k\Omega$ |

| 8          | GND2               | 0V                                            |                                                                          | Analog (tuner) GND pin.                                                                                                |

| 9<br>10    | L-OUT<br>R-OUT     | 2.5V<br>(It is 3.3V<br>for<br>LEVSHIF =<br>1) |                                                                          | L-ch (R-ch) output pin.<br>R = 100 $\Omega$<br>R <sub>OUT</sub> = 150 $\Omega$                                         |

Continued on next page.

Continued from preceding page.

| No. | Pin name             | Voltage (V)     | Internal Equivalent Circuit                                                  | Remarks                                                                                                                                                  |

|-----|----------------------|-----------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | V <sub>CC</sub> -Low | -               | (15)<br>(1)<br>Regulator                                                     | It is short 11pin with 15pin when using it with $V_{\mbox{CC}} < 6.0 V.$                                                                                 |

| 12  | AM LCF               | 2.2V            | $\begin{array}{c} \\ 12 \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | AM Low-cut Filter pin.<br>R1 = $250\Omega$<br>R2 = $100k\Omega$<br>R3 = $100k\Omega$<br>R4 = $50k\Omega$<br>R5 = $50k\Omega$                             |

| 13  | SD-OUT               | V <sub>DD</sub> | 22<br>R<br>SD<br>SW<br>(3)<br>m                                              | SD indicator output pin.<br>Active Low output<br>R = 100kΩ                                                                                               |

| 14  | ST-OUT               | V <sub>DD</sub> | R<br>R<br>ST<br>SW<br>T<br>T                                                 | FM stereo indicator output pin.<br>Active Low output<br>R = 100kΩ                                                                                        |

| 15  | V <sub>CC</sub>      | Vcc             |                                                                              | Analog area supply voltage pin.<br>8.5 to 9.5V are impressed at Resister 1Eh bit<br>1(LEVSHIF) = 1, and it is short at "0" with<br>V <sub>CC</sub> _Low. |

| 16  | CLK_IN               | 2.1V            | 16-Crystal<br>oscillator                                                     | Clock connection pin for internal standard.<br>32.768kHz crystal is connected.<br>$R = 100\Omega$                                                        |

| 17  | ST-ADJ               | 3.7V            |                                                                              | Stereo lighting sensitivity adjustment pin.<br>It connects it to GND through $180k\Omega$ .<br>R = $24k\Omega$                                           |

| 18  | CE                   | -               |                                                                              | Chip enable pin.<br>Pin assumed to be high-level when serial data<br>input (DI) and serial data output (DO).                                             |

| 19  | CL                   | -               |                                                                              | Data clock input pin<br>Clock that takes data and synchronization<br>when serial data input (DI) and serial data<br>output (DO).                         |

Continued on next page.

| Continu  | ed from preceding pa | age.        |                                                  |                                                                                                           |

|----------|----------------------|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| No.      | Pin name             | Voltage (V) | Internal Equivalent Circuit                      | Remarks                                                                                                   |

| 20       | DI                   | _           |                                                  | Serial data input pin.<br>Input pin of the serial data transmitted by<br>controller.                      |

| 21       | DO                   | _           |                                                  | Serial data output pin.<br>Serial data output pin to controller.                                          |

| 22       | V <sub>DD</sub>      | 3.3V        |                                                  | Logic area standard bias pin.<br>V <sub>DD</sub> = 3.3V                                                   |

| 23       | GND3                 | 0V          |                                                  | Digital area (control block) GND pin.                                                                     |

| 24<br>26 | L1<br>L2             | 4.3V        | CAP<br>BANK<br>#<br>BANK<br>BANK<br>BANK<br>BANK | OSC coil connect pin.<br>33nH is connected between 25pin.                                                 |

| 25       | VREF2                | 4.3V        | 12<br>4.3V<br>Regulator<br>25                    | OSC area standard bias pin.<br>VREF2 = 4.3V                                                               |

| 27       | SD-ADJ               | 0.1V        |                                                  | SD lighting sensitivity adjustment pin.<br>It connects it to GND through $22k\Omega$ .<br>R = $100\Omega$ |

| 28       | FLL-CAP              | _           |                                                  | LPF pin for internal FLL control.<br>R = 80kΩ                                                             |

| 29       | GND4                 | 0V          |                                                  | Analog (FMRF) GND pin.                                                                                    |

| 30       | FM-ANT               | 0.9V        |                                                  | FM antenna input pin.<br>R = 1.5kΩ<br>RIN = 75Ω                                                           |

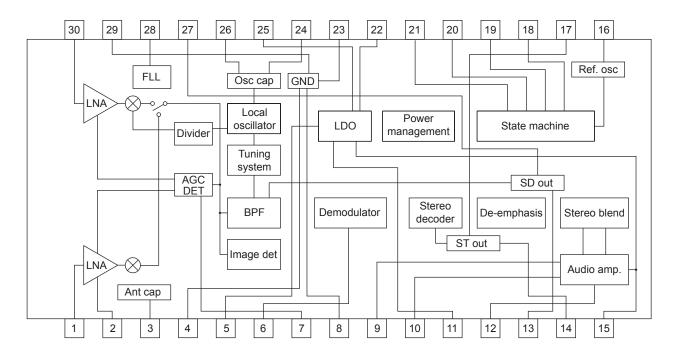

#### **Block Diagram**

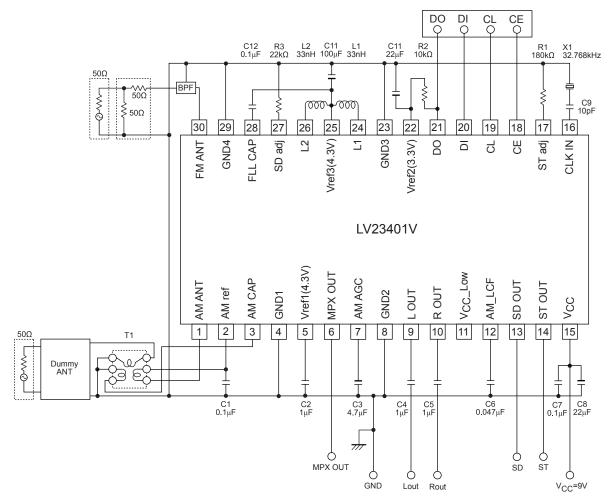

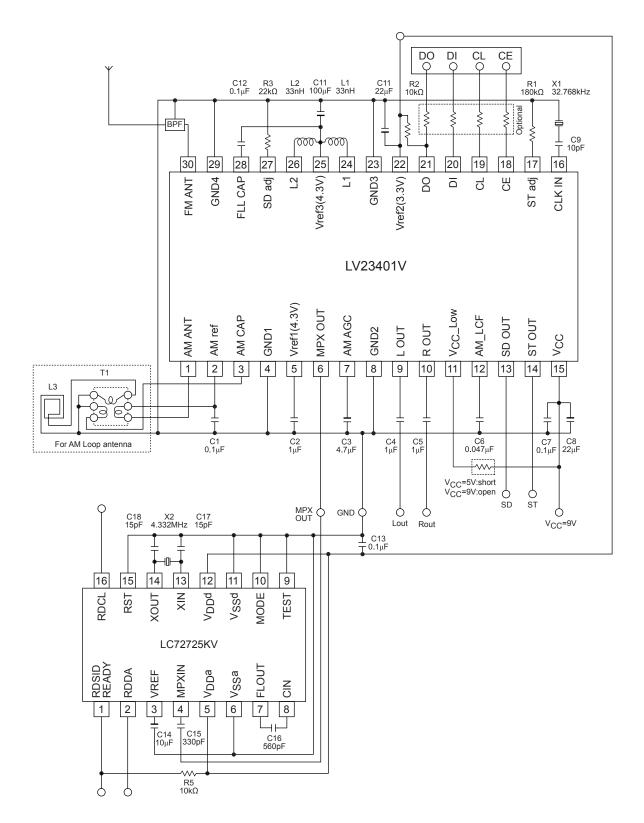

#### **Measurement circuit**

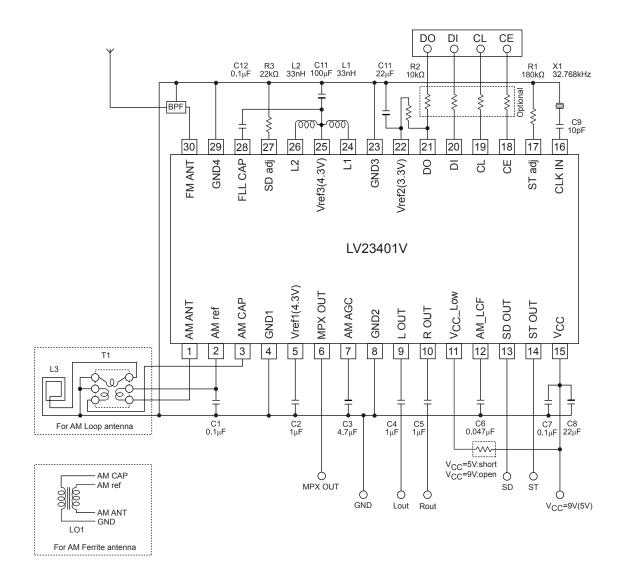

#### Example of applied circuit 2

#### **Used parts**

| Component | Parameter               | Value     | Tolerance | Туре              | Supplier  |

|-----------|-------------------------|-----------|-----------|-------------------|-----------|

| L1        | Local Osc Coil          | 33nH      | 5%        | LL2012-FHL33NJ    | TOKO      |

| L2        | Local Osc Coil          | 33nH      | 5%        | LL2012-FHL33NJ    | ТОКО      |

| L3        | AM Loop antenna         | 18.1µH    | 5%        | 4910-CSL18R1JN1   | SAGAMI    |

|           |                         |           |           | A90326057         | COILS     |

| T1        | AM RF matching          | -         | -         | #7003RNS-A1109YZS | ТОКО      |

| C1        | Ripple Filter           | 0.1µF     |           |                   |           |

| C2        | Ripple Filter           | 1µF       |           |                   |           |

| C3        | AM RF AGC Capacitor     | 4.7µF     |           |                   |           |

| C4        | Coupling Capacitor      | 1µF       |           |                   |           |

| C5        | Coupling Capacitor      | 1µF       |           |                   |           |

| C6        | AM Low-cut Filter       | 0.047µF   |           |                   |           |

| C7        | Supply Bypass Capacitor | 0.1µF     |           |                   |           |

| C8        | Supply Bypass Capacitor | 22µF      |           |                   |           |

| С9        | Correction Capacitor    | 10pF      |           |                   |           |

| C10       | Supply Bypass Capacitor | 22µF      |           |                   |           |

| C11       | Ripple Filter           | 0.1µF     |           |                   |           |

| C12       | Osc Filter              | 0.1µF     |           |                   |           |

| C13       | Ripple Filter           | 0.1µF     |           |                   |           |

| C14       | Ripple Filter           | 10µF      |           |                   |           |

| C15       | Coupling Capacitor      | 330pF     |           |                   |           |

| C16       | Coupling Capacitor      | 560pF     |           |                   |           |

| C17       | Correction Capacitor    | 15pF      |           |                   |           |

| C18       | Correction Capacitor    | 15pF      |           |                   |           |

| R1        | Reference Resistor      | 180Ω      |           |                   |           |

| R2        | Pulled-up Resistor      | 10kΩ      |           |                   |           |

| R3        | Reference Resistor      | 22kΩ      |           |                   |           |

| R4        | Reference Resistor      | 33kΩ      |           |                   |           |

| R5        | Pulled-up Resistor      | 10kΩ      |           |                   |           |

| BPF       | FM ANT BPF              | -         | -         | GFMB7             | SOSHIN    |

| X1        | Crystal                 | 32.768kHz | 100ppm    | VT-200-F(12.5pF)  | SEIKO     |

| X2        | Crystal                 | 4.332MHz  | 100ppm    | AT-49             | DAISHINKI |

| LO1       | AM Ferrite antenna      | 260µH     | TBD       | -                 | -         |

$\ast$  L1 must be used when you receive an Eastern European band (65MHz to 75MHz) and L2 must use 39nH.

\* Inquire match (C9, C17, C18) of X1 and the X2 crystal of the crystal maker together with the substrate used.

#### Interface specification

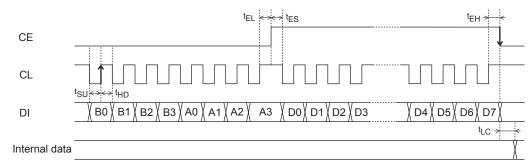

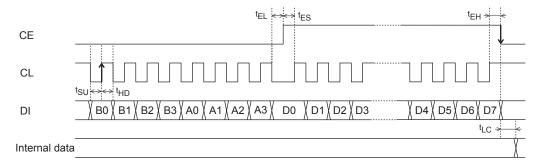

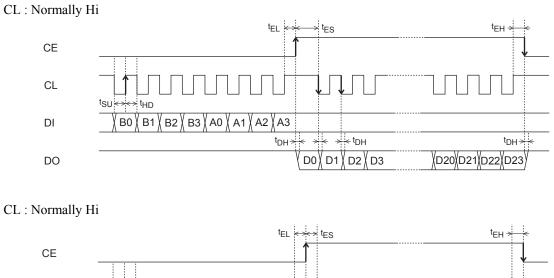

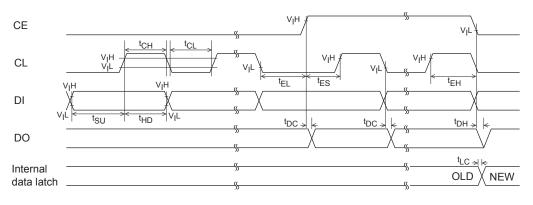

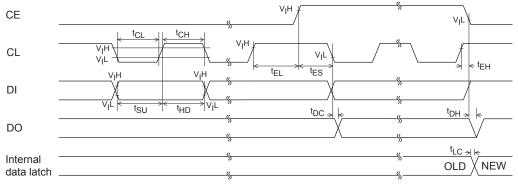

#### 1) LV23401 Interface specification

LV23401 is controlled by the  $C^2B$  (Computer Control Bus) cereal bus format.

$C^2B$  is a bus to achieve it economically surely format as for the communications between LSI in the system with two or more LSI. Because it is single master's system, the processing of a complex arbitration is unnecessary. Therefore, the load of hardware is reduced, and the system configuration that is economically abundant becomes possible. Moreover, neither a lot of kinds of controller and interface doing nor special hardware is easily needed by serial I/O with software. C<sup>2</sup>B is thought between LSI in the equipment, and the communications between equipment that need a long line are not targeted.

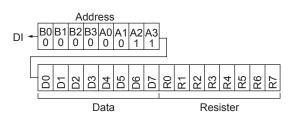

#### 2) C2B data composition

DI control data (cereal data input) composition IN mode

LV23401V is controlled by the bus format composed of the sub-address (register) that stores the data of the device address of 8bit (address) and each 8bit. "C0" is input from LSB to the start as an address when the serial data is input to LV23401V, the device that controls is specified, and the mode as the data input is fixed. It inputs from LSB in order of data (bit setting)  $\rightarrow$  register synchronizing with data clock (CL) after the address is input and the data input can be concluded.

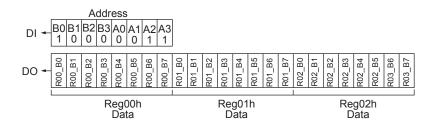

Composition of the DO control data (serial data output) OUT mode

"C1" is input from LSB to the start as an address when the serial data is output from LV23401V, the controlled device is specified, and the mode as the data output is fixed. The subsequent data is output from DO pin synchronizing with lock (CL) after the address is input LSB from one with small register number. The output of data is ended by setting CE pin to Low.

#### 3) Description of the Register of LV23401

#### *Register* 00h – *CHIP\_ID* – *Chip identify register* (*Read-Only*)

| 7                  | 6                        | 5                     | 4       | 3 | 2 | 1 | 0 |  |  |  |  |

|--------------------|--------------------------|-----------------------|---------|---|---|---|---|--|--|--|--|

| ID[7:0]            |                          |                       |         |   |   |   |   |  |  |  |  |

| Bit 7-0 :          | ID[7:0] : 8-bit CHIP ID. |                       |         |   |   |   |   |  |  |  |  |

|                    | LV23400 : 18h            |                       |         |   |   |   |   |  |  |  |  |

| Note : To abort th | ne command, write        | any value in this reg | gister. |   |   |   |   |  |  |  |  |

#### Register 01h - CHIP\_REV - Chip Revision identify resister (Read-Only)

| 7               | 6                             | 5                    | 4       | 3 | 2 | 1 | 0 |  |  |  |  |

|-----------------|-------------------------------|----------------------|---------|---|---|---|---|--|--|--|--|

| Revision[7:0]   |                               |                      |         |   |   |   |   |  |  |  |  |

| Bit 7-0 :       | ID[7:0] : 8-bit Chip revision |                      |         |   |   |   |   |  |  |  |  |

|                 | ES1:00h                       |                      |         |   |   |   |   |  |  |  |  |

| Note : To abort | the command, write            | any value in this re | gister. |   |   |   |   |  |  |  |  |

#### Register 02h - RADIO\_STAT - Radio station status (Read-Only)

| 7               | 6                                 | 5               | 4                       | 3                  | 2                   | 1                   | 0                             |  |  |  |

|-----------------|-----------------------------------|-----------------|-------------------------|--------------------|---------------------|---------------------|-------------------------------|--|--|--|

| IM_STAT         | IM_FS[1:0]                        |                 | MO_ST                   | FS[2:0]            |                     |                     | TUNED                         |  |  |  |

| Bit 7 :         | IM_STAT : State                   | of image evasi  | on code                 |                    |                     |                     |                               |  |  |  |

|                 | 0 = Eternal operati               | on (It is possi | ble to write it.)       |                    |                     |                     |                               |  |  |  |

|                 | 1 = The image eva                 | sion is being p | processed. (Writing i   | s improper.)       |                     |                     |                               |  |  |  |

| Note : This bit | t operates only when R            | esister 14h_bi  | t7 (IM_EVAS) is set     | to "1". The data   | writing processing  | to LV23401 when the | his bit is "1" is prohibited. |  |  |  |

| Bit 6 - 5 :     | IM_FS : Image bu                  | reau electric f | ield strength           |                    |                     |                     |                               |  |  |  |

|                 | 0 : Image bureau n                | one             |                         |                    |                     |                     |                               |  |  |  |

|                 | 1:0                               |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 2:0dB to 10dB co                  | mpared with     | he hope bureau.         |                    |                     |                     |                               |  |  |  |

|                 | 3 : The level of the              | e image bureau  | is +10dB or more s      | tronger than tha   | t of the hope burea | u.                  |                               |  |  |  |

| Bit 4 :         | MO_ST : MONAURAL/STEREO display   |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 0 = Stereo receptio               | on (Compellin   | g the monaural settin   | g is also the san  | ne.)                |                     |                               |  |  |  |

|                 | 1 = Receiving in s                | tereo mode.     |                         |                    |                     |                     |                               |  |  |  |

| Bit 3 - 1 :     | FS[2:0] : Field strength          |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 0 : Field strength < $10 dB\mu V$ |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 1 : Field strength 10 to 20dBµV   |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 2 : Field strength 20 to 30dBµV   |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | •••                               |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 3 : Field strength >              | > 70dBµV        |                         |                    |                     |                     |                               |  |  |  |

| Bit 0 :         | TUNED : Radio-tu                  | uning flag      |                         |                    |                     |                     |                               |  |  |  |

|                 | 0 = No tuning.                    |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 1 = The tuning.                   |                 |                         |                    |                     |                     |                               |  |  |  |

| Note : When t   | the frequency tuning s            | ucceeds, this b | it is set. This flag is | cleared under th   | e following three c | conditions.         |                               |  |  |  |

|                 | 1. $PW_RAD = 0$                   |                 |                         |                    |                     |                     |                               |  |  |  |

|                 | 2. Do the tuning of               | the frequency   | <i>.</i>                |                    |                     |                     |                               |  |  |  |

|                 | 3. When FLL beco                  |                 |                         |                    |                     |                     |                               |  |  |  |

| Only when the   | e TUNED flag is chan              | ged from one    | into 0, the RAD_IF i    | nterrupt flag is a | set.                |                     |                               |  |  |  |

| When the stat   | us of TUNED changes               | s from 0 into o | ne, the interrupt is n  | ot generated.      |                     |                     |                               |  |  |  |

#### Register 04h – TNPL – Tune position low (Read-Only)

| 7                                                       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------------------------------------------------------|---|---|---|---|---|---|---|--|--|

| TUNEPOS[7:0]                                            |   |   |   |   |   |   |   |  |  |

| Bit 7-0: TUNEPOS[7:0] : Current RF frequency (Low 8bit) |   |   |   |   |   |   |   |  |  |

| Register 05h | – TNPH_STAT          | <sup>–</sup> Tune position | n high / status (. | Read-Only)    |      |   |   |

|--------------|----------------------|----------------------------|--------------------|---------------|------|---|---|

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| ERROR[1:0]   |                      | TUNEPOS[12:8               | ]                  |               |      |   |   |

| Bit 7 - 6 :  | ERROR[1:0] : Er      | ror code                   | 1                  |               |      |   |   |

|              | ERROR[1:0]           |                            | Remark             |               |      |   |   |

|              | 0                    |                            | OK, Command e      | nd (No Error) |      |   |   |

|              | 1                    |                            | DAC Limit Error    | -             |      |   |   |

|              | 2                    |                            | Command forced     |               |      |   |   |

|              | 3                    |                            | Command busy (     | executing it) |      |   |   |

| Bit 5 – 0 :  | TUNEPOS[13:8]        | : Current RF freque        | ency (High 5 bit)  |               |      |   |   |

| Register 06h | – COUNT_L –          | Counter low (R             | Read-Only)         |               |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| COUNT[7:0]   |                      | 1                          |                    |               |      | 1 | 1 |

| Bit 7 – 0 :  | COUNT[7:0] : Co      | ounter value (Low 8        | bit)               |               |      |   |   |

| Register 07h | – COUNT_H –          | - Counter High             | (Read Only)        |               |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| COUNT[15:8]  |                      |                            |                    |               |      |   |   |

| Bit 7 – 0 :  | COUNT[15:8]: 0       | Counter value (High        | 8bit)              |               |      |   |   |

| Register 08h | – IF_OSC – D.        | AC for IF OSC              | (Read/Write)       |               |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| IFOSC[7:0]   |                      | ·                          | ·                  |               |      | • |   |

| Bit 7 – 0 :  | IFOSC[7:0] : IF 0    | Dscillator DAC             |                    |               |      |   |   |

| Register 09h | – IFBW – DAC         | C for IF – Filter          | Band width (Re     | ead/Write)    |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| IFBW[7:0]    |                      |                            |                    |               |      |   |   |

| Bit 7 – 0 :  | IFBW[7:0] : IF B     | and-pass Filter Ban        | d DAC              |               |      |   |   |

| Register 0Bh | – STEREO_OS          | SC – DAC for Si            | tereo Decoder (    | OSC (Read/Wri | ite) |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| SDOSC[7:0]   |                      |                            |                    |               |      |   |   |

| Bit 7 – 0 :  | SDOSC[7:0] : Ste     | ereo Decoder Oscilla       | ator DAC           |               |      |   |   |

| Register 0Ch | – RF_OSC – L         | DAC for RF OS              | C (Read/Write)     |               |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| RFCAP[7:0]   |                      |                            |                    |               |      |   |   |

| Bit 7 – 0 :  | RFOSC[7:0] : RF      | Oscillator DAC             |                    |               |      |   |   |

| Register 0Dh | e – RFCAP – RI       | F Cap bank (Red            | ad/Write)          |               |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| RFCAP[7:0]   |                      | ·                          | •                  |               |      |   |   |

| Bit 7 – 0 :  | RFCAP[7:0] : RF      | Oscillator Capacito        | or bank            |               |      |   |   |

| Register 0Eh | – AMCAP1 – A         | AM-ANT Cap be              | ank1 (Read/Wri     | te)           |      |   |   |

| 7            | 6                    | 5                          | 4                  | 3             | 2    | 1 | 0 |

| AMCAP[7:0]   | -                    | •                          | -                  | -             |      | · | • |

| Bit 7 – 0 :  | AMCAP[7:0] : A       | M Antenna Capacit          | or bank            |               |      |   |   |

|              |                      | ank is composed of         |                    |               |      |   |   |

| High 4 bi    | ts are arranged in A | MCTRL resister.            |                    |               |      |   |   |

|              |                      |                            |                    |               |      |   |   |

| 7           | 6                                     | 5 4                          | 3                  | 2                   | 1        | 0     |

|-------------|---------------------------------------|------------------------------|--------------------|---------------------|----------|-------|

| AMDIV[2:0]  |                                       | AM_0                         | CAL ACAP11         | ACAP10              | ACAP9    | ACAP8 |

| Bit 7 – 5 : | AMDIV[2:0] : AM                       | 1 Clock Divider              |                    |                     |          |       |

| Bit 7 :     | AM_CD2 : AM C                         | lock Divider bit 2.          |                    |                     |          |       |

| Bit 6 :     | AM_CD1 : AM C                         | lock Divider bit 1.          |                    |                     |          |       |

| Bit 5 :     | AM_CD0 : AM C                         | lock Divider bit 0.          |                    |                     |          |       |

|             |                                       |                              |                    |                     |          |       |

|             |                                       | cy of FM belt even for the A |                    |                     |          |       |

| Set the     |                                       | viding frequency to turning  |                    |                     |          |       |

|             | AM_CD[2:0]                            | Rate of dividing frequen     | ncy Rough estimate | e AM-RF frequency ( | (In kHz) |       |

|             | 0,1                                   | Divider OFF                  |                    | 0 (FM mode)         |          |       |

|             | 2                                     | 224                          |                    | 338 - 483           |          |       |

|             | 3                                     | 160                          |                    | 474 - 676           |          |       |

|             | 4                                     | 112                          |                    | 676 – 966           |          |       |

|             | 5                                     | 80                           |                    | 947 - 1353          |          |       |

|             | 6                                     | 64                           |                    | 1183 - 1692         |          |       |

|             | 7                                     | 48                           |                    | 1578 - 2256         |          |       |

| Bit 4 :     | NA (0 Fixation)                       |                              |                    |                     |          |       |

| Bit 3 – 0 : | · · · · · · · · · · · · · · · · · · · | M antenna capacitor bank.    |                    |                     |          |       |

| Bit 3 :     | AMCAP_bit11                           | <u>.</u>                     |                    |                     |          |       |

| Bit 2 :     | AMCAP_bit10                           |                              |                    |                     |          |       |

| Bit 1 :     | AMCAP_bit9                            |                              |                    |                     |          |       |

| Bit 0 :     | AMCAP_bit8                            |                              |                    |                     |          |       |

Register 10h – DO\_REF\_CLK\_CNF – Do output mode and reference clock configuration (Read/Write)

| 0              |                         | —               | 1                | 5                        | 5               | 0                |              | ,                     |

|----------------|-------------------------|-----------------|------------------|--------------------------|-----------------|------------------|--------------|-----------------------|

| 7              | 6                       | 5               | 4                | 3                        | 2               | 1                |              | 0                     |

| IPOL           | DO_SEL[1:0]             |                 | EXT_C            | CLK_CFG[1:0]             | FS_S            | [2:0]            |              |                       |

| Bit 7 :        | IPOL : Indicator (I     | DO pin _SD/S    | T mode) polari   | ty                       |                 |                  |              |                       |

|                | 0 = SD/ST Active        | Low (The san    | ne state change  | as 13pin – SD pin / 14   | pin – ST pin )  | )                |              |                       |

|                | 1 = SD/ST Active        | High (State cl  | nange opposite   | to 13pin – SD pin / 14p  | oin – ST pin )  |                  |              |                       |

| Note : This bi | t doesn't influence the | polarity of the | e serial data.   |                          |                 |                  |              |                       |

|                |                         |                 |                  |                          |                 |                  |              |                       |

| Bit 6 -5 :     | DO_SEL : DO pin         | select (DO p    | in output mode   | select)                  |                 |                  |              |                       |

|                | DO SEL[1:0]             | DO              | ) pin            |                          |                 |                  |              |                       |

|                | 00                      | Se              | rial data output | mode                     |                 |                  |              |                       |

|                | 01                      |                 | pin mode         |                          |                 |                  |              |                       |

|                | 10                      | SD              | pin mode         |                          |                 |                  |              |                       |

|                | 11                      | Lo              | cal position cor | nfirmation mode          |                 |                  |              |                       |

| DO pin is use  | d by observing the pos  | ition (Upper l  | neterodyne / Lo  | wer heterodyne) of a st  | ate of SD pin   | /ST pin besides  | the serial d | data output and local |

| OSC.           |                         |                 |                  |                          |                 |                  |              |                       |

| * The state of | DO pin changes synch    | nronizing with  | SD pin / ST pi   | in when DO_SEL is set    | t to (01b) or ( | 10b).            |              |                       |

| * The state of | DO pin changes by the   | e position of I | Local OSC whe    | en DO is set to (11b). L | ower heterod    | yne = 0, Upper l | neterodyne   | = 1                   |

| * Set DO_SE    | L to (00b) when you or  | utput the seria | l data.          |                          |                 |                  |              |                       |

|                |                         |                 |                  |                          |                 |                  |              |                       |

| Bit 4 – 3 :    | EXT_CLK_CFG[            | 1:0] : Externa  | l clock setting  |                          |                 |                  |              |                       |

|                | EXT_CLK_CF              | G[1:0]          | Reference        | e clock                  |                 |                  |              |                       |

|                | 00                      |                 | Off              |                          |                 |                  |              |                       |

|                | 01                      |                 | The exter        | nal clock is supplied.   |                 |                  |              |                       |

|                | 10                      |                 |                  | Crystal oscillation      |                 |                  |              |                       |

|                | 11                      |                 | Unused           |                          |                 |                  |              |                       |

|                | ·                       |                 |                  |                          |                 |                  |              |                       |

Bit 2 – 0: FS\_S[2:0] : SD(Station Detector) operate level setting (distinguishes at the FS level )

| 7                |           | 6       |             | 5              |              | 4        |            | 3         |             | 2          |           |             | 1         |             | 0           |           |

|------------------|-----------|---------|-------------|----------------|--------------|----------|------------|-----------|-------------|------------|-----------|-------------|-----------|-------------|-------------|-----------|

| FLL_M            | OD        | AMIF    | [2:0]       |                |              |          |            | FMI       | F[3:0]      |            |           |             |           |             |             |           |

| Bit 7 :          |           | FLL_M   | OD : FLI    | L operation    | n mode       |          |            |           |             |            |           |             |           |             |             |           |

|                  |           | 0 : Smo | othing fil  | ter = OFF      |              |          |            |           |             |            |           |             |           |             |             |           |

|                  |           | 1 : Smo | othing fil  | ter = ON       |              |          |            |           |             |            |           |             |           |             |             |           |

|                  |           |         | 0.01 . IE 6 |                |              | A. M     | 4 - : 1    | 41        |             |            |           |             |           |             |             |           |

| Bit 6 -4         | :         | AMIF[2  | 2:0] : IF I | requency       | setting when | AM mo    | de 1s sel  | ected     |             |            |           |             |           |             |             |           |

|                  |           |         |             |                |              | •        | AMIF       | [2:0]     |             |            |           |             |           |             |             |           |

|                  |           | 0       | 1           |                | 2            |          | 3          | 4         |             | 5          |           | 6           |           | 7           |             |           |

|                  | 2         | 20kHz   | 31k         | Hz             | 42kHz        | 531      | kHz        | 64k]      | Hz          | 75kH       | z         | 86kHz       | g         | 97kHz       |             |           |

|                  |           |         |             |                |              |          |            |           |             |            |           |             |           |             |             |           |

|                  |           | FMIF[3  | 3:0] : IF f | requency       | setting when | FM mo    | de is sele | ected (kI | Hz)         |            |           |             |           |             |             |           |

| Bit 3 – (        | ):        | _       |             | FMIF[3:0]      |              |          |            |           |             |            |           |             |           |             |             |           |

| Bit 3 – (<br>SE_ | D:<br>RF_ | _       |             |                |              |          |            | FMI       | F[3:0]      |            |           |             |           |             |             |           |

|                  |           | 0       | 1           | 2 3            | 4            | 5        | 6          | FMIF<br>7 | F[3:0]<br>8 | 9          | 10        | 11          | 12        | 13          | 14          | 15        |

| SE_              | RF_       | 0 112.5 | 1<br>125 1  | 2 3<br>37.5 15 |              | 5<br>175 | 6<br>187.5 |           |             | 9<br>237.5 | 10<br>250 | 11<br>262.5 | 12<br>275 | 13<br>287.5 | 14<br>312.5 | 15<br>325 |

### Register 11h – IF\_SEL – IF frequency selection (Read/Write)

Register 12h - REF\_CLK\_MOD - Slope correction (Read/Write)

| 7                                                                                                                                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|--|--|

| REFMOD[7:0]                                                                                                                                                     |   |   |   |   |   |   |   |  |  |

| Bit 7 – 0 : REFMOD[7:0] : Reference clock correction                                                                                                            |   |   |   |   |   |   |   |  |  |

|                                                                                                                                                                 |   |   |   |   |   |   |   |  |  |

| Note : As for this register, a set value is different according to the crystal connected with 16pin and the input clock. Inform of a set value of this register |   |   |   |   |   |   |   |  |  |

| when you adopt the applications other than an example of applied circuit and recommended parts of this specifications.                                          |   |   |   |   |   |   |   |  |  |

| 7           | 6                   | 5                       | 4                      | 3                       | 2                    | 1                    | 0                  |

|-------------|---------------------|-------------------------|------------------------|-------------------------|----------------------|----------------------|--------------------|

| FLL_ON      | CLKS_SE             | [2:0]                   |                        | nSD_PM                  | nIF_PM               | DM_SE[1:0]           |                    |

| Bit 7 :     | FLL_ON : F          | FLL control             |                        |                         |                      |                      |                    |

|             | 0 = FLL OF          | F                       |                        |                         |                      |                      |                    |

|             | 1 = FLL ON          | 1                       |                        |                         |                      |                      |                    |

| Bit 6 – 4 : | CLKS SE ·           | Clock course select     |                        |                         |                      |                      |                    |

| BRO 4.      | 0 = No selec        |                         |                        |                         |                      |                      |                    |

|             |                     | rce of the stereo deco  | oder oscillator is ef  | fective                 |                      |                      |                    |

|             |                     | rce of the IF oscillato |                        |                         |                      |                      |                    |

|             |                     | rce of the AM antenr    |                        | ctive.                  |                      |                      |                    |

|             | 4 = The source      | rce of the FM-RF os     | cillator is effective. |                         |                      |                      |                    |

|             | 5 = The sour        | rce of the AM-RF os     | cillator is effective  |                         |                      |                      |                    |

|             | 6 - 7 = no s        | select                  |                        |                         |                      |                      |                    |

| No          | ta · Dit[6 4] sala  | ats the source of the   | osaillator. Salaat th  | e arbitrary source that | t to be adjusted and | to be measured       |                    |

| NO          |                     |                         |                        | ic aronnary source ma   | t to be adjusted and | to be measured.      |                    |

| Bit 3 :     | —                   | Stereo decoder clock    | PLL mute               |                         |                      |                      |                    |

|             |                     | OFF (Adjustment)        |                        |                         |                      |                      |                    |

|             | 1 = SD PLL          | ON (Operation usua      | ally)                  |                         |                      |                      |                    |

| Bit 2 :     | nIF_PM : IF         | F PLL mute              |                        |                         |                      |                      |                    |

|             | 0 = IF PLL          | OFF (Adjustment)        |                        |                         |                      |                      |                    |

|             | 1 = IF PLL          | ON (Operation usua      | lly)                   |                         |                      |                      |                    |

| Bit 1 – 0 : | CM_SE : Co          | ommand mode select      | t                      |                         |                      |                      |                    |

|             | 0 = Comma           |                         |                        |                         |                      |                      |                    |

|             | 1 = Measure         |                         |                        |                         |                      |                      |                    |

|             | 2 = Adjustm         | nent mode               |                        |                         |                      |                      |                    |

|             | 3 = Radio tu        | ining (reception freq   | uency adjustment)      | mode                    |                      |                      |                    |

| No          | ta : This hit is us | ed to select the com    | mand mode. Select      | the arbitrary comman    | d to be executed. T  | he command is ever   | uted by setting    |

| 110         | TARGET_V            |                         | nand mode. Select      | the arbitrary comman    | a to be executed. T  | ne command is excel  | ated by setting    |

|             |                     |                         |                        |                         |                      |                      |                    |

| Co          | mmand executio      |                         |                        |                         |                      |                      |                    |

|             | SD calibration      |                         |                        |                         |                      |                      |                    |

|             | IF calibratio       |                         |                        |                         |                      |                      |                    |

|             | RF(FM) tun          | •                       |                        |                         |                      |                      |                    |

|             | . ,                 | ning = 158ms            | 1 - 1 f 4h h -         |                         |                      |                      |                    |

|             | -                   | -                       | ieu for the above-m    | nentioned before all pr | rocessing including  | reading the register | value after having |

|             | executed th         | ne command.             |                        |                         |                      |                      |                    |

#### *Register 13h – SM\_CTRL – Statemachine control (Read/Write)*

Register 14h – REF\_CLK\_PRS – Reference clock pre-scalar (Read/Write)

| 7           | 6                                                              | 5                    | 4                   | 3           | 2 | 1 | 0 |  |  |

|-------------|----------------------------------------------------------------|----------------------|---------------------|-------------|---|---|---|--|--|

| IM_EVAS     | Reserved                                                       | WAIT_SEL             | A<_FINE             | REFPRE[3:0] |   |   |   |  |  |

| Bit 7 :     | IM_EVAS : Image                                                | evasion function C   | ON/OFF              |             |   |   |   |  |  |

|             | 0 = The image burg                                             | eau is not evaded.   |                     |             |   |   |   |  |  |

|             | 1 = The image bure                                             | eau is evaded. (reco | ommendation)        |             |   |   |   |  |  |

| Bit 6 :     | Reserved : 0 fixati                                            | on                   |                     |             |   |   |   |  |  |

| Bit 5 :     | WAIT_SEL : Selection after tuning at mute release standby time |                      |                     |             |   |   |   |  |  |

|             | 0 = 8ms standby                                                |                      |                     |             |   |   |   |  |  |

|             | 1 = 4ms standby                                                |                      |                     |             |   |   |   |  |  |

| Bit 4 :     | AM_FINE : Select                                               | ion at AM_ANT ac     | ljustment standby t | ime         |   |   |   |  |  |

|             | 0 = No standby after                                           |                      |                     |             |   |   |   |  |  |

|             | 1 = 2ms standby af                                             | ter switch of DAC    |                     |             |   |   |   |  |  |

| Bit 3 – 0 : | REFPRE[3:0] : Sta                                              | indard Clock Pre-sc  | calar               |             |   |   |   |  |  |

|             | 0 = 1:1                                                        |                      |                     |             |   |   |   |  |  |

|             | 1 = 1:2                                                        |                      |                     |             |   |   |   |  |  |

|             | 2 = 1:4                                                        |                      |                     |             |   |   |   |  |  |

|             | •••                                                            |                      |                     |             |   |   |   |  |  |

|             | 15 = 1:32768                                                   |                      |                     |             |   |   |   |  |  |

Register 15h – REF\_CLK\_DIV – Reference clock divider (Read/Write)

| 7           | 6                                     | 5               | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------|---------------------------------------|-----------------|---|---|---|---|---|--|--|

| REFDIV[7:0] |                                       |                 |   |   |   |   |   |  |  |

| Bit 7 – 0 : | REFDIV[7:0] : Standard clock divider  |                 |   |   |   |   |   |  |  |

|             | 0 : Rate of dividing frequency = 1    |                 |   |   |   |   |   |  |  |

|             | 1 : Rate of dividing                  | frequency $= 2$ |   |   |   |   |   |  |  |

|             | •••                                   |                 |   |   |   |   |   |  |  |

|             | 255 : Rate of dividing frequency =256 |                 |   |   |   |   |   |  |  |

#### *Register 16h – TARGET\_VAL\_L – Target Value Low Register (Read/Write)*

| 7                                                                                                                        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |