**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# **3-phase Inverter Power Module 1200 V SPM® 49 Series Application Note**

# AND90069

# INTRODUCTION

This application note provides practical guidelines for designing with the SPM 49 Series power modules. This series of Intelligent Power Modules (IPM) for 3-phase motor drives contains a three-phase inverter stage, gate drivers and a thermistor (Optional).

#### **Design Concept**

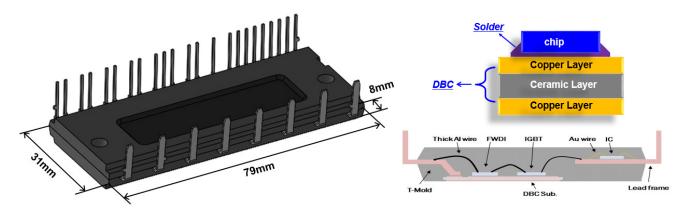

The SPM 49 design objective is to provide a minimized package and a low power consumption module with improved reliability. This is achieved by applying new gate-driving High-Voltage Integrated Circuit (HVIC), a new Insulated-Gate Bipolar Transistor (IGBT) of advanced silicon technology, and improved Direct Bonded Copper (DBC) substrate based on transfer mold package. The SPM 49 achieves reduced board size and improved reliability compared to existing discrete solutions. Target

# **ON Semiconductor®**

www.onsemi.com

# **APPLICATION NOTE**

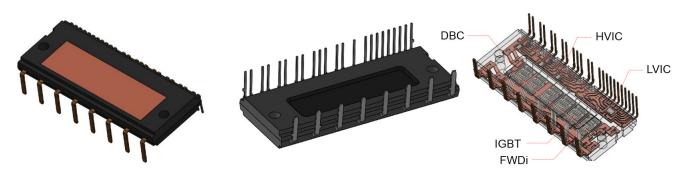

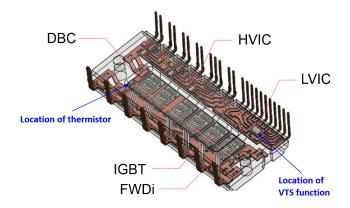

such as commercial air conditioners, general-purpose inverters and servo motors. The temperature sensing function of SPM 49 products are implemented in the LVIC to enhance the system reliability and isolated optional thermistor is available as well. The analog voltage proportional to the temperature of the LVIC and integrated thermistor temperature in module are provided for monitoring the module temperature and necessary protections against over-temperature situations. Figure 1 shows the package outline structure.

Figure 1. External View and Internal Structure of SPM 49

#### **Key Features**

- 1200 V / 35, 50 three phase IGBT inverter including control ICs for gate driving and protections.

- Very low thermal resistance by adopting DBC substrate.

- Easy PCB layout thanks to built-in bootstrap circuits.

- Open emitter configuration for easy monitoring of each phase current sensing.

- Sense IGBT technology is applied for low side to provide over current protection.

- Single–grounded power supply thanks to built–in HVICs and bootstrap operations.

- Built-in temperature sensing function by LVIC and optional NTC.

- Isolation rating of 2500 Vrms / min.

#### **1.PRODUCT DESCRIPTION**

#### **Ordering Information**

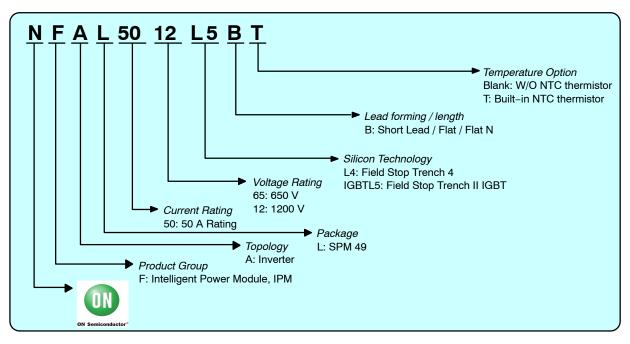

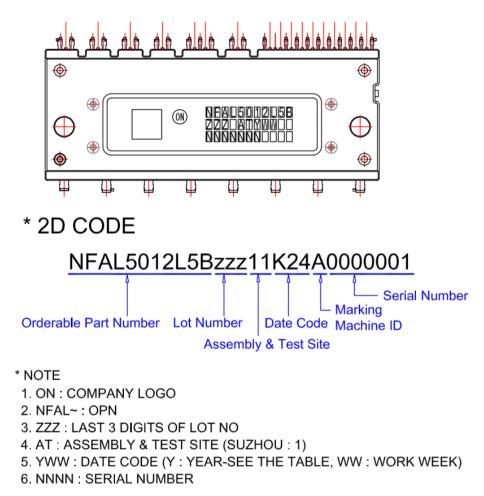

Figure 2. Ordering Information

#### Product Line-up

Table 1 shows the basic line up without package variations. Online loss and temperature simulation tool,

Motion Control Design Tool is recommended to find out the right IPM product for the desired application. For package drawing, please refer to Chapter <u>Package Outline</u>.

#### Table 1. PRODUCT LINE-UP

| Target Application                                     | Device         | IGBT Rating   | Motor Rating (Note 1) | Isolation Voltage                                  |

|--------------------------------------------------------|----------------|---------------|-----------------------|----------------------------------------------------|

| Air Conditioners, Industrial<br>Motor, General-purpose | NFAL3512L5B(T) | 35 A / 1200 V | 5.5 kW                | V <sub>ISO</sub> = 2500 Vrms<br>(Sine 60 Hz, 1–min |

| Inverters, Servo Motors                                | NFAL5012L5B(T) | 50 A / 1200 V | 7.5 kW                | All Shorted Pins Heat Sink)                        |

1. These motor ratings are general ratings, so can be changed by the operation conditions.

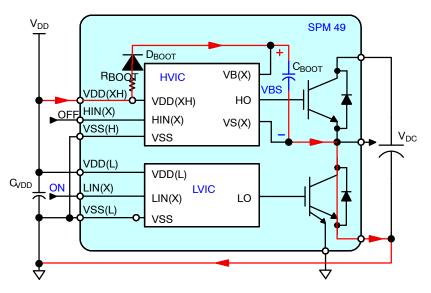

#### Internal Circuit Diagram

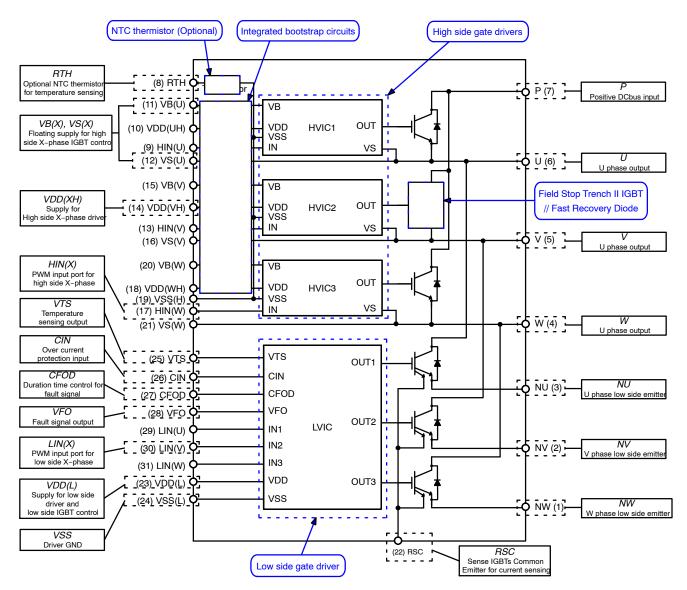

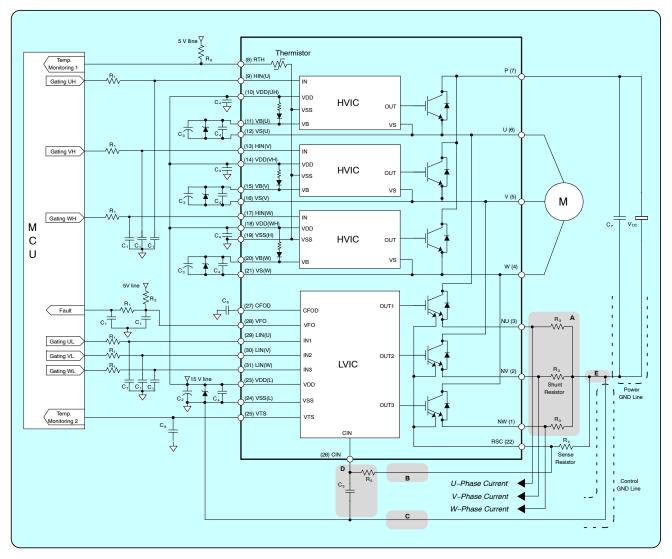

Three bootstrap circuits generate the voltage needed for driving the high-side IGBTs. The boost diodes are internal to the part and sourced from VDD (15 V). There is an internal level shift circuit for the high-side drive signals allowing all control signals to be driven directly from GND levels common with the control circuit such as the microcontroller without requiring external isolation with opto-couplers. Major differences between SPM 49 –T version and normal version are shown on pins 8 of the internal circuit diagram as shown in Figure 3. The –T version has built–in NTC which senses the temperature of the power chip. Normal version NTC is not built in. Both –T version and Normal version function as conventional functions LVIC temperature sensing signal is output from the VTS pin.

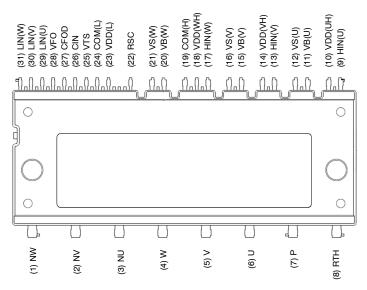

Figure 4. Package Top–View and Pin Assignment

#### Table 2. NUMBERS, NAMES AND DUMMY PINS

| Pin Number | Name    | Description                                            |

|------------|---------|--------------------------------------------------------|

| 1          | NW      | Negative DC-Link Input for W Phase                     |

| 2          | NV      | Negative DC-Link Input for V Phase                     |

| 3          | NU      | Negative DC-Link Input for U Phase                     |

| 4          | W       | Output for W Phase                                     |

| 5          | V       | Output for V Phase                                     |

| 6          | U       | Output for U Phase                                     |

| 7          | Р       | Positive DC-Link Input                                 |

| 8          | RTH     | Series Resister for Thermistor (Temperature Detection) |

| 9          | HIN(U)  | Signal Input for High-Side U Phase                     |

| 10         | VDD(UH) | High-Side Bias Votage for U Phase IC                   |

| 11         | VB(U)   | High-Side Bias Voltage for U Phase IGBT Driving        |

| 12         | VS(U)   | High-Side Bias Voltage GND for U Phase IGBT Driving    |

| 13         | HIN(V)  | Signal Input for High-Side V Phase                     |

| 14         | VDD(VH) | High-Side Bias Votage for V Phase IC                   |

| 15         | VB(V)   | High-Side Bias Voltage for V Phase IGBT Driving        |

| 16         | VS(V)   | High-Side Bias Voltage GND for V Phase IGBT Driving    |

| 17         | HIN(W)  | Signal Input for High-Side W Phase                     |

| 18         | VDD(WH) | High-Side Bias Votage for W phase IC                   |

| 19         | VSS(H)  | Low-Side Common Supply Ground, Connected to HVIC       |

| 20         | VB(W)   | High-Side Bias Voltage for W Phase IGBT Driving        |

| 21         | VS(W)   | High-Side Bias Votage GND for W phase IGBT Driving     |

| 22         | RSC     | Resistor for Over and Short-Circuit Current Detection  |

| 23         | VDD(L)  | Low-Side Bias Votage for IC and IGBTs Driving          |

| 24         | VSS(L)  | Low–Side Common Supply Ground, Connected to LVIC       |

| 25         | VTS     | Voltage Output for LVIC Temperature Sensing Unit       |

| 26         | CIN     | Input for Over Current Protection                      |

| 27         | CFOD    | Capacitor for Fault Output Duration Selection          |

| 28         | VFO     | Fault Output                                           |

| 29         | LIN(U)  | Signal Input for Low-Side U Phase                      |

| 30         | LIN(V)  | Signal Input for Low-Side V Phase                      |

| 31         | LIN(W)  | Signal Input for Low-Side W Phase                      |

#### **Detailed Pin Definition and Notification**

Pins: VB(U)-VS(U), VB(V)-VS(V), VB(W)-VS(W)

High-side bias voltage pins for driving the IGBT / high-side bias voltage ground pins for driving the IGBTs.

VB(U), VB(V), VB(W) are integrated bootstrap diode cathode pins.

These are drive power supply pins for providing gate drive power to the high–side IGBTs.

The virtue of the ability to bootstrap the circuit scheme is that no external power supplies are required for the high-side IGBTs. Each bootstrap capacitor is charged from the VDD supply during ON state of the corresponding low-side IGBT and Diode. To prevent malfunctions caused by noise and ripple in the supply voltage, a low-ESR, a low-ESL filter capacitor should be mounted very close to these pins.

Pins: VDD(UH), VDD(VH), VDD(WH), VDD(L)

Low-side bias voltage pin / high-side bias voltage pins. This is control supply pins for the built-in ICs.

These four pins should be connected externally.

To prevent malfunctions caused by noise and ripple in the supply voltage, a low–ESR, low–ESL filter capacitor should be mounted very close to these pins.

# Pin: VSS(H), VSS(L)

Control signal ground pin.

This is supply ground pin for the built-in ICs.

Important! To avoid noise influences, the main power circuit current should not be allowed to blow through this pin.

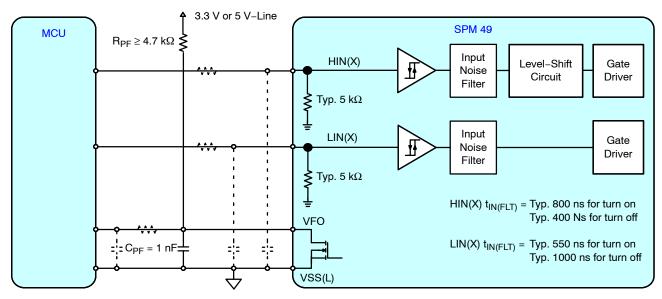

Pins: HIN(U), HIN(V), HIN(W), LIN(U), LIN(V), LIN(W) Signal input pins.

These pins control the operation of the built-in IGBTs.

They are activated by voltage input signals. The terminals are internally connected to a Schmitt-trigger circuit composed of 3.3 V and 5 V-class CMOS.

The signal logic of these pins is active high. The IGBT associated with each of these pins is turned on.

ON when a sufficient logic voltage is applied to these pins.

The wiring of each input should be as short as possible to protect the SPM 49 against noise influences.

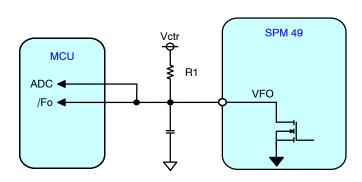

To prevent signal oscillations, an RC coupling as illustrated in Figure 28 is recommended.

### Pin: CIN

Over-current and short-circuit detection input pin.

The current sensing shunt resistor should be connected between the pin CIN and the low-side ground

Pin VSS to detect over or short circuit current.

The shunt resistor should be selected to meet the detection levels matched for the specific application.

An RC filter should be connected to the CIN pin to eliminate noise.

The connection length between the shunt resistor and CIN pin should be minimized.

### Pin: RSC

Low-side sense IGBT current flows through this pin. Short-circuit and over current can be detected at this pin through an external resistor. If using three shunt resistors at N terminal for OCP and SCP without sensing from RSC, RSC pin should be connected to VSS pin.

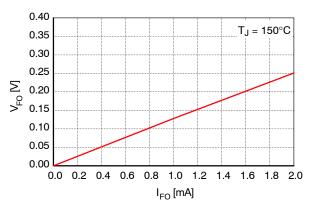

### Pin: VFO

Fault output pin.

This is the fault output alarm pin. An active low output is given on this pin for a fault state condition in the SPM 49.

The alarm conditions are: Short-Circuit Current Protection (SCP), and low-side bias Under-Voltage Lock Out (UVLO).

The VFO output is open drain configured. The VFO signal line should be pulled to the 3.3 V or 5 V logic power supply with approximately  $4.7 \text{ k}\Omega$  resistance.

## Pin: CFOD

Fault output duration time control pin.

The fault-out pulse width time depends on the capacitance value of CFOD.

### Pin: RTH (Optional for -T type)

For case temperature (Tc) detection, this pin should be connected to an external series resistor.

The external series resistor should be selected to meet the detection range matched for the specification of each application (for details, refer to Figure 26).

#### Pin: VTS

Analog temperature sensing output pin.

This is to indicate the temperature of LVIC with analog voltage. LVIC itself creates some power loss, but mainly heat generated from the IGBTs will increase the temperature of the LVIC.

VTS versus temperature characteristics is illustrated in Figure 22.

Pin: P

Positive DC-link pin.

This is the DC-link positive power supply pin of the inverter.

It is internally connected to the collectors of the high-side IGBTs.

To suppress surge voltage caused by the DC-link wiring or PCB pattern inductance, connect a smoothing filter capacitor close to this pin (tip: metal film capacitor is typically used).

### Pins: NU, NV, NW

Negative DC-link pins.

These are the DC-link negative power supply pins (power ground) of the inverter.

These pins are connected to the low-side IGBT emitters of the each phase.

These pins are used to one shunt or three shunt resistor.

### Pins: U, V, W

Inverter power output pins.

Inverter output pins for connecting to the inverter load (e.g. motor).

# PACKAGE

#### Package Structure

Since heat dissipation is an important factor limiting the power module's current capability, the heat dissipation characteristics of a package are important in determining the performance. A trade-off exists among heat dissipation characteristics, package size, and isolation characteristics. The key to good package technology lies in the optimization package size while maintaining outstanding heat dissipation characteristics without compromising the isolation rating. In SPM 49, technology was developed with DBC substrate that resulted in good heat dissipation characteristics. Power chips are attached directly to the DBC substrate. This technology is applied SPM 49, achieving improved reliability and heat dissipation.

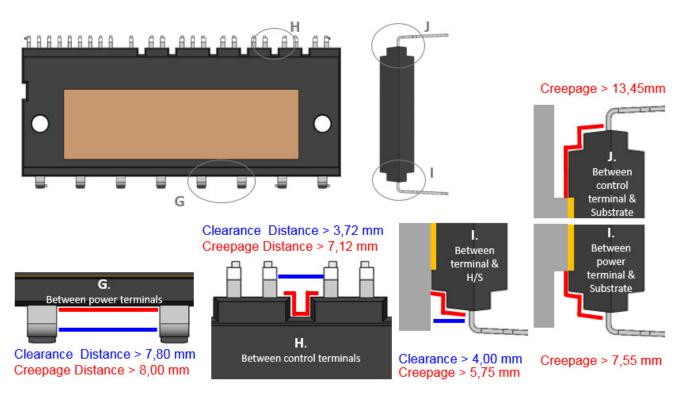

Figure 5 shows the internal package structure and cross-sections including the lead frame and boding wires.

Figure 6 shows each creepage and clearance distance of the SPM 49 package.

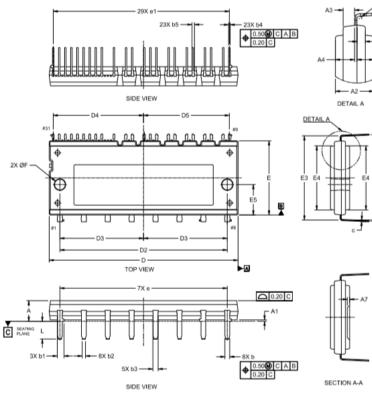

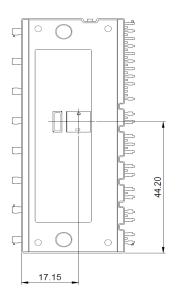

#### Package Outline Unit: mm NFALxx12L5BT

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER. ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSION b and c APPLY TO THE PLATED LEADS AND ARE MEASURED BETWEEN 1.00 AND 2.00 FROM THE LEAD TIP.

- 4. POSITION OF THE LEAD IS DETERMINED AT THE BASE OF THE LEAD WHERE IT EXITS THE PACKAGE BODY.

|     | M     | ILLIMETER | ₹S    |     | M     | ILLIMETER | ₹S    |  |

|-----|-------|-----------|-------|-----|-------|-----------|-------|--|

| DIM | MIN.  | NOM.      | MAX.  | DIM | MIN,  | NOM.      | MAX,  |  |

| A   | 8.40  | 8.60      | 8.80  | E   | 30.80 | 31.00     | 31.20 |  |

| A1  | 0.40  | 0.60      | 0.80  | E1  | 12.30 | 12.50     | 12.70 |  |

| A2  | 7.90  | 8.00      | 8.10  | E2  | 35.75 | 36.20     | 36.65 |  |

| A3  | 2.30  | 2.40      | 2,50  | E3  |       | 35.17 REF |       |  |

| A4  | 3.90  | 4.00      | 4.10  | E4  | 26.60 | 26.80     | 27.00 |  |

| A5  | 1.65  | 1.75      | 1.85  | E5  | 12.55 | 12.70     | 12.85 |  |

| A6  | 3.40  | 3.50      | 3.60  | E6  | 6,80  | 7,00      | 7,20  |  |

| A7  |       | 1.00 REF  |       | 0   |       | 10.00 BSC |       |  |

| b   | 1,90  | 2,00      | 2.10  | e1  |       | 2.54 BSC  |       |  |

| b1  |       |           | 2.80  | F   | 4.40  | 4.50      | 4.60  |  |

| b2  |       | 1.40 REF  |       | L   |       | 7.40 REF  |       |  |

| b3  |       |           | 2.20  | M   |       |           | 5.0°  |  |

| b4  | 0.50  | 0.60      | 0.70  | R   |       | 0.50 REF  |       |  |

| b5  |       |           | 0.80  |     |       |           |       |  |

| с   | 0.45  | 0.50      | 0.60  | ]   |       |           |       |  |

| D   | 78,80 | 79,00     | 79,20 | ]   |       |           |       |  |

| D1  | 49.50 | 49.70     | 49.90 | 1   |       |           |       |  |

D2

D3

D4

69,85

34.80

37.60

70,00

35.00

37.80

70,15

35.20

38,00

Figure 7.

12.70

36,65

27.00

12.85

7.20

$\oplus$

ሐ

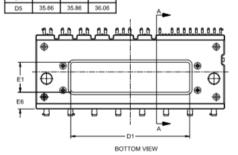

## Unit: mm NFALxx12L5B

MILLIMETERS MILLIMETERS NOM. MAX. DIM MIN. DIM MIN. NOM. MAX. NOTES: 8,60 8.80 8.40 Α Е 30.80 31.00 31.20 1. DIMENSIONING AND TOLERANCING PER. ASME Y14.5M, 2009. A1 0.40 0.60 0.80 E1 12,30 12,50 A2 7,90 8.00 8.10 E2 35,75 36,20 2. CONTROLLING DIMENSION: MILLIMETERS A3 2.30 2,40 2,50 E3 35.17 RE 3. DIMENSION b and c APPLY TO THE PLATED LEADS AND ARE MEASURED BETWEEN 1.00 AND 2.00 FROM THE LEAD TIP. A4 3,90 4,00 4.10 E4 26.60 26.80 A5 1,65 1,75 1.85 E5 12,55 12.70 A6 3.40 3.50 3.60 E6 6.80 7.00 4. POSITION OF THE LEAD IS DETERMINED AT THE A7 1.00 REI 10.00 BSC e ROOT OF THE LEAD WHERE IT EXITS THE PACKAGE BODY. 1.90 2.00 2.10 2.54 BSC b e1 b1 2.80 F 4.40 4.50 4.60 - 29X e1 A3 1.40 REF b2 7.40 REF L 2.20 b3 М 5.0\* 23X b5 23X b4 \_ ● 0.50 ● C A B 0.20 C 0.70 0.50 REF b4 0.50 0.60 R 0.80 b5 0.45 0.50 0.60 79.20 78.80 79.00 D 49.50 49.70 49.90 D1 70.00 70.15 D2 69.85 - A2 35.00 D3 34,80 35.20 SIDE VIEW DETAIL A 37.80 37.60 38.00 D4 D4 D5 D5 35.66 35.86 36.06 DETAIL A 00000000 1000000000 0.0 0 0.0 0.0 0.0 0.0 00 10.0 0.0 0.0 0.0 0.0.0 \$ ŧ ۲ 2X ØF E2  $\oplus$ Ð  $\oplus$ E1 E5 ₩ \$ ۲ B E6 Ţ 1) П υ υ υ D3 D1 - D2 BOTTOM VIEW Đ TOP VIEW (4.50) 7X e 0.20 C - A1 Π C BEATING L Ţ 2X b1 7X h2 SECTION A-A ● 0.50 ℃ A B 0.20 C 5X b3 SIDE VIEW

Figure 8.

**Marking Specification**

| Y    | Alphabet |

|------|----------|

| 2017 | J        |

| 2018 | К        |

| 2019 | L        |

| 2020 | М        |

| 2021 | N        |

| 2022 | 0        |

| 2023 | Р        |

| 2024 | Q        |

| 2025 | R        |

| 2026 | S        |

| 2027 | Т        |

Figure 9.

#### **PRODUCT SYNOPSIS**

This section discusses electrical specification, characteristics and mechanical characteristics.

#### **ABSOLUTE MAXIMUM RATINGS** (Tj = 25°C, Unless Otherwise Specified)

| Symbol                 | Parameter                                                                     | Condition                                                           | Rating         | Unit |

|------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------|------|

| INVERTER PA            | ART (BASE ON NFAL5012L5B(T))                                                  | ·                                                                   |                |      |

| VPN                    | Supply Voltage                                                                | Applied between P – NU, NV, NW                                      | 900            | V    |

| VPN <sub>(Surge)</sub> | Supply Voltage (Surge)                                                        | Applied between P – NU, NV, NW                                      | 1000           | V    |

| Vces                   | Collector – Emitter Voltage                                                   |                                                                     | 1200           | V    |

| ±lc                    | Each IGBT Collector Current                                                   | Tc = 25°C, Tj $\leq$ 150°C (Note 2)                                 | 50             | Α    |

| ±lcp                   | Each IGBT Collector Current (Peak)                                            | Tc = 25°C, Tj $\leq$ 150°C, Under 1 ms Pulse Width                  | 100            | A    |

| Pc                     | Collector Dissipation                                                         | Tc = 25°C per One Chip                                              | 219            | W    |

| Tj                     | Operating Junction Temperature (Note 2)                                       |                                                                     | -40~150        | °C   |

| CONTROL PA             | ART                                                                           |                                                                     |                |      |

| VDD                    | Control Supply Voltage                                                        | Applied between VDD(XX) – VSS                                       | 20             | V    |

| VBS                    | High-Side Control Bias Voltage                                                | Applied between VB(X) – VS(X)                                       | 20             | V    |

| VIN                    | Input Signal Voltage                                                          | Applied between HIN(X), LIN(X) – VSS                                | -0.5~VDD + 0.5 | V    |

| VFO                    | Fault Output Supply Voltage                                                   | Applied between VFO – VSS                                           | -0.5~VDD + 0.5 | V    |

| IFO                    | Fault Output Current                                                          | Sink Current at VFO Pin                                             | 5              | mA   |

| VCIN                   | Current Sensing Input Voltage                                                 | Applied between CIN – VSS                                           | -0.5~VDD + 0.5 | V    |

| Tj                     | Operating Junction Temperature                                                |                                                                     | -40~150        | °C   |

| BOOTSTRAP              | DIODE PART                                                                    |                                                                     |                |      |

| VRRM                   | Maximum Repetitive Reverse Voltage                                            |                                                                     | 1200           | V    |

| CBOOT                  | Load Capacitor for Bootstrap Supply                                           | Tc = 25°C, Tj $\leq$ 150°C, VDD < 20 V                              | 470            | μF   |

| Tj                     | Operating Junction Temperature                                                |                                                                     | -40~150        | °C   |

| TOTAL SYST             | EM                                                                            | •                                                                   | -              |      |

| VPN(PROT)              | Self-Protection Supply Voltage Limit<br>(Short-Circuit Protection Capability) | VDD(L), VB(X) = 13.5~16.5 V, Tj = 150°C,<br>(Non-Repetitive, <2 μs) | 800            | V    |

| Tc                     | Module Case Operation Temperature                                             | See Figure 10                                                       | -40~125        | °C   |

TcModule Case Operation TemperatureSee Figure 10-40~125°CTstgStorage Temperature-40~125°CVisoIsolation Voltage60 Hz, Sinusoidal, 1–Minute, Connect Pins<br/>to Heat Sink2500Vrms

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. These values had been made on acquisition by the calculation considered to design factor. The maximum junction temperature rating of power chips integrated within the SPM 49 products are 150°C.

#### **ABSOLUTE MAXIMUM RATINGS** (T<sub>J</sub> = $25^{\circ}$ C, unless otherwise noted)

| Symbol                                      | Parameter                           | Condition                           | Min | Тур | Max  | Unit |

|---------------------------------------------|-------------------------------------|-------------------------------------|-----|-----|------|------|

| THERMAL RESISTANCE (BASE ON NFAL5012L5B(T)) |                                     |                                     |     |     |      |      |

| Rth(j−c)Q                                   | Junction to Case Thermal Resistance | Inverter IGBT Part (per 1/6 Module) | -   | -   | 0.57 | °C/W |

| Rth(j-c)F                                   | (Note 3)                            | Inverter FWDi Part (per 1/6 Module) | _   | _   | 1.15 |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

3. For the measurement point of case temperature (T<sub>C</sub>), please refer Figure 10.

Figure 10. Case Temperature (Tc) Detecting Point

#### **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $25^{\circ}$ C, unless otherwise noted)

| Syn    | nbol    | Parameter                            | Conc                             | lition                                                                        | Min  | Тур  | Max  | Unit |

|--------|---------|--------------------------------------|----------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| INVERT | ER PARI | (BASE ON NFAL5012L5B(T))             |                                  |                                                                               |      |      |      |      |

| VCE    | E(sat)  | Collector-Emitter Saturation Voltage | VDD, VBS = 15 V,<br>yIN(X) = 5 V |                                                                               |      | 2.00 | 2.50 | V    |

| V      | /F      | FWDi Forward Voltage                 | yIN(X) = 5 V                     | lf = 50 A                                                                     | -    | 2.30 | 2.90 |      |

| High   | ton     | Switching Times                      | VPN = 600 V, VDD =               |                                                                               | 1.10 | 1.70 | 2.30 | μs   |

| Side   | tc(on)  |                                      | See Figure 11                    | Ic = 50 A, $V_{IN}$ = 0 V $\leftrightarrow$ 5 V, Inductive Load See Figure 11 |      | 0.25 | 0.55 |      |

|        | toff    |                                      |                                  |                                                                               |      | 1.50 | 2.10 |      |

|        | tc(off) |                                      |                                  |                                                                               | -    | 0.15 | 0.45 |      |

|        | trr     |                                      |                                  |                                                                               | -    | 0.25 | -    |      |

| Low    | ton     |                                      |                                  |                                                                               | 1.00 | 1.60 | 2.20 |      |

| Side   | tc(on)  |                                      |                                  | -                                                                             | 0.25 | 0.55 |      |      |

|        | toff    |                                      |                                  |                                                                               | -    | 1.40 | 2.00 |      |

|        | tc(off) |                                      |                                  |                                                                               | -    | 0.15 | 0.45 |      |

|        | trr     |                                      |                                  |                                                                               | -    | 0.25 | -    |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

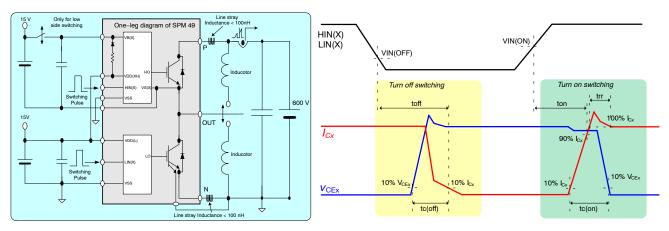

4. ton and toff include the propagation delay time of the internal drive IC. tc(on) and tc(off) are the switching time of IGBT itself under the given gate driving condition internally. For the detail information, please refer to Figure 11.

Figure 11. Switching Evaluation Circuit and Switching Time Definition

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C, unless otherwise noted)

| Symbol     | Parameter                                     | Conditions                                                                                         | i                      | Min   | Тур   | Max   | Unit     |

|------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------|-------|-------|-------|----------|

| BOOTSTRAP  | CIRCUIT PART                                  |                                                                                                    |                        | •     | •     | •     | <b>-</b> |

| VF         | Forward Voltage                               | lf = 0.1 A, Tj = 25°C                                                                              |                        | 2.1   | 2.5   | 2.9   | V        |

| RBOOT      | Bootstrap Resistor                            | lf = 0.1 A, Tj = 25°C                                                                              |                        | 12.5  | 15.5  | 18.5  | V        |

| CONTROL PA | NRT (BASE ON NFAL5012L5B                      | (T))                                                                                               |                        |       |       |       |          |

| IQDDH      | Quiescent VDD Supply                          | VDD(XH) = 15 V, HIN(X) = 0 V                                                                       | VDD(XH) – VSS(H)       | -     | -     | 0.30  | mA       |

| IQDDL      | Current                                       | VDD(L) = 15 V, LIN(X) = 0 V                                                                        | VDD(L) - VSS(L)        | -     | -     | 3.50  |          |

| IQBS       | Quiescent VBS Supply<br>Current of Each Phase | VB(X) – VS(X) = 15 V, HIN(X) = 0                                                                   | V                      | -     | -     | 0.30  |          |

| ISEN       | Sensing Current of Each<br>Sense IGBT         | VDD(L) = 15 V, VIN = 5 V,<br>RSC = 0 $\Omega$ , No Connection of<br>Shunt Resistor at NX Terminals | lc = 50 A              | -     | 22    | -     |          |

| VFOH       | Fault Output Voltage                          | $VDD(L)$ = 15 V, $CIN$ = 0 V, Pulled up to 5 V by 10 k $\Omega$                                    |                        | 4.90  | -     | -     | V        |

| VFOL       |                                               | VDD(L) = 15 V, CIN = 1 V, IFO = 1 mA                                                               |                        | -     | -     | 0.95  |          |

| VSC(ref)   | Short-Circuit Trip Level                      | VDD(L) = 15 V                                                                                      | CIN – VSS(L)           | 0.46  | 0.48  | 0.50  |          |

| UVDDD      | Supply Circuit,                               | Detection Level                                                                                    |                        | 10.3  | -     | 12.5  |          |

| UVDDR      | Under-Voltage Protection<br>(Note 5)          | Reset Level                                                                                        |                        | 10.8  | -     | 13.0  | 1        |

| UVBSD      |                                               | Detection Level                                                                                    |                        | 10.0  | -     | 12.0  |          |

| UVBSR      |                                               | Reset Level                                                                                        |                        | 10.5  | -     | 12.5  |          |

| ISC        | Short Circuit Trip Level                      | Rsc = TBD $\Omega$ (±1%), No Connect<br>at NU, NV, NW                                              | tion of Shunt Resistor | 75    | -     | -     | A        |

| tFOD       | Fault-Out Pulse Width                         | CFOD = 22 nF                                                                                       |                        | 1.6   | -     | -     | ms       |

| VTS        | LVIC Temperature Sensing<br>Voltage Output    | VDD(L) = 15 V, VTS - VSS(L) = 1                                                                    | 10 nF, TLVIC = 25°C    | 0.909 | 1.030 | 1.151 | V        |

| VIN(ON)    | ON Threshold Voltage                          | Applied between HIN(X), LIN(X)                                                                     | – VSS                  | -     | -     | 2.6   |          |

| VIN(OFF)   | OFF Threshold Voltage                         |                                                                                                    |                        | 0.8   | -     | _     |          |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Short-circuit current protection is functioning only at low side.

| RECOMMENDED OPERATING CONDITIONS | 6 (BASE ON NFAL5012L5B(T)) |

|----------------------------------|----------------------------|

|----------------------------------|----------------------------|

| Symbol              | Parameter                                 | Conditions                                                                      | Min  | Тур  | Max  | Unit |

|---------------------|-------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| VPN                 | Supply Voltage                            | Applied between P – N <sub>x</sub>                                              | 350  | 600  | 800  | V    |

| VDD                 | Control Supply Voltage                    | Applied VDD – VSS                                                               | 13.5 | 15.0 | 16.5 |      |

| VBS                 | High-Side Bias Voltage                    | Applied between VB(X) – VS(X)                                                   | 13.0 | 15.0 | 18.5 | V    |

| dVDD/dt,<br>dVBS/dt | Control Supply Variation                  |                                                                                 | -1   | -    | +1   | V/μs |

| tdead               | Blanking Time for<br>Preventing Arm-Short | For Each Input Signal                                                           | 2.0  | -    | -    | μs   |

| FPWM                | PWM Input Signal                          | $40^{\circ}C \leq Tc \leq 125^{\circ}C, -40^{\circ}C \leq Tj \leq 150^{\circ}C$ | -    | -    | 20   | kHz  |

| PWIN(ON)            | Minimum Input Pulse Width                 | $VDD = VBS = 15 V$ , $Ic \le 50 A$ , Wiring Inductance                          | 1.5  | -    | _    | μs   |

| PWIN(OFF)           |                                           | between NU, NV, NW and DC Link $\tilde{N}$ < 10 nH                              | 2.0  | -    | -    |      |

| Tj                  | Junction Temperature                      |                                                                                 | -40  | -    | +150 | °C   |

6. This product might not make response if input pulse width is lee than the recommended value.

#### **MECHANICAL CHARACTERISTICS**

| Item      | Recomm                                                                                                                                                                                                                                                                                                                                                                                   | ended Condition                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Pitch     | 79.0 $\pm$ 0.2 mm (Please refer to Package Outline Diagra                                                                                                                                                                                                                                                                                                                                | am)                                                                      |

| Screw     | Diameter: M4<br>Recommended thread engagement for screws with pr                                                                                                                                                                                                                                                                                                                         | operty class 4.8 to 6.8 for different materials                          |

| Washer    | Spring washer diameter: D = 7 mm to DIN 127 or DIN<br>Plane washer dimensions: D = 9 mm to DIN 125                                                                                                                                                                                                                                                                                       | 128                                                                      |

| Heat sink | Material: Aluminum or Copper<br>Warpage (the surface that contacts IPM) : -50 to 100<br>Screw holes must be countersunk.<br>No contamination on the heat sink surface that contact                                                                                                                                                                                                       |                                                                          |

| Torque    | Pre tightening : 0.2~0.3 Nm on first screw<br>Pre tightening : 0.2~0.3 Nm on second screw<br>Final tightening : 0.98~1.47 Nm on second screw<br>Final tightening : 0.98~1.47 Nm on first screw<br>Screw $\longrightarrow$ $\square$ $\square$ $\square$ $\square$<br>Washer $\longrightarrow$ $\square$ $\square$ $\square$ $\square$<br>Grease $\longrightarrow$ $\square$<br>Heat Sink | Pre - Screwing : $1 \rightarrow 2$<br>Final Screwing : $2 \rightarrow 1$ |

| Grease    | Silicone grease.<br>Thickness : 50 to 100 µm<br>Uniformly apply silicon grease to whole back.<br>Thermal foils are only recommended after careful eva<br>Thickness, stiffness and compressibility parameters h<br>strong influence on performance.                                                                                                                                       |                                                                          |

|           | Recommend                                                                                                                                                                                                                                                                                                                                                                                | Not recommend                                                            |

## **OPERATION SEQUENCE FOR PROTECTIONS**

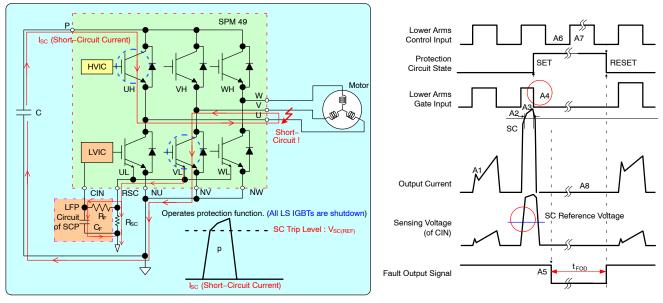

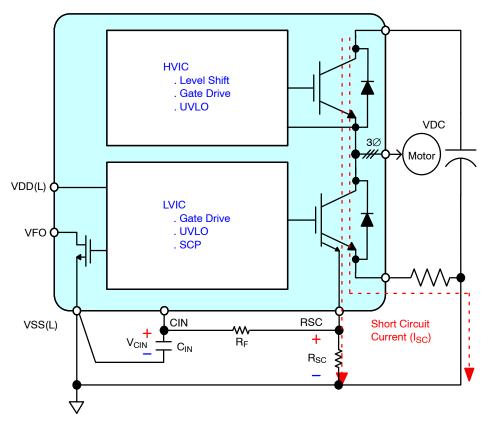

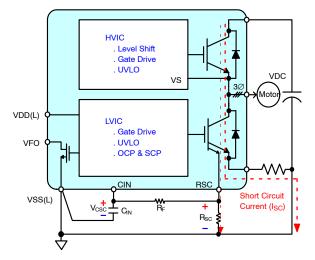

#### **Short Circuit Protection**

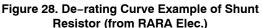

The 1200 V SPM 3 uses external shunt resistor for the short circuit current detection, as shown in Figure 12. LVIC has a built–in short–circuit current protection function. This protection function senses the voltage to the CIN pin. If this voltage (VCIN) exceeds the VSC(ref) (the threshold voltage trip level of over current protection) specified in the device datasheets (VSC(ref), typ. is 0.48 V), a fault signal is asserted and the all low side IGBTs are turned off.

Typically, the maximum short-circuit current magnitude is gate-voltage dependent: higher gate voltage (VDD and VBS) results in larger short-circuit current. To avoid potential problems, the maximum short circuit trip level is set below 1.5 times the nominal rated collector current. The LVIC short circuit protection timing chart is shown in Figure 12.

#### NOTES:

- 7. A1: normal operation: IGBT turn on and carrying current.

- 8. A2: short-circuit current detection (SC trigger).

- 9. A3: hard IGBT gate interrupt.

- 10.A4: IGBT turns off.

- 11. A5: fault output timer operation start with internal delay (min. 1.6 ms, CFOD = 22 pF), Fault-out duration time is controlled by CFOD. 12. A6: input "L": IGBT turn off state.

- 13.A7: input "H": IGBT turn on state, but during the active period of fault output the IGBT doesn't turn on.

- 14.A8: IGBT keeps turn off state

#### Figure 12. Operation of Short-Circuit Protection & Timing Chart of Short-Circuit Protection Function

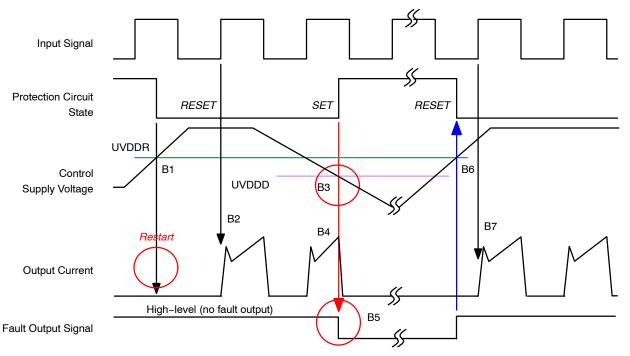

#### **Under-Voltage Lock Out Protection**

The LVIC has an Under-Voltage Lock Out protection (UVLO) function to protect the low-side IGBTs from

operation with insufficient gate driving voltage. A timing chart for this protection is shown in Figure 13.

NOTES: Low-Side Protection Sequence

15.B1: control supply voltage rise: the circuits starts to operate when the next input is applied after the voltage rises UVDDR.

16.B2: normal operation: IGBT turn on and carrying current.

17.B3: under-voltage detection UVDDD.

18. B4: IGBT turn off in spite of control input is alive.

19.B5: fault output signal starts.

20. B6: under-voltage reset UVDDR.

21.B7: normal operation: IGBT turn on and carrying current. If fault-out duration (tfod) by external capacitor at CIN pin is longer than UVDDR timing, fault output and IGBT state are cleared after tfod.

#### Figure 13. Timing Chart of Low-side Under-Voltage Protection Function

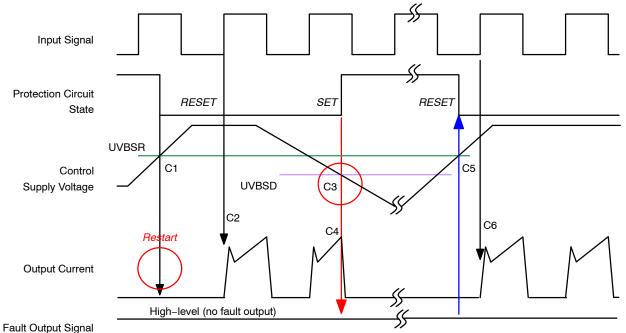

The HVIC has an under-voltage lockout function to protect the high-side IGBT from insufficient gate driving voltage. A timing chart for this protection is shown in Figure 14. A fault-out (VFO) alarm is not given for low HVIC bias conditions.

. . . .

NOTES: High–Side Protection Sequence

22.C1: control supply voltage rises: after the voltage reaches UVBSR, the circuit starts when the next input is applied.

23.C2: normal operation: IGBT turn on and carrying current.

24.C3: under-voltage detection (UVBSD).

25.C4: IGBT turn off in spite of control input is alive, but there is no fault output signal.

26.C5: under-voltage reset (UVBSR).

27.C6: normal operation: IGBT turn on and carrying current

#### Figure 14. Timing Chart of High-Side Under-Voltage Protection Function

## **KEY PARAMETER DESIGN GUIDANCE**

For stable operation, there are recommended parameters for passive components and bias conditions, considering operating characteristics of the 1200 V SPM 49 series

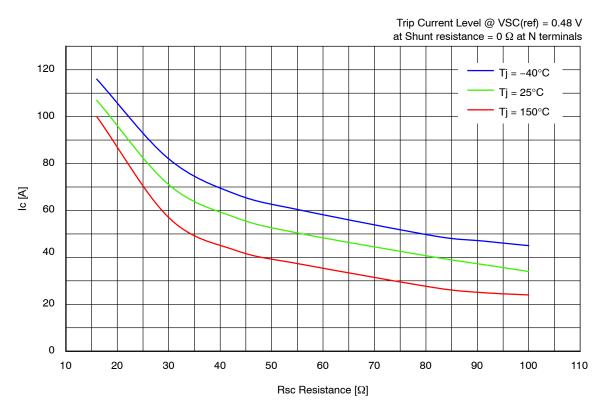

#### Selection of RSC Resistor for Protection

Figure 15 is an example circuit of the short-circuit protection using the  $R_{SC}$  resistor. Sense IGBT is employed for the low side. The designer can use the RSC pin for Over-Current Protection (OCP) and Short-Circuit Protection (SCP) without an external shunt resistor at the N-terminal. The line current on RSC is detected and the protective operation signal is passed through the RC filter. If the voltage (VCIN) exceeds the VSC(ref), all the gates of the N-side three IGBTs are turned off and the fault signal is

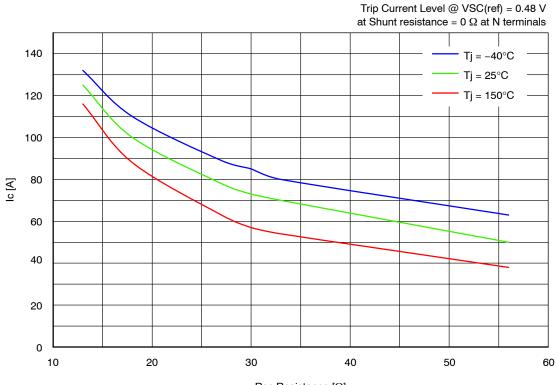

transmitted from SPM 49 to MCU. Since repetitive short circuit is not allowable, IGBT operation should be halted immediately when the fault signal is given. Figure 16 shows " $R_{SC}$  resistance vs. trip current" curve of NFAL5012L5B(T) under the shunt resistor = 0  $\Omega$  condition.

For current sensing, apply an external shunt resistor at each N terminal. Sensing voltage from RSC pin is influenced by an external shunt resistor, as shown in Figure 17.

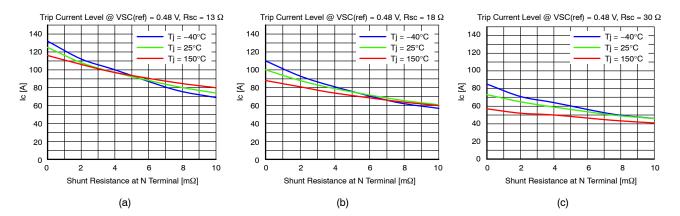

Figure 17 shows RSC value of NFAL5012L5B(T) under one-shunt resistor condition. For adequate RSC value in a three-shunt structure, the RSC value needs to be considered by the N-terminal shunt resistor value and target protection current level.

Figure 15. Function Current Path in Short-Circuit Condition by Leg Short Circuit

Figure 16. Rsc Resistance vs. Trip Current Level for Protection at Variable Junction Temperature of NFAL3512L5B(T)

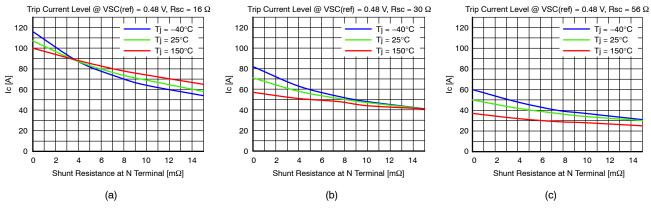

Figure 17. Trip Current Level vs. Shunt Resistor of NFAL3512L5B(T) (a):  $R_{SC}$  = 16  $\Omega$ , (b):  $R_{SC}$  = 30  $\Omega$ , (c):  $R_{SC}$  = 56  $\Omega$

Rsc Resistance  $[\Omega]$

Figure 18. Rsc Resistance vs. Trip Current Level for Protection at Variable Junction Temperature of NFAL5012L5B(T)

#### Thermal Sensor Output (TOT) and NTC Thermistor

The junction temperature of power devices should not exceed the maximum junction temperature. Even though there is some margin between the Max. Tj specified on the datasheet and the actual Max. Tj at which power devices get destroyed, caution should be given to make sure the junction temperature stays well below the Max. Tj. One of the inconveniences in using previous versions of SPM 49 series products was lack of temperature monitoring. An NTC had to be mounted on the heat sink or very close to the module if over-temperature protection is required in the application

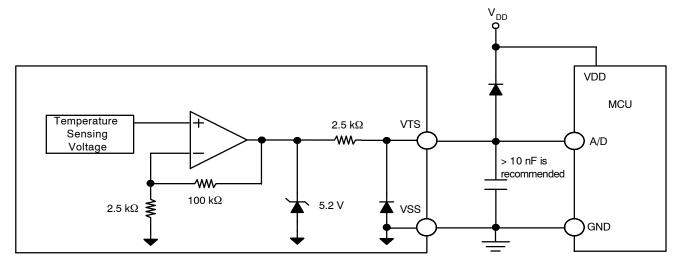

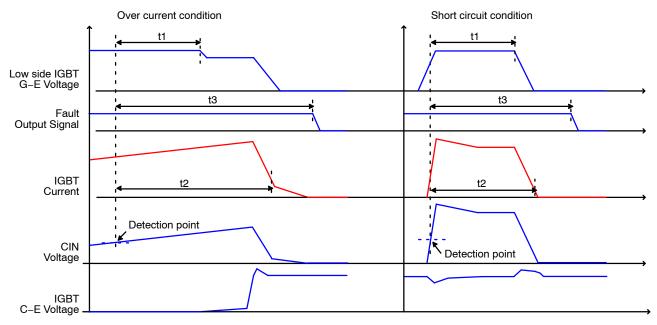

#### Circuit of VTS

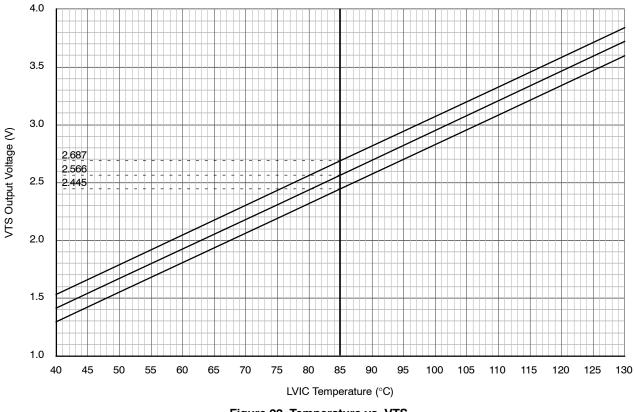

The Thermal Sensing Unit analog voltage output reflects the temperature of the LVIC in 1200 V SPM 49 version 6 series products. The relationship between VTS voltage output and LVIC temperature is shown in Figure 22. It does not have any self-protection function, and, therefore, it should be used appropriately based on application requirement. It should be noted that there is a time lag from IGBT temperature to LVIC temperature. It is very difficult to respond quickly when temperature rises sharply in a transient condition such as shoot-through event. Even though VTS has some limitation, it will be definitely useful in enhance the system reliability. Figure 20 shows the LVIC location of SPM 49 series.

Figure 20. Location of VTS Function (LVIC) and NTC

Figure 21. Internal Block Diagram and Interface Circuit of VTS

Figure 22. Temperature vs. VTS

Figure 21 shows the equivalent circuit diagram of VTS inside IC and a typical application diagram. This output voltage is clamped to 5.2 V by an internal Zener diode, but in case the maximum input range of Analog to Digital converter of MCU is below 5.2 V, an external Zener diode should be inserted between an A/D input pin and the analog ground pin of MCU. An amplifier can be used to change the range of voltage input to the Analog to Digital converter to have better resolution of the temperature. It is recommended to add a ceramic capacitor of 1000 pF between VTS and VSS (Signal Ground) to make the VTS more stable.

Therefore, the load connected to VTS pin should be minimized to maintain the accurate voltage output level without degradation. Figure 22 shows that the relationship between VTS voltage and LVIC temperature. It can be expressed as the following equation.

$VTS_{min} = 0.0256 \text{ x } T_{LVIC} + 0.269 [V]$

$VTS_{,typ} = 0.0256 \text{ x } T_{LVIC} + 0.390 \text{ [V]}$

$VTS_{max} = 0.0256 \text{ x } T_{LVIC} + 0.511 \text{ [V]}$

The maximum variation of VTS is 0.121 V, and the minimum variation of VTS is 0.121 V due to process

variation which is equivalent  $\pm 5^{\circ}$ C approximately. This is regardless of the temperature because the slopes of three lines are identical. If the ambient temperature information is available. For example, through NTC in the system, VTS can be measured to adjust the offset before the motor starts to operate. As temperature decreases further below 0°C, VTS decreases linearly until it reaches zero volts. If the temperature of LVIC increases above 150°C, which is above the maximum operating temperature, VTS would increase theoretically up to 5.2 V until it gets clamped by the internal zener diode.

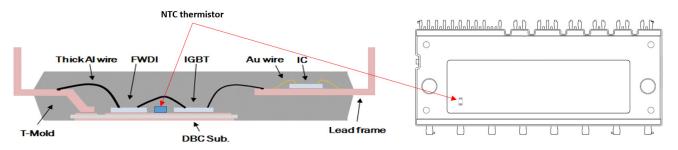

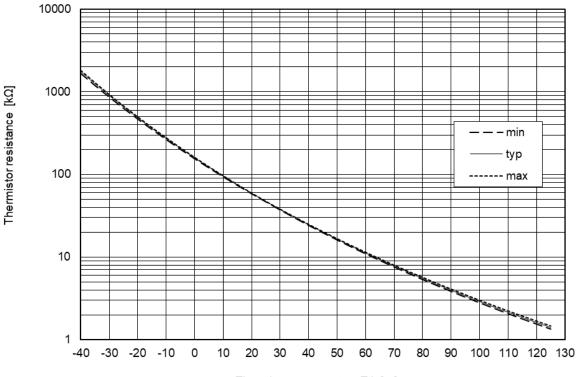

#### Circuit of NTC Thermistor

The Motion SPM 49 series includes a Negative Temperature Coefficient (NTC) thermistor for module internal temperature sensing. This thermistor is located in DBC substrate with the power chip (IGBT//FWDi).

Therefore, the thermistor can accurately reflect the temperature of the power chip (see Figure 23).

Figure 23. Location of NTC Thermistor in SPM 49 Package

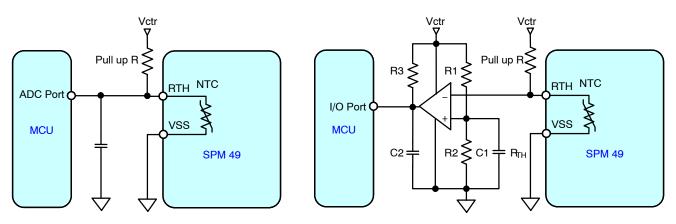

Normally, circuit designers use two kinds of circuit for temperature protection (monitoring) by NTC thermistor. One is circuit by Analog–Digital Converter (ADC). The other is circuit by comparator. Figure 24 shows examples of application circuits with an NTC thermistor.

Figure 24. Over Temperature Protection Circuit by MCU and Comparator

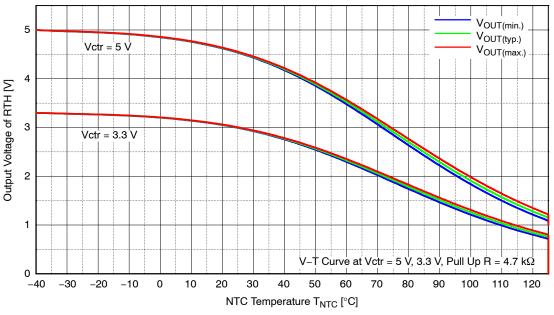

Figure 25. V – T Curve of Figure 24. Pull Up R = 4.7  $k\Omega$

| Symbol           | Parameter              | Condition  | Min.   | Тур.  | Max.   | Unit |

|------------------|------------------------|------------|--------|-------|--------|------|

| R <sub>25</sub>  | Resistance             | Tc = 25°C  | 46.530 | 47    | 47.47  | kΩ   |

| R <sub>125</sub> | Resistance             | Tc = 125°C | 1.320  | 1.406 | 1.497  | kΩ   |

| -                | B-Constant (25 - 50°C) | В          | 4009.5 | 4050  | 4090.5 | к    |

| -                | Temperature range      | -          | -40    | -     | +125   | °C   |

#### Table 3. THERMISTOR CHARACTERISTICS (BUILT-IN ONLY IN -T TYPE)

# Thermistor resistance versus Thermistor temperature Tth

Thermistor temperature Tth [°C]

Figure 26. Thermistor Resistance vs. Temperature

#### Table 4. R-T TABLE OF NTC THERMISTOR

| T <sub>NTC</sub> (°C) |          | -        | R <sub>max</sub> (kΩ) |    | R <sub>min</sub> (kΩ) | R <sub>cent</sub> (kΩ) | R <sub>max</sub> (kΩ) | T <sub>NTC</sub> (°C) | R <sub>min</sub> (kΩ) | R <sub>cent</sub> (kΩ) | R <sub>max</sub> (kΩ) |

|-----------------------|----------|----------|-----------------------|----|-----------------------|------------------------|-----------------------|-----------------------|-----------------------|------------------------|-----------------------|

| 0                     | 153.8063 | 158.2144 | 162.7327              | 42 | 22.1759               | 22.6466                | 23.1249               | 85                    | 4.4694                | 4.6736                 | 4.8866                |

| 1                     | 146.0956 | 150.1651 | 154.3326              | 43 | 21.2753               | 21.7401                | 22.2129               | 86                    | 4.3228                | 4.5226                 | 4.731                 |

| 2                     | 138.8168 | 142.5725 | 146.4152              | 44 | 20.4158               | 20.8746                | 21.3416               | 87                    | 4.1817                | 4.3771                 | 4.5811                |

| 3                     | 131.9431 | 135.4081 | 138.9502              | 45 | 19.5953               | 20.0478                | 20.5088               | 88                    | 4.0459                | 4.2369                 | 4.4366                |

| 4                     | 125.4497 | 128.6453 | 131.9091              | 46 | 18.812                | 19.258                 | 19.7126               | 89                    | 3.915                 | 4.1019                 | 4.2973                |

| 5                     | 119.3135 | 122.2594 | 125.2655              | 47 | 18.0638               | 18.5032                | 18.9514               | 90                    | 3.789                 | 3.9717                 | 4.1629                |

| 6                     | 113.5129 | 116.2273 | 118.9947              | 48 | 17.3492               | 17.7818                | 18.2234               | 91                    | 3.6675                | 3.8463                 | 4.0334                |

| 7                     | 108.0276 | 110.5275 | 113.0739              | 49 | 16.6663               | 17.0921                | 17.5269               | 92                    | 3.5505                | 3.7253                 | 3.9084                |

| 8                     | 102.8388 | 105.1398 | 107.4814              | 50 | 16.0137               | 16.4325                | 16.8605               | 93                    | 3.4377                | 3.6087                 | 3.7879                |

| 9                     | 97.9288  | 100.0454 | 102.1974              | 51 | 15.3899               | 15.8016                | 16.2227               | 94                    | 3.329                 | 3.4963                 | 3.6716                |

| 10                    | 93.2812  | 95.2267  | 97.2031               | 52 | 14.7934               | 15.1981                | 15.6122               | 95                    | 3.2242                | 3.3878                 | 3.5593                |

| 11                    | 88.8803  | 90.6673  | 92.481                | 53 | 14.223                | 14.6205                | 15.0277               | 96                    | 3.1235                | 3.2836                 | 3.4515                |

| 12                    | 84.7119  | 86.3519  | 88.0148               | 54 | 13.6773               | 14.0677                | 14.4678               | 97                    | 3.0264                | 3.183                  | 3.3473                |

| 13                    | 80.7624  | 82.2661  | 83.7894               | 55 | 13.1552               | 13.5385                | 13.9316               | 98                    | 2.9328                | 3.086                  | 3.2468                |

| 14                    | 77.019   | 78.3963  | 79.7903               | 56 | 12.6556               | 13.0318                | 13.4178               | 99                    | 2.8425                | 2.9923                 | 3.1497                |

| 15                    | 73.47    | 74.7302  | 76.0043               | 57 | 12.1774               | 12.5465                | 12.9255               | 100                   | 2.7553                | 2.9019                 | 3.0559                |

| 16                    | 70.1042  | 71.2558  | 72.4189               | 58 | 11.7195               | 12.0815                | 12.4536               | 101                   | 2.6712                | 2.8146                 | 2.9654                |

| 17                    | 66.9112  | 67.962   | 69.0224               | 59 | 11.281                | 11.6361                | 12.0011               | 102                   | 2.5901                | 2.7303                 | 2.8779                |

| 18                    | 63.8812  | 64.8386  | 65.8039               | 60 | 10.861                | 11.2091                | 11.5673               | 103                   | 2.5117                | 2.6489                 | 2.7933                |

| 19                    | 61.005   | 61.8759  | 62.753                | 61 | 10.4594               | 10.8007                | 11.152                | 104                   | 2.436                 | 2.5703                 | 2.7117                |

| 20                    | 58.2739  | 59.0647  | 59.8601               | 62 | 10.0746               | 10.4091                | 10.7536               | 105                   | 2.363                 | 2.4943                 | 2.6327                |

| 21                    | 55.6798  | 56.3961  | 57.116                | 63 | 9.7058                | 10.0336                | 10.3714               | 106                   | 2.2921                | 2.4206                 | 2.556                 |

| 22                    | 53.2152  | 53.8628  | 54.5127               | 64 | 9.3522                | 9.6734                 | 10.0046               | 107                   | 2.2236                | 2.3493                 | 2.4819                |

| 23                    | 50.8732  | 51.4569  | 52.0422               | 65 | 9.0133                | 9.3279                 | 9.6525                | 108                   | 2.1575                | 2.2805                 | 2.4102                |

| 24                    | 48.6469  | 49.1715  | 49.6969               | 66 | 8.6882                | 8.9963                 | 9.3145                | 109                   | 2.0936                | 2.2139                 | 2.3409                |

| 25                    | 46.53    | 47       | 47.47                 | 67 | 8.3764                | 8.6782                 | 8.9899                | 110                   | 2.0319                | 2.1496                 | 2.2739                |

| 26                    | 44.4567  | 44.936   | 45.4159               | 68 | 8.0773                | 8.3727                 | 8.6782                | 111                   | 1.9725                | 2.0877                 | 2.2094                |

| 27                    | 42.4868  | 42.9737  | 43.4618               | 69 | 7.7902                | 8.0795                 | 8.3787                | 112                   | 1.9151                | 2.0278                 | 2.147                 |

| 28                    | 40.6147  | 41.1075  | 41.6021               | 70 | 7.5147                | 7.7979                 | 8.091                 | 113                   | 1.8596                | 1.9699                 | 2.0866                |

| 29                    | 38.8351  | 39.3323  | 39.8319               | 71 | 7.2496                | 7.5268                 | 7.8138                | 114                   | 1.806                 | 1.9139                 | 2.0282                |

| 30                    | 37.1428  | 37.6431  | 38.1463               | 72 | 6.995                 | 7.2663                 | 7.5474                | 115                   | 1.7541                | 1.8598                 | 1.9716                |

| 31                    | 35.5329  | 36.0351  | 36.5408               | 73 | 6.7505                | 7.016                  | 7.2913                | 116                   | 1.7042                | 1.8076                 | 1.9171                |

| 32                    | 34.0011  | 34.5041  | 35.0111               | 74 | 6.5157                | 6.7755                 | 7.045                 | 117                   | 1.6559                | 1.7572                 | 1.8644                |

| 33                    | 32.5433  | 33.0462  | 33.5534               | 75 | 6.2901                | 6.5443                 | 6.8082                | 118                   | 1.6092                | 1.7083                 | 1.8134                |

| 34                    | 31.1555  | 31.6573  | 32.164                | 76 | 6.0739                | 6.3227                 | 6.581                 | 119                   | 1.564                 | 1.6611                 | 1.7639                |

| 35                    | 29.834   | 30.3339  | 30.8392               | 77 | 5.8662                | 6.1096                 | 6.3624                | 120                   | 1.5203                | 1.6153                 | 1.7161                |

| 36                    | 28.576   | 29.0734  | 29.5764               | 78 | 5.6665                | 5.9046                 | 6.1521                | 121                   | 1.4777                | 1.5707                 | 1.6694                |

| 37                    | 27.3776  | 27.8717  | 28.372                | 79 | 5.4745                | 5.7075                 | 5.9498                | 122                   | 1.4365                | 1.5276                 | 1.6242                |

| 38                    | 26.2356  | 26.726   | 27.2228               | 80 | 5.2899                | 5.5178                 | 5.7549                | 123                   | 1.3966                | 1.4858                 | 1.5804                |

| 39                    | 25.1472  | 25.6332  | 26.1261               | 81 | 5.1129                | 5.3358                 | 5.568                 | 124                   | 1.358                 | 1.4453                 | 1.538                 |

| 40                    | 24.1094  | 24.5907  | 25.0792               | 83 | 4.7788                | 4.9921                 | 5.2145                | 125                   | 1.3206                | 1.406                  | 1.4969                |

| 41                    | 23.1198  | 23.596   | 24.0796               | 84 | 4.6211                | 4.8299                 | 5.0475                |                       |                       |                        |                       |

#### **Selection of Shunt Resistor**

Figure 27 shows an example circuit of the SC protection using 1-shunt resistor. The line current on the N side DC-link is detected and the protective operation signal is passed through the RC filter. If the current exceeds the SC reference level, all the gates of the N-side three-phase IGBTs are switched to the off state and the VFO fault signal is transmitted to MCU. Since SC protection is non-repetitive, IGBT operation should be immediately halted when the VFO fault signal is given.

Figure 27. Short Circuit Current Protection Circuit with One Shunt Resistor

The value of shunt resistor is calculated by the following equation.

Maximum over current trip level:  $I_{OC(max)} = 1.5 \text{ x } I_C \text{ (rated current)}$ SC trip referenced voltage:  $V_{SC}$  = min. 0.45 V, typ. 0.48 V, max. 0.51 V Shunt resistance:  $I_{SC(max)} = V_{SC(max)} / R_{SHUNT(min)} \rightarrow R_{SHUNT(min)} =$ V<sub>SC(max)</sub> / I<sub>SC(max)</sub> If the deviation of shunt resistor should is limited below ±5 %,  $R_{SHUNT(typ)} = R_{SHUNT(min)} / 0.95, R_{SHUNT(max)} =$ R<sub>SHUNT(typ)</sub> x 1.05 Actual SC trip current level becomes:  $I_{SC(tvp)} = V_{SC(tvp)} / R_{SHUNT(min)}, I_{SC(min)} = V_{SC(min)} /$ R<sub>SHUNT(max)</sub> Inverter output power:  $P_{OUT} = \sqrt{3} \times VO, LL \times I_{O(RMS)} \times PF$ Where: VO,LL =  $(\sqrt{3} / \sqrt{2}) \times MI \times (V_{DC} / 2)$ I(O)RMS = Maximum load current of inverter; and MI = Modulation Index;

VDC = DC link voltage;

PF = Power Factor

Average DC Current

```

I_{DC_{AVG}} = V_{DC_{Link}} / (P_{out} \times Eff)

```

Where:

Eff = Inverter Efficiency

The power rating of shunt resistor is calculated by the following equation.

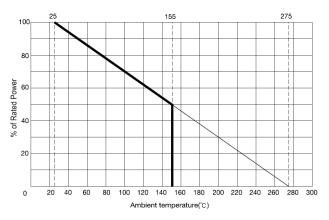

$P_{SHUNT} = (I_{RMS}^2 \times R_{SHUNT} \times Margin) / De-rating Ratio Where:$

Shunt resistor typical value at  $T_C = 25^{\circ}C(R_{SHUNT})$

De-rating ratio of shunt resistor at  $T_{SHUNT} = 100^{\circ}C$  (From datasheet of shunt resistor)

Safety margin (Determine by customer)

The calculation examples for shunt resistance:

DUT: NFAL5012L5B(T)

Tolerance of shunt resistor:  $\pm 5\%$

Over Current Trip Reference Voltage:

$Vsc(ref)_{min} = 0.46$  V,  $Vsc(ref)_{typ} = 0.48$  V,  $Vsc(ref)_{max} = 0.50$  V

Maximum Load Current of Inverter (IRMS): 35 Arms

Maximum Peak Load Current of Inverter (I<sub>C(max)</sub>): 75 A

Modulation Index(MI): 0.9

DC Link Voltage(V<sub>DC Link</sub>): 600 V

Power Factor (PF): 0.8

Inverter Efficiency (Eff): 0.95

Shunt Resistor Value at  $T_C = 25^{\circ}C (R_{SHUNT})$ : 7 m $\Omega$

De-rating Ration of Shunt Resistor at  $T_{SHUNT} = 100^{\circ}C$ : 70% (refer to Figure 28)

Safety Margin: 20%

Calculation results:

$$\begin{split} &I_{SC(max)}: 1.5 \ x \ I_{C(max)} = 1.5 \ x \ 50 \ A = 75 \ A \\ &R_{SHUNT(typ)}: \\ &V_{SC}(ref)\__{typ} \ / \ I_{SC(max)} = 0.48 \ V \ / \ 75 \ A = 6.4 \ m\Omega \\ &R_{SHUNT(max)}: \\ &R_{SHUNT(max)} \ x \ 1.05 = 6.4 \ m\Omega \ x \ 1.05 \ A = 6.72 \ m\Omega \\ &R_{SHUNT(min)}: \\ &R_{SHUNT(min)}: \\ &R_{SHUNT(min)}: \\ &V_{SC}(ref)\__{min} \ / \ R_{SHUNT(max)} = 0.45 \ V \ / \ 6.72 \ m\Omega = 67 \ A \\ &I_{SC(max)}: \\ &V_{SC}(ref)\__{max} \ / \ R_{SHUNT(min)} = 0.51 \ V \ / \ 6.08 \ m\Omega = 84 \ A \\ &P_{OUT} \ \sqrt{3} \ x \ ((\sqrt{3} \ / \ \sqrt{2}) \ x \ MI \ (V_{DC} \ / \ 2)) \ x \ I_{(0)RMS} \ x \ PF = (3 \ / \ \sqrt{2}) \ x \ 0.9 \ x \ (600 \ / \ 2) \ x \ 35 \ x \ 0.8 = 16 \ kW \\ &I_{DC\_AVG} = (P_{OUT} \ / \ Eff) \ / \ V_{DC\_Link} = 28.07 \ A \\ &P_{SHUNT} = (I^2_{DC} \ AVG \ x \ R_{SHUNT} \ x \ Margin) \ / \ De-rating \end{split}$$

$P_{SHUNT} = (I_{DC_{AVG}} \times R_{SHUNT} \times Margin) / De-rating Ratio = (28.07^2 \times 0.0065 \times 1.2) / 0.7 = 8.8 W (therefore, the proper power rating of shunt resistor is over 9 W).$

When over-current events are detected, the 1200 V Motion SPM 49 series shuts down all low-side IGBTs and sends out the fault-out (VFO) signal. FAULT output timer operation start with internal delay (typ. 4.0  $\mu$ s), Fault-out duration time is controlled by CFOD. To prevent

malfunction, it is recommended that an RC filter be inserted at the CIN pin. To shut down IGBTs within 3  $\mu$ s when over-current situation occurs, a time constant of 0.75~1.25  $\mu$ s is recommended. Table 5 shows the shunt resistance and typical short-circuit protection current

Table 5. RECOMMENDED OVER-CURRENT (OC) PROTECTION TRIP LEVEL FOR 1200 V RATED SPM 49

| Device         | R <sub>SHUNT</sub> | OC Trip Level | Remark              |

|----------------|--------------------|---------------|---------------------|

| NFAL3512L5B(T) | 9.0 mΩ             | 52 A          | It is typical value |

| NFAL5012L5B(T) | 6.4 m $\Omega$     | 75 A          |                     |

#### **Time Constant of Internal Delay**

An RC filter is prevents noise-related over and short circuit current protection (OCP, SCP) circuit malfunction. The RC time constant is determined by the applied noise filter time and the Short-Circuit Withstanding Time (SCWT) of SPM 49 version series.

When the  $R_{shunt}$  voltage exceeds the VSC(ref) level, this is applied to the CIN pin via the RC filter. The RC filter delay is the time required for the CIN pin voltage to rise to the referenced OCP & SCP level. The LVIC has an internal filter time (logic filter time for noise elimination: around 0.85 µs). Consider this filter time when designing the RC filter of CIN pin Figure 29 shows actual real time at over and short circuit current protection. Each time sections have a distribution, so we have to consider of distribution

Figure 29. Timing Diagram of Over and Short Circuit Protection

# Table 6. TIME TABLE OF OVER AND SHORT CIRCUIT CONDITIONS; VSC(REF) TO LOW SIDE GATE, COLLECTOR CURRENT AND VFO

| Ref. Condition<br>VDCbus = 600 V, VDD = 15 V |                     | (       | Over Current Condition. 2 * I rating |         |      |         |      | Short Circuit Condition |      |         |      |         |      |

|----------------------------------------------|---------------------|---------|--------------------------------------|---------|------|---------|------|-------------------------|------|---------|------|---------|------|

|                                              |                     | t1 (μs) |                                      | t2 (μs) |      | t3 (μs) |      | t1 (μs)                 |      | t2 (μs) |      | t3 (μs) |      |

| Device                                       | T <sub>J</sub> (°C) | Тур.    | Max.                                 | Тур.    | Max. | Тур.    | Max. | Тур.                    | Max. | Тур.    | Max. | Тур.    | Max. |

| NFAL2512L5B(T)                               | 25                  | 1.05    | 1.30                                 | TBD     | TBD  | 4.0     | 5.0  | 1.05                    | 1.30 | TBD     | TBD  | 4.0     | 5.0  |

|                                              | 150                 | 1.0     | 1.25                                 | TBD     | TBD  | 3.2     | 4.2  | 1.0                     | 1.25 | TBD     | TBD  | 3.2     | 4.2  |

| NFAL3512L5B(T)                               | 25                  | 1.05    | 1.30                                 | TBD     | TBD  | 4.0     | 5.0  | 1.05                    | 1.30 | TBD     | TBD  | 4.0     | 5.0  |

|                                              | 150                 | 1.0     | 1.25                                 | TBD     | TBD  | 3.2     | 4.2  | 1.0                     | 1.25 | TBD     | TBD  | 3.2     | 4.2  |

| NFAL5012L5B(T)                               | 25                  | 1.05    | 1.30                                 | TBD     | TBD  | 4.0     | 5.0  | 1.05                    | 1.30 | TBD     | TBD  | 4.0     | 5.0  |

|                                              | 150                 | 1.0     | 1.25                                 | TBD     | TBD  | 3.2     | 4.2  | 1.0                     | 1.25 | TBD     | TBD  | 3.2     | 4.2  |

28. To guarantee safe short-circuit protection under all operating conditions, CIN should be triggered within 1.0 μs after short-circuit occurs. (Recommendation: SCWT < 3.0 μs, Conditions: VDC = 400 V, VDD = 16.5 V, Tj = 150°C).

29. It is recommended that delay from short-circuit to CIN triggering should be minimized.

30.t1: from CIN detection to gate driver LO shut down

31.t2: from CIN detection to collector current 10%

32.t3: from CIN detection to fault out signal activation

#### **Fault Output Circuit**

Because VFO terminal is an open-drain type; it should be pulled up via a pull-up resistor.

#### Figure 30. Voltage–Current Characteristics of VFO Terminal

#### Circuit of Input Signal (HINx, LINx)

Figure 32 shows recommended I/O interface circuit between the MCU and SPM 49. Because SPM 49 input logic is active HIGH and there are built–in pull–down resistors, external pull–down resistors are not needed.

The fault output is open drain and its rating is VDD + 0.5, 15 V supply interface is possible.

However, it is recommended that the fault output be configured with the 3.3 V or 5 V logic supplies, which is the same as the input signals. It is also recommended that the decoupling capacitors be placed at both the MCU and Motion SPM 49 ends of the VFO signal line, as close as

Figure 31. Voltage–Current Characteristics of VFO Terminal

possible to each device. The RC coupling at each input (parts shown dotted in Figure 32) can be changed depending on the PWM control scheme used in the application and the wiring impedance of the PCB layout.

The input signal section of the Motion SPM 49 series integrates a 5 k $\Omega$  (typical) pull-down resistor. Therefore, when using an external filtering resistor between the MCU output and the Motion SPM 49 input, attention should be given to the signal voltage drop at the Motion SPM 49 input terminals to satisfy the turn on threshold voltage requirement. For instance, R = 100  $\Omega$  and C = 1 nF for the parts shown dotted in Figure 32.

Figure 32. Recommended MCU I/O Interface Circuit

#### **Bootstrap Circuit Design**

#### Operation of Bootstrap Circuit

The V<sub>BS</sub> voltage, which is the voltage difference between VB(X) and VS(X), provides the supply to the HVIC within the 1200 V SPM 49 series. This supply must be in the range of 13.0 V~18.5 V to ensure that the HVIC can fully drive the high–side IGBT. The SPM 49 series includes an under–voltage lock out protection function for the VBS to ensure that the HVIC does not drive the high–side IGBT, if the VBS voltage drops below a specified voltage. This function prevents the IGBT from operating in a high

dissipation mode. There are a number of ways in which the VBS floating supply can be generated. One of them is the bootstrap method described here (refer to Figure 33). This method has the advantage of being simples and inexpensive. However, the duty cycle and on-time are limited by the requirement to refresh the charge in the bootstrap capacitor. The bootstrap to ground (either through the low-side or the load), the bootstrap capacitor ( $C_{BOOT}$ ) is charged through the bootstrap diode ( $D_{BOOT}$ ) and the resistor ( $R_{BOOT}$ ) from the VDD supply.

Figure 33. Current Path of Bootstrap Circuit

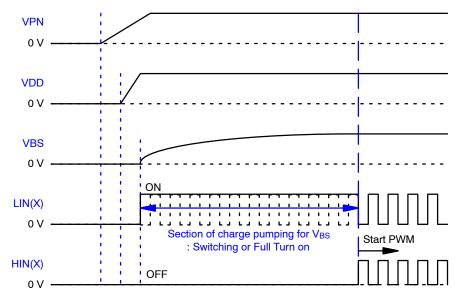

# Selection of Bootstrap Capacitor Considering Initial Charging

Adequate on-time of the low-side IGBT to fully charge the bootstrap capacitor is required for initial bootstrap charging. The initial charging time  $(t_{charge})$  can be calculated by:

$$t_{charge} = C_{BOOT} \times R_{BOOT} \times \frac{1}{\Delta} \times In \frac{V_{DD}}{VDD - VBS(min.) - VF - VLS}$$

(eq. 1)

Where:

VF = Forward voltage drop across the bootstrap diode; VBS(min.) =The minimum value of the bootstrap capacitor; VLS = Voltage drop across the low-side IGBT or load; and  $\Delta$  = Duty ratio of PWM.

When the bootstrap capacitor is charged initially; VDD drop voltage is generated based on initial charging method, VDD line SMPS output current, VDD source capacitance, and bootstrap capacitance. If VDD drop voltage reaches UVDDD level, the low side is shut down and a fault signal is activated.

To avoid this malfunction, related parameter and initial charging method should be considered. To reduce VDD voltage drop at initial charging, a large VDD source capacitor and selection of optimized low-side turn-on method are recommended. Adequate on-time duration of the low-side IGBT to fully charge the bootstrap capacitor is initially required before normal operation of PWM starts.

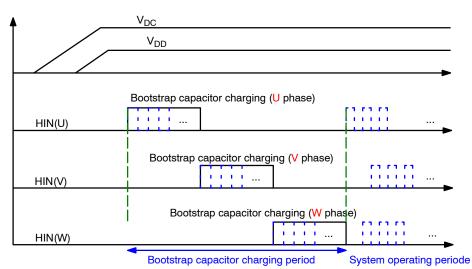

Figure 34 shows an example of initial bootstrap charging sequence. Once VDD establishes, VBS needs to be charged by turning on the low-side IGBTs. PWM signals are typically generated by an interrupt triggered by a timer with a fixed interval, based on the switching carrier frequency.

Therefore, it is desired to maintain this structure without creating complementary high-side PWM signals. The capacitance of VDD should be sufficient to supply necessary charge to VBS capacitance in all three phases. If a normal PWM operation starts before VBS reaches UVLO reset level, the high-side IGBTs cannot switch without creating a fault signal. It may lead to a failure of motor start in some applications. If three phases are charged synchronously, initial charging current through a single shunt resistor may exceed the over-current protection level.

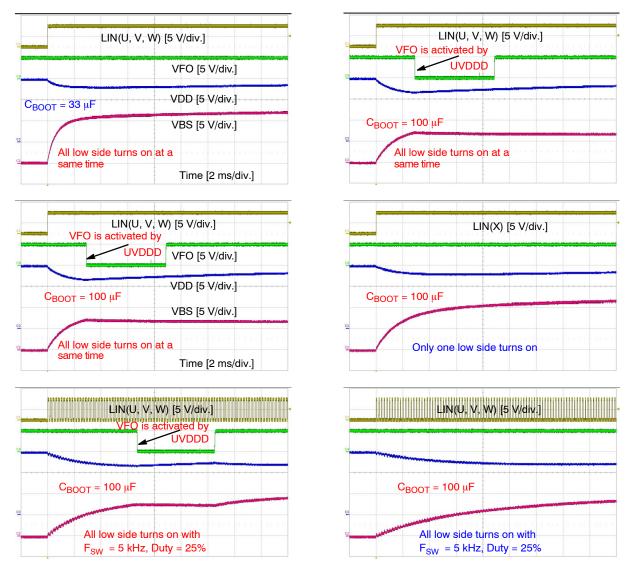

Therefore, initial charging time for bootstrap capacitors should be separated, as shown in Figure 35. The effect of the bootstrap capacitance factor and charging method (low-side IGBT driving method) is shown in Figure 36.

Figure 34. Timing Chart of Initial Bootstrap Charging

Figure 36. Initial Charging According to Bootstrap Capacitance and Charging Method (Ref. Condition: VDD = 15 V / 300 mA, VDD Capacitor = 220  $\mu$ F, C<sub>BOOT</sub> = 100  $\mu$ F, R<sub>BOOT</sub> = 20  $\Omega$ )

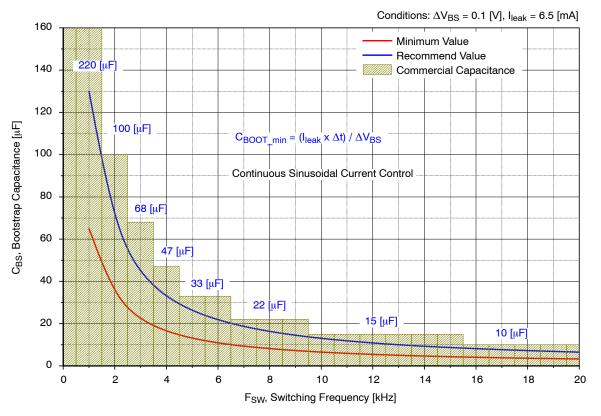

#### Selection of Bootstrap Capacitor Considering Operating The bootstrap capacitance can be calculated by:

$$C_{BOOT} = \frac{I_{leak} \times \Delta t}{\Delta V_{BS}}$$

(eq. 2)

Where:

$\Delta$ t: maximum on pulse width of high-side IGBT;  $\Delta$ V<sub>BS</sub>: the allowable discharge voltage of the C<sub>BOOT</sub>

(voltage ripple); and

$I_{leak}$ : maximum discharge current of the  $C_{\mbox{BOOT}}$

Mainly via the following mechanisms:

Gate charge for turning the high-side IGBT on. Quiescent current to the high-side circuit in HVIC.

Level-shift charge required by level-shifters in HVIC.

Leakage current in the bootstrap circuit.

$C_{BOOT}$  capacitor leakage current (ignored for non-electrolytic capacitors).

Bootstrap diode reverse recovery charge.

Practically, 6.5 mA of  $I_{leak}$  is recommended for the 1200 V SPM 49 series. By considering dispersion and reliability, the capacitance is generally selected to be 2~3 times the calculated one. The C<sub>BOOT</sub> is only charged when the high-side IGBT is off and the VS(x) voltage is pulled down to ground.

The on-time of the low-side IGBT must be sufficient to for the charge drawn from the  $C_{BOOT}$  capacitor to be fully replenished. This creates an inherent minimum on-time of the low-side IGBT (or off-time of the high-side IGBT).

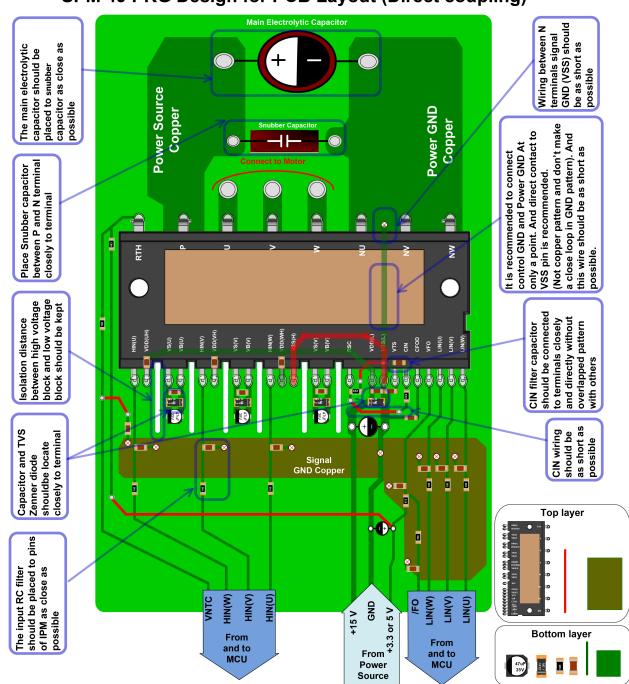

Figure 37. Capacitance of Bootstrap Capacitor on Variation of Switching Frequency