**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# AMIS-30660/42000 -Topology Aspects of a High-Speed CAN Bus

# **ON Semiconductor®**

http://onsemi.com

# **APPLICATION NOTE**

Although these points are analyzed separately, all of them should be considered and the resulting conditions should be fulfilled simultaneously in order to achieve a correct bus topology.

#### **DEFINITION OF CAN BIT TIMING**

#### **Parameter Definition**

This paragraph gives an abbreviated definition of parameters related to the CAN bit timing which will be used later in relation with the bus topology aspects.

A CAN bus system uses a nominal bit rate  $f_{nbr}$  (in bits per second) which is uniform throughout the network. To each bit corresponds an interval of time:

$$\mathsf{T}_{\mathsf{bit}} = \frac{1}{f_{\mathsf{nbr}}}$$

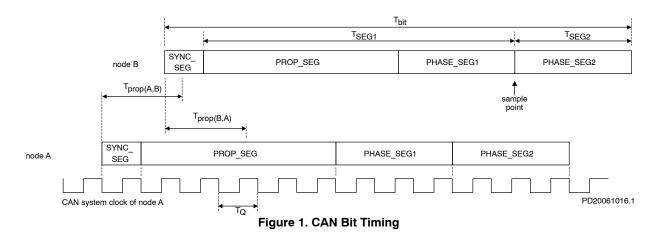

As defined in detail in [1], each node in a CAN network has to perform frequent "hard synchronization" and "re–synchronization" in order to ensure correct data processing according the CAN protocol. For the purpose of the synchronization, the CAN controller regards each bit period as being split to several segments as shown in Figure 1.

The time in a CAN node is referred to a CAN system clock, the period of which is called "time quantum"  $T_Q$ . ISO CAN norm [1] requires that each bit period is split to 8–25 time quanta, i.e. that the CAN system clock is 8–25 times faster than the nominal bit rate. The CAN system clock controls the bit timing and sampling of the bus state. The CAN system clock is derived from the node local oscillator by means of a prescaler. The choice of the local oscillator frequency and of the time quantum value derived from the local oscillator is a task of the CAN system design.

#### Introduction

AMIS-30660, together with AMIS-42000, is a family of high speed CAN transceiver products intended for automotive and industrial applications. Although individual members of the product family differ in some aspects – operation modes, additional features, single-channel bus versus bus-repeater etc. – they all incorporate high-speed CAN transceiver(s) compliant with ISO11898 norm. The transceiver functional blocks throughout the product family share the same set of limitations which have to be considered when designing the topology of the CAN bus which they interface.

A CAN bus topology is determined by the number of nodes, maximum allowed bus length and the maximum allowed length of unterminated stubs connected to the main bus line. These topology parameters are mainly defined by:

- 1. The delay of the line and the loop delay of the nodes (loop delay is the sum of the receiver delay, the transmitter delay and the delays of the interface lines between the transceiver and the CAN controller)

- 2. The signal amplitude drop due to the non-zero bus wire resistance and the finite input resistance of the nodes

- 3. Differences of oscillator frequency between nodes

This application note deals with points 1 and 2, whereas point 3 - the oscillator frequency tolerance - is not considered.

After a definition of CAN bit timing related terms and parameters in the "Definition of CAN Bit Timing" section, the application note addresses the following questions in individual chapters:

- 1. What is the maximum bus length if the bit timing parameters are known?

- 2. What is the maximum length of unterminated stubs if the bit timing parameters are known?

- 3. What is the maximum bus length for a given number of nodes which still guarantees sufficient signal amplitude?

- 4. What is the maximum number of nodes which can be driven by the given CAN transceiver?

Each bit period begins with a SYNC\_SEG, the duration of which is fixed to one period of the CAN system clock. Transmitting node begins to drive the bus at the beginning of the SYNC\_SEG, whereas a correctly synchronized receiving node expects every edge on the bus arriving during SYNC SEG.

The bit period continues with a PROP\_SEG, a period fixed by the CAN system design to 1–8 time quanta. It's the minimum time a receiver will wait before accepting a valid bus value sample. Following segments PHASE\_SEG1 and PHASE\_SEG2 are periods of time which are adapted during the "re–synchronization" in order to move the "sample point". The maximum allowed one–time modification of the PHASE\_SEG1 or PHASE\_SEG2 is referred to as SJW, or "synchronization jump width".

Some definitions or software packages might use an alternative set of terms, splitting the bit period to SYNC SEG, SEG1 and SEG2 (see Figure 1), where:

$$T_{SEG1} = T_{PROP\_SEG} + T_{PHASE\_SEG1}$$

$$T_{SEG2} = T_{PHASE\_SEG2}$$

However, the CAN timing remains identical, as these definitions are purely formal.

The bus state detected at the "sample point" is accepted by the receiving node as the logical value valid for the current bit period. Under the worst case conditions, by modifying the duration of PHASE\_SEG1 and PHASE\_SEG2, the sample point might arrive as early as immediately after the PROP SEG part of the bit period.

# Maximum Bus Length in Function of Maximum Bus Line Delay

To identify the permissible maximum line delay, the node relation in Figure 1 has to be considered. During an "acknowledge" field, the transmitting node (node A) transmits a recessive bit but expects a dominant bit being transmitted by other nodes (node B in the figure). For the "acknowledge" field to be correctly received, node A has to sample "dominant" at his sample point.

As explained in "Definition of CAN Bit Timing" section, the sample point might arrive as early as immediately after the PROP\_SEG period, which must thus accommodate for all propagation delays between node A and node B:

## $T_{PROP SEG} \ge T_{PROP(A,B)} + T_{PROP(B,A)}$

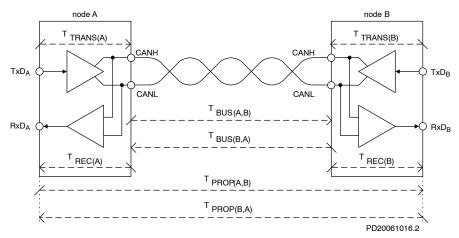

The propagation delays are the total delays between the CAN controller interface of node A (pins  $TxD_A$  and  $RxD_A$ ) and the CAN controller interface of node B (pins  $TxD_B$  and  $RxD_B$ ) and their components are shown in Figure 2.

Figure 2. Components of the CAN Bus Delay

The delays can be expressed as follows:

$$T_{PROP(A,B)} = T_{TRANS(A)} + T_{BUS(A,B)} + T_{REC(B)}$$

$$T_{PROP(B,A)} = T_{TRANS(B)} + T_{BUS(B,A)} + T_{REC(A)}$$

Where:

$T_{BUS(X,Y)}$  is the proper bus line delay from node X to node Y.

$T_{TRANS(X)}$  and  $T_{REC(X)}$  are delays of node X transmitter and receiver parts, respectively.

The sum of  $T_{TRANS(X)}$  and  $T_{REC(X)}$  can be found in specifications of CAN transceivers as "propagation delay TxD to RxD".

The bus line is then limited by the following formula:

$$L_{\text{BUS}_{MAX}_{DEL}} = \frac{\left(\frac{{}^{\text{T}_{\text{PROP}_{SEG}}}}{2} - {}^{\text{T}_{\text{PROP}(\text{RxD},\text{TxD})}}\right)}{{}^{\text{T}_{\text{PROP}(\text{BUS})}}}$$

Where:

$L_{BUS\_MAX\_DEL}$  is the biggest allowed distance between any two nodes.

$T_{PROP\_SEG}$  is the length of PROP\_SEG part of one bit period.

$T_{PROP(RxD,TxD)}$  is the propagation delay TxD to RxD of the used CAN transceiver.

T<sub>PROP(BUS)</sub> is the bus line delay per unit length.

#### Example

Given:

AMIS-42665 transceivers will be used with the following relevant parameters (extract from the datasheet):

| Symbol                   | Parameter                    | Conditions | Min | Max | Unit |

|--------------------------|------------------------------|------------|-----|-----|------|

| t <sub>pd(rec-dom)</sub> | Propagation Delay TxD to RxD |            | 70  | 230 | ns   |

| t <sub>pd(dom-rec)</sub> | Propagation Delay TxD to RxD |            | 100 | 245 | ns   |

The transceiver delay is slightly different for opposite edges (recessive to dominant vs. dominant to recessive). To analyze the worst case, we will take 245 ns.

The bus line has a delay of 5 ns per 1 m length

The bit rate of 500 kbps is required, resulting in 1 bit period of 2  $\mu s$

The CAN controller is setup to have PROP\_SEG equal to 1100 ns

Then:

The maximum permissible bus line delay is (1100 ns / 2 - 245 ns) = 305 ns.

The maximum allowed distance between any two nodes  $L_{BUS MAX DEL}$  is 61 m (= 305 ns / 5 ns).

#### **Maximum Unterminated Stub Length**

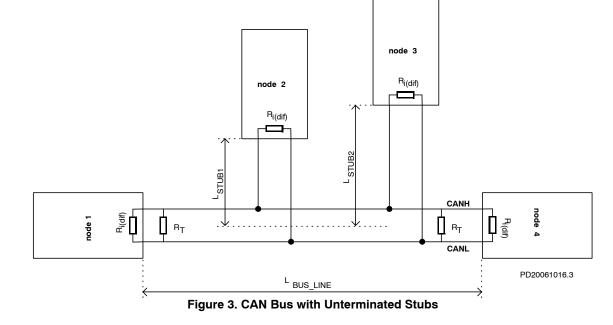

A CAN bus is intended to be as close as possible to a single line structure. However, deviations from this basic topology must be taken into account – e.g. for temporary connection of diagnostic equipment or for connection of nodes by short unterminated cables. In all these case, signal reflections will occur in the bus due to the existence of unterminated stubs. An example of a CAN bus with unterminated stubs can be seen in Figure 3.

Although the reflected signals will disappear once they arrive at a bus termination, and although the CAN protocol is robust, an upper limit must be set to the allowed unterminated stub length as well as to the cumulative stubs length.

Some rules of thumb can be used:

$$L_{\text{STUB}_{\text{MAX}}} < \frac{T_{\text{PROP}_{\text{SEG}}}}{50 \cdot T_{\text{PROP}(\text{BUS})}}$$

AND

$$L_{\text{STUB}_{\text{TOT}_{\text{MAX}}}} < \frac{I_{\text{PROP}_{\text{SEG}}}}{10 \cdot T_{\text{PROP}(\text{BUS})}}$$

Where:

$L_{STUB\_MAX}$  is the maximum length of one unterminated stub.

$L_{STUB\_TOT\_MAX}$  is the cumulative length of all unterminated stubs in the bus.

T<sub>PROP\_SEG</sub> is the duration of the PROP\_SEG part of the bit time (see the "Definition of CAN Bit Timing" section and Figure 1).

$T_{PROP(BUS)}$  is the propagation delay of the bus line per unit length.

Furthermore, the sum of all stub length must be subtracted from the maximum bus length  $L_{BUS\_MAX\_DEL}$  calculated from the maximum permissible propagation delay (as per the "Definition of CAN Bit Timing" section). In the example depicted in Figure 3, the sum ( $L_{STUB1} + L_{STUB2} + L_{BUS\_LINE}$ ) must be less than  $L_{BUS\_MAX\_DEL}$ .

### Example

#### Given:

AMIS-42665 transceivers will be used with the following relevant parameters (extract from the datasheet):

| Symbol                   | Parameter                    | Conditions | Min | Max | Unit |

|--------------------------|------------------------------|------------|-----|-----|------|

| t <sub>pd(rec-dom)</sub> | Propagation delay TxD to RxD |            | 70  | 230 | ns   |

| t <sub>pd(dom-rec)</sub> | Propagation delay TxD to RxD |            | 100 | 245 | ns   |

The transceiver delay is slightly different for opposite edges (recessive to dominant vs. dominant to recessive). To analyze the worst case, we will take 245 ns.

Other parameters are:

The bus line has a delay of 5 ns per 1 m length

The bit rate of 500 kbps is required, resulting in 1 bit period of 2  $\mu s$

The CAN controller is setup to have PROP\_SEG equal to 1100 ns

Then:

Maximum permissible stub length  $L_{STUB\_MAX}$  is 4.4 m (1100 ns / 5 ns / 50)

If the full total length of stubs is used, the main bus line may be max. 39 m long (61 m - 22 m, see example in the "Maximum Unterminated Stub Length" section for L<sub>BUS TOT MAX</sub> calculation)

# Maximum Bus Line Length in Function of the Required Signal Amplitude

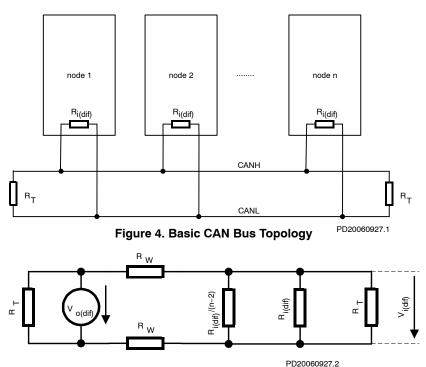

Another limitation on the CAN bus topology is defined by the amplitude of the bus voltage required for correct reception of the bus state. Dominant bit signaled by any single node of the bus must be correctly detected as dominant at all other nodes. The signal amplitude is decreased by voltage drops along the bus line, as the bus is loaded by the bus terminations and the finite input resistances of the nodes. Signal integrity of a recessive state is not influenced by these drops, as it's defined by the termination resistors as typically zero differential voltage.

To analyze the effect of voltage drops, bus topology with n nodes shown in Figure 4 will be considered. A representation of the worst case is shown in Figure 5. The transmitting node, together with its termination resistor  $R_T$ , is placed on one side of the bus, whereas all other nodes and the second termination resistor are situated on the opposite side of the bus line. Each node loads the bus with its differential mode input resistance  $R_{i(diff)}$ , the non-zero resistance of the wires is represented by resistors  $R_W$ . The differential voltage driven by the transmitting node is denoted  $V_{o(diff)}$ , the receiving node can see differential voltage  $V_{i(diff)}$  on its input.

Figure 5. Electric Representation of the CAN bus from Figure 4

For proper detection of the dominant state, a minimum differential voltage Vi(diff)\_MIN\_REQ is required at the input of the receiving node. This minimum is given by the receiver threshold and a user-defined safety margin:

$$V_{i(diff)\_MIN\_REQ} = V_{i(diff)\_TH} + k \cdot \left(V_{o(diff)} - V_{i(diff)\_TH}\right)$$

Where:

$V_{i(diff)\_MIN\_REQ}$  is the minimum required dominant differential voltage at any receiving node

$V_{i(diff)_TH}$  is the receiver threshold level

$V_{o(diff)}$  is the dominant differential voltage driven by the transmitting node

k is an optional "safety margin" coefficient, its value ranging from 0 to 1.

The maximum wire length with respect to the voltage drop can be then found out with the help of Figure 5 and considering following worst-case situation: Minimum differential voltage  $V_{o(diff)\_MIN}$  is driven by the transmitting node.

Maximum receiver threshold V<sub>i(diff) MAX</sub>.

Maximum value of the bus resistance  $R_{W\_MAX}$  is encountered.

Minimum termination resistors  $R_{T\_MIN}$  are placed on the bus. The nodes are loading the bus with their minimum differential input resistance  $R_{i(diff) MIN}$ .

Number of nodes connected to the bus is  $n_{NODES}$ .

Under the above conditions, the differential input voltage will reach its minimum:

$$V_{i(diff)\_MIN} = \frac{V_{o(diff)\_MIN}}{1 + 2.R_{W\_MAX} \cdot \left(\frac{1}{R_{T\_MIN}} + \frac{n_{NODES-1}}{R_{i(diff)\_MIN}}\right)}$$

This worst case differential voltage must be higher than the required minimum  $V_{i(diff)\_MIN\_REQ}$  defined above. Knowing that the cable resistance  $R_W$  is proportional to its length L with ratio  $\rho_W$  representing the specific resistance, both equations can be combined to yield:

$$L_{\text{BUS}\_\text{MAX}\_\text{DROP}} = \frac{1}{2.\rho_{\text{W}\_\text{MAX}}} \times \left( \frac{V_{\text{o}(\text{diff})\_\text{MIN}}}{V_{\text{i}(\text{diff})\_\text{MAX}} + k \cdot \left(V_{\text{o}(\text{diff})\_\text{MIN}} - V_{\text{i}(\text{diff})\_\text{TH}\_\text{MAX}}\right)} - 1 \right) \times \frac{R_{\text{T}\_\text{MIN}} \cdot R_{\text{i}(\text{diff})\_\text{MIN}}}{R_{\text{i}(\text{diff})\_\text{MIN}} + \left(n_{\text{NODES}} - 1\right) \cdot R_{\text{T}\_\text{MIN}}}$$

# Example

Given:

AMIS-42665 transceivers will be used with the following relevant parameters (extract from the datasheet):

| Symbol                        | Parameter                                                                      | Conditions                                                                  | Min  | Тур  | Max  | Unit |

|-------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| V <sub>o(dif)</sub> (bus_dom) | Differential bus output voltage (V <sub>CANH</sub> -<br>V <sub>CANL</sub> )    | $V_{TxD}$ = 0V; dominant;<br>42.5 $\Omega$ < $R_{LT}$ < 60 $\Omega$         | 1.5  | 2.25 | 3.0  | V    |

| Vihcm(dif) (th)               | Differential receiver threshold voltage for<br>high common-mode (see Figure 5) | -35V <v<sub>CANL &lt; +35V;<br/>-35V <v<sub>CANH &lt; +35V;</v<sub></v<sub> | 0.40 | 0.7  | 1.00 | V    |

| R <sub>i(dif)</sub>           | Differential input resistance                                                  |                                                                             | 25   | 50   | 75   | Ω    |

From the above table, the following inputs for the calculations will be extracted:

Minimum differential output voltage Vo(diff) MIN: 1.5 V

Maximum dominant threshold of the receiver  $V_{i(diff)_MAX}$ : 1.00 V

Minimum differential input resistance of a receiver  $R_{i(diff) MIN}$ : 25000  $\Omega$

Remaining inputs for the calculations are:

Maximum specific bus line resistance  $Q_{W\_MAX}{:}~0.0346~\Omega$  / m

Minimum termination resistor value  $R_{T\ MIN}$ : 95  $\Omega$

Number of nodes n<sub>NODES</sub>: 60

Safety margin coefficient k: 0

Then:

Maximum bus line length with respect to the voltage drop is  $L_{BUS\_MAX\_DROP}$ : 560 m.

# Maximum Number of Nodes in Function of the Transmitter Driving Capability

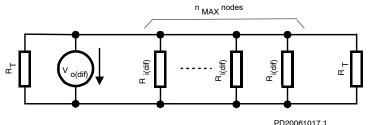

$n_{MAX}$  is the number of nodes connected to the bus.

The resulting resistance  $R_L$  must stay above the specified minimum value  $R_L$  MIN, leading to the following limit for

$n_{MAX} = 1 + R_{i(diff)\_MIN} \times \left(\frac{1}{R_{L}MIN} - \frac{2}{R_{T}MIN}\right)$

The maximum number of nodes is limited by the driving capability of a CAN transmitter. It's usually specified by the minimum allowed load resistance  $R_{L_MIN}$ . The load of a transmitter in the CAN bus is composed of the termination resistors and the parallel combination of differential input resistances of all nodes – see Figure 6.

## Figure 6. Electric Representation of a CAN Bus for Calculation of the Maximum Number of Nodes

one node.

the number of nodes:

The transmitter is then loaded with resistance R<sub>L</sub>, calculated as:

$$\mathbf{R}_{L} = \frac{\mathbf{R}_{T\_MIN} \times \mathbf{R}_{i(diff)\_MIN}}{\left(\mathbf{n}_{MAX} - 1\right) \times \mathbf{R}_{T\_MIN} + 2 \cdot \mathbf{R}_{i(diff)\_MIN}}$$

Where:

$R_{T_{MIN}}$  is the minimum termination resistance.  $R_{i(diff) MIN}$  is the minimum differential input resistance of

## Example

Given:

AMIS42665 transceivers will be used with the following relevant parameters (extract from the datasheet):

| Symbol                        | Parameter                                                                   | Conditions                                                                 | Min | Тур  | Max | Unit |

|-------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|------|-----|------|

| V <sub>o(dif)</sub> (bus_dom) | Differential bus output voltage<br>(V <sub>CANH</sub> – V <sub>CANL</sub> ) | $V_{TxD}$ = 0V; dominant;<br>42.5 $\Omega$ < R <sub>LT</sub> < 60 $\Omega$ | 1.5 | 2.25 | 3.0 | V    |

| R <sub>i(dif)</sub>           | Differential input resistance                                               |                                                                            | 25  | 50   | 75  | Ω    |

From the above table, the following inputs for the calculations will be extracted:

Minimum differential input resistance of a receiver  $R_{i(diff) MIN}$ : 25000  $\Omega$ .

Minimum allowed load to be driven by the transmitter  $R_{L\_MIN}$ : 42.5  $\Omega$  (see the "Conditions" column of the above table).

Remaining input for the calculations is:

Minimum termination resistor  $R_{T MIN:}$  95  $\Omega$

Then:

The maximum allowed number of nodes  $n_{\mbox{MAX}}$  connected to the CAN bus is 62.

#### References

[1] ISO11898/1 – Road vehicles – Controller area network (CAN) – Part 1: Data link layer and physical signaling

ON Semiconductor and IIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative