# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# ECLinPS MAX<sup>™</sup> (SiGe) SPICE Modeling Kit

Prepared by: Casey Stys and Paul Shockman

http://onsemi.com

### APPLICATION NOTE

### **Objective**

The objective of this kit is to provide sufficient circuit schematic and SPICE parameter information to perform system level interconnect modeling for devices in ON Semiconductor's high performance ECLinPS MAX (SiGe) logic family. The family has output edge rates as low as 50 ps and power supply levels of as low as 2.5 V.

The kit is not intended to provide information necessary to perform circuit level or device behavioral LOGIC modeling on the ECLinPS MAX devices.

### **Schematic Information**

The kit contains representative input and output schematics, netlists and waveforms for SPICE modeling and simulating the ECLinPS MAX family devices INPUT and OUTPUT structures. This application note will be modified as new devices are added. Table 1 describes the nomenclature used for modeling the schematic and netlist for ECLinPS MAX devices.

**Table 1. Schematics and Netlist Nomenclature**

| Parameter       | Function Description                                             |

|-----------------|------------------------------------------------------------------|

| V <sub>CC</sub> | 2.5 / 3.3 V for LVPECL and 0 V for LVNECL                        |

| V <sub>EE</sub> | -2.5 / -3.3 V for LVNECL and 0 V for LVPECL                      |

| V <sub>CS</sub> | Internally Generated Voltage (V <sub>EE</sub> + 0.915 V ± 50 mV) |

| IN              | True (+) Input to BUFFER                                         |

| ĪN              | Inverted (-) Input to BUFFER                                     |

| Q               | True (+) Output of BUFFER                                        |

| Q               | Inverted (-) Output of BUFFER                                    |

| INT             | Internal True (+) Input to Output Buffer                         |

| INT             | Internal Invert (-) Input to Output Buffer                       |

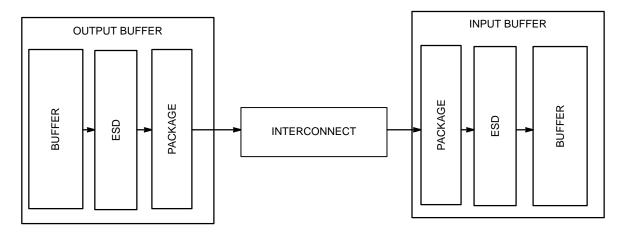

The subcircuit models, such as input or output buffers, ESD and package simulate only device input or output paths. When used with interconnect models, a complete signal path may be modeled as shown in Figure 1.

**Figure 1. Interconnect Model Template**

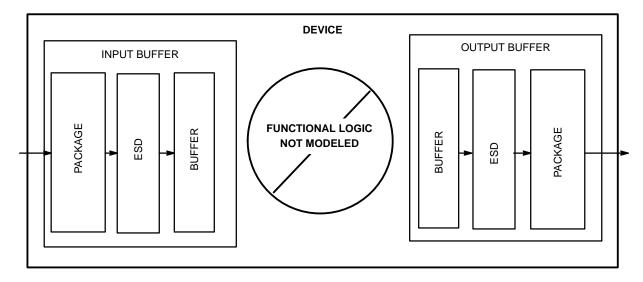

For device modeling, the behavioral LOGIC or gate functionality is not modeled (see Figure 2. DEVICE Model Template)

Figure 2. DEVICE Model Template

# **Package**

Models for various package types have been included to improve the accuracy of the system interconnect model (Table 2).

Table 2. Available Package Models

| Package | Model                              |

|---------|------------------------------------|

| SOIC-8  | Appendix B (Figure 11 and Table 4) |

| TSSOP-8 | Appendix B (Figure 12 and Table 5) |

| QFN-16  | Figure 9                           |

The package model represents the parasitics as they are measured at a significant distance from an AC ground pin. The package models should be placed on all external inputs of an input model, all external outputs of an output model and the  $V_{CC}$  line. Since the current in the  $V_{EE}$  pin is a constant, a package model for  $V_{EE}$  pin is not necessary. Note an internal  $V_{CS}$  voltage does not require a package model. To speed up the simulation process, simplified package models have been used.

### **Input Buffer**

The input buffer schematics and netlists present the various input structures for ECLinPS MAX family devices. The schematics and netlists include ESD and package model parasitics for accuracy.

### **Output Buffer**

Output buffer schematics and netlists models are provided. The package model parasitics has been added for accuracy. The output buffer models typically show internal differential inputs driven by INT and  $\overline{\text{INT}}$ . Outputs should always be simulated with both output lines properly terminated, even when only one line or single ended use is intended. This will balance the output buffer's load.

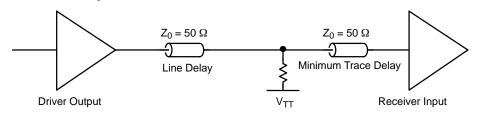

For correlation, a typical output waveform seen at the input of the receiver, is shown in Figure 10.

### **SPICE Netlist**

The netlists are organized as a subcircuit. In each subcircuit model netlist, the model name should be followed by a list of external node interconnects. When copying a "SUBCKT" netlist files to your text editor, use Adobe® Acrobat® Reader 4.0 or higher to ensure proper character conversion.

#### **SPICE Parameter Information**

In addition to the schematics and netlists there is a listing of the SPICE parameters for the transistors and diodes referenced in the schematics and netlists found provided in APPENDIX A. These parameters represent a typical case device of the transistor or diode. Varying the typical parameters will affect the DC and AC performance of the structures and is not recommended. Modeling of device actual delay time is not the intention of this document.

The performance levels may be varied by methods and discussed in the next section. The resistors referenced in the schematics are polysilicon and have negligible parasitic capacitance in the real circuit. The schematics display only devices needed in the SPICE netlists.

### **Modeling Information**

The bias drivers for the devices are not included as they are unnecessary for interconnect simulations and their use results in a large increase in model complexity and simulation time. The internal reference voltages ( $V_{BB}$ ,  $V_{CS}$ , etc.) should be modeled with ideal constant voltage sources. Output and input levels of ECLinPS MAX devices generally vary in a one to one ratio with the power supply; and remain relatively constant over temperature. Note the  $V_{CS}$  supply is always relative to  $V_{EE}$ , the most negative supply. The output schematics and SPICE parameters include a typical waveform, for simulation correlation. Inclusion of ESD and package models typically will add about 5.0 ps - 7.0 ps to the output waveform rise and fall time. Simple adjustments made to the models may permit

output characteristics to emulate conditions at or near the performance corners of the data sheet specifications. Consistent, repeatable cross–point voltages of 50% should be maintained.

## To Adjust Rise and Fall Times, tr and tf

Produce the desired variant rise and fall times output slew rates by adjusting collector load resistors. This  $V_{CS}$  voltage determines the tail current in the output differential affecting the  $t_{\rm r}$  and  $t_{\rm f}$  of the output.

### To Adjust the VOH

Adjust the  $V_{OH}$  and  $V_{OL}$  level together by varying  $V_{CC}$ . The output levels will follow changes in  $V_{CC}$  at a 1:1 ratio.

# To Adjust the VoL

Adjust the  $V_{OL}$  level independently of the  $V_{OH}$  level by adjusting increasing the collector load resistance. Note the  $V_{OH}$  level will also by affected due to an  $I_{BASE}$  \* R drop across the collector load resistor. The  $V_{OL}$  can be changed by varying the  $V_{CS}$  supply which will also affect gate current through the current source resistor.

### **Device Specifics**

### 6L239

An exception to the general rule of "levels are relative to  $V_{CC}$ " is found in the internal input node of  $\overline{EN}$ , SELx, and

$\overline{\text{MR}}$  INPUT BUFFERS at the voltage divider BIAS feeding one side of the differential. This remains at  $V_{CC}/2$  forcing the detect threshold to ratiometrically change with  $V_{CC}$ .

When left floating open, the  $\overline{EN}$  and SELx inputs will be forced to a default state of LOW by the internal 75 k $\Omega$  pulldown resistor to  $V_{EE}$ , relative to the  $V_{CC}/2$  BIAS voltage on the other side of the differential. The  $\overline{MR}$  input, when left floating open, will be forced to a default state of HIGH by the internal 75 k $\Omega$  pullup resistor to  $V_{CC}$ .

#### 6L11 and 6L16

Inputs, when left floating open, will not be forced to a determined default state. Precautionary considerations may be needed to prevent spontaneous self oscillation of the device.

### **Summary**

The information included in this kit provides adequate information to run a SPICE level system interconnect simulation. The block diagram in Figure 2 illustrates a typical situation, which can be modeled using the information in this kit.

Figure 3. Typical Application for I/O SPICE Modeling Kit

Device input or output models are presented in Table 3.

Table 3. ECLinPS MAX Input/Output Buffer Selector Guide

| Device   | Function                                                                         | Pin           | Description         | Model    |

|----------|----------------------------------------------------------------------------------|---------------|---------------------|----------|

|          | 2.5 V / 3.3 V Multilevel Input to Differential                                   | 6, 7          | INPUT               | INBUF_01 |

|          | LVNECL/LVPECL 1:2 Clock or Data Fan-<br>out Buffer/Translator                    |               | OUTPUT              | OBUF_01  |

| NB6L16   | 36L16 2.5 V / 3.3 V Multilevel Input to Differential LVNECL/LVPECL Clock or Data |               | INPUT               | INBUF_01 |

|          | Receiver/Buffer/Translator                                                       | 6, 7          | OUTPUT              | OBUF_01  |

| NB6L239  |                                                                                  |               | EN and SELx INPUT   | EN_SEL   |

|          | Differential LVPECL OUT DIV by 1/2/4/8/16 Clock Divider                          | 16            | MR INPUT            | MR       |

|          |                                                                                  | 1, 2, 3       | CLKs and VDT INPUT  | CLK_IN   |

|          |                                                                                  | 9, 10, 11, 12 | OUTPUT              | OBUF_01  |

| NB6N239S |                                                                                  |               | Single Ended Inputs | INBUF_01 |

|          | to LVDS OUT DIV by 1/2/4/8, DIV by 2/4/8/16 Clock Divider                        | 16            | MR INPUT            | MR       |

|          |                                                                                  | 2, 3          | CLKs and VDT INPUT  | INBUF_01 |

|          |                                                                                  | 9, 10, 11, 12 | LVDS OUTPUT         | OBUF_02  |

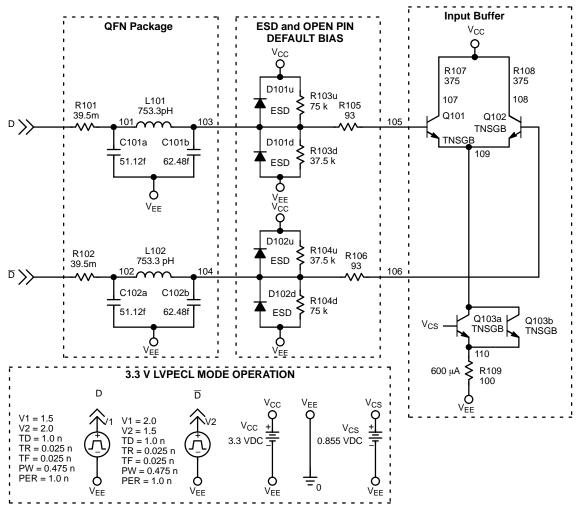

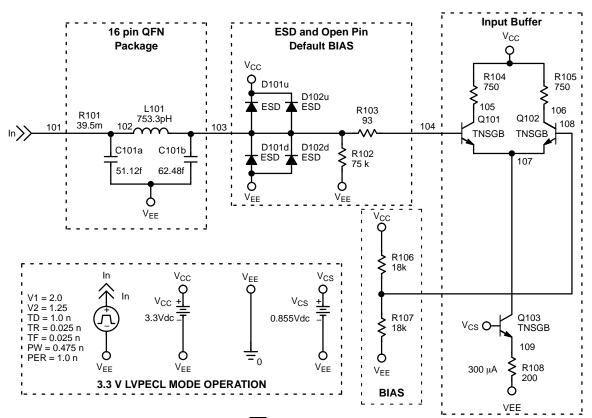

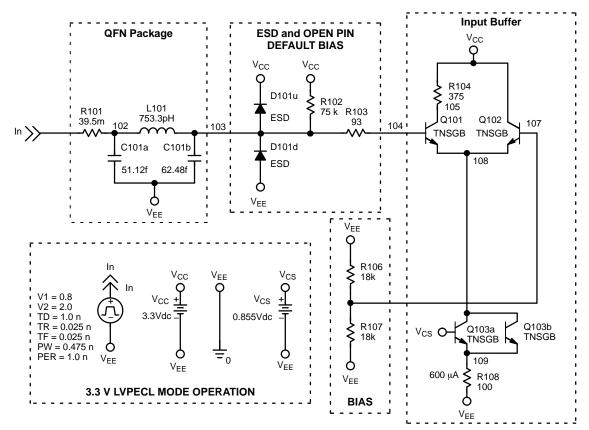

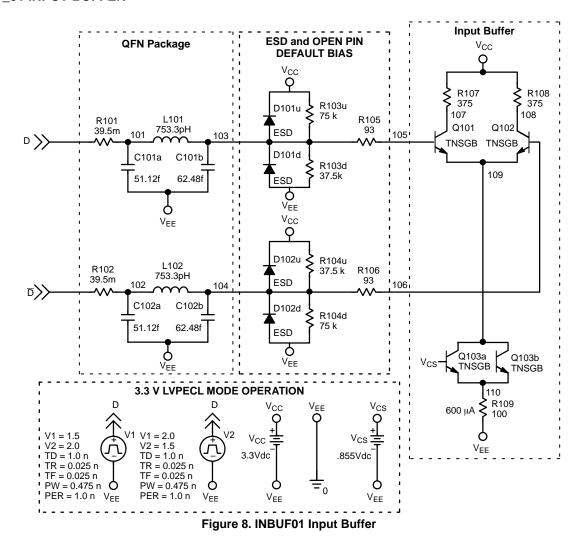

### **INBUF 01 INPUT BUFFER**

Figure 4. INBUF\_01 Input Buffer

```

V_V1

D 0

V_V2

DB 0

V_VCC

VCC 0 3.3Vdc

VCS 0 .855Vdc

+PULSE 1.5 2.0 1n 0.025n 0.025n 0.475n 1n

+PULSE 2.0 1.5 1n 0.025n 0.025n 0.475n 1n

.SUBCKT INBUF_01

0 101 51.12f

C_C101a

0 103 62.48f

C_C101b

0 102 51.12f

C_C102a

C_C102b

0 104 62.48f

D_D101d

0 103 ESD

D_D101u

103 VCC ESD

D_D102d

0 104 ESD

D_D102u

104 VCC ESD

L_L101

101 103 753.3pH

L_L102

102 104 753.3pH

107 105 109 TNSGB

Q_Q101

Q_Q102

108 106 109 TNSGB

Q_Q103a

109 VCS 110 TNSGB

Q_Q103b

109 VCS 110 TNSGB

R_R101

101 D 39.5m

R_R102

102 DB 39.5m

```

| R_R103d     | 103 0 37.5K   |

|-------------|---------------|

| R_R103u     | VCC 103 75K   |

| R_R104d     | 104 0 75K     |

| R_R104u     | VCC 104 37.5K |

| R_R105      | 103 105 93    |

| R_R106      | 104 106 93    |

| R_R107      | 107 VCC 375   |

| R_R108      | 108 VCC 375   |

| R_R109      | 0 110 100     |

| .END INBUF_ | 01            |

# **EN AND SELX INPUT BUFFER**

Figure 5. EN and SELx Input Buffer

```

IN 0

V_In

V_VCC

VCC 0 3.3Vdc

V_VCS

VCS 0 0.855Vdc

+PULSE 2.0 1.25 1n 0.025n 0.025n 0.475n 1n

.SUBCKT ENb_SEL

0 102 51.12f

C_C101a

C_C101b

0 103 62.48f

D_D101d

0 103 ESD

D_D101u

103 VCC ESD

D_D102d

0 103 ESD

D_D102u

103 VCC ESD

102 103 753.3pH

L_L101

105 104 107 TNSGB

Q_Q101

106 108 107 TNSGB

Q_Q102

107 VCS 109 TNSGB

Q_Q103

102 IN 39.5m

R_R101

R_R102

103 0 75K

R_R103

103 104 93

R_R104

105 VCC 750

R_R105

106 VCC 750

R_R106

VCC 108 18K

108 0 18K

R_R107

0 108 200

R_R108

.END ENb_SEL

```

### **MR** INPUT BUFFER

Figure 6. MR Input Buffer

```

+PULSE 0.8 2.0 1n 0.025n 0.025n 0.475n 1n

V_V1

IN 0

V_VCC

VCC 0 3.3Vdc

V_VCS

VCS 0 .855Vdc

.SUBCKT MRb

0 102 51.12f

C_C101a

0 103 62.48f

C_C101b

D_D101d

0 103 ESD

D_D101u

103 VCC ESD

L_L101

102 103 753.3pH

Q_Q101

105 104 108 TNSGB

VCC 107 108 TNSGB

Q_Q102

108 VCS 109 TNSGB

Q_Q103a

108 VCS 109 TNSGB

Q_Q103b

102 IN 39.5m

R_R101

VCC 103 75K

R_R102

R_R103

103 104 93

R_R104

105 VCC 375

R_R106

VCC 107 18K

R_R107

107 0 18K

R_R108

0 109 100

.END .MRb

```

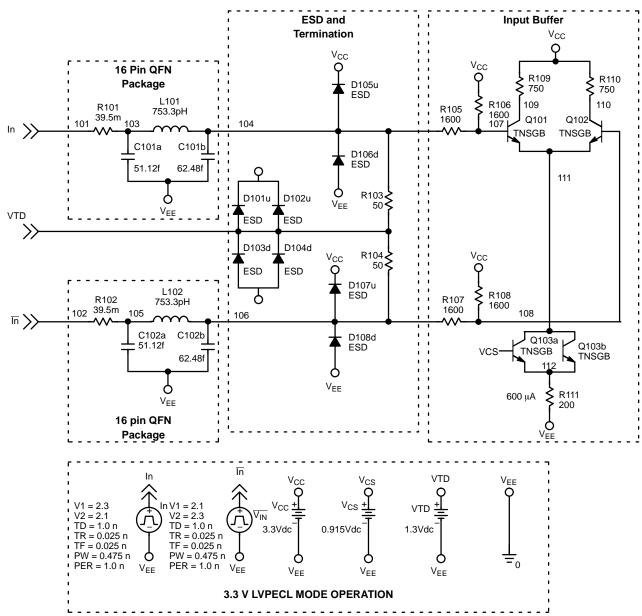

### **CLKS AND VTD INPUT BUFFER**

Figure 7. CLKs and VTD Input Buffer

```

+PULSE 2.1 2.3 1n 0.025n 0.025n 0.475n 1n

+PULSE 2.3 2.1 1n 0.025n 0.025n 0.475n 1n

V_TD

TD 0 1.3Vdc

V_VCC

VCC 0 3.3Vdc

V_VCS

VCS 0 0.915Vdc

V_VIN

IN 0

INB 0

V_VINb

.SUBCKT CLK_IN

C_C101a

0 103 51.12f

C_C101b

0 104 62.48f

C_C102a

0 105 51.12f

C C102b

0 106 62.48f

TD VCC ESD

D_D101u

TD VCC ESD

D_D102u

D_D103d

0 TD ESD

```

| D_D104d    | 0 TD ESD          |

|------------|-------------------|

| D_D105u    | 104 VCC ESD       |

| D_D106d    | 0 104 ESD         |

| D_D107u    | 106 VCC ESD       |

| D_D108d    | 0 106 ESD         |

| L_L101     | 103 104 753.3рН   |

| L_L102     | 105 106 753.3pH   |

|            | 109 107 111 TNSGB |

| Q_Q102     | 110 108 111 TNSGB |

| Q_Q103a    | 111 VCS 112 TNSGB |

| Q_Q103b    | 111 VCS 112 TNSGB |

| R_R101     | 103 IN 39.5m      |

| R_R102     | 105 INB 39.5m     |

| R_R103     |                   |

| R_R104     |                   |

| R_R105     | 104 107 1600      |

| R_R106     | VCC 107 1600      |

| R_R107     | 106 108 1600      |

| R_R108     | VCC 108 1600      |

| R_R109     | 109 VCC 750       |

| R_R110     | 110 VCC 750       |

| R_R111     | 0 112 200         |

| .END CLK_I | Ŋ                 |

### **INBUF 01 INPUT BUFFER**

V\_V1 D 0

V\_V2 DB 0 V\_VCC VCC 0 3.3Vdc V\_VCS VCS 0 .855Vdc

+PULSE 1.5 2.0 1n 0.025n 0.025n 0.475n 1n +PULSE 2.0 1.5 1n 0.025n 0.025n 0.475n 1n

.SUBCKT INBUF\_01

C\_C101a 0 101 51.12f C\_C101b 0 103 62.48f C\_C102a 0 102 51.12f C\_C102b 0 104 62.48f 0 103 ESD D\_D101d 103 VCC ESD D\_D101u D\_D102d 0 104 ESD D\_D102u 104 VCC ESD L\_L101 101 103 753.3рН 102 104 753.3pH L\_L102 Q\_Q101 107 105 109 TNSGB 108 106 109 TNSGB Q\_Q102 109 VCS 110 TNSGB Q\_Q103a Q\_Q103b 109 VCS 110 TNSGB 101 D 39.5m R\_R101 R\_R102 102 DB 39.5m

| R_R103d     | 103 0 37.5K   |

|-------------|---------------|

| R_R103u     | VCC 103 75K   |

| R_R104d     | 104 0 75K     |

| R_R104u     | VCC 104 37.5K |

| R_R105      | 103 105 93    |

| R_R106      | 104 106 93    |

| R_R107      | 107 VCC 375   |

| R_R108      | 108 VCC 375   |

| R_R109      | 0 110 100     |

| .END INBUF_ | _01           |

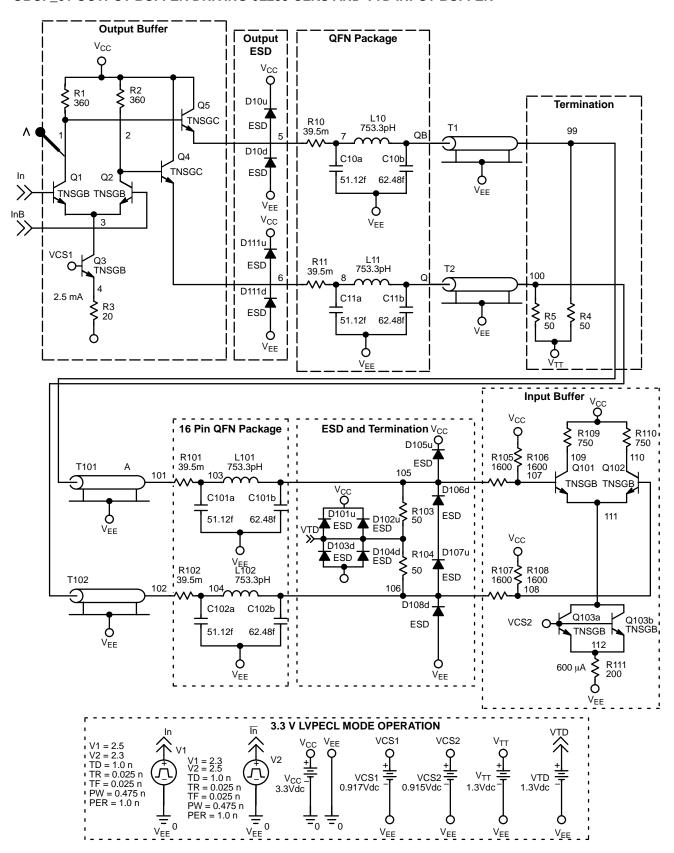

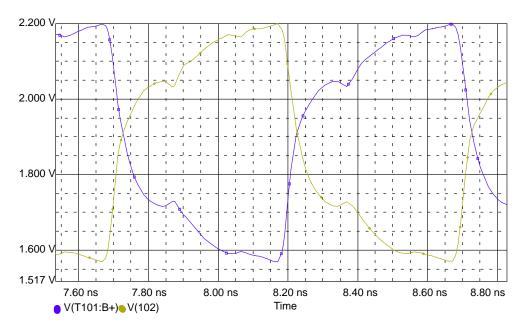

### **OBUF 01 OUTPUT BUFFER DRIVING 6L239 CLKS AND VTD INPUT BUFFER**

Figure 9. OBUF\_01 Output Buffer driving 6L239 CLKs and VTD Input Buffer

```

V_V1

IN 0

V_V2

INB 0

VCC 0 3.3Vdc

V VCC

VCS1 0 0.917Vdc

V_VCS1

V_VCS2

VCS2 0 0.915Vdc

V_{VTD}

VTD 0 1.3Vdc

V_VTT

VTT 0 1.3Vdc

+PULSE 2.3 2.5 1n 0.025n 0.025n 0.475n 1n

+PULSE 2.5 2.3 1n 0.025n 0.025n 0.475n 1n

.SUBCKT OBUF_01

0 7 51.12f

C_C10a

C_C10b

0 QB 62.48f

0 8 51.12f

C_C11a

C_C11b

0 Q 62.48f

D_D10d

0 5 ESD

D_D10u

5 VCC ESD

L_L10

7 QB 753.3pH

L_L11

8 Q 753.3pH

1 IN 3 TNSGB

Q_Q1

Q_Q2 2 INB 3 TNSGB

Q_Q3

3 VCS1 4 TNSGB

VCC 2 6 TNSGC

Q_Q4

VCC 1 5 TNSGC

Q_Q5

R_R1

1 VCC 360

5 7 39.5m

R_R10

R_R11

6 8 39.5m

2 VCC 360

R_R2

R_R3

0 4 20

99 VTT 50

R_R4

100 VTT 50

R_R5

T_T1

QB 0 99 0 Z0=50 TD=80ps

T_T2

Q 0 100 0 Z0=50 TD=80ps

.END OBUF_01

.SUBCKT CLK_INBUF

C_C101a 0 103 51.12f

0 105 62.48f

C_C101b

C_C102a 0 104 51.12f

C_C102b

0 106 62.48f

VTD VCC ESD

D_D101u

D_D102u

VTD VCC ESD

D_D103d

0 VTD ESD

D D104d

0 VTD ESD

D_D105u

105 VCC ESD

D_D106d

0 105 ESD

106 VCC ESD

D_D107u

0 106 ESD

D_D108d

D_D111d

0 6 ESD

D_D111u

6 VCC ESD

103 105 753.3рН

L_L101

104 106 753.3pH

L_L102

109 107 111 TNSGB

Q_Q101

110 108 111 TNSGB

Q_Q102

Q_Q103a 111 VCS2 112 TNSGB

111 VCS2 112 TNSGB

Q_Q103b

R_R101

103 101 39.5m

R_R102

104 102 39.5m

105 VTD 50

R R103

R_R104

VTD 106 50

105 107 1600

R_R105

VCC 107 1600

R_R106

106 108 1600

R_R107

```

Figure 10. Typical OBUF\_01 OUTPUT Waveform driving 6L239 CLK/CLK INPUT BUFFER

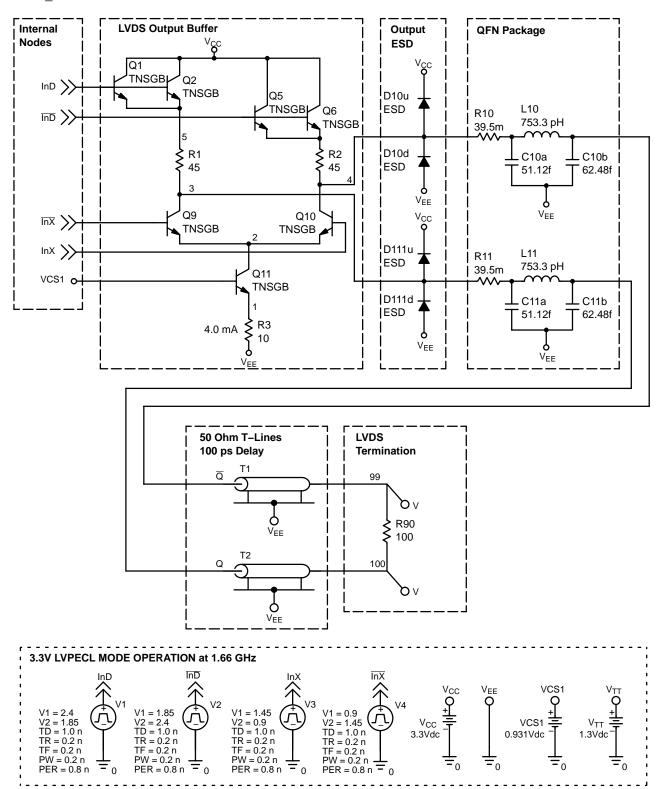

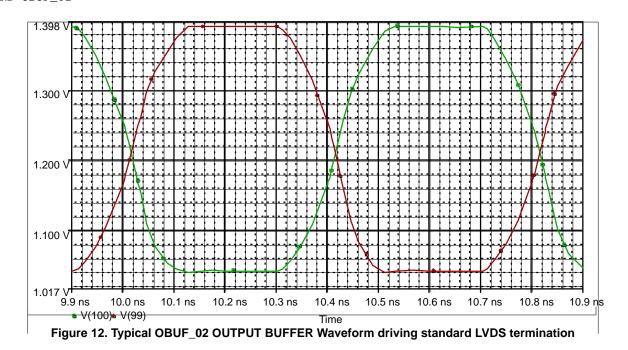

### **OBUF 02 OUTPUT BUFFER DRIVING STANDARD LVDS TERMINATION**

Figure 11. OBUF\_02 Output Buffer driving standard LVDS termination

```

V_V1

IND 0

V_V2

INDB 0

V_V3

INX 0

INXB 0

V_V4

V_VCC

VCC 0 3.3Vdc

V_VCS1

VCS1 0 .931Vdc

V_VTT

VTT 0 1.3Vdc

+PULSE 0.9 1.45 1n 0.2n 0.2n 0.2n .8n

+PULSE 1.45 0.9 1n 0.2n 0.2n 0.2n .8n

+PULSE 1.85 2.4 1n 0.2n 0.2n 0.2n .8n

+PULSE 2.4 1.85 1n 0.2n 0.2n 0.2n .8n

.SUBCKT OBUF_02

C_C10a

0 N66098 51.12f

C_C10b

0 QB 62.48f

C_C11a

0 N09146 51.12f

C_C11b

0 Q 62.48f

D_D10d

0 4 ESD

D_D10u

4 VCC ESD

0 3 ESD

D_D111d

D_D111u

3 VCC ESD

N66098 QB 753.3pH

L_L10

N09146 Q 753.3pH

L_L11

VCC IND 5 TNSGB

Q_Q1

Q_Q10

4 INX 2 TNSGB

Q_Q11

2 VCS1 1 TNSGB

Q_Q2

VCC IND 5 TNSGB

Q_Q5

VCC INDB N293875 TNSGB

VCC INDB N293875 TNSGB

Q_Q6

3 INXB 2 TNSGB

Q_Q9

3 5 45

R_R1

4 N66098 39.5m

R_R10

R_R11

3 N09146 39.5m

R_R2

4 N293875 45

0 1 10

R R3

R_R90

100 99 100

T_T1

QB 0 99 0 Z0=50 TD=100ps

T_T2

Q 0 100 0 Z0=50 TD=100ps

.END OBUF_02

```

#### **APPENDIX A**

\*\*\*\*\*\* Transistor and Diode Models for ECLinPS MAX \*\*\*\*\*\*\*\*\*

.MODEL TNSGB NPN (IS=2.18e-17 BF=179 NF=1 VAF=96.5 IKF=2.42e-02

- + ISE=3.83e-16 NE=2.5 BR=20.4 VAR=2.76 IKR=1.98e-03 ISC=2.91e-17

- + NC=1.426 RB=55 IRB=1.12e-04 RBM=48 RE=6 RC=11 CJE=7.98e-15

- + VJE=.8867 MJE=.2868 TF=2.00e-12 ITF=0.4e-02 XTF=0.7 VTF=0.6 PTF=20 TR=0.5e-9

- + CJC=4.55e-15 VJC=0.632 MJC=0.301 XCJC=0.3 CJS=4.71e-15 VJS=.4193 MJS=0.256

- + EG=1.119 XTI=3.999 XTB=0.8826 FC=0.9)

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

.MODEL TNSGC NPN (IS=1.47e-16 BF=180 NF=1 VAF=96.3 IKF=1.62e-01

- + ISE=2.96e-15 NE=2.5 BR=20.2 VAR=2.76 IKR=1.34e-02 ISC=2.14e-16

- + NC=1.426 RB=25 IRB=1.50e-03 RBM=4 RE=1 RC=7 CJE=6.34e-14

- + VJE=.8867 MJE=.2868 TF=2.00e-12 ITF=0.25e-01 XTF=0.7 VTF=0.35 PTF=20 TR=0.5e-9

- + CJC=4.08e-14 VJC=0.632 MJC=0.301 XCJC=.3 CJS=11.12e-15 VJS=.4193 MJS=0.256

- + EG=1.119 XTI=3.999 XTB=0.8826 FC=0.9)

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

### **APPENDIX B**

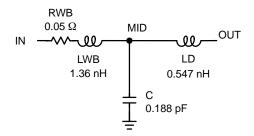

Figure 13. Schematic Model of 8 ld SOIC Packge

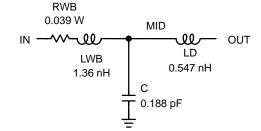

Figure 14. Schematic Model of 8 ld TSSOP Packge

Table 4.

| Package: 8-Lead SOIC (D) |          |

|--------------------------|----------|

| Component                | Value    |

| RWB                      | 0.05 Ω   |

| LWB                      | 1.36 nH  |

| LD                       | .547 nH  |

| С                        | 0.188 pF |

Table 5.

| Package: 8-Lead TSSOP (DT) |         |  |

|----------------------------|---------|--|

| Component                  | Value   |  |

| RWB                        | .039 Ω  |  |

| LWB                        | 1.36 nH |  |

| LD                         | .547 nH |  |

| С                          | .188 pF |  |

ECLinPS MAX is a trademark of Semiconductor Components Industries, LLC (SCILLC). Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free LISA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.