## **ON Semiconductor**

## Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

## Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# **AN-9746**

## Assembly Guidelines for MicroFET 1.6x1.6mm Packaging

## **Summary**

The Fairchild MicroFET 1.6x1.6mm is a package based on Molded Leadless Packaging (MLP) technology. This technology is often used for power-related products due to its low package height and excellent thermal performance. Large thermal pads in the center of the package solder directly to the Printed Wiring Board (PWB). Modularity in package design, single- and multi-die packages, is within MLP capability.

The MicroFET 1.6x1.6 has two large die-attach pads, allowing direct soldering to the PWB for best thermal and electrical performance. The MicroFET 1.6x1.6 is designed to be used with Fairchild discrete MOSFET products. This application note focuses on the soldering and back-end processing of the MicroFET 1.6x1.6.

## **Board Mounting**

The solder joint and pad design are the most important factors in creating a reliable assembly. The pad dimensions must allow for tolerances in PWB fabrication and pick and place, which are necessary for proper solder fillet formation. MLP packages, when the pre-plated lead-frame is sawn, show bare copper on the end of the exposed edge leads. This is normal and is addressed by IPC JEDEC J-STD-001C "Bottom Only Termination" standard. In practice, optimized PWB pad design and a robust solder process often creates solder fillets to the ends of the lead due to the cleaning action of the flux in the solder paste.

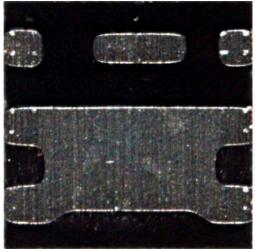

Figure 1. MicroFET 1.6x1.6 (Bottom)

## **PWB Design Considerations**

Any land pad pattern must take into account the various PWB and board assembly tolerances for successful soldering of the MLP to the PWB. These factors are considered for the recommended footprint in the datasheet; follow this footprint to assure best assembly yield, thermal performance, and overall system performance.

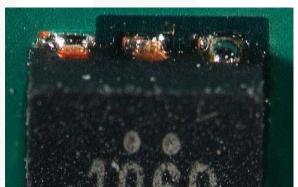

Figure 2. Exposed Copper on Package Edge, Solder Wetting after Reflow, from Singulation Process

### Pad Finish

The MicroFET 1.6x1.6 is sold with a lead-free lead finish. Immersion silver, immersion nickel gold, and Organic Surface Protectant (OSP), are the pad finishes of choice for lead-free processing. Hot-air solder-level pad finish does not have chemistry compatibility issues, but is not recommended due to inconsistency in the thickness of the finish. Each finish has useful properties and each has challenges. It is beyond the scope of this paper to debate each system's merits. No one finish is right for all applications, but the most common in large-scale consumer electronics, largely due to cost, is OSP. A high-quality OSP, formulated for the rigors of lead-free reflow, like Enthone® Entek® Plus HT, is recommended.

#### **PWB Material**

It is recommended that lead-free FR-4 is used in PWB construction. Lower-quality FR-4 can cause numerous problems with the reflow temperatures seen when using lead-free solder. IPC-4101B "Specification for Base Materials for Rigid and Multilayer Printed Boards" contains further information on choosing the correct PWB material for the intended application.

## Using Vias with MicroFET 1.6x1.6

Designers often wish to place vias inside the thermal pads. While this is understandable, the vias often create voiding and appropriately sized vias for the small pads can be quite costly in production. Previous studies have shown the vias can be placed just outside the pad and excellent performance still achieved.

## **Stencil Design**

It is estimated that 60% of all assembly errors are due to paste printing. For a controlled, high-yielding manufacturing process; it is, therefore, the most critical phase of assembly. Due to the importance of the stencil design, many stencil types have been characterized to determine the optimal stencil design for the datasheet recommended footprint pad on a typical application board with OSP surface finish on FR-4. The paste was printed from a laser-cut 4-mils thick stainless steel stencil. Two stencil recommendations are given in the appendix. The best performance was found with the split solder print on the drain tab. However, both solder apertures were proven to work well. The paste was printed on the outer pins with a slightly reduced ratio to the PWB pad. IPC-7525 "Stencil Design Guidelines" gives a formula for calculating the area ratio for paste release prediction:

$$Area\ Ratio = \frac{Area\ of\ Pad}{Area\ of\ Aperture\ Walls} = \frac{L*W}{2*(L*W)*T} \tag{1}$$

where L is the length, W the width, and T the thickness of the stencil. When using this equation, an area ratio >0.66 should yield acceptable paste release.

For MicroFET 1.6x1.6, it is recommended that the solder screen be opened to cover 60% of the outer pads, and 35% of the drain tab when using a 4-mils (0.10mm) thick stencil. A drawing is in the appendix, and can be used as a starting point for the solder process optimization.

#### **Solder Paste**

The MicroFET 1.6x1.6 is a RoHS-compliant and lead-free package. The lead finish is NiPdAu. Any standard lead-free no clean solder paste commonly used in the industry should work with this package. The IPC Solder Products Value Council has stated that the lead-free alloy, 96.5Sn/3.0Au/0.5Cu, commonly known as SAC 305, is "...the lead-free solder paste alloy of choice for the electronics industry." Type-3 no-clean paste, SAC 305 alloy, was used for the construction of the boards studied to optimize the process.

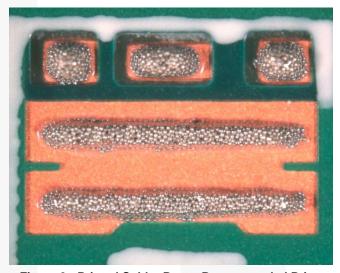

Figure 3. Printed Solder Paste, Recommended Print

#### **Reflow Profile**

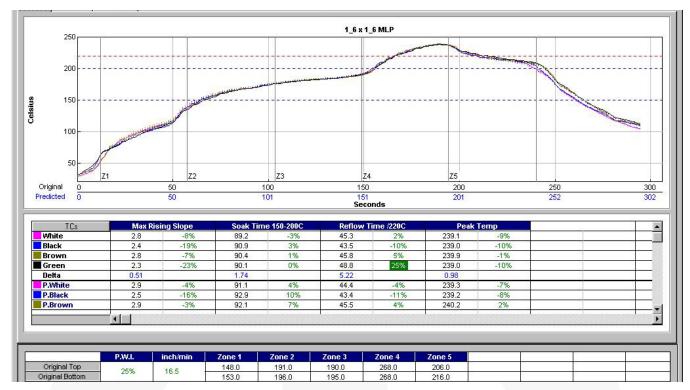

The optimum reflow profile used for every product and oven is different. Even the same brand and model oven in a different facility may require a different profile. The proper ramp and soak rates are determined by the solder paste vendor for their specific products.

Obtaining this information from the paste vendor is highly recommended. If using a KIC® profiler, download the latest paste library from KIC yield ramp rate and soak times at temperatures for most commonly used solder pastes. Using this data, the software optimizes the zone set-points and conveyor speed. The Fairchild MicroFET 1.6x1.6 is rated for 260°C peak temperature reflow. The appendix contains a sample reflow profile used for building demonstration boards. This profile is provided for reference only; different PWBs, ovens, and pastes changes this profile, perhaps dramatically.

## Voiding

Voiding is a very controversial topic in the industry. The move to lead-free solders has driven the need for intense study in the area of solders, solder joints, and reliability effects. There are varying viewpoints on the effect of vias and allowable quantity. There are several types of voids; for simplicity this applications note classifies them into two categories, macro voids and micro voids.

Macro voids could also be called process voids. Macro voids are the large-sized voids commonly seen on x-ray during inspection. These voids are due to process design, process control issues, or PWB design issues. All of the parameters discussed in this application note effect macro-voiding. Most standards that currently exist, such as IPC-610D, specifically address void criteria for BGA and limit it to 25%. This standard is for macro voiding.

There is currently no industry standard for macro voiding in MLP solder joints. Fairchild has completed several reliability studies, characterizing voiding in various types of components with large thermal pads and the effect on reliability. It was found that components with ≤25% voiding exhibit acceptable reliability performance in package qualification temperature cycling. Fairchild suggests the 25% as maximum voiding for MLP type packages.

There are also several forms of micro-voiding, planar micro voids and Kirkendall voids. The mechanism of void creation is different for each and both are practically undetectable by x-ray inspection. Both types are also currently the subject of several in-depth studies; however, none have confirmed theories of creation.

Planar micro voids, or "champagne voids," occur at the PWB land-to-solder-joint interface. There are several theories on the mechanism that creates planar micro voids, but there is no industry consensus on the causal mechanism. Planar micro voids are a risk for reliability failures.

Kirkendall voids are created at the interface of two dissimilar metals at higher temperatures; in the case of solder attachments, at the pad to joint intermetallic layer. They are not due to the reflow process; Kirkendall voids are created by electromigration in assemblies that spend large amounts of time above 100°C. There is conflicting evidence on whether or not Kirkendall voids are a reliability risk.

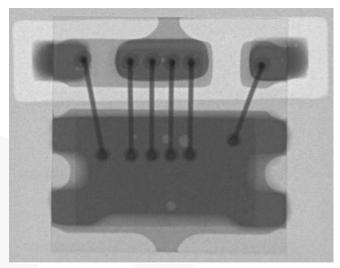

Figure 4. X-Ray Image Showing Voiding Caused by Normal Process Variation during Reflow

#### Rework

Due to the high temperatures associated with lead-free reflow, it is recommended that this component not be reused if rework becomes necessary. The MicroFET 1.6x1.6 should be removed from the PWB with hot air. After removal, the MicroFET 1.6x1.6 should be discarded. The solder remnants should be removed from the pad with a solder vacuum or solder wick, the pads cleaned, and new paste printed with a mini stencil. Localized hot air can be applied to reflow the solder and make the joint. Due to the thermal performance of this component and the high performance PWB it is mounted on, quite a bit of heat energy is necessary. Heating of the PWB may be helpful for the rework process.

### **Board-Level Reliability**

Per JDC-STD-001D, a solder fillet is not required on the side of the lead for this package; but it has been found through modeling and temperature cycling that a solder fillet on the lead end can improve reliability. An improvement of 20% can be expected with this fillet. It has also been found that the 20% reliability enhancement is attained even when the fillet only wets halfway up the side of the lead. Expect to create reliability enhancing solder fillets through proper process design and control.

As part of the standard reliability testing, this package was temperature cycled from -40°C to 125°C. There should be no failures in the sample set at 1000 cycles to pass the test.

APPLICATION NOTE

# **Appendix**

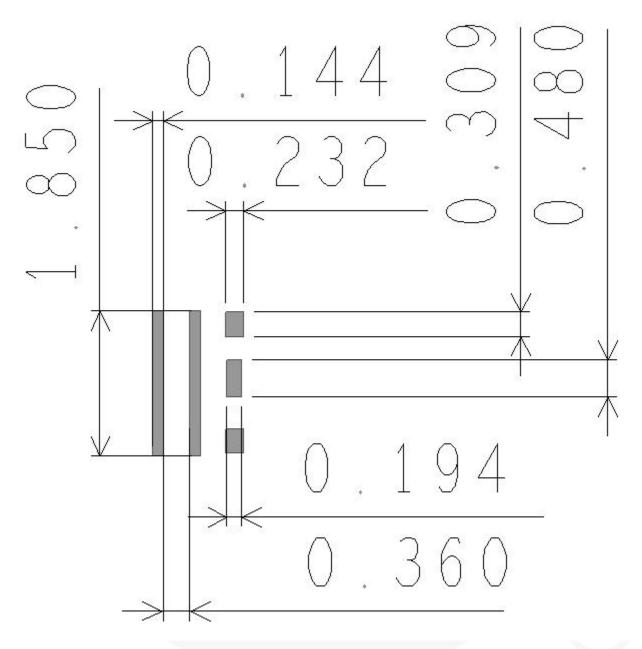

Figure 5. Solder Stencil Opening Recommendations (mm)

Figure 6. Reflow Profile used for Building Demonstration Boards

## References

- [1] Aspandiar, Raiyo, "Voids in Solder Joints," SMTA Northwest Chapter Meeting, September 21, 2005, Intel® Corporation.

- [2] Bryant, Keith, "Investigating Voids," Circuits Assembly, June 2004.

- [3] Comley, David, et al, "The QFN: Smaller, Faster and Less Expensive," Chip ScaleReview.com, August/September 2002.

- [4] Englemaier, Werner, "Voids in Solder Joints-Reliability," Global SMT & Package, December 2005.

- [5] IPC Solder Products Value Council, "Round Robin Testing and Analysis of Lead Free Solder Pastes with Alloys of Tin, Silver and Copper," 2005.

- [6] IPC-A-610-D, "Acceptance of Electronic Assemblies," February 2005.

- [7] IPC J-STD-001D, "Requirements for Soldered Electrical and Electronic Assemblies."

- [8] IPC-SM-7525A, "Stencil Design Guidelines," May 2000.

- [9] JEDEC, JESD22-B102D, "Solderability," VA, Sept. 2004.

- [10] Syed, Ahmer, et al, "Board-Level Assembly and Reliability Considerations for QFN Type Packages," Amkor Technology, Inc., Chandler, AZ.

## **Related Datasheets**

FDME410NZT - <a href="http://www.fairchildsemi.com/pf/FD/FDME410NZT.html">http://www.fairchildsemi.com/pf/FD/FDME410NZT.html</a>

FDME510PZT - <a href="http://www.fairchildsemi.com/pf/FD/FDME510PZT.html">http://www.fairchildsemi.com/pf/FD/FDME510PZT.html</a>

FDME905PT - <a href="http://www.fairchildsemi.com/pf/FD/FDME905PT.html">http://www.fairchildsemi.com/pf/FD/FDME905PT.html</a>

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and h

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative