# ONSEM

# AN-9034

# Introduction

The Power MOSFET is a very popular switching device used in switching power supplies and DC-DC converters. Their operation frequency is being continuously increased to reduce size and increase power density. This causes high di/dt, intensifies the negative effect from para-sitic inductances, and results in high voltage spike between the Power MOSFET drain and source during device turn off. The spike is worst at power on due to empty bulk capacitors and small inductance because the transformer primary side inductance almost reaches the level of leakage inductance. Fortunately, the Power MOSFET is equipped to withstand a certain level of stress, unnecessitating expensive protection circuits. This note presents an effective way to determine the applicability of a Power MOSFET in an application. The designers can balance between cost and reliability.

# 1. A Rating System: Single Pulse UIS SOA

**onsemi** has introduced a rating system that specifies the Power MOSFET capability for single pulse Unclamped Inductive Switching (UIS) <sup>[1]</sup>. This system enables easy determination and/or estimation of device feasibility in any application with simple parameters: the peak current through the Power MOSFET during avalanche (I<sub>AS</sub>), the junction temperature at the start of the UIS pulse (T<sub>J</sub>), and the time the Power MOSFET remains in avalanche (t<sub>AV</sub>). By plotting I<sub>AS</sub> and t<sub>AV</sub> on a graph the user can check the UIS capability of the device. The application specific part of **onsemi** UltraFET and POWERTRENCH<sup>®</sup> provide such rating chart, and a part of QFET datasheets will soon be updated.

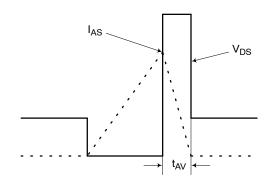

Figure 1. UIS Waveforms

# 2. Over-Voltage Conditions

The over-voltage conditions in actual applications can be classified into two different groups. One is when the drain-source voltage of Power MOSFET exceeds the specified absolute maximum rating but is still short of the breakdown voltage of the device. This is not an avalanche situation and the device feasibility can be determined through junction temperature analysis. Another is when the device breaks down and goes into avalanche mode. The Rating System is a great tool for avalanche mode analysis.

# 3. Avalanche Mode Analysis

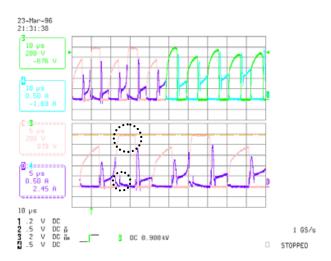

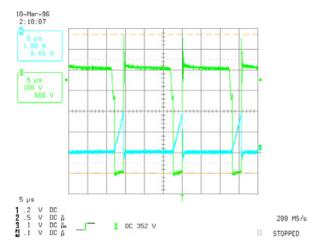

When the Power MOSFET avalanches, the drain-source voltage is clamped to its effective breakdown voltage and the current is commutated through a parasitic antiparallel diode. Figure 2 shows typical avalanche waveforms in switching power supplies. The drain-source voltage is over 1 kV and a commutating current is observed.

Figure 2. Device Breakdown, 800 V Rated MOSFET

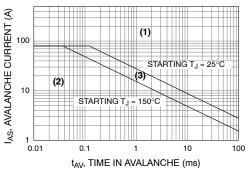

The UIS Rating System is very useful in dealing with avalanche situations. There are three areas in the UIS SOA graph as indicated in Figure 3: (1) above and right of the 25 °C line, (2) below and left of the maximum junction temperature line, (3) in between the two lines. (1) and (2) are easy to determine: the device is within the UIS rating ((2)), or beyond the rating ((1)). But the junction temperature of the Power MOSFET at the start of the UIS pulse is required to determine (3). The junction temperature analysis methods will be discussed later in detail.

This UIS Rating System can also be applied to repetitive pulses through superposition technique. Each UIS pulse is evaluated separately just as in single pulse. Usually, the last pulse in a series of power pulses occurs at the highest junction temperature and is therefore the worst stress. If the Power MOSFET is within the specified UIS rating for the last pulse, it is certainly within the UIS ratings for previous pulses which occurred at a lower junction temperature <sup>[2]</sup>.

Figure 3. UIS Capability, FDP050AN06A0

#### 4. Junction Temperature Analysis

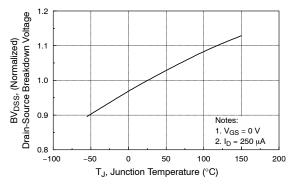

Generally, breakdown of the Power MOSFET seldom occurs even if the drain-source voltage exceeds the absolute maximum rating. The  $BV_{DSS}$  of the Power MOSFET has a positive temperature coefficient as shown in Figure 4. It reaches about 990 V at 120 °C in this example. Therefore, a greater voltage is required to cause device breakdown at higher temperature. In many cases, the ambient temperature during the Power MOSFET operation is over 25 °C and the power loss causes the junction temperature of the Power MOSFET to rise above the ambient temperature.

Figure 4. Normalized BV<sub>DSS</sub> vs T<sub>J</sub>, FQA11N90C

Also, note that the BVDSS in Figure 4 is measured at  $250 \,\mu\text{A}$  of the drain current. In a real breakdown, the drain current reaches a much higher level and the breakdown voltage is even higher than the above value.

Figure 5. Waveforms from Switching Power Supply, 600 V Rated MOSFET

For practical purposes, an actual breakdown voltage in applications is chosen as 1.3 times the rated low current breakdown voltage <sup>[1]</sup>. Figure 5 is an example of this non-breakdown but over the absolute maximum rating. The peak drain-source voltage is 668 V but there is no breakdown yet.

Even though the abnormal voltage spike did not cause a device breakdown, the junction temperature of the Power MOSFET should be kept below the specified maximum junction temperature to ensure reliability. The steady state junction temperature can be expressed as

$$T_{J} = P_{D} R_{\Theta JC} + T_{C}$$

(eq. 1)

where

$T_J$ : junction temperature  $T_C$ : case temperature

P<sub>D</sub>: power dissipated in the junction

$R_{\Theta,IC}$ : steady state thermal resistance from junction to case

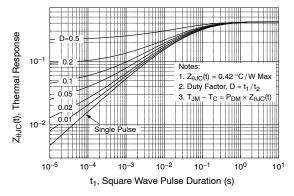

In many applications, however, the power dissipated in the Power MOSFET is pulsed rather than DC. When a power pulse is applied to the device, the peak junction temperature varies depending on peak power and pulse width. Thermal resistance at a given time is called transient thermal resistance and is expressed as

$$Z_{\Theta JC}(t) = r(t) \times R_{\Theta JC}$$

(eq. 2)

where r(t) is a time dependent factor regarding thermal capacity. For very short pulses, r(t) is quite small, but for long pulses it is nearly 1 and transient thermal resistance approaches the steady state thermal resistance. Most **onsemi** Power MOSFET datasheets have a graph similar to that of Figure 6.

Figure 6. Transient Thermal Response, FQA11N90C

From this curve, the junction temperature can be obtained as follows:

$$T_{J} = P_{D} Z_{\Theta JC}(t) + T_{C}$$

(eq. 3)

For example, the calculation of the temperature rise resulting from single 2 kW power pulse applied to FQA11N90C during 1  $\mu$ s can be expressed as follows:

$$T = P_D Z_{\Theta JC}(1 \ \mu s) = 2000 \times 1.49 \times 10^{-3} \approx 3 \ ^\circ C \eq. 4) \label{eq:eq.4}$$

The applied power is substantial but the temperature rise is only 3 degrees. Note that a power dissipation rating specified in the datasheet is a steady state power rating, and in a relatively short time the Power MOSFET can handle even greater power pulse.

In the above example, however, transient thermal resistance of 1  $\mu$ s is not available in Figure 6. In cases where the given time is too short and out of the graph range, the single pulse transient thermal resistance is known to be proportionate to the square root of time. So  $Z_{\Theta JC}(1 \ \mu s)$  becomes

$$\begin{split} & Z_{\Theta JC}(1 \ \mu s) \, = \, Z_{\Theta JC}(10 \ \mu s) \, \times \, \sqrt{\frac{1 \ \mu s}{10 \ \mu s}} \, = \\ & = \, 4.72 \, \times \, 10^{-3} \, \times \, \sqrt{0.1} \, = \, 1.49 \, \times \, 10^{-3} \end{split} \tag{eq. 5}$$

where

$Z_{\Theta JC}$  (10 µs): taken from Figure 6

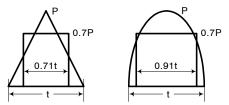

The above thermal response is based on a rectangular power pulse. It is possible to obtain a response for arbitrary shapes. However, since the mathematical solution would be very complex, it would be easiest to convert it to an equivalent rectangular pulse. Some examples for triangular and sine wave power pulses are shown in Figure 7.

Figure 7. Conversion of Power Pulses

The equation 3 can also be applied to applications that have repetitive pulses. The transient thermal resistance for repetitive pulses can be approximated as follows <sup>[3]</sup>

where

t<sub>1</sub>: pulse width of the power pulse t<sub>2</sub>: period of the power pulse

Assume a situation where the drain-source voltage of a Power MOSFET applied to a switching power supply exceeds its maximum rating specified in the datasheet during delay time to protection activation while conducting short circuit test. The specific conditions are as follows: FQA9N90C switching device, 100 ns  $t_{AV}$ , 9.2 µs period, and 20 ms delay time. In this case, the transient thermal resistance becomes

$$\begin{split} & Z_{\Theta JC}(t) \ = \ 0.01 \ \times \ Z_{\Theta JC}(20 \ \text{ms}) + (1 \ - \ 0.01) \ \times \\ & \times \ Z_{\Theta JC}(9.3 \ \mu \text{s}) + Z_{\Theta JC}(100 \ \text{ns}) - Z_{\Theta JC}(9.2 \ \mu \text{s}) \ = \ 0.00274 \\ & (\text{eq. 7}) \end{split}$$

If a 5 kW power loss is assumed during avalanche, the resulting junction temperature rise will be

$$\Delta T = 5 \text{ kW} \times 0.00274 \text{ }^{\circ}\text{C/W} = 13.7 \text{ }^{\circ}\text{C}$$

(eq. 8)

This is an additional junction temperature rise caused by avalanche. Therefore, the system designer should first calculate the junction temperature of a normal operation, and then add the above value to obtain the transient junction temperature during avalanche. This temperature should be kept below the maximum allowable junction temperature with some safety margin according to the designer's choice.

#### 5. Conclusions

The system designers are frequently forced to determine the applicability of a Power MOSFET to their application. This can be done by using the avalanche mode analysis and/or junction temperature analysis which are very practical.

### AN-9034

#### References

- [1] "Single Pulse Unclamped Inductive Switching: A Rating System", onsemi Application Note AN-7514

- [2] "A Combined Single Pulse and Repetitive UIS Rating System", onsemi Application Note AN-7515

- [3] Rudy Severns, 1984, "Safe Operating Area and Thermal Design for MOSPOWER Transistors", MOSPOWER Applications Handbook, Siliconix

POWERTRENCH is a registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights or the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such u

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales