**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# Transmission-Line Effects Influence High-Speed CMOS

Unlike low-power, metal-gate CMOS, high-speed 54HC/74HC devices readily drive long cable runs and backplanes. While the family maintains CMOS's traditional noise immunity, you must watch transmission-line effects in such applications.

Because of 54HC/74HC high-speed CMOS's short propagation delays and fast rise and fall times, you must understand its transmission-line behavior when driving lines as short as even a foot or two, whether those lines are coaxial cables, twisted pairs or backplanes. Moreover, the devices' fast edge rates increase the likelihood of crosstalk among interconnecting cables.

Despite the need, however, to take design precautions that minimize adverse effects related to high-speed operation, 54HC/74HC logic – unlike slower metal-gate CMOS – includes many features that suit it to driving transmission lines. For example, its symmetrical push-pull outputs result in stiff logic levels, and its high output drive allows fast bit rates.

Another advantage of high-speed-CMOS designs is that they don't prove to be as difficult as those based on other high-speed logic families. In general, high-speed CMOS doesn't require the detailed attention to pc-board layout and transmission-line characteristics that Schottky TTL or ECL designs do. Furthermore, controlling unwanted reflections is easier in the CMOS designs, because 54HC/74HC devices' electrostatic-protection diodes tend to clamp the reflected voltages to the power-supply levels.

## **Mismatches Create Reflections**

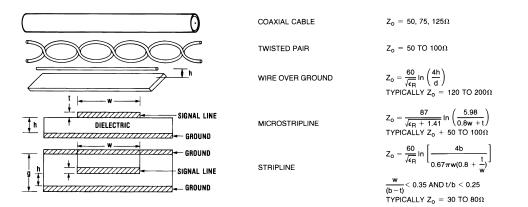

Transmission-line effects come into play when signal-line lengths are so long that the signal delay down the line and back becomes longer than the waveform's rise or fall time. Mismatches between the line's characteristic impedance and either the driver's output or the receiver's input impedance create signal-line reflections. These in turn cause overshoot and undershoot, which can reduce noise margins and cause excessive delay. *Figure 1* shows various transmission media and their impedances.

# **ON Semiconductor®**

## www.onsemi.com

# **APPLICATION NOTE**

A 54HC/74HC device's output rise and fall times can be as short as 5 ns, and transmission–line effects can become noticeable when lines longer than a foot or two are driven. The length of the signal line at which transmission–line ringing should be considered is:

$$MAXIMUM LINE LENGTH = \frac{OUTPUT RISE/FALL TIME}{2 (DELAY PER UNIT LENGTH)}$$

(eq. 1)

The signal delay per unit of line length  $(t_{PD})$  depends on the line's characteristic impedance and the load on the line. For a typical pc-board trace with a groundplane,

$$t_{PD} = 1.017 \sqrt{0.47 \epsilon_{R} + 0.67} \text{ ns/ft}$$

(eq. 2)

where  $\epsilon_R$  is the relative dielectric constant. Loading the trace with inputs to other gates alters the t<sub>PD</sub>.

$$t_{PD} (ALTERED) = t_{PD} \sqrt{1 + \frac{C_{IN}}{C_O}}$$

(eq. 3)

where  $C_{IN}$  is the total input capacitance associated with the line, and  $C_O$  is the line capacitance per unit of length.

If you know the characteristics of the transmission line, you can use these equations to find the signal-transit time. This time is typically between 1.5 and 2.4 ns/ft for an unloaded line.

In addition to the line's transit time, you need to find its characteristic impedance:

$$Z_{O} = L_{O} / C_{O}$$

(eq. 4)

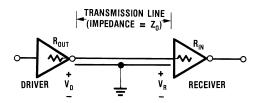

where  $L_O$  and  $C_O$  are the wire's inductance and capacitance per unit of length. When a 54HC/74HC device drives a transmission line (*Figure 2*), the driver's output looks into the equivalent line impedance. When the output switches, the signal propagated is the result of the voltage divider created by the line and the driver's impedance.

Published in EDN Magazine ©Copyright 1984 Cahners Magazine

# AN-393

# Figure 1. By Using the Impedances for Various Types of Signal–transmission Lines, You Can Determine the Amount of Ringing You'll Experience. (Note that $\epsilon_R$ Is the Relative Dielectric Constant.)

If the line's electrical length is long compared with the signal's rise time, the mismatch of the line and the CMOS input creates a reflection when the signal reaches the other end of the line. The reflection's magnitude depends on the incident signal's voltage ( $V_{INC}$ ) and the reflection coefficient (p), where

$$p = \frac{R_{IN} - Z_O}{R_{IN} + Z_O}$$

(eq. 5)

The reflected signal is therefore

$$V_{\rm R} = V_{\rm D} \left(1 + r\right) \tag{eq. 6}$$

# **High Input Doubles Reflection**

Figure 2. When a High-speed CMOS Driver/Receiver Pair Communicates over Distances Longer than a Foot or Two, Transmission-line Effects Come into Play.

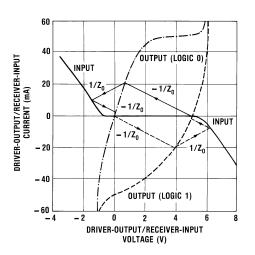

Figure 3. This Plot of Input and Output Transfer Functions for Standard 54HC/74HC High-speed CMOS Logic Includes the Effects of Input-protection and Parasitic Diodes. It Provides the Basis for a Graphic Method of Determining Ringing and Overshoot.

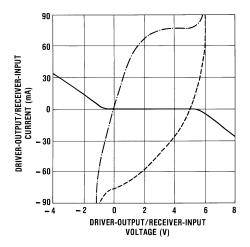

Figure 4. Bus-output Drivers in the 54HC/74HC High-speed CMOS Family Exhibit Different Input and Output Transfer Functions than Do the Standard Parts whose Characteristics are Shown in *Figure 3*.

Because a 54HC/74HC device's input impedance is high compared with the line's (r = 1.0), the reflected voltage at the receiver doubles. This reflection propagates back to the driver, where another reflection is generated (depending on the driver's output impedance). Typical 54HC/74HC output impedances result in reflection coefficients of -0.3 to -0.7.

A simplified analysis based on the preceding equations, however, fails to take into account nonlinearity in a 54HC/74HC gate's output impedance. Also, the input of a 54HC/74HC gates has diodes to  $V_{CC}$  and ground; these diodes clamp the reflected signal as it tries to exceed the supply level.

A load-line graphic technique overcomes these drawbacks. Illustrating the technique, *Figure 3* and *Figure 4* plot the input and output characteristics for a standard and a bus-driver 54HC/74HC IC at  $V_{CC} = 5$  V. These plots include the effect of the input and output diodes. With these curves, you can approximately determine the ringing for various line impedances when one 54HC/74HC gates drives another.

An example based on a High-to-Low transition on a 200  $\Omega$  line illustrates how to use the graphs. Starting at the quiescent 5 V, 0 A point on the logic–One output's curve (*Figure 3*), draw a load line with a slope of  $-1 / Z_0$  to the logic–Zero output's curve. The voltage at this intersection is the initial output voltage that drives the line after the transition. Then draw a line with a +1 /  $Z_0$  slope to the input curve. This intersection yields the signal's voltage, including the reflection, when it reaches the receiver. Next, draw another line back to the logic–Zero output curve. This intersection indicates the voltage at the driver when the reflection returns. This process continues until the zigzag load line converges on the 0 V, 0 A intersection.

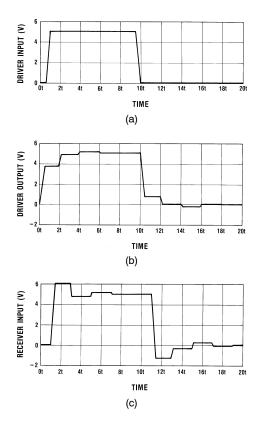

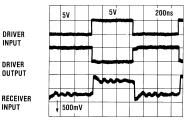

*Figure 5* plots the *Figure 3* example's voltages vs propagation delay. *Figure 6* shows real-world waveforms for a 74HC00 device driving another gate through a wire

poised above a groundplane ( $Z_O = 200 \Omega$ ). Notice that the driver's output level swings further toward the opposite logic level than the graphic method initially predicts, resulting in slightly more–ringing at the receiver as well. This additional ringing is due to either a lower output impedance or a slightly higher line impedance than that used in the paper analysis.

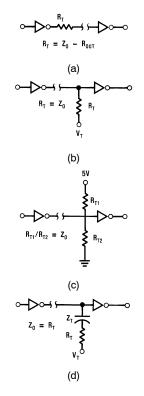

Although line reflections aren't a problem for most designs, you may have to reduce ringing for certain applications, such as those including long cables, backplanes and sensitive circuits that can't tolerate radiated noise and crosstalk. You can use several techniques to reduce ringing. One solution is to use series–terminating resistors (*Figure 7a*). Series termination places a resistor in series with the driver's output to match the output impedance of the driver to that of the line. This procedure eliminates overshoot at the receiver's end of the line but slows down the output signal, and it won't work with buses or backplanes.

Figure 5. Using the Plots Shown in *Figure 3* and *Figure 4* Along with the Graphic Method Described in the Text, You Can Construct the Driver (b) and Receiver (c) Waveforms Resulting from an Input (a).

# Parallel Terminations Can Overload CMOS

Parallel termination (*Figure 7 (b*) and *Figure 7 (c*)) connects a resistor at the receiver's end of the line to either  $V_{CC}$  or ground or to a voltage divider between  $V_{CC}$  and ground. The resistor value (or the equivalent resistance of the resistor pair) should match the line's impedance.

Normally, a system backplane has one termination per signal line. Some very-high-speed buses, however, can include two termination networks at each end of the backplane for each line.

One problem with parallel termination is that the termination consumes large amounts of power, negating the reason for choosing 54HC/74HC devices to begin with. Moreover, because the termination network must match the line's impedance, parallel termination can overload a 54HC/74HC device's outputs and prevent them from driving the bus to a valid logic level.

Consider, for example, a 150  $\Omega$  TTL bus with a single termination and the equivalent of a 150  $\Omega$  termination resistor connected to a 3.5 V supply. The worst–case output impedance of a 54HC/74HC bus driver is 100  $\Omega$ . The dc output voltage for the 54HC/74HC driving a TTL bus to a low level would be V<sub>OUT</sub> = 3.5 V (100  $\Omega$  / 250  $\Omega$ ) = 1.2 V, which is too high to represent a valid logic–Zero output. You can use such dc–termination schemes only if a 54HC/74HC device can pull the termination network to within 0.5 V of the supply rails (HCT parts work between 0.4 and 2.4 V).

Aside from such brute–force power considerations, a subtle problem arises from reflections in certain cases. If the line is long enough to exhibit a significant delay down the line, the ability of the receiving logic element to switch on the original incident–wave front becomes important. If the incident wave isn't of the proper magnitude, the receiver must wait for the reflection before sensing the change at its input. The voltage at the receiver equals the driver's output voltage divided across the driver's output impedance and the line's characteristic impedance. 54HC/74HC gates typically have 40 to 50  $\Omega$  output impedances, so 54HC/74HC receivers switch on the incident–wave transitions if the line impedances are greater than 150  $\Omega$  typically.

In general, when replacing LS components with 54HC/74HC units, avoid driving buses with a termination network whose equivalent impedance is less than 500  $\Omega$  (worst case) terminated to V<sub>CC</sub> or ground, or 250  $\Omega$  terminated to 3 V.

The TTL termination's impedance isn't the only problem involved in substituting 54HC/74HC parts for TTL. For example, consider the voltages that the termination networks are tied to. Usually, TTL termination networks look like their equivalent impedance tied between 2.5 and 3.5 V. Consequently, when these TTL buses are in the high–impedance state, they float toward these voltages, causing the 54HC/74HC circuits to draw  $I_{CC}$  currents that are large compared with the currents generated when the bus is terminated to  $V_{CC}$  or ground. Also note that some logic errors might develop because the 2.5 to 3.5 V range is not a valid 54HC/74HC logic level.

Using the termination network shown in *Figure 7* (d), which couples the signal to the termination network with a small capacitor, avoids this problem. The capacitor blocks

the DC currents while acting as a short circuit during signal transitions. This termination scheme doesn't draw any DC power, although it does draw additional AC (dynamic) power. Furthermore, if the bus goes to a high–impedance state, the termination capacitors hold the bus at the last logic level for a short time (perhaps a millisecond), avoiding excessive  $I_{CC}$  currents. If the bus has the potential to float for long periods, you might have to add large–value pull–up resistors to ensure that bus leakages don't cause spurious behavior.

Figure 6. A High-speed CMOS Device Driving Another Gate through a 28-gauge Wire Poised above a Groundplane ( $Z_o = 200 \Omega$ ) Exhibits Higher Ringing and Overshoot than Predicted in *Figure 5*, Thus Indicating a Lower Output Impedance or Higher Line Impedance than that Used in the Prediction.

Figure 7. The Three Termination Techniques Shown Here in (a), (b), and (c) Work Best for Conventional TTL. For High-speed CMOS, (d) Might Provide the Best Solution. These considerations apply to 54HC/74HC outputs. 54HC/74HC inputs interface easily to any type of bus or transmission line that meets the 54HC/74HC input–voltage requirements.

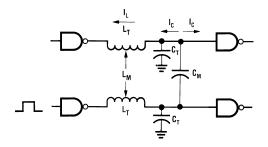

Eliminating troublesome reflections only handles problems involving a single transmitter/receiver pair. Seldom, however, do transmitter/receiver pairs exist in isolation; they more commonly occur in groups, and the possibility of crosstalk always exists. Parasitic mutual inductance and capacitance associated with system interconnections cause crosstalk.

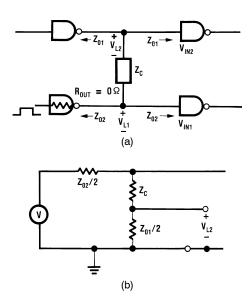

Figure 8. Ringing and Overshoot from Impedance Mismatches Aren't the Only Problems You Can Encounter in Applying High-speed CMOS. Parasitic Coupling Arising from Distributed Capacitance and Inductance of Parallel Wires or Pc-board Traces Can Cause Crosstalk.

*Figure 8* and *Figure 9* illustrate these inductances and capacitances. Their magnitudes depend on the length, spacing, amount of shielding and type of wiring used. Generally, crosstalk isn't necessarily a concern unless two

or more signal lines run in parallel over long distances. Even when using long signal runs, 54HC/74HC devices' noise immunity eases the requirements for crosstalk minimization.

Although you can analyze crosstalk by finding the current coupling caused by distributed capacitance and inductance,

$$V_{L2} = \frac{Z_{O2} / 2}{Z_{C} + \left(\frac{Z_{O1}}{2}\right) + \left(\frac{Z_{O2}}{2}\right)} \times V_{OUT} = \frac{1}{2} \frac{Z_{O}}{2 Z_{C} + Z_{O}} V_{CC}$$

(eq. 7)

When the signal reaches the receiver, the reflection causes the signal's level to double, and  $V_{IN} = 2 (V_{L2})$ .

Qualitatively, you can see that crosstalk increases as  $Z_C$  decreases.  $Z_C$  in turn decreases with increasing coupling length (decreasing the spacing between the two connectors) and poor shielding. Lowering  $Z_O$  decreases crosstalk but not as dramatically as changing  $Z_C$  does. Notice that as  $Z_C$  becomes small (which indicates a lot of cross coupling), changing  $Z_O$  has little effect with respect to reducing crosstalk. However, adding shielding to the cable both lowers  $Z_O$  and raises  $Z_C$  and consequently proves effective in reducing crosstalk.

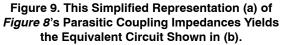

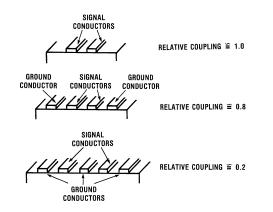

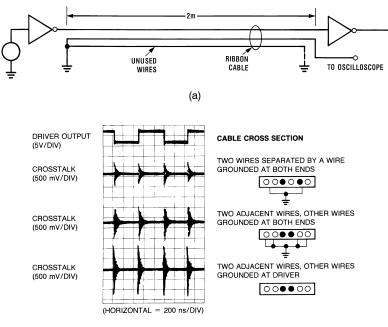

Figures Figure 10, Figure 11 and Figure 12 illustrate crosstalk effects for several conductor configurations. Figure 10 shows the relative coupling between two pc-board traces alone and also with various guarding schemes. Figure 11 illustrates oscilloscope traces of a 1-MHz signal in a 2 meter bundled cable with various numbers of wires connected to ground. Notice the dramatic reduction in crosstalk between two wires when a third wire is grounded in the cable. Figure 12 shows the same schemes for various configurations of wire in a ribbon cable. Here, the lowest crosstalk comes from separating the two signal lines by a ground cable. The most crosstalk occurs when the two cables are adjacent to each other and no other cable is grounded.

Figure 10. Grounding Scheme Can Significantly Reduce Crosstalk. For Example, Separating Pc-board Signal Conductors with Grounded Ones Reduces Relative Coupling from 1 to 0.2. AN-393

Figure 11. The Effectiveness of Guarding Techniques in Reducing Crosstalk Isn't Limited to Pc Boards, as Results Based on a 6-wire Bundled-cable Test Circuit Illustrate (a). Grounding Unused Wires at Both Ends Yields the Best Performance (b).

(b)

Figure 12. To Reduce Crosstalk between Two Conductors in a Ribbon Cable, Separating the Signal-carrying Conductors with Ones Grounded at Both Ends Proves to Be Effective.

## Low Voltages Increase Delays

Although the bulk of the applications for high-speed CMOS involve a 5 V power supply, some applications can use 2 V - the low end of 54HC/74HC devices' power-supply operating range. At 2 V, a 54HC/74HC device has approximately one-third to one-fifth the output drive and about three to five times the circuit delays and transition times of the same ICs powered by 5 V supplies. At  $V_{CC} = 2 V$ , output transition times are about 30 nsec, which tends to ease signal-line routing and termination requirements. Because rise and fall times are so long, reflections and ringing are insignificant. Crosstalk and general signal-line to signal-line noise coupling are also reduced by a factor of three to five, limiting internally generated noise coupling. However, by using a lower supply voltage, the dc noise immunity is approximately halved, and overall immunity to external noise is reduced.

Thus, for 2 V designs, transmission-line noise and ringing are essentially eliminated, and crosstalk is reduced by a factor of two (when device noise-immunity reduction is included). Designing with high-speed CMOS at 2 V can best be described as almost identical to trying to design with older CMOS logic at 5 V.

## References

- 1. Blood, W. R. Jr., *MECL System Design Handbook*, Motorola Semiconductor Inc, 1980.

- Blakeslee, T. R., *Digital Design with Standard MSI and LSI*, 2nd edition, John Wiley and Sons, New York, 1979.

- 3. Designing With TTL Integrated Circuits, Texas Instruments Staff, McGraw Hill, New York, 1971.

- 4. *MM54HC/74HC High–Speed CMOS Handbook*, Fairchild Semiconductor Corp, 1983.

- "Fairchild's Process Enhancements Eliminate the CMOS SCR Latchup Problem in 54HC/74HC Logic," Application Note AN–399, Fairchild Semiconductor Corp, 1983.

- 6. "DC Electrical Characteristics of High–Speed CMOS," Application Note *AN–319*, Fairchild Semiconductor Corp, 1983.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor ."Typical" parameters which may be provided in ON Semiconductor dates sheets and/or application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights or others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semic

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe. Middle East and Africa Technical Support:

ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

For additional information, please contact your local Sales Representative