## AC-DC Active Clamp Flyback PWM IC

## **NCP1568**

The NCP1568 is a highly integrated ac-dc PWM controller designed to implement an active clamp flyback topology. NCP1568 employs a proprietary variable frequency algorithm to enable zero voltage switching (ZVS) of Super-Junction or GaN FETs across line, load, and output conditions. The ZVS feature increases power density of a power converter by increasing the operating frequency while achieving high efficiency. The Active Clamp Flyback (ACF) operation simplifies EMI filter design to avoid interference with other sensitive circuits in the system. The NCP1568 features a HV startup circuit, a strong low side driver, and a 5 V logic level driver for the active clamp FET. The NCP1568 is suitable for a variety of applications including ac-dc adapters, industrial, telecom, lighting, and other applications where power density is an important requirement.

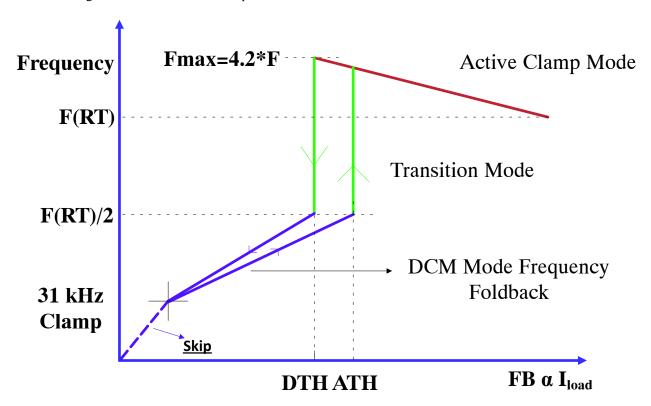

The NCP1568 also features multimode operation and transitions from ACF mode to Discontinuous Conduction Mode (DCM) to meet regulatory requirements from around the world. The NCP1568 further implements skip in standby mode, resulting in excellent standby power. The combination of flexible control scheme and user programmable features allow the use of NCP1568 with Super–Junction MOSFETs (Si) and Gallium Nitride (GaN) FETs.

#### **Features**

- Topology and Control Scheme

- Active Clamp Flyback Topology Aids in ZVS

- Proprietary Multi-Mode Operation to Enhance Light Load Efficiency

- Proprietary Adaptive ZVS Allows High Frequency Operation while Reducing EMI

- Inbuilt Adaptive Dead-Time for Both Main and Active Clamp

- Peak Current-Mode Control with Inbuilt Slope Compensation with Options

- Flexible Control Scheme and Programmability Allow for Configuration with Either External Silicon or GaN FETs

- DCM and Light Load Operation

- ◆ Customer Programmable Optional Transition to DCM

- Integrated Frequency Foldback with Minimum Frequency Clamp for Highest Performance in Standby Mode

- Minimum Frequency Clamp and Quiet Skip Eliminates Audible Noise

- ◆ Standby Power < 30 mW</li>

- Integrated HV and Startup Circuits

- 700 V Startup Circuit

- ◆ AC Line Brownout Detect

- Drivers

- 0.85 A/1.5 A Source/Sink for Low Side

- ♦ 65 mA/150 mA Active Clamp Driver Output

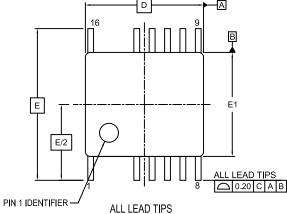

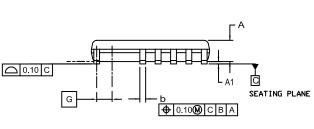

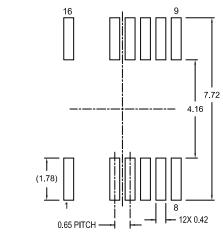

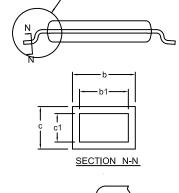

#### MARKING DIAGRAM

TSSOP-16 **DT SUFFIX** CASE 948BW

1

1568 = Specific Device Code XXX = Specific Variant (S02, G03, G04) = Assembly Location

= Wafer Lot Υ = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

#### Features (Continued)

- Oscillator

- Programmable Frequency from 100 kHz to 1 MHz

- Internal Soft-Start Timer with 4 **Options**

- Protection

- Dedicated FLT Pin Compatible with a Thermistor

- Adjustable Over Power Protection (OPP)

- Option for Auto-Recovery and Latched in Various Faults

- Internal Thermal Shutdown

#### **Applications**

- USB Power Delivery

- Notebook Adapters

- High Density Chargers

- Industrial Power Supplies

#### **ORDERING INFORMATION**

| Device          | LEB/DTMAX/<br>T_ZVSA<br>(ns) | T_ZVSB<br>(ns) | ACF FET<br>Soft Start Time<br>(ms) | ACF FET<br>Soft Stop Time<br>(ms) | Fixed Dead-Time<br>from LDRV OFF to<br>HDRV or ADRV<br>ON (ns) | ATH Pin<br>Mapping | Package               | Shipping <sup>†</sup>  |

|-----------------|------------------------------|----------------|------------------------------------|-----------------------------------|----------------------------------------------------------------|--------------------|-----------------------|------------------------|

| NCP1568S02DBR2G | 179/420/210                  | 150            | 4                                  | 0                                 | 20                                                             | I = 1.92 E = 1     | TSSOP-16<br>(Pb-Free) | 2,500 /<br>Tape & Reel |

| NCP1568G03DBR2G | 99/240/120                   | 60             | 4                                  | 0.5                               | 0                                                              | I = 1.92 E = 1     | TSSOP-16<br>(Pb-Free) | 2,500 /<br>Tape & Reel |

| NCP1568G04DBR2G | 99/240/120                   | 100            | 4                                  | 0.5                               | 0                                                              | I = 1.92 E = 1     | TSSOP-16<br>(Pb-Free) | 2,500 /<br>Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

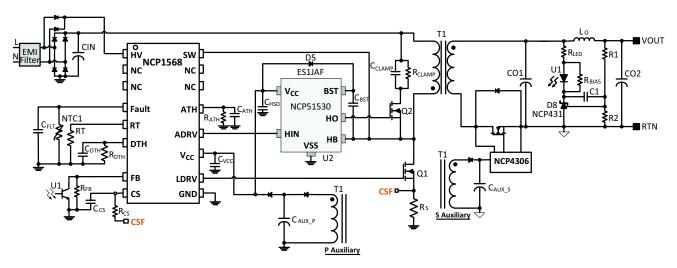

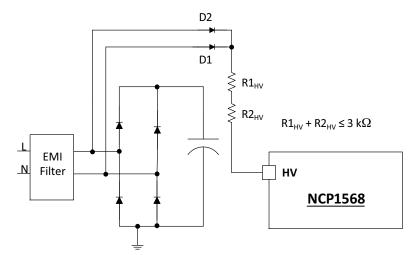

Figure 1. Typical Application for the NCP1568 Active Clamp Flyback

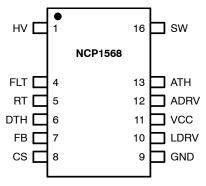

#### **PIN DESCRIPTION**

Figure 2. Pinout

#### **Table 1. PIN FUNCTIONAL DESCRIPTION**

| Pin Out<br>Controller |                 |                                                                                                                                                                                                                                    |

|-----------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option                | Name            | Function                                                                                                                                                                                                                           |

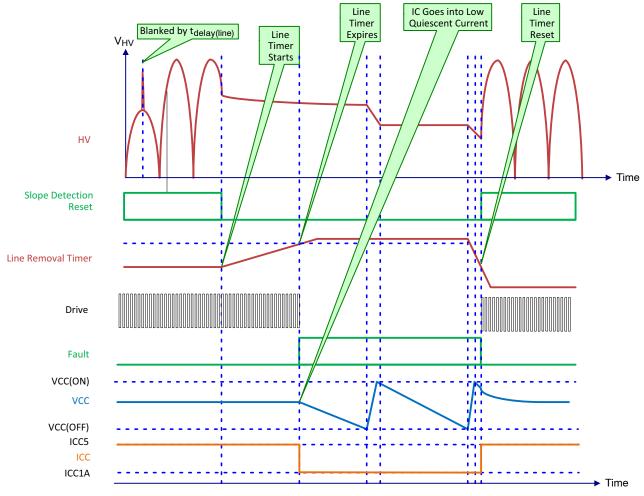

| 1                     | HV              | Input to the HV startup circuit. Information derived from HV pin is also used for BO detection, AC line presence detection and over power protection                                                                               |

| 2,3,14,15             | -               | Removed for creepage and clearance compliance                                                                                                                                                                                      |

| 4                     | FLT             | The controller enters fault mode if the voltage of this pin is pulled above or below the fault thresholds                                                                                                                          |

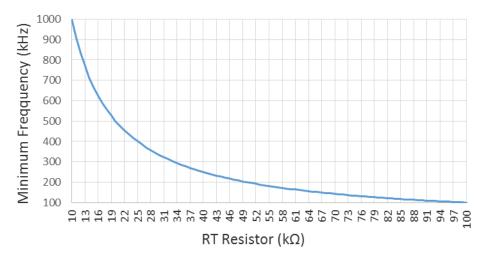

| 5                     | RT              | A resistor from the RT pin to ground sets the minimum frequency of the internal oscillator                                                                                                                                         |

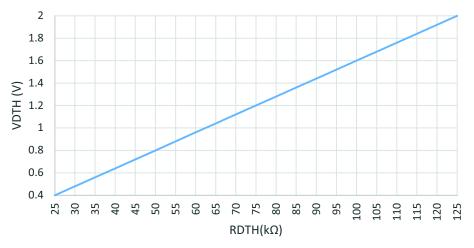

| 6                     | DTH             | A resistor to ground sets the ACF to DCM transition threshold                                                                                                                                                                      |

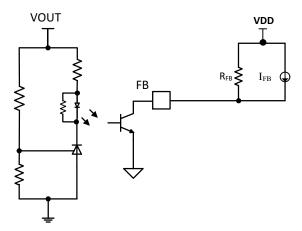

| 7                     | FB              | Feedback input allows direct connection to an opto-coupler and is pulled up with an internal resistor and current source                                                                                                           |

| 8                     | CS              | Current sense input. A CS resistor connected between the source of the power FET and the GND provides primary current information to the IC                                                                                        |

| 9                     | GND             | Ground reference                                                                                                                                                                                                                   |

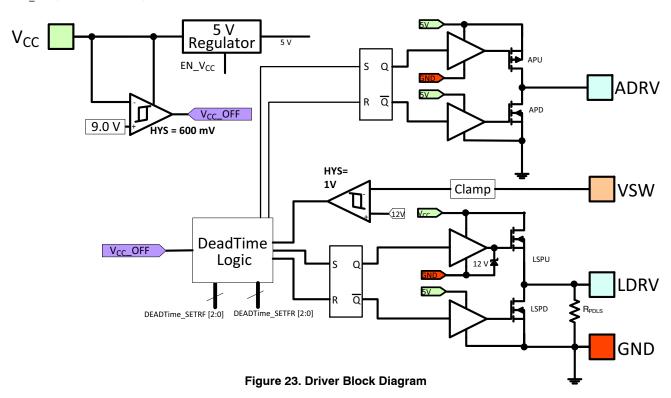

| 10                    | LDRV            | Low-side drive output. Clamped to 12 V output                                                                                                                                                                                      |

| 11                    | V <sub>CC</sub> | Supply input. At startup, an internal HV current charges the $V_{CC}$ capacitor. Once the power stage is enabled, an auxiliary winding supplies current to the $V_{CC}$ capacitor and the internal HV current source is turned-off |

| 12                    | ADRV            | ADRV is the 5 V alternate ground based high side driver signal                                                                                                                                                                     |

| 13                    | ATH             | A resistor to ground sets the DCM to ACF transition threshold                                                                                                                                                                      |

| 16                    | SW              | Connect to SW node used for adaptive dead-time control and ZVS based frequency modulation                                                                                                                                          |

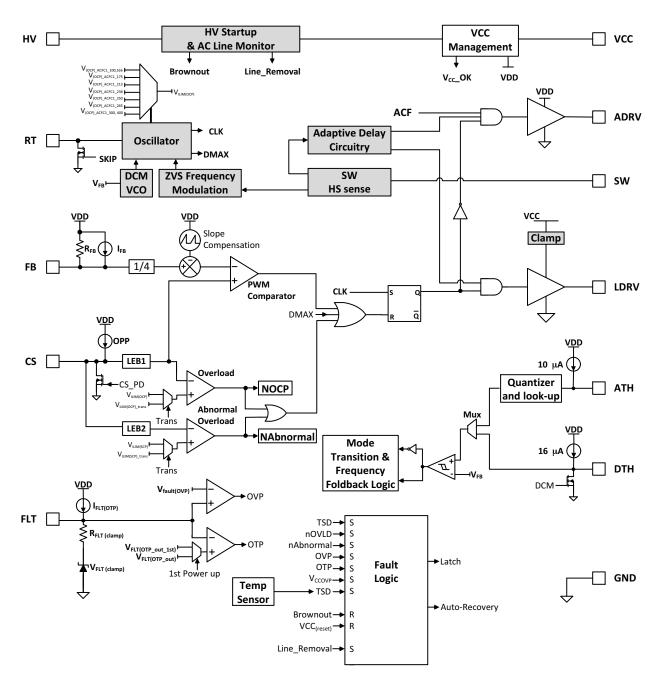

#### **BLOCK DIAGRAM**

Figure 3. Block Diagram

**Table 2. MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                    | Symbol                                           | Value                            | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------|-------------------|

| High Voltage Startup Circuit Input Voltage                                                                                                                                                                                                | V <sub>HV(MAX)</sub>                             | -0.3 to 700                      | V                 |

| High Voltage Startup Circuit Input Current                                                                                                                                                                                                | I <sub>HV(MAX)</sub>                             | 20                               | mA                |

| Supply Input Voltage                                                                                                                                                                                                                      | V <sub>CC(MAX)</sub>                             | -0.3 to 30                       | V                 |

| Supply Input Current                                                                                                                                                                                                                      | I <sub>CC(MAX)</sub>                             | 30                               | mA                |

| Supply Input Voltage Slew Rate                                                                                                                                                                                                            | dV <sub>CC</sub> /dt                             | 25                               | mV/μs             |

| SW Pin to GND                                                                                                                                                                                                                             | V <sub>SW(MAX)</sub>                             | –1 to 700                        | V                 |

| SW Pin Circuit Input Current                                                                                                                                                                                                              | I <sub>SW(MAX)</sub>                             | 1                                | mA                |

| ADRV Pin to GND                                                                                                                                                                                                                           | V <sub>ADRV</sub>                                | -0.3 V to 5.5                    | V                 |

| ADRV Driver Maximum Current                                                                                                                                                                                                               | I <sub>ADRV(SRC)</sub><br>I <sub>ADRV(SNK)</sub> | 130<br>190                       | mA                |

| Low Side Driver Voltage (Note 1)                                                                                                                                                                                                          | $V_{DRV}$                                        | −0.3 V to V <sub>DRV(high)</sub> | V                 |

| Maximum Input Voltage ATH                                                                                                                                                                                                                 | V <sub>ATH(MAX)</sub>                            | 0.3 V to 5.5                     | V                 |

| Maximum Input Current ATH                                                                                                                                                                                                                 | I <sub>ATH(MAX)</sub>                            | 10                               | mA                |

| Maximum Input Voltage DTH                                                                                                                                                                                                                 | V <sub>DTH(MAX)</sub>                            | 0.3 V to 5.5                     | V                 |

| Maximum Input Current DTH                                                                                                                                                                                                                 | I <sub>DTH(MAX)</sub>                            | 10                               | mA                |

| Current Sense Input Voltage                                                                                                                                                                                                               | V <sub>CS</sub>                                  | -0.3 to 5.5                      | V                 |

| Current Sense Input Current                                                                                                                                                                                                               | I <sub>CS</sub>                                  | 10                               | mA                |

| Maximum Input Voltage (Other Pins: FB, RT, FLT)                                                                                                                                                                                           | $V_{MAX}$                                        | -0.3 to 30                       | V                 |

| Maximum Input Current (Other Pins: FB, RT, FLT)                                                                                                                                                                                           | I <sub>MAX</sub>                                 | 27                               | mA                |

| Operating Junction Temperature                                                                                                                                                                                                            | TJ                                               | -40 to 125                       | °C                |

| Storage Temperature Range                                                                                                                                                                                                                 | T <sub>STG</sub>                                 | -60 to 150                       | °C                |

| Power Dissipation (T <sub>A</sub> = 25°C, 1 Oz Cu, 0.231 Sq Inch Printed Circuit Copper Clad) Plastic Package TSSOP16                                                                                                                     | P <sub>D(MAX)</sub>                              | 833                              | mW                |

| Thermal Resistance, Junction to Ambient 1 Oz Cu Printed Circuit Copper Clad) Plastic Package TSSOP16                                                                                                                                      | $R_{	hetaJA}$                                    | 150                              | °C/W              |

| ESD Capability Human Body Model per JEDEC Standard JESD22-A114F Except SW Pin Human Body Model per JEDEC Standard JESD22-A114F SW Pin Charge Device Model per JEDEC Standard JESD22-C101F. Latch-Up Protection per JEDEC Standard JESD78E |                                                  | 2000<br>1500<br>1000<br>±100     | V<br>V<br>V<br>mA |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 3. RECOMMENDED OPERATING CONDITIONS**

| Description                       | Symbol          | Min | Тур | Max | Units |

|-----------------------------------|-----------------|-----|-----|-----|-------|

| V <sub>CC</sub> operating voltage | V <sub>CC</sub> | 10  | 16  | 27  | V     |

| Operating Junction temperature    | Jc              | -40 |     | 125 | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Maximum driver voltage is limited by the driver clamp voltage, V<sub>DRV(high)</sub>, when V<sub>CC</sub> exceeds the driver clamp voltage. Otherwise, the maximum driver voltage is V<sub>CC</sub>.

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} \\ (V_{CC} = 12 \ V, \ V_{HV} = 120 \ V, \ V_{FLT} = open, \ V_{FB} = 2 \ V, \ RT1 = 33 \ k\Omega, \ V_{CS} = 0 \ V, \ C_{VCC} = 100 \ nF, \ A_{DRV} = 100 \ pF, \ L_{DRV} = 1.5 \ nF \ for \ typical values \ T_J = 25 ^{\circ}C, \ for \ min/max \ values, \ T_J \ is -40 ^{\circ}C \ to \ 125 ^{\circ}C, \ unless \ otherwise \ noted) \end{tabular}$

| Characteristics                                                                       | Conditions                                                        | Symbol                       | Min       | Тур        | Max        | Unit |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------|-----------|------------|------------|------|

| START-UP AND SUPPLY CIRCUITS                                                          |                                                                   |                              | •         | •          |            |      |

| Supply Voltage                                                                        |                                                                   |                              |           |            |            | V    |

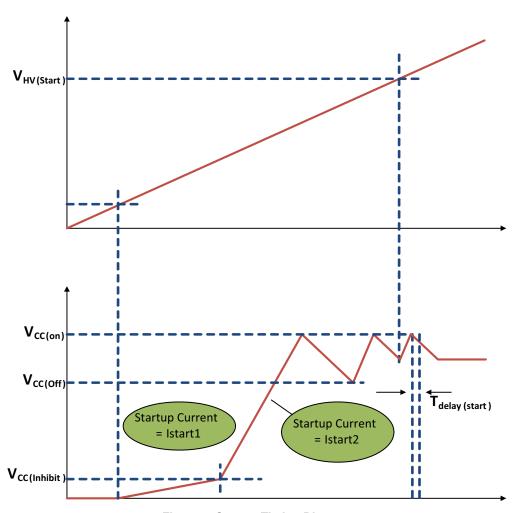

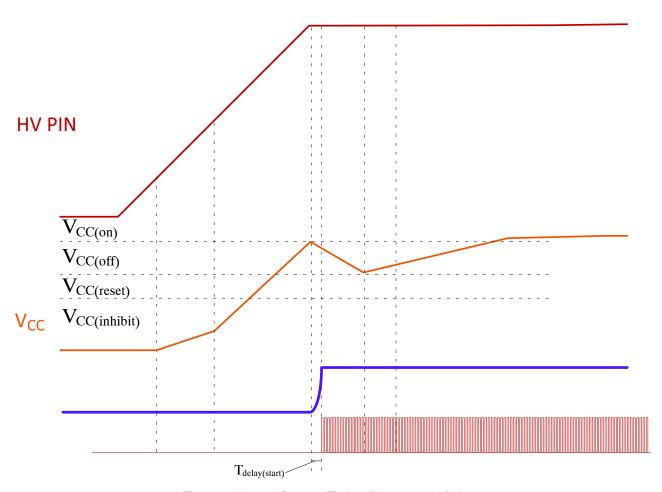

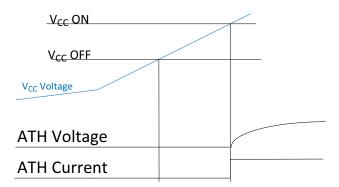

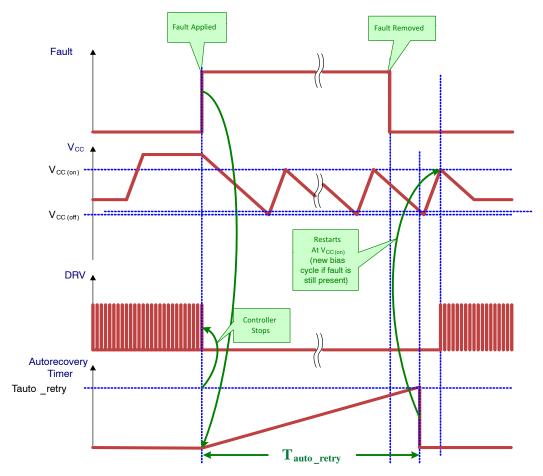

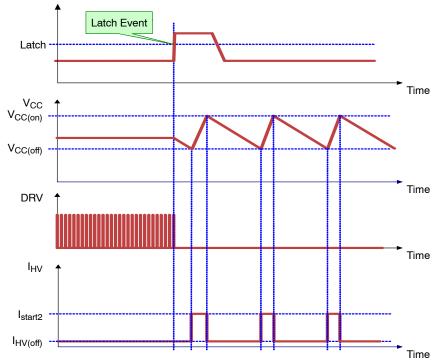

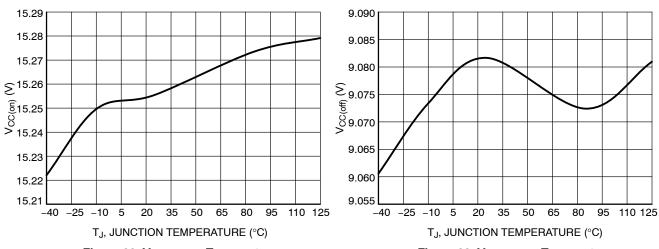

| Startup Threshold                                                                     | V <sub>CC</sub> increasing                                        | $V_{CC(on)}$                 | 14.5      | 15.2       | 15.9       |      |

| Minimum Operating Voltage After Turn-On                                               | V <sub>CC</sub> decreasing                                        | $V_{CC(off)}$                | 8.5       | 9.0        | 9.9        |      |

| Operating Hysteresis                                                                  | $V_{CC(on)} - V_{CC(off)}$                                        | V <sub>CC(HYS)</sub>         | 5.5       | -          | -          |      |

| Internal Latch/Logic Reset Level                                                      | V <sub>CC</sub> decreasing                                        | V <sub>CC(reset)</sub>       | 5.6       | 6.1        | 6.6        |      |

| V <sub>CC</sub> Level at Which I <sub>start1</sub> Transitions to I <sub>start2</sub> | V <sub>CC</sub> increasing, I <sub>HV</sub> = I <sub>start1</sub> | V <sub>CC(inhibit)</sub>     | 0.27      | 0.57       | 1.03       |      |

| V <sub>CC(off)</sub> to Drive Turn-Off Timeout Delay                                  | V <sub>CC</sub> decreasing                                        | t <sub>delay(Vcc_off)</sub>  | -         | 42         | 100        | μs   |

| Startup Delay                                                                         | Delay from $V_{CC(on)}$ to first LDRV pulse                       | <sup>t</sup> delay(start)    | 8         | 34         | 60         | μs   |

| Start-Up Time                                                                         | $C_{VCC}$ = 0.47 $\mu\text{F},~V_{CC}$ = 0 V to $V_{CC(on)}$      | t <sub>start-up</sub>        | =         | 2.53       | 6.5        | ms   |

| Minimum HV Pin Voltage for Rated Start-Up Current Source                              | $V_{CC} = V_{CC(on)} - 0.5 \text{ V}$                             | $V_{HV(MIN)}$                | -         | -          | 40         | ٧    |

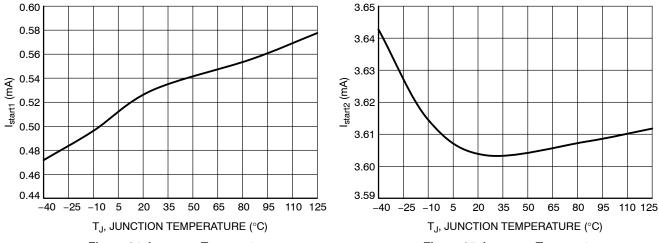

| Inhibit Current Sourced from V <sub>CC</sub> Pin                                      | V <sub>CC</sub> = 0 V                                             | I <sub>start1</sub>          | 0.342     | 0.540      | 0.794      | mA   |

| Start-Up Current Sourced from V <sub>CC</sub> Pin                                     | V <sub>CC</sub> = V <sub>CC(on)</sub> – 0.5 V                     | I <sub>start2</sub>          | 2.5       | 3.67       | 4.4        | mA   |

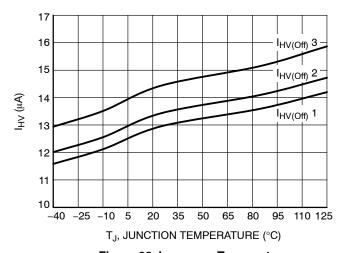

| Start-Up Circuit Off-State V <sub>hv</sub> = 162.5 V                                  |                                                                   | I <sub>HV(off1)</sub>        | _         | _          | 23         | μΑ   |

| Leakage Current                                                                       | $V_{hv} = 325 \text{ V}$                                          | I <sub>HV(off2)</sub>        | -         | _          | 24         |      |

|                                                                                       | V <sub>hv</sub> = 700 V                                           |                              | -         | _          | 25         |      |

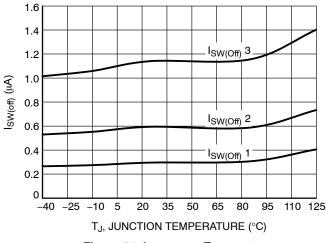

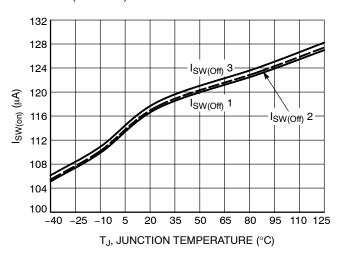

| Switch Pin Off-State Leakage Current                                                  | FLT = 0 V                                                         |                              |           |            |            | μΑ   |

| V <sub>hv</sub> = 162 V                                                               |                                                                   | I <sub>SW(off1)</sub>        | -         | _          | 1.5        |      |

|                                                                                       | V <sub>hv</sub> = 325 V                                           | I <sub>SW(off2)</sub>        | -         | _          | 2          |      |

|                                                                                       | V <sub>hv</sub> = 700 V                                           |                              | -         | _          | 4          |      |

| Switch Pin Active Current Draw V <sub>ATH</sub> = V <sub>DTH</sub> = 0 V              |                                                                   |                              |           |            |            | μΑ   |

|                                                                                       | V <sub>HV</sub> = 162 V                                           | I <sub>SW(on1)</sub>         | 92        | 117        | 152        |      |

|                                                                                       | V <sub>HV</sub> = 325 V                                           | I <sub>SW(on2)</sub>         | 92        | 118        | 153        |      |

|                                                                                       | V <sub>HV</sub> = 700 V                                           | I <sub>SW(on3)</sub>         | 92        | 119        | 154        |      |

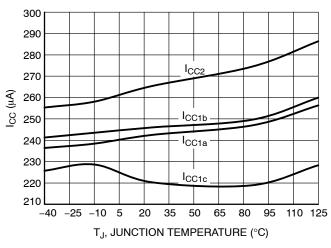

| Supply Current                                                                        |                                                                   |                              |           |            |            | mA   |

| FLT PIN OTP                                                                           | $V_{CC} = V_{CC(on)} - 0.5 V$                                     | I <sub>CC1A</sub>            | 0.14      | 0.24       | 0.32       |      |

| FLT PIN OVP                                                                           | $V_{CC} = V_{CC(on)} - 0.5 V$                                     | I <sub>CC1B</sub>            | 0.14      | 0.25       | 0.32       |      |

| Latch Fault                                                                           | $V_{CC} = V_{CC(on)} - 0.5 V$                                     | I <sub>CC1C</sub>            | 0.14      | 0.22       | 0.32       |      |

| Skip Mode (Excluding FB & FLT Current)                                                | V <sub>FB</sub> = 0 V                                             | I <sub>CC2</sub>             | 0.18      | 0.26       | 0.35       |      |

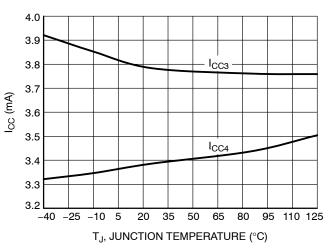

| Operating Current 500 kHz                                                             | $F_{sw} = 500 \text{ kHz}, A_{DRV} = L_{DRV} = 100 \text{ pF}$    | I <sub>CC3</sub>             | 2.25      | 4.00       | 6.17       |      |

| Operating Current 100 kHz                                                             | $F_{sw} = 100 \text{ kHz}, V_{CC} = 20 \text{ V}$                 | I <sub>CC4</sub>             | 2.0       | 4.0        | 6.0        |      |

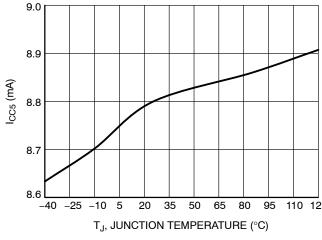

| Operating Current 500 kHz  V <sub>CC</sub> Overvoltage Protection Threshold           | F <sub>sw</sub> = 500 kHz, V <sub>CC</sub> = 10 V  Latched event  | I <sub>CC5</sub>             | 9<br>26.6 | 13<br>27.8 | 16<br>29.2 | V    |

| V <sub>CC</sub> Overvoltage Protection Timeout Delay                                  | Laterieu event                                                    | V <sub>CC(OVP)</sub>         | 40        | 63         | 90         |      |

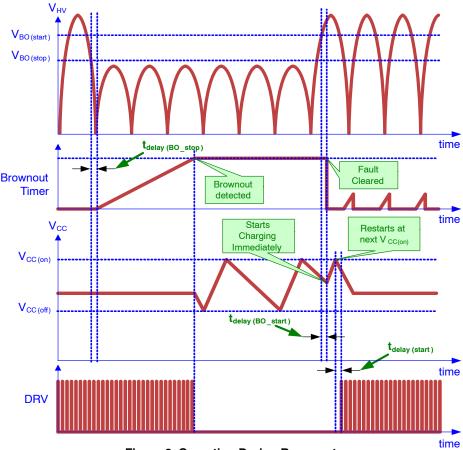

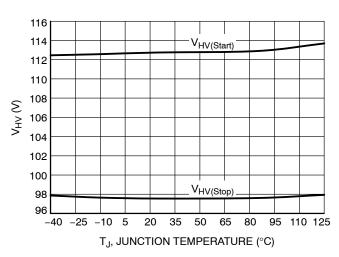

| BROWNOUT DETECTION                                                                    |                                                                   | t <sub>delay(Vcc_OVP)</sub>  | 40        | 03         | 90         | μS   |

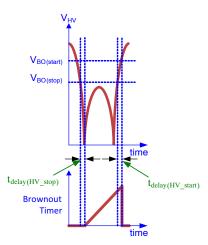

| System Start-Up Threshold                                                             | V <sub>HV</sub> increasing DC level                               | Vinueren                     | 109       | 113        | 118        | V    |

| Brownout Threshold                                                                    | V <sub>HV</sub> decreasing DC level                               | V <sub>HV(start)</sub>       | 92        | 98         | 104        | V    |

| Hysteresis                                                                            | THY GOODGOING DO 16761                                            | V <sub>HV(stop)</sub>        | 92        | 15         | -          | V    |

| Brownout Detection Blanking Time                                                      | V <sub>HV</sub> decreasing                                        | t <sub>HV(stop)</sub>        | 40        | 50         | 60         | ms   |

| System Start-Up Threshold Filter                                                      | Rising AC waveform                                                | t <sub>delay(HV start)</sub> | 30        | 70         | 110        | μs   |

| Brownout Detection Blanking Time Filter                                               | Falling AC waveform                                               | t <sub>delay(HV_start)</sub> | 243       | 396        | 551        | μs   |

| SOFT-START                                                                            | . samily no marolollii                                            | -delay(HV_Stop)              | 1 - 10    |            |            | μο   |

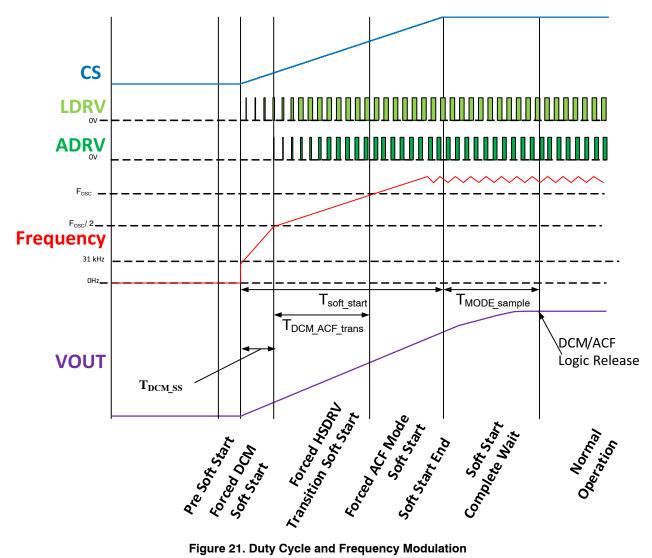

| Soft-Start Time                                                                       | Ramp time for CS from 0 to I <sub>limit</sub>                     | t <sub>soft-start</sub>      | 6         | 7.5        | 9          | ms   |

| Forced DCM Time at the Beginning of Soft Start                                        | RT = 33 k $\Omega$ (303 kHz)                                      | t <sub>DCM_SS</sub>          | 512       | 706        | 850        | μs   |

**Table 4. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC}$  = 12 V,  $V_{HV}$  = 120 V,  $V_{FLT}$  = open,  $V_{FB}$  = 2 V, RT1= 33 kΩ,  $V_{CS}$  = 0 V,  $C_{VCC}$  = 100 nF,  $A_{DRV}$  = 100 pF,  $L_{DRV}$  = 1.5 nF for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                      | Conditions                                                                                                                                                                                                                                      | Symbol                                                                              | Min                   | Тур                   | Max                   | Unit     |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------|--|

| SOFT-START                                           |                                                                                                                                                                                                                                                 |                                                                                     |                       | 1                     | 1                     | <u>I</u> |  |

| Time at which FB is Compared to DTH Threshold        | Time from the End of Soft Start to the ACF/DCM Assessment                                                                                                                                                                                       | t <sub>MODE_</sub> Sam                                                              | 13.5                  | 16                    | 18.5                  | ms       |  |

| OSCILLATOR                                           |                                                                                                                                                                                                                                                 |                                                                                     |                       |                       |                       |          |  |

| Minimum Oscillator Frequency in ACF Mode             | VSW = 15 V, RT = 100 k $\Omega$                                                                                                                                                                                                                 | F <sub>osc_ACF_100</sub>                                                            | 78                    | 100                   | 121                   | kHz      |  |

| Minimum Oscillator Frequency in ACF Mode             | VSW = 15 V, RT = 20 kΩ                                                                                                                                                                                                                          | F <sub>osc_ACF_500</sub>                                                            | 430                   | 532                   | 650                   | kHz      |  |

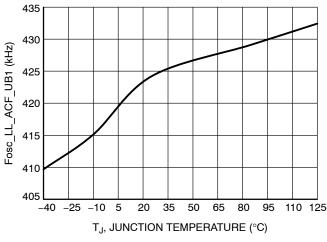

| Frequency Modulation Bounds                          | VSW = Modulated<br>RT = 100 kΩ, 4.20 * $F_{osc\_ACF}$<br>RT = 42.2 kΩ, 4.20 * $F_{osc\_ACF}$<br>(Note 3)                                                                                                                                        | F <sub>osc1_LL_</sub> ACF_UB1<br>F <sub>osc1_LL_</sub> ACF_UB2                      | 310<br>700            | 420<br>861            | 530<br>1000           | kHz      |  |

| Oscillator Frequency at Low/High<br>Line in DCM Mode | RT = 20 k $\Omega$ , FB = DCM to ACF Trip Threshold –5 mV                                                                                                                                                                                       | F <sub>osc_DCM_2</sub>                                                              | 200                   | 260                   | 320                   | kHz      |  |

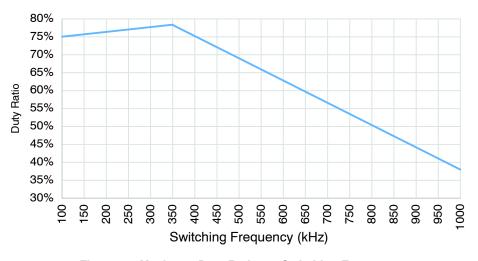

| Maximum Duty Cycle  Minimum Off Time for ADRV        | $F_{osc} = 100 \text{ kHz}, \text{ RT} = 100 \text{ k}\Omega$ $F_{osc} = 205 \text{ kHz}, \text{RT} = 49.9 \text{ k}\Omega$ $F_{osc} = 500 \text{ kHz}, \text{ RT} = 20 \text{ k}\Omega, \text{ T}_{min\_OFF}$ Measured at 50% of Drive Voltage | D <sub>Max_100</sub> D <sub>Max_400</sub> D <sub>Max_500</sub> T <sub>min_OFF</sub> | 53<br>60<br>53<br>365 | 75<br>79<br>69<br>582 | 96<br>92<br>88<br>808 | %<br>ns  |  |

|                                                      | From Falling Edge to Rising Edge of LDRV                                                                                                                                                                                                        |                                                                                     |                       |                       |                       |          |  |

| TRANSITION MODE                                      |                                                                                                                                                                                                                                                 |                                                                                     | ı                     | 1                     | 1                     | T        |  |

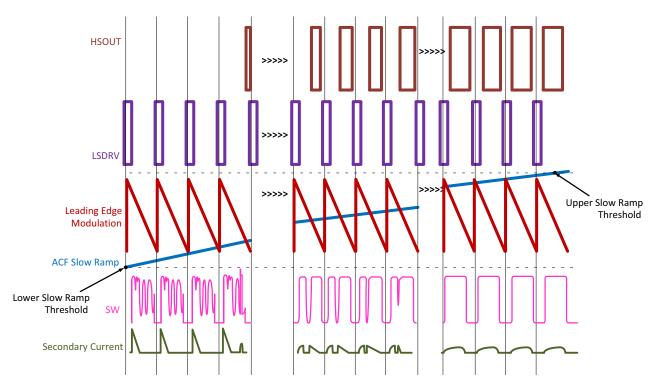

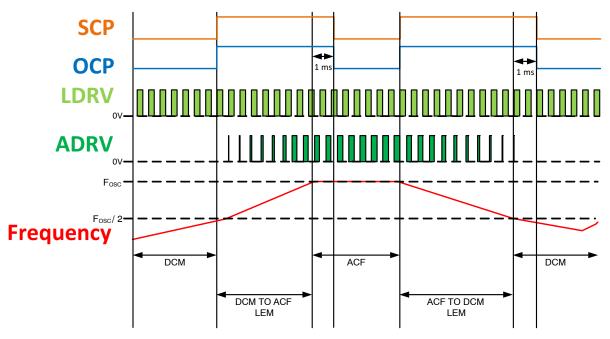

| ACF to DCM Transition                                | ADRV LEM Soft Stop Time<br>S02<br>G03, G04                                                                                                                                                                                                      | tACF_DCM_TranstACF_DCM_Trans1                                                       | -<br>1                | 0<br>0.506            | _<br>1                | ms       |  |

| DCM to ACF Transition                                | ADRV LEM Soft Start Time<br>S02, G03, G04                                                                                                                                                                                                       | t <sub>DCM_ACF_Trans1</sub>                                                         | 3.5                   | 4                     | 4.7                   | ms       |  |

| DCM to ACF Blanking Time after Transition            | Time the DCM to ACF Comparator is Blanked                                                                                                                                                                                                       | t <sub>DCM_ACF_HOLD</sub>                                                           | 0.9                   | 1                     | 1.1                   | ms       |  |

| ACF to DCM Level Trip Time                           | Time the ACF to DCM Comparator must be High before Transition                                                                                                                                                                                   | tacf_dcm_hold                                                                       | 11                    | 12                    | 17                    | ms       |  |

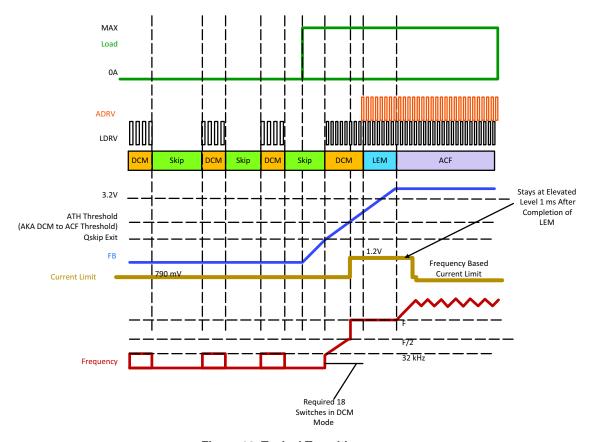

| Required DCM Cycles Before ACF                       | DCM Operation                                                                                                                                                                                                                                   | NDCM                                                                                | 18                    |                       |                       | #        |  |

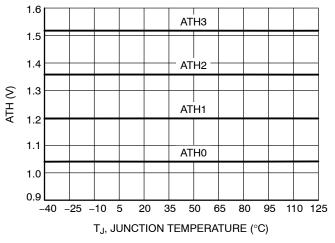

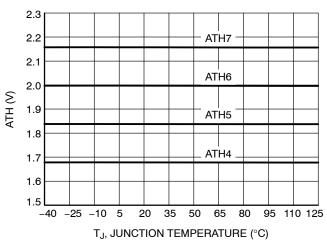

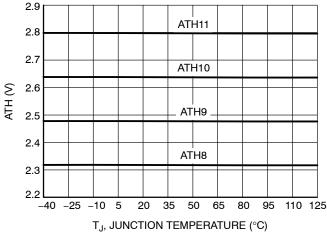

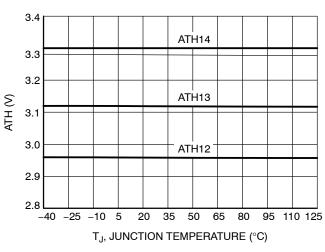

| ATH FUNCTION                                         |                                                                                                                                                                                                                                                 |                                                                                     |                       |                       |                       |          |  |

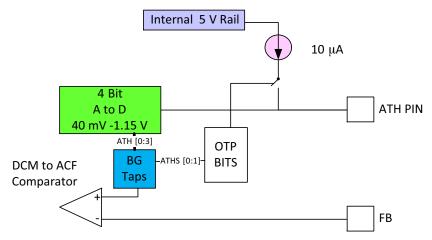

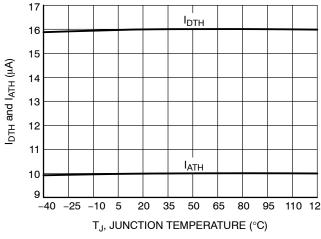

| Current Sourced From ATH                             | ATH = 2 V                                                                                                                                                                                                                                       | I <sub>ATH</sub>                                                                    | 9.4                   | 10                    | 10.5                  | μΑ       |  |

| ATH BIN 0                                            | 50 mV                                                                                                                                                                                                                                           | ATH_BIN0                                                                            | 1.00                  | 1.04                  | 1.07                  | _        |  |

| ATH BIN 1                                            | 180 mV                                                                                                                                                                                                                                          | ATH_BIN1                                                                            | 1.16                  | 1.20                  | 1.23                  | V        |  |

| ATH BIN 2                                            | 220 mV                                                                                                                                                                                                                                          | ATH_BIN2                                                                            | 1.326                 | 1.36                  | 1.394                 | V        |  |

| ATH BIN 3                                            | 270 mV                                                                                                                                                                                                                                          | ATH_BIN3                                                                            | 1.482                 | 1.52                  | 1.558                 | V        |  |

| ATH BIN 4                                            | 330 mV                                                                                                                                                                                                                                          | ATH_BIN4                                                                            | 1.638                 | 1.68                  | 1.722                 | V        |  |

| ATH BIN 5                                            | 390 mV                                                                                                                                                                                                                                          | ATH_BIN5                                                                            | 1.794                 | 1.84                  | 1.886                 | V        |  |

| ATH BIN 6                                            | 460 mV                                                                                                                                                                                                                                          | ATH_BIN6                                                                            | 1.95                  | 2                     | 2.05                  | ٧        |  |

| ATH BIN 7                                            | 540 mV                                                                                                                                                                                                                                          | ATH_BIN7                                                                            | 2.106                 | 2.16                  | 2.214                 | ٧        |  |

| ATH BIN 8                                            | 630 mV                                                                                                                                                                                                                                          | ATH_BIN8                                                                            | 2.262                 | 2.32                  | 2.378                 | V        |  |

| ATH BIN 9                                            | 740 mV                                                                                                                                                                                                                                          | ATH_BIN9                                                                            | 2.418                 | 2.48                  | 2.542                 | V        |  |

| ATH BIN 10                                           | 870 mV                                                                                                                                                                                                                                          | ATH_BIN10                                                                           | 2.574                 | 2.64                  | 2.706                 | V        |  |

| ATH BIN 11                                           | 1.02 V                                                                                                                                                                                                                                          | ATH_BIN11                                                                           | 2.73                  | 2.8                   | 2.87                  | V        |  |

| ATH BIN 12                                           | 1.19 V                                                                                                                                                                                                                                          | ATH_BIN12                                                                           | 2.886                 | 2.96                  | 3.034                 | V        |  |

| ATH BIN 13                                           | 1.39 V                                                                                                                                                                                                                                          | ATH_BIN13                                                                           | 3.042                 | 3.12                  | 3.198                 | V        |  |

**Table 4. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC}$  = 12 V,  $V_{HV}$  = 120 V,  $V_{FLT}$  = open,  $V_{FB}$  = 2 V, RT1= 33 kΩ,  $V_{CS}$  = 0 V,  $C_{VCC}$  = 100 nF,  $A_{DRV}$  = 100 pF,  $L_{DRV}$  = 1.5 nF for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                                                        | Conditions                                                         | Symbol                         | Min   | Тур   | Max   | Unit  |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|-------|-------|-------|-------|

| ATH FUNCTION                                                                           |                                                                    | •                              | ı     |       |       |       |

| ATH BIN 14                                                                             | 1.63 V                                                             | ATH BIN14                      | 3.198 | 3.28  | 3.362 | V     |

| DTH FUNCTION                                                                           |                                                                    | _                              | 1     |       |       |       |

| DTH Pin Pullup Current                                                                 | RT = 100 kΩ                                                        | I <sub>DTH</sub>               | 15.25 | 16.0  | 16.75 | μΑ    |

| DTH Trip Voltage                                                                       | VDTH = 500 mV FB Decreasing                                        | V <sub>FB_DTH1</sub>           | 0.45  | 0.50  | 0.55  | V     |

|                                                                                        | VDTH = 1.5 V FB Decreasing                                         | V <sub>FB_DTH2</sub>           | 1.45  | 1.5   | 1.55  |       |

|                                                                                        | VDTH = 3.0 V FB Decreasing                                         | V <sub>FB_DTH3</sub>           | 2.95  | 3.0   | 3.05  |       |

| SLOPE COMPENSATION                                                                     | I 5 11 405 1 1 50444 1                                             | T =                            |       |       |       |       |

| Duty Cycle at which Ramp<br>Compensation Begins                                        | Both ACF and DCM Mode                                              | D <sub>Slope_Start</sub>       | 32    | 41.2  | 50    | %     |

| Slope of Compensating Ramp                                                             |                                                                    | S <sub>RAMP</sub>              | 110   | 143   | 190   | mV/μs |

| DCM MODE FREQUENCY FOLDBACK                                                            |                                                                    |                                |       |       |       |       |

| Feedback Voltage Below which CS<br>Detected Peak Current is Frozen<br>(at the FB Pin)  |                                                                    | V <sub>FB</sub> (lpk_freeze)_0 | 740   | 792   | 850   | mV    |

| CS Pin Peak Current Floor Threshold                                                    | RT = 100 kΩ                                                        | V <sub>CS(lpk_freeze)_0</sub>  | 160   | 220   | 270   | mV    |

| Set when FB is Lower than VFB(lpk_freeze)                                              | RT = 33.3 kΩ                                                       | V <sub>CS(Ipk_freeze)_1</sub>  | 280   | 349   | 410   |       |

|                                                                                        | RT = 20 kΩ                                                         | V <sub>CS(lpk_freeze)_2</sub>  | 390   | 475   | 560   |       |

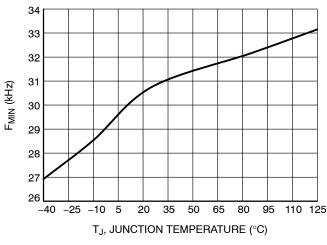

| Minimum Oscillator Frequency                                                           | Operating Mode = DCM,<br>V <sub>FB</sub> = 400 mV                  | F <sub>osc(min)</sub>          | 20.5  | 30    | 40    | kHz   |

| Oscillator Frequency at Low/High<br>Line in DCM Mode                                   | RT = 20 k $\Omega$<br>FB = DCM to ACF Trip<br>Threshold –5 mV      | F <sub>osc_DCM_2</sub>         | 220   | 260   | 305   | kHz   |

| Feedback Voltage at which Minimum<br>Switching Frequency is Reached<br>(at the FB Pin) | Fsw = F <sub>osc(min)</sub>                                        | V <sub>Fosc(min)</sub>         | 370   | 400   | 440   | mV    |

| Feedback Voltage at which Skip Cycle<br>Comparator Trips (at the FB Pin)               | Feedback Falling                                                   | V <sub>FB(skip)</sub>          | 370   | 400   | 440   | mV    |

| Skip Cycle Comparator Hysteresis                                                       | Feedback Rising (Positive)                                         | V <sub>FB(skip)_hys</sub>      | 38    | 66    | 94    | mV    |

| Skip Wakeup Time                                                                       | FB > (V <sub>FB(skip)</sub> + V <sub>FB(skip)_hys</sub> + 100 mV)  | T <sub>Skip_wake</sub>         | 14    | 24    | 34    | μs    |

| FEEDBACK                                                                               |                                                                    | •                              |       |       |       |       |

| Open Pin Voltage                                                                       |                                                                    | V <sub>FB(open)</sub>          | 4.89  | 5.0   | 5.1   | V     |

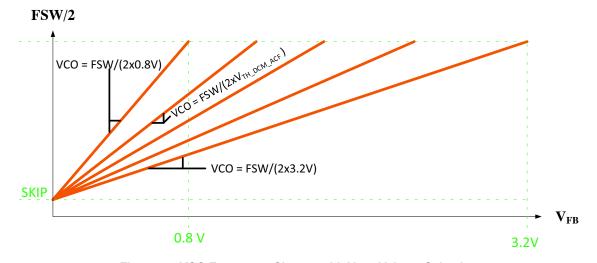

| VFB to Internal Current Set Point<br>Division Ratio                                    | VFB = 4 V                                                          | K <sub>FB</sub>                | 3.75  | 4.00  | 4.20  |       |

| Internal Pull-Up Resistor                                                              | V <sub>FB</sub> = 0.4 V                                            | R <sub>RFB_0</sub>             | 80    | 100   | 120   | kΩ    |

| Internal Pull-Up Current                                                               | V <sub>FB</sub> = 0.4 V                                            | I <sub>FB 0</sub>              | 83    | 99    | 114   | μΑ    |

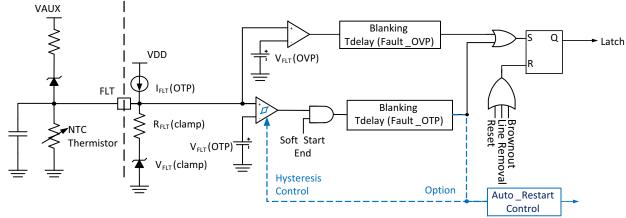

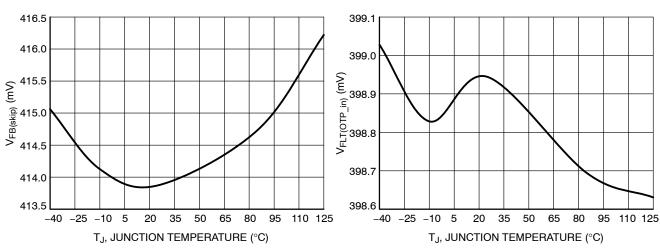

| FLT PROTECTION                                                                         |                                                                    | <del>-</del>                   | 1     |       |       |       |

| Overvoltage Protection (OVP) Threshold                                                 | V <sub>FLT</sub> Increasing                                        | V <sub>FLT (OVP)</sub>         | 2.9   | 3.0   | 3.1   | V     |

| OVP Detection Delay                                                                    | V <sub>FLT</sub> Increasing                                        | t <sub>delay(OVP)</sub>        | 21    | 35    | 49    | μs    |

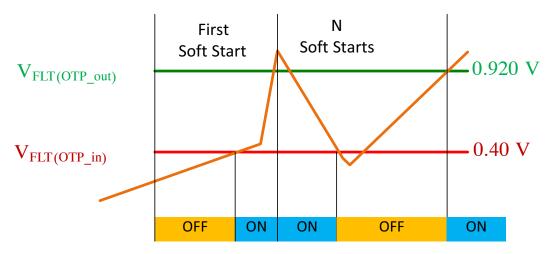

| Over Temperature Protection (OTP)<br>Threshold                                         | V <sub>FLT</sub> Decreasing (Note 2)                               | V <sub>FLT(OTP_in)</sub>       | 0.35  | 0.40  | 0.45  | V     |

| Over Temperature Protection Exiting Threshold                                          | V <sub>FLT</sub> Increasing (Note 2)                               | V <sub>FLT</sub> (OTP_out)     | 0.870 | 0.937 | 0.990 | ٧     |

| Over Temperature Protection Exiting<br>Threshold on Startup                            | V <sub>FLT</sub> Increasing with first V <sub>CC</sub><br>Power on | V <sub>FLT</sub> (OTP_out_1st) | 0.370 | 0.418 | 0.470 | ٧     |

| OTP Detection Delay                                                                    | V <sub>FLT</sub> Decreasing                                        | t <sub>delay(OTP)</sub>        | 21    | 33    | 49    | μs    |

**Table 4. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC}$  = 12 V,  $V_{HV}$  = 120 V,  $V_{FLT}$  = open,  $V_{FB}$  = 2 V, RT1= 33 kΩ,  $V_{CS}$  = 0 V,  $C_{VCC}$  = 100 nF,  $A_{DRV}$  = 100 pF,  $L_{DRV}$  = 1.5 nF for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                                                       | Conditions                                                                                                          | Symbol                                                                                                                                                                                               | Min                                                  | Тур                                                  | Max                                                         | Unit |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|------|

| FLT PROTECTION                                                                        |                                                                                                                     |                                                                                                                                                                                                      |                                                      |                                                      |                                                             |      |

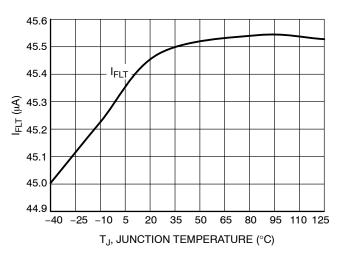

| OTP Pull-Up Current Source                                                            | $V_{FLT} = V_{FLT (OTP_in)} + 0.2 V$                                                                                | I <sub>FLT(OTP)</sub>                                                                                                                                                                                | 42.5                                                 | 45.5                                                 | 48.5                                                        | μΑ   |

| FLT Input Clamp Voltage                                                               |                                                                                                                     | V <sub>FLT (clamp)</sub>                                                                                                                                                                             | 1.69                                                 | 1.75                                                 | 1.90                                                        | V    |

| FLT Input Clamp Series Resistor                                                       |                                                                                                                     | R <sub>FLT (clamp)</sub>                                                                                                                                                                             | 1.26                                                 | 1.58                                                 | 1.90                                                        | kΩ   |

| OVER POWER PROTECTION                                                                 |                                                                                                                     | , ,,                                                                                                                                                                                                 |                                                      | ı                                                    |                                                             |      |

| OPP Current GM                                                                        | V <sub>HV</sub> _peak = 123 V<br>V <sub>HV</sub> _peak = 346 V                                                      | HV_GM                                                                                                                                                                                                | 112                                                  | 188                                                  | 265                                                         | nS   |

| HV Update Time                                                                        | Guaranteed by Design                                                                                                | T <sub>UPDATE</sub>                                                                                                                                                                                  |                                                      | 30.7                                                 |                                                             | ms   |

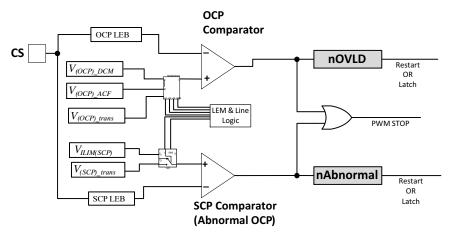

| CURRENT LIMIT PROTECTION                                                              |                                                                                                                     |                                                                                                                                                                                                      |                                                      |                                                      |                                                             |      |

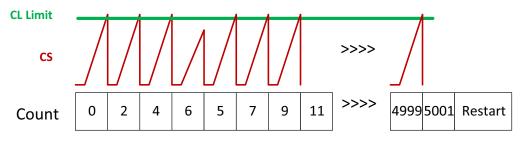

| Count of OCP Events Before Fault is Declared                                          | V <sub>CS</sub> > V <sub>ILIM(OCP)</sub>                                                                            | N <sub>OCP</sub>                                                                                                                                                                                     |                                                      | 5                                                    |                                                             | k #  |

| Count of SCP Events Before Fault is Declared                                          | V <sub>CS</sub> > V <sub>ILIM(SCP)</sub>                                                                            | N <sub>SCP</sub>                                                                                                                                                                                     | 5                                                    | 5                                                    | 5                                                           | #    |

| Restart Timer for Auto – Recovery                                                     |                                                                                                                     | T <sub>auto_retry</sub>                                                                                                                                                                              | 1460                                                 | 1600                                                 | 1755                                                        | ms   |

| CS Pin Internal Pull-up Current                                                       | V <sub>CS</sub> = 0.8 V                                                                                             | I <sub>bias</sub>                                                                                                                                                                                    | 0.7                                                  | 1                                                    | 1.3                                                         | μΑ   |

| CURRENT SENSE                                                                         |                                                                                                                     |                                                                                                                                                                                                      |                                                      | -                                                    | -                                                           |      |

| Cycle by Cycle Current Limit Threshold<br>Over Current Protection (OCP)               | DCM threshold                                                                                                       | V <sub>ILIM(OCP)_DCM</sub>                                                                                                                                                                           | 740                                                  | 785                                                  | 825                                                         | mV   |

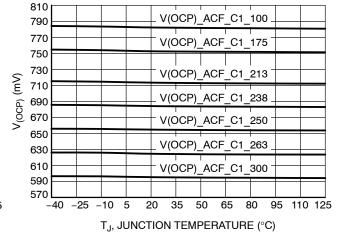

| Cycle by Cycle Current Limit Threshold ACF                                            | FSW = 166 kHz<br>FSW = 175 kHz<br>FSW = 213 kHz<br>FSW = 238 kHz<br>FSW = 250 kHz<br>FSW = 263 kHz<br>FSW = 300 kHz | V(OCP)_ACFC1_100<br>V(OCP)_ACFC1_166<br>V(OCP)_ACFC1_175<br>V(OCP)_ACFC1_213<br>V(OCP)_ACFC1_238<br>V(OCP)_ACFC1_250<br>V(OCP)_ACFC1_263<br>V(OCP)_ACFC1_263<br>V(OCP)_ACFC1_300<br>V(OCP)_ACFC1_400 | 740<br>740<br>710<br>670<br>635<br>610<br>580<br>550 | 785<br>785<br>750<br>710<br>680<br>650<br>620<br>590 | 825<br>825<br>795<br>750<br>725<br>688<br>660<br>630<br>630 | mV   |

| Cycle by Cycle Current Limit Threshold<br>Over Current Protection (OCP) During<br>LEM | In Transition Mode<br>(ACF to DCM or DCM to ACF)                                                                    | V <sub>ILIM(OCP)_Trans</sub>                                                                                                                                                                         | 1.12                                                 | 1.19                                                 | 1.26                                                        | V    |

| Short Circuit Protection (SCP) Threshold                                              | Both ACF and DCM                                                                                                    | V <sub>ILIM(SCP)</sub>                                                                                                                                                                               | 1.12                                                 | 1.19                                                 | 1.26                                                        | V    |

| Short Circuit Protection (SCP) Threshold During LEM                                   | In Transition Mode<br>(ACF to DCM or DCM to ACF)                                                                    | VI <sub>LIM(SCP)_Trans</sub>                                                                                                                                                                         | 1.31                                                 | 1.391                                                | 1.48                                                        | V    |

| OCP Leading Edge Blanking Delay                                                       | S02<br>G03, G04                                                                                                     | T <sub>LEB(OCP)0</sub><br>T <sub>LEB(OCP)1</sub>                                                                                                                                                     |                                                      | 195<br>121                                           | 230<br>141                                                  | ns   |

| SCP Leading Edge Blanking Delay                                                       | S02<br>G03, G04                                                                                                     | T <sub>LEB(SCP)0</sub><br>T <sub>LEB(SCP)1</sub>                                                                                                                                                     |                                                      | 147<br>38                                            | 172<br>83                                                   | ns   |

| OCP Propagation Delay                                                                 | CS ramped from 0 to 1 V at dv/dt = 20 V/µs to LDRV 8.5 V falling edge                                               | T <sub>PROP(OCP)</sub>                                                                                                                                                                               |                                                      | 38                                                   | 78                                                          | ns   |

| SCP Propagation Delay                                                                 | CS ramped from 0 to 1.6 V at dv/dt = 20 V/µs to LDRV 8.5 V falling edge                                             | T <sub>PROP(SCP)</sub>                                                                                                                                                                               |                                                      | 43                                                   | 78                                                          | ns   |

| CS Switch Discharge Resistance                                                        | Measured with 5 mA Pull Up Current                                                                                  | R <sub>DS(ON)_CS</sub>                                                                                                                                                                               |                                                      |                                                      | 80                                                          | Ω    |

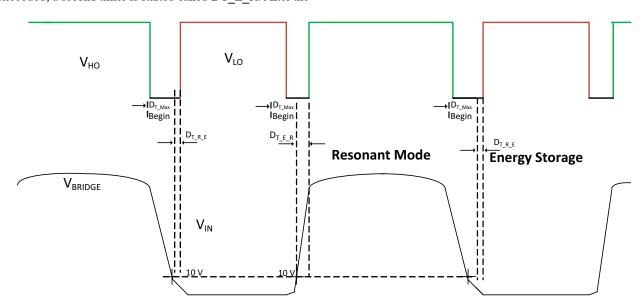

| DEAD TIME MANAGEMENT IN ACF MOD                                                       | E                                                                                                                   |                                                                                                                                                                                                      |                                                      |                                                      |                                                             |      |

| Resonant Mode to Energy Storage<br>Voltage Threshold                                  | Falling Edge of SW Pin Voltage                                                                                      | D <sub>T_R_E_VTH</sub>                                                                                                                                                                               | 8                                                    | 9.6                                                  | 10.7                                                        | V    |

Table 4. ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC}$  = 12 V,  $V_{HV}$  = 120 V,  $V_{FLT}$  = open,  $V_{FB}$  = 2 V, RT1= 33 k $\Omega$ ,  $V_{CS}$  = 0 V,  $C_{VCC}$  = 100 nF,  $A_{DRV}$  = 1.0 pF,  $L_{DRV}$  = 1.5 nF for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                                                                                             | Conditions                                                                                                  | Symbol                                               | Min               | Тур               | Max               | Unit |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|-------------------|-------------------|------|

| DEAD TIME MANAGEMENT IN ACF MOD                                                                                             | E                                                                                                           |                                                      |                   |                   |                   |      |

| Energy Storage to Resonant Mode<br>Voltage Threshold                                                                        | Rising Edge of SW Pin Voltage                                                                               | D <sub>T_E_R_VTH</sub>                               | 9                 | 9.6               | 11                | V    |

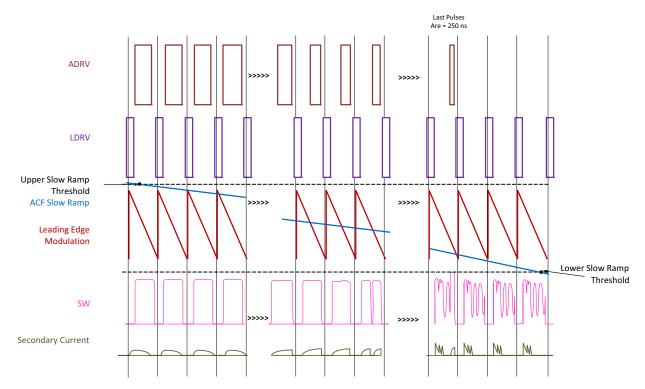

| Dead Time from Energy Storage to<br>Resonant Mode                                                                           | $V_{SW} > D_{T\_E\_R\_VTH}$ to ADRV 2.5 V                                                                   | D <sub>T_E_R1</sub>                                  | 20                | 46                | 76                | ns   |

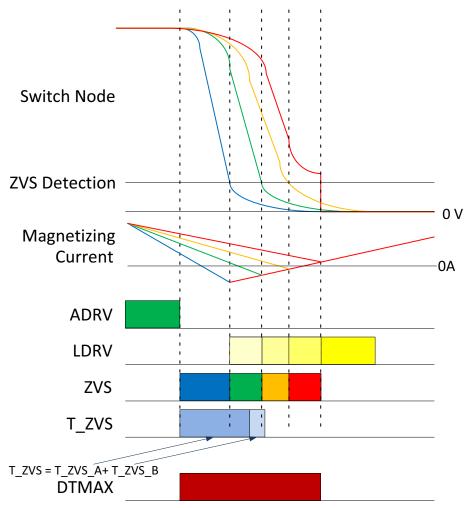

| Maximum Dead Time (Timer Starts at ADRV Falling Edge and is Reset when D <sub>T_R_E</sub> Expires)                          | S02<br>G03, G04                                                                                             | D <sub>T_Max_1</sub><br>D <sub>T_Max_2</sub>         | 380<br>229        | 449<br>276        | 515<br>320        | ns   |

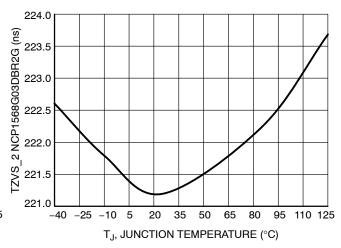

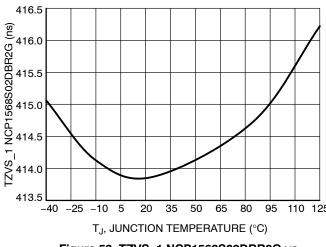

| ZVS Reference Time for Frequency<br>Modulation (Timer Starts at ADRV Falling<br>Edge and is Reset when D <sub>T_Max</sub> ) | S02<br>G03<br>G04                                                                                           | T_ZVS_1<br>T_ZVS_2<br>T_ZVS_3                        | 350<br>188<br>228 | 415<br>221<br>261 | 462<br>300<br>340 | ns   |

| LOW SIDE DRIVER                                                                                                             |                                                                                                             |                                                      |                   |                   |                   |      |

| LDRV Rise Time                                                                                                              | $V_{LDRV} = 2.4 \text{ V to } 8.5 \text{ V}$ $V_{CC} = V_{CC(off)} + 0.5 \text{ V}$ $V_{CC} = 18 \text{ V}$ | T <sub>LS_rise</sub> T <sub>LS_rise</sub> (Clamp)    | 2<br>2            | 10.7<br>10.6      | 20<br>20          | ns   |

| LDRV Fall Time                                                                                                              | $V_{LDRV} = 8.5 \text{ V to } 2.4 \text{ V}$ $V_{CC} = V_{CC(off)} + 0.5 \text{ V}$ $V_{CC} = 18 \text{ V}$ | T <sub>LS_fall</sub><br>T <sub>LS_fall</sub> (Clamp) | 1<br>1            | 6.5<br>5.9        | 15<br>15          | ns   |

| LDRV Source Current                                                                                                         | V <sub>CC</sub> = V <sub>CC(off)</sub> + 0.5 V<br>V <sub>CC</sub> = 18 V                                    | I <sub>LS_src</sub>                                  |                   | 0.855<br>0.847    |                   | Α    |

| LDRV Sink Current                                                                                                           | V <sub>CC</sub> = V <sub>CC(off)</sub> + 0.5 V<br>V <sub>CC</sub> = 18 V                                    | I <sub>LS_snk</sub>                                  |                   | 1.41<br>1.55      |                   | Α    |

| LDRV Clamp Voltage                                                                                                          | $V_{CC}$ = 18 V, $R_{DRV}$ = 10 k $\Omega$                                                                  | V <sub>LDRV(Clamp)</sub>                             | 10.5              | 11.75             | 12.6              | V    |

| ADRV                                                                                                                        |                                                                                                             |                                                      |                   |                   |                   | -    |

| ADRV Rise Time                                                                                                              | V <sub>ADRV</sub> = 1V to 3V with 920 pF Load                                                               | T <sub>ADRV_rise</sub>                               | 15                | 28.5              | 49                | ns   |

| ADRV Fall Time                                                                                                              | V <sub>ADRV</sub> = 3V to 1V with 920 pF Load                                                               | T <sub>ADRV_fall</sub>                               | 7                 | 12.2              | 21                | ns   |

| ADRV Source Current                                                                                                         | V <sub>ADRV</sub> = 2.5 V                                                                                   | l <sub>ADRV_SRC</sub>                                |                   | 65                |                   | mA   |

| ADRV Sink Current                                                                                                           | V <sub>ADRV</sub> = 2.5 V                                                                                   | ladrv_snk                                            |                   | 150               |                   | mA   |

| Minimum Pulse Width Allowed                                                                                                 |                                                                                                             | MIN_ <sub>PW_GD</sub>                                | 196               | 234               | 280               | ns   |

| ADRV Clamp Voltage                                                                                                          | R <sub>DRV</sub> = 10 kΩ                                                                                    | V <sub>ADRV(Clamp)</sub>                             | 4.25              | 4.75              | 5.25              | V    |

| THERMAL SHUTDOWN                                                                                                            |                                                                                                             |                                                      |                   | _                 |                   |      |

| Thermal Shutdown                                                                                                            | Temperature Increasing                                                                                      | T <sub>SHDN</sub>                                    |                   | 150               |                   | °C   |