# **3.2 A Dual Input, Switch Mode Charger with Power Path**

#### Description

The FAN5451x family of chargers includes an  $I^2C$  controlled 3.2 A USB-compliant switch-mode charger.

To facilitate fast system startup, the IC includes an optimized Power Path circuit which also accurately measures battery currents during charging and provides low impedance during discharge.

The charging parameters and operating modes are programmable through an I<sup>2</sup>C Interface. Charge status is reported back to the host through the I<sup>2</sup>C port and the / STAT pin.

The FAN5451x provides battery charging in three modes: Pre-Charge (IPP), Constant Current (CC) and Constant Voltage (CV). The charger can automatically restart the charge cycle when the battery falls below a restart voltage threshold. If the input source is removed, the IC enters a high-impedance mode, blocking battery current from leaking to either input.

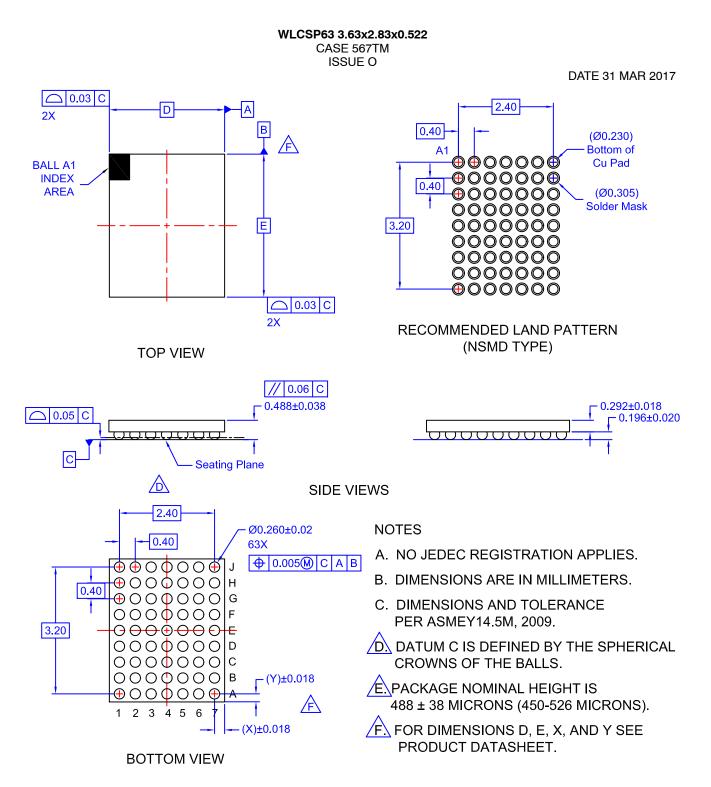

The FAN5451x is available in a 63-bump, 0.4 mm pitch WLCSP package.

#### Features

- Fully Integrated, High–Efficiency Charger for Single–Cell Li–Ion and Li–Polymer Battery Packs

- Power Path Circuit ensures Fast System Startup with a Dead Battery

- 95% Charge Efficiency

- Charge Current Programmable up to 3.2 A

- 10 mV Float Voltage Accuracy

- ±5% Charge Current Regulation Accuracy

- 5 V, 1.5 A Boost Mode for USB OTG

- 22 V DC Withstand Voltage on VBUS

- 13.25 V Maximum Input Operating Voltage

- -2 V Input Reverse Polarity Protection

#### Benefits

- Secondary Input for Wireless Charging

- Dynamic Input Voltage Control (DIVC) for Operation with Weak Adapters

- USB BC1.2 Compatible

- Programmable 10 mA LDO

- Programmable Safety Timer with Reset Control

- Pin Configurable Ship Mode prevents Battery Discharge to System Load

#### Applications

- Smart Phones

- Tablets

# **ON Semiconductor®**

www.onsemi.com

# ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

- Pin or Software Configurable Hardware Reset for Quick System Restart

- Battery Temperature Sensing Ensures Safe-To-Charge Operation (JEITA)

- Thermal Shutdown and Programmable Thermal Regulation

- High–Speed I<sup>2</sup>C Interface (3.4 Mb/s) with Fast Mode Plus Compatibility

- e-Books

- Li Ion Powered Devices

#### **Table 1. ORDERING INFORMATION**

| Part Number   | Package                                           | Packing Method |

|---------------|---------------------------------------------------|----------------|

| FAN54510AUCX  | 63 - Bump, Wafer-Level Chip_Scale Package (WLCSP) | Tape and Reel  |

| FAN54511AUCX  | 0.4 mm Pitch                                      |                |

| FAN54511APUCX |                                                   |                |

| FAN54512AUCX  |                                                   |                |

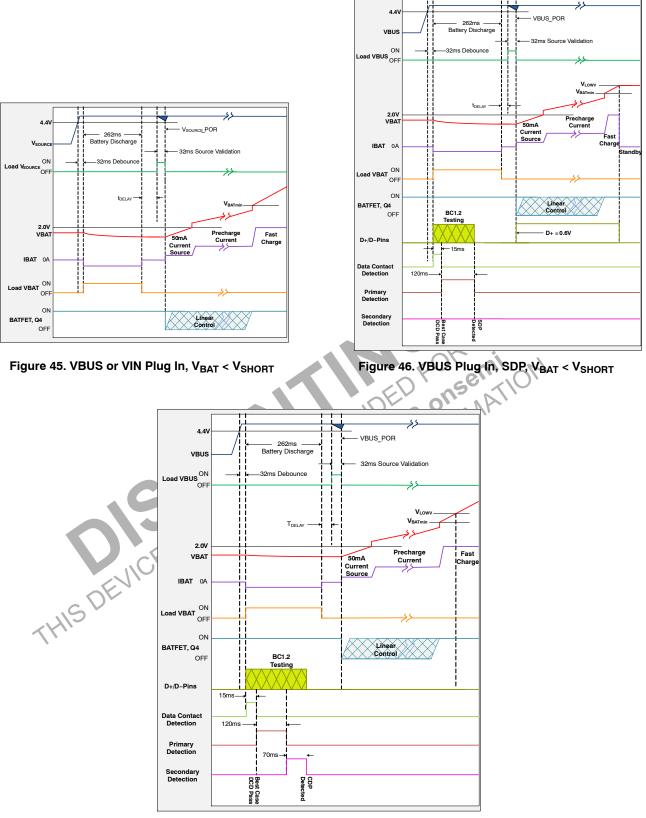

| FAN54513AUCX  |                                                   |                |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **Table 2. DEVICE ORDERING INFORMATION**

| Part Number           | Slave<br>Address | PN Bits:<br>IC_INFO[<br>5:3] | BC1.2<br>Detection | BC1.2 SDP<br>I <sub>BUS</sub><br>Current<br>Limit | BC1.2<br>CDP/DCP<br>I <sub>BUS</sub><br>Current<br>Limit | ILIM<br>Pin<br>Control | I <sub>BUS</sub> Current<br>Limit<br>(ILIM Pin =<br>HIGH) | I <sub>BUS</sub> Current<br>Limit<br>(ILIM Pin =<br>LOW) |

|-----------------------|------------------|------------------------------|--------------------|---------------------------------------------------|----------------------------------------------------------|------------------------|-----------------------------------------------------------|----------------------------------------------------------|

| FAN54510A<br>(Note 1) | 1101011_         | 000                          | ON<br>(D+, D–)     | 2 min.<br>@500 mA                                 | Safety<br>Timer<br>@1500 mA                              | OFF                    | NA                                                        | N/A                                                      |

| FAN54511A             | 1101011_         | 001                          | OFF<br>(GPO1,GPO2) | N/A                                               | N/A                                                      | ON                     | 500 mA                                                    | 1500 mA                                                  |

| FAN54511AP            | 1101010_         | 001                          | OFF<br>(GPO1,GPO2) | N/A                                               | N/A                                                      | ON                     | 500 mA                                                    | 1500 mA                                                  |

| FAN54512A<br>(Note 1) | 1101011_         | 010                          | ON<br>(D+, D–)     | 45 min.<br>@100 mA                                | Safety<br>Timer<br>@1500 mA                              | OFF                    | N/A                                                       | N/A                                                      |

| FAN54513A             | 1101011_         | 011                          | OFF<br>(GPO1,GPO2) | N/A                                               | N/A                                                      | ON                     | 100 mA                                                    | 1500 mA                                                  |

| 1. Contact ON for     | r these options. | REP REP                      | OFF<br>(GPO1,GPO2) | NTACE                                             | 04                                                       |                        |                                                           |                                                          |

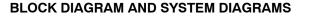

# STATE DIAGRAMS

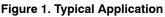

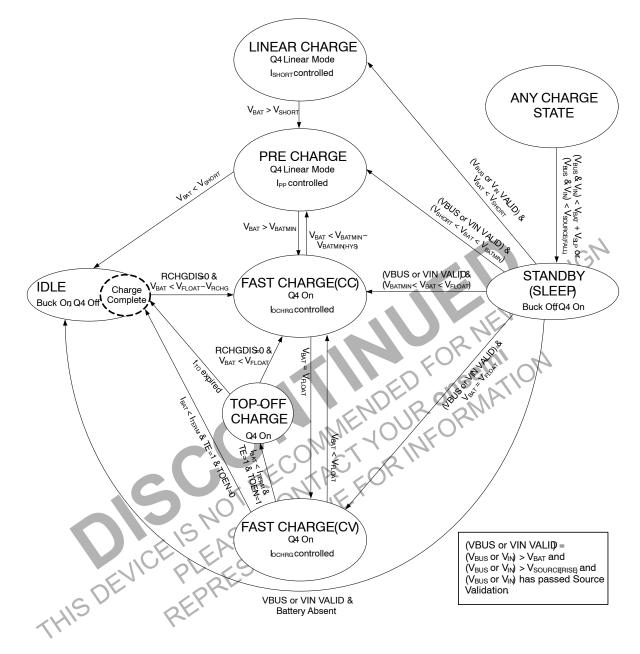

Figure 2. Charger State Diagram: State and Mode Transitions

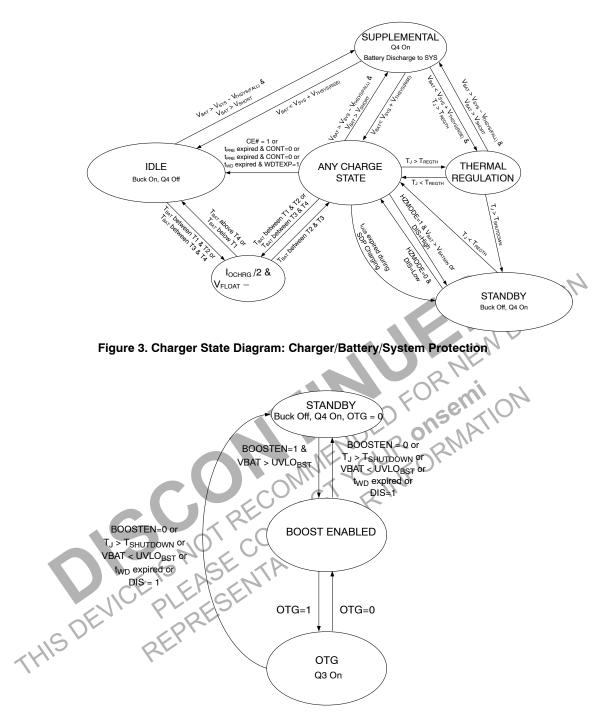

Figure 4. Boost State Diagram

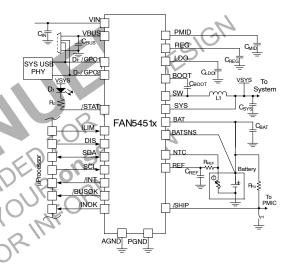

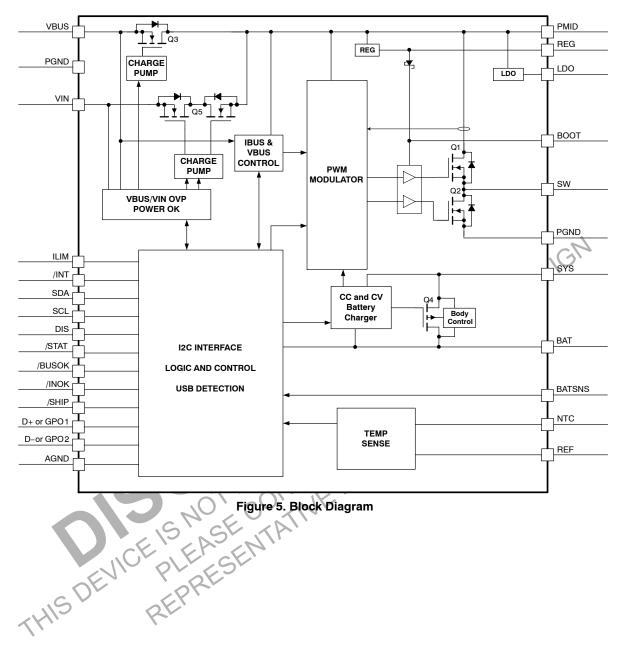

Figure 7. FAN54511A, FAN54511AP, FAN54513A System Diagram

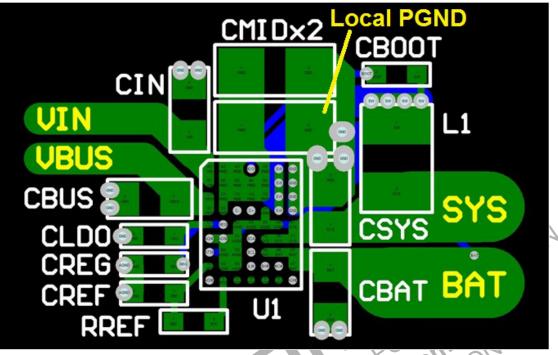

#### **RECOMMENDED EXTERNAL COMPONENTS**

| Component                                             | Description                            | Description Vendor                           |     | Тур. | Unit |

|-------------------------------------------------------|----------------------------------------|----------------------------------------------|-----|------|------|

| L1                                                    | 1.0 μH, +20/–10%, 4.1 A, 2520 x        | SEMCO CIGT252010EH1R0MNE                     | L   | 1.0  | μH   |

|                                                       | 1.0 mm                                 | SEMCO CIGT2520TOERTROMINE                    | DCR | 26   | mΩ   |

| C <sub>BAT</sub> (Note 2)                             | 22 $\mu\text{F},6.3$ V, 20%, X5R, 0603 | TDK C1608X5R0J226M                           | С   | 22   | Ē    |

| C <sub>MID</sub> x 2 (Note 3)                         | 10 μF, 25 V, 10%, X5R, 0805            | Murata GRM219R61E106M                        | С   | 10   | μF   |

| C <sub>BUS</sub> , C <sub>IN</sub>                    | 1.0 μF, 25 V, 10% X5R, 0603            | Murata GRM188R61E105K<br>TDK: C1608X5R1E105M | С   | 1.0  | nF   |

| C <sub>SYS</sub> (Note 4)                             | 10 μF, 6.3 V, 20%, X5R, 0603           | Murata GRM188R60J106M                        | С   | 10   |      |

| C <sub>REF,</sub> C <sub>REG</sub> , C <sub>LDO</sub> | 1.0 μF, 10 V, 20%, X5R, 0402           | Murata GRM155R61A105M                        | С   | 1.0  | μF   |

| C <sub>BOOT</sub>                                     | 10 nF, 10 V, 10%, X7R, 0201            | Murata GRM033R71A103K                        | С   | 10   |      |

| R <sub>REF</sub>                                      | 10 kΩ                                  |                                              | R   | 10   | kΩ   |

| R <sub>PU</sub>                                       | 1 MΩ                                   |                                              | RC  | Pi-  | MΩ   |

2. A minimum effective capacitance of 3.6 μF is required after accounting for tolerance, temperature, and aging.

3. A minimum effective capacitance of 8 µF is required after accounting for tolerance, temperature, and aging.

4. Including CSYS, a minimum effective system capacitance (distributed) of 20 µF after accounting for tolerance, temperature, and aging is required.

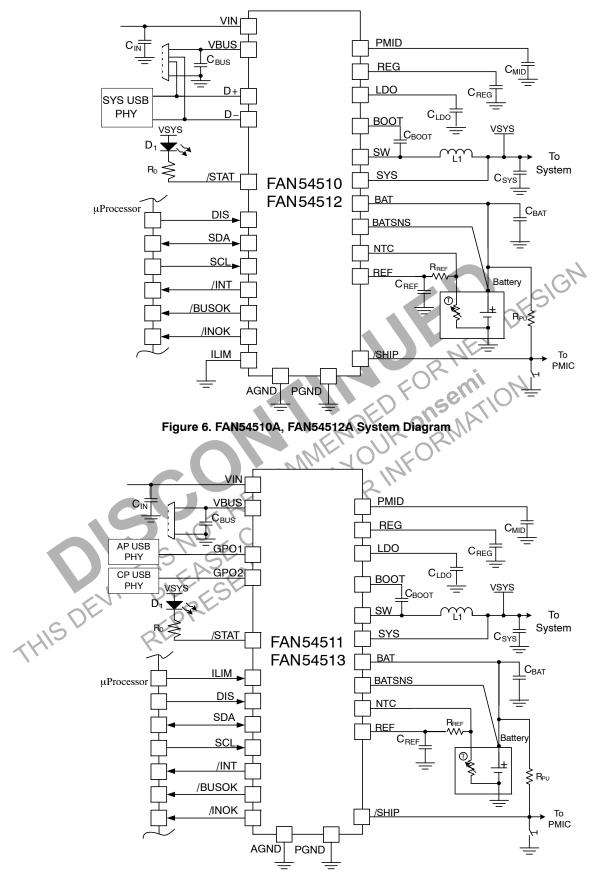

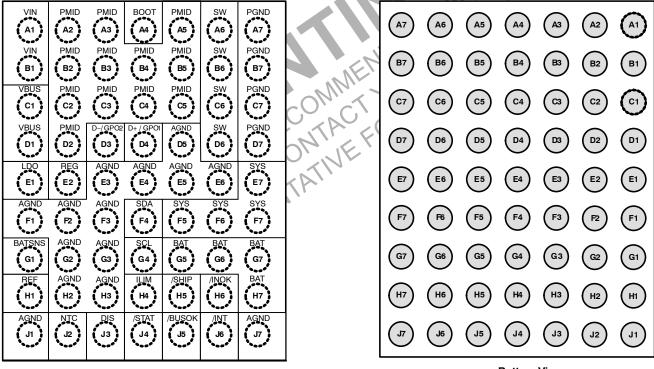

Top View

**Bottom View**

Figure 8. WLCSP-63 Pin Assignments

#### **Table 4. PIN DEFINITIONS**

| Pin #                           | Pin # Name Type Description               |          |                                                                                                                                                                                                                         |  |  |  |

|---------------------------------|-------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| POWER GROUND (LO                | POWER GROUND (LOCAL PGND) REFERENCED PINS |          |                                                                                                                                                                                                                         |  |  |  |

| A1, B1                          | VIN                                       | Р        | Wireless Charger Input Voltage. From wireless receiver or second input power source. Bypass VIN to PGND with 1 $\mu\text{F}.$                                                                                           |  |  |  |

| C1, D1                          | VBUS                                      | Р        | Charger Input Voltage. USB adapter input source also used for the USB–OTG output voltage. Bypass VBUS to PGND with 1 $\mu F$ .                                                                                          |  |  |  |

| A2, A3, A5, B2-B5,<br>C2-C5, D2 | PMID                                      | PFP      | Power Input Voltage. Power input to the charger regulator, bypass point for the input current sense. Bypass PMID to PGND locally with a minimum of $2x C_{MID}$ .                                                       |  |  |  |

| A6, B6, C6, D6                  | SW                                        | Р        | Switching Node. Connect to inductor L1 and CBOOT.                                                                                                                                                                       |  |  |  |

| A4                              | BOOT                                      | Р        | Bootstrap. High side NMOS Driver Bias. Connect a 10 nF capacitor between BOOT and SW.                                                                                                                                   |  |  |  |

| E7, F5–F7                       | SYS                                       | Р        | System Supply. Connect system load here. Bypass SYS to PGND locally with $C_{SYS}$ .                                                                                                                                    |  |  |  |

| G5–G7, H7                       | BAT                                       | Р        | Battery Voltage. Connect to the positive (+) terminal of the battery pack. Bypass BAT to PGND with $C_{BAT}$ .                                                                                                          |  |  |  |

| E1                              | LDO                                       | AO       | Linear Regulator. LDO is for powering external circuitry. Default output is 4.95 V when VBUS or VIN is valid.                                                                                                           |  |  |  |

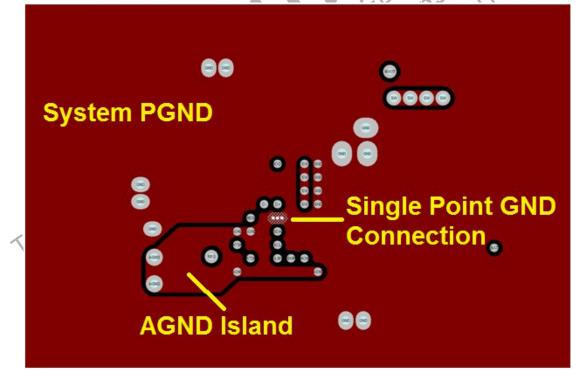

| A7, B7, C7, D7                  | PGND                                      | PG       | Power Ground. Power return for gate drive and power transistors. The connection from these pins to the ground pads of $C_{MID}$ and $C_{SYS}$ should be as short as possible. Refer to Recommended Component Placement. |  |  |  |

| ANALOG GROUND (A                | AGND) REFE                                | RENCED I | PINS                                                                                                                                                                                                                    |  |  |  |

# ANALOG GROUND (AGND) REFERENCED PINS

| E2                                             | REG    | AFP  | Internal Regulator. Bypass with a 1 µF capacitor to AGND                                                                                                                                                                                                                     |

|------------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G1                                             | BATSNS | AI   | Battery Voltage Sense. Connect this pin as close to battery terminal as possible using a single trace. Do not use as a power pin.                                                                                                                                            |

| H1                                             | REF    | AO   | Reference Voltage. REF is a 1.8 V regulated output used in conjunction with the NTC pin to determine the battery temperature. Connect to a 1 $\mu F$ capacitor to AGND.                                                                                                      |

| J2                                             | NTC    | AI   | Negative Temperature Coefficient Resistor. Pin is connected to the NTC terminal of the battery pack with a 10 k $\Omega$ external pull-up resistor to the REF pin. Note: Other values of the pull/up resistor and NTC may be used. See applications section for more detail. |

| D5, E3–E6, F1–F3,<br>G2, G3,<br>H2, H3, J1, J7 | AGND   | AGND | Analog Ground, All IC signals are referenced to this node. Connect to PGND at a single point. Refer to Recommended Component Placement.                                                                                                                                      |

# SYSTEM GROUND (PGND) REFERENCED PINS

| D4 | D+   | AI/O | Positive USB data line (FAN54510A, FAN54512A only). Used for BC1.2 adapter detec-<br>tion of SDP, DCP, or CDP device connection.                                                                                                                                           |

|----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | GPO1 | DO   | General Purpose Output 1 (FAN54511A, FAN54511AP, FAN54513A only). CMOS output driver that is sourced from the LDO output.                                                                                                                                                  |

| D3 | D-   | AI/O | Negative USB data line (FAN54510A, FAN54512A only). Used for BC1.2 detection of SDP or DCP/CDP device connection.                                                                                                                                                          |

| 03 | GPO2 | DO   | General Purpose Output 2 (FAN54511A, FAN54511AP, FAN54513A only). CMOS output driver that is sourced from the LDO output                                                                                                                                                   |

| F4 | SDA  | DI/O | I <sup>2</sup> C Interface Serial Data. Open-drain, Bi-directional I <sup>2</sup> C serial data line. This pin should not be left floating.                                                                                                                                |

| G4 | SCL  | DI   | $\rm I^2C$ Interface Serial Clock. $\rm I^2C$ communication clock input. This pin should not be left floating.                                                                                                                                                             |

| H4 | ILIM | DI   | Input Current Limit for VBUS (FAN54511A, FAN54511AP, FAN54513A only). Input LOW sets the input current limit to 1.5 A and HIGH sets to 500 mA (FAN54511A, FAN54511AP only) or 100 mA (FAN54513A only). This pin is internally pulled down through a 1 M $\Omega$ resistor. |

|    |      |      | ILIM pin functionality is disabled for FAN54510A and FAN54512A versions where it is recommended to tie ILIM to AGND or PGND.                                                                                                                                               |

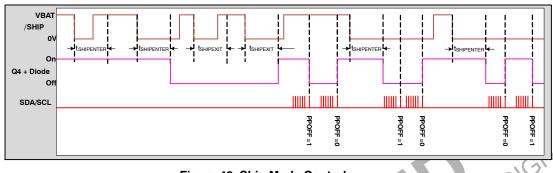

| H5    | /SHIP  | DI                 | Ship Mode Enable (Active–Low). If this pin is held LOW for more than $t_{SHIPENTER}$ during any other state, Ship Mode is entered and the battery is fully isolated from the system load. If /SHIP is held LOW again for more than $t_{SHIPEXIT}$ , Ship mode is disabled and Q4 is configured to allow the battery to discharge to the system load. Ship mode can also be exited, automatically, by applying a valid input source. Tie this pin to BAT using a 1 M $\Omega$ pull–up resistor for devices with embedded batteries. |

|-------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H6    | /INOK  | DO                 | VIN Power Okay (Active–Low). Active low, open–drain output indicates that the input source voltage at VIN has risen above V <sub>SOURCE(RISE)</sub> and passed validation, and a valid VBUS is not present. /INOK remains low while V <sub>IN (FALL)</sub> < V <sub>IN</sub> < V <sub>INOVP</sub> and V <sub>IN</sub> > V <sub>BAT</sub> . /INOK will be HIGH if /BUSOK is LOW.                                                                                                                                                    |

| J4    | /STAT  | DO                 | Status (Active–Low). Open–drain output indicating charge status. The IC pulls this pin LOW when charging is in progress, and can be used to signal the host processor or drive an LED.                                                                                                                                                                                                                                                                                                                                             |

| J5    | /BUSOK | DO                 | VBUS Power Okay (Active-Low). Active low, open-drain output indicates that the input source voltage at VBUS has risen above V <sub>SOURCE(RISE)</sub> and passed validation. /BUSOK remains low while V <sub>BUS (FALL)</sub> < V <sub>BUS</sub> < V <sub>BUSOVP</sub> and V <sub>BUS</sub> > V <sub>BAT</sub> .                                                                                                                                                                                                                   |

| J6    | /INT   | DO                 | Interrupt (Active–Low). Active low, open–drain output indicates that an interrupt bit or bits have been set. This pin is reset to HIGH after all set interrupt register bit(s) are read. This pin is not pulled LOW when an interrupt occurs that is masked by the associated mask bit.                                                                                                                                                                                                                                            |

| J3    | DIS    | DI                 | Disable. If this pin is held HIGH, the PWM converter is disabled, creating a high impedance path between VBUS/VIN and SYS. This pin has an internal 1 M $\Omega$ pull-down.                                                                                                                                                                                                                                                                                                                                                        |

| THISD | EVICE  | IS N<br>PLE<br>EPP | CONNENDED FOR NE<br>OT RECONTACT OR INFORMATION<br>SECUTATIVE FOR INFORMATION<br>SECUTATIVE FOR INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Table 5. ABSOLUTE | MAXIMUM RATINGS |

|-------------------|-----------------|

|-------------------|-----------------|

| Symbol           | Parameter                                                      |                           | Min  | Max             | Unit |

|------------------|----------------------------------------------------------------|---------------------------|------|-----------------|------|

|                  | VBUS, PMID Voltage, Maximum Slew Rate of 2 V/ $\mu$ s (Note 6) |                           | -2.0 | 22.0            |      |

|                  | VIN Voltage, Maximum Slew Rate of 2 V/ $\mu$ s (Not            | e 6)                      | -2.0 | 16.0            |      |

|                  | BOOT Voltage                                                   |                           | -0.3 | 19.0            |      |

| V <sub>DC</sub>  |                                                                | DC                        | -0.3 | 14.0            |      |

|                  | SW Voltage                                                     | Transient: < 5 ns         | -1.0 | 17.0            | V    |

|                  | SYS, BAT Voltage                                               |                           | -0.3 | 6.5<br>(Note 7) |      |

| V <sub>DCO</sub> | Voltage on Other Pins                                          |                           |      | 6.5<br>(Note 7) |      |

|                  | Electrostatic Discharge Protection Level, HBM                  | VBUS, PMID, VIN, BOOT, SW | 12   | 50              |      |

| ESD              | per JESD22-A114                                                | All Other Pins            | 20   | 00              | V    |

|                  | Electrostatic Discharge Protection Level, CDM per JESD22–C101  | All Pins                  | 15   | 00              |      |

| TJ               | Junction Temperature                                           | OFP MS                    | -40  | +150            | °C   |

| T <sub>STG</sub> | Storage Temperature                                            | CN R 2                    | -65  | +150            | °C   |

| TL               | Lead Soldering Temperature, 10 Seconds                         | NNE 100 COT               |      | +260            | °C   |

6. Positive slew rate applies only to voltages above the VIN\_OVP or VBUS\_OVP threshold.

7. Lesser of 6.5 V or  $V_{BAT}$  + 0.3 V.

# RECOMMENDED OPERATING CONDITIONS

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. On Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

#### Table 6. RECOMMENDED OPERATING CONDITIONS

| Symbol                             | Parameter                                                                                                 | Min. | Max.  | Unit |    |

|------------------------------------|-----------------------------------------------------------------------------------------------------------|------|-------|------|----|

| V <sub>BUS</sub> , V <sub>IN</sub> | Supply Voltage                                                                                            | 4.50 | 13.25 | V    |    |

| T <sub>A</sub>                     | Ambient Temperature                                                                                       | -30  | +85   | °C   |    |

| TJ                                 | Junction Temperature                                                                                      | -30  | +100  | °C   |    |

| C <sub>BAT</sub>                   | Minimum Effective Capacitance on VBAT                                                                     | 3.6  |       | μF   |    |

| C <sub>MID</sub>                   | Minimum Effective Capacitance on PMID V <sub>BST</sub> = 5 V                                              |      | 8     |      | μF |

| C <sub>SYS_DISTRIBUTED</sub>       | Minimum Effective Capacitance on SYS (includes $\ensuremath{C_{SYS}}$ and distributed system capacitance) |      | 20    |      | μF |

| C <sub>LDO</sub>                   | Minimum Effective Capacitance on LDO                                                                      |      | 0.4   |      | μF |

| C <sub>REG</sub>                   | Minimum Effective Capacitance on REG                                                                      |      | 0.4   |      | μF |

### THERMAL PROPERTIES

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards without vias in accordance to

JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_A$ .

#### Table 7. THERMAL PROPERTIES

| Symbol        | Parameter                                                               |     | Unit |

|---------------|-------------------------------------------------------------------------|-----|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance                                  | 40  | °C/W |

| $\Psi_{JB}$   | Junction-to-Board Thermal Characterization Parameter (Evaluation Board) | 4.3 | °C/W |

#### Table 8. ELECTRICAL SPECIFICATIONS

Unless otherwise specified:  $V_{BUS}$  = 5.0 V;  $V_{BAT}$  = 3.7 V; HZMODE = "0"; BOOSTEN = "0" (Charge Mode); TREGTH = 120°C;  $I_{REG}$  =  $I_{LDO}$  = 0 A; SCL, SDA = 0 or 1.8 V; and typical values are for  $T_A$  = 25°C

| Symbol              | Parameter                                                          | Conditions                                                                                                                       | Min. | Тур.  | Max. | Unit |

|---------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| POWER SUPPLI        | ES                                                                 |                                                                                                                                  |      |       | 10,  |      |

|                     |                                                                    | V <sub>BUS</sub> > V <sub>SOURCE(RISE)</sub> ; V <sub>IN</sub> Open;<br>PWM Switching; I <sub>BAT</sub> = I <sub>SYS</sub> = 0 A |      | AL.   |      | mA   |

| I <sub>SOURCE</sub> | V <sub>BUS</sub> or V <sub>IN</sub> Current                        | V <sub>IN</sub> > V <sub>SOURCE(RISE)</sub> ; V <sub>BUS</sub> Open;<br>PWM Switching; I <sub>BAT</sub> = I <sub>SYS</sub> = 0 A | JEV  | 4     |      | mA   |

|                     |                                                                    | HZMODE= "1"; V <sub>SOURCE</sub> ><br>V <sub>SOURCE(RISE)</sub> , NTC = GND                                                      | in   | 200   | 400  | μA   |

|                     |                                                                    | Sleep State; $V_{BUS} = V_{IN} = Open \text{ or } 0V;$<br>$V_{BAT} = 4.2 \text{ V}$                                              | e T  | $O_3$ | 10   | μΑ   |

|                     | Battery Discharge Current                                          | Ship Mode State; $V_{BUS} = V_{IN} = Open$<br>or 0 V; $V_{BAT} = 4.2$ V                                                          | Nu   | 0.8   | 10   | μΑ   |

| I <sub>BAT_HZ</sub> |                                                                    | DIS = HIGH or HZMODE="1";<br>V <sub>BUS</sub> =5 V; V <sub>IN</sub> = Open; V <sub>BAT</sub> = 4.2V ;<br>I <sub>SYS</sub> = 0 A  |      | 1     | 10   | μA   |

|                     | S NOT R                                                            | DIS = HIGH or HZMODE ="1"; V <sub>BUS</sub> =<br>Open; V <sub>IN</sub> = 5V; V <sub>BAT</sub> = 4.2V; I <sub>SYS</sub> =<br>0 A  |      | 1     | 10   | μA   |

|                     | Battery Leakage Current to V <sub>BUS</sub> in High-Impedance Mode | $V_{BUS}$ = 0 V; $V_{IN}$ = Open; $V_{BAT}$ = 4.2 V; $I_{SYS}$ = 0 A                                                             |      | 0.2   | 5.0  | μΑ   |

| ISOURCE_HZ          | Battery Leakage Current to V <sub>IN</sub> in High-Impedance Mode  | V <sub>IN</sub> = 0 V; V <sub>BUS</sub> = Open; V <sub>BAT</sub> = 4.2 V;<br>I <sub>SYS</sub> = 0 A                              |      | 0.2   | 5.0  | μA   |

#### CHARGER VOLTAGE REGULATION

| THIS               | Charge Voltage Range    |                                                            | 3.30 | <br>4.72 | V  |

|--------------------|-------------------------|------------------------------------------------------------|------|----------|----|

|                    |                         | $T_J = 25^{\circ}C; V_{FLOAT} = 4.20 V \text{ to } 4.50 V$ | -6   | +6       |    |

| V <sub>FLOAT</sub> | Charge Voltage Accuracy | $T_{J}$ = 0 to 70°C; $V_{FLOAT}$ = 4.20 V to 4.50 V        | -10  | +10      | mV |

|                    |                         | $T_J$ = -25 to 85°C; $V_{FLOAT}$ = All Settings            | -25  | +25      |    |

#### FAST CHARGE CURRENT REGULATION

|        | Output Charge Current Range | V <sub>BATMIN</sub> < V <sub>BAT</sub> < V <sub>FLOAT</sub>                    | 200 | 3200 | mA |

|--------|-----------------------------|--------------------------------------------------------------------------------|-----|------|----|

| IOCHRG | Charge Current Accuracy     | $I_{OCHRG} \ge 500 \text{ mA}, -30^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$ | -5  | +5   | %  |

|        |                             | I <sub>OCHRG</sub> < 500 mA, –30°C <t<sub>A&lt; 85°C</t<sub>                   | -10 | +10  | 70 |

#### PRE-CHARGE CURRENT CONTROL

| I <sub>pp</sub>    | Pre-Charge Current Range    |                                       | 200 |    | 800 | mA |

|--------------------|-----------------------------|---------------------------------------|-----|----|-----|----|

|                    | Pre-Charge Current Accuracy |                                       | -15 |    | +15 | %  |

| I <sub>SHORT</sub> | Linear Charging Current     | V <sub>BAT</sub> < V <sub>SHORT</sub> | 45  | 55 | 65  | mA |

#### Table 8. ELECTRICAL SPECIFICATIONS (continued)

Unless otherwise specified:  $V_{BUS} = 5.0 \text{ V}$ ;  $V_{BAT} = 3.7 \text{ V}$ ; HZMODE = "0"; BOOSTEN = "0" (Charge Mode); TREGTH = 120°C;  $I_{REG} = I_{LDO} = 0 \text{ A}$ ; SCL, SDA = 0 or 1.8 V; and typical values are for  $T_A = 25^{\circ}C$

| Symbol                      | Parameter                                               | Conditions                                                                                      | Min. | Тур. | Max.     | Unit |

|-----------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|----------|------|

| CHARGE TERM                 | INATION DETECTION                                       | -                                                                                               |      |      |          |      |

|                             | Termination Current Threshold<br>Range                  | V <sub>BAT</sub> > V <sub>FLOAT</sub> - V <sub>RCHG</sub> ; V <sub>BUS</sub> > V <sub>BAT</sub> | 25   |      | 600      | mA   |

| I <sub>TERM</sub>           | Termination Current Threshold                           | ITERM Setting > 200 mA                                                                          | -10  |      | +10      |      |

|                             | Accuracy                                                | ITERM Setting = 100 mA to 200 mA                                                                | -20  |      | +20      | %    |

|                             | Termination Current Deglitch Time                       |                                                                                                 |      | 30   |          | ms   |

| WEAK BATTER                 | Y DETECTION                                             | •                                                                                               |      |      |          |      |

|                             | Weak Battery Threshold Range                            |                                                                                                 | 3.0  |      | 3.7      | V    |

|                             | Hysteresis                                              | FAN54512A Only                                                                                  |      | 100  | ,GM      | mV   |

| V <sub>LOWV</sub>           |                                                         | All Other Part Numbers                                                                          |      | 3    | <b>)</b> | ΠV   |

|                             | Termination Current Threshold<br>Accuracy               |                                                                                                 | -5   |      | +5       | %    |

|                             | Weak Battery Deglitch Time                              | Rising Voltage; 2 mV Overdrive                                                                  |      | 30   |          | ms   |

| MINIMUM BATT                | ERY VOLTAGE DETECTION                                   | FU                                                                                              | en.  | 07   |          | -    |

| V <sub>BATMIN</sub>         | Pre-charge to Fast Charge<br>Transition Threshold Range | NDED one                                                                                        | 2,7  |      | 3.4      | V    |

|                             | Hysteresis                                              | ME OU FOR                                                                                       | 180  | 265  | 350      | mV   |

| BATMIN                      | Threshold Accuracy                                      | CONCIENN                                                                                        | -5   |      | +5       | %    |

|                             | Deglitch Time                                           | FOLLEDI                                                                                         |      | 30   |          | ms   |

| BATTERY RECH                | IARGE THRESHOLD                                         | ONTE                                                                                            |      |      |          |      |

| V <sub>RCHG</sub>           | Recharge Threshold                                      | Below V <sub>FLOAT</sub> ; T <sub>J</sub> = 25°C                                                |      | 170  |          | m۷   |

| · NORG                      | Deglitch Time                                           | $V_{BAT}$ falling below $V_{RCHG}$ threshold                                                    |      | 130  |          | ms   |

| SHORTED BAT                 | TERY THRESHOLD                                          |                                                                                                 |      |      |          |      |

| V <sub>SHORT</sub>          | Battery Short-Circuit Threshold                         | V <sub>BAT</sub> Rising                                                                         | 1.94 | 2.00 | 2.06     | V    |

| BATTERY FET                 | SUPPLEMENTAL CONTROL                                    |                                                                                                 |      |      |          |      |

|                             | BAT to SYS Threshold for BATFET                         | $V_{SYS -} V_{BAT,}$ Falling $V_{SYS}$                                                          | -6   | -5   | -4       |      |

| V <sub>THSYS</sub>          | Gate transition while charging                          | $V_{SYS -} V_{BAT,}$ Rising $V_{SYS}$                                                           | 0    | 1    | 2        | mV   |

| BATTERY TEMP                | PERATURE DETECTION                                      | •                                                                                               |      |      |          |      |

| T1                          | T1 (0°C) Temperature Threshold                          |                                                                                                 | 71.9 | 73.9 | 75.9     |      |

| T2                          | T2 (10°C) Temperature Threshold                         |                                                                                                 | 62.6 | 64.6 | 66.6     | % 0  |

| Т3                          | T3 (45°C) Temperature Threshold                         |                                                                                                 | 30.9 | 32.9 | 34.9     | VRE  |

| T4                          | T4 (60°C) Temperature Threshold                         |                                                                                                 | 21.3 | 23.3 | 25.3     |      |

| V <sub>JEITA</sub> (Note 9) | FLOAT Voltage Reduction During<br>JEITA Region          | V <sub>FLOAT</sub> = 4.35 V                                                                     | 160  | 200  | 240      | m۷   |

#### Table 8. ELECTRICAL SPECIFICATIONS (continued)

Unless otherwise specified: V<sub>BUS</sub> = 5.0 V; V<sub>BAT</sub> = 3.7 V; HZMODE = "0"; BOOSTEN = "0" (Charge Mode); TREGTH = 120°C; I<sub>REG</sub> = I<sub>LDO</sub> = 0 A; SCL, SDA = 0 or 1.8 V; and typical values are for  $T_A$  = 25  $^\circ C$

| Symbol                    | Parameter                                                             | Conditions                                | Min. | Тур. | Max. | Unit |

|---------------------------|-----------------------------------------------------------------------|-------------------------------------------|------|------|------|------|

| INPUT POWER S             | OURCE DETECTION                                                       |                                           |      |      |      |      |

| V <sub>SOURCE(RISE)</sub> | $\rm V_{BUS}$ or $\rm V_{IN}$ Input Voltage Rising                    | To Initiate Source Validation             | 4.30 | 4.40 | 4.52 | V    |

| V <sub>SOURCE(FALL)</sub> | Minimum $V_{BUS}$ or $V_{IN}$                                         | During Charging, V <sub>BAT</sub> < 3.6 V | 3.55 | 3.70 | 3.80 | V    |

| V <sub>SLP</sub>          | Sleep–Mode Entry Threshold,<br>V <sub>SOURCE</sub> – V <sub>BAT</sub> | VSOURCE(FALL) ≤[¥BAT                      | 0    | 40   | 100  | mV   |

| <sup>t</sup> SRCQUAL      | $V_{BUS}$ or $V_{IN}$ Input Qualification Time                        |                                           |      | 32   |      | ms   |

| tvsc_valid                | $V_{BUS}$ or $V_{IN}$ Input Validation Time                           |                                           |      | 32   |      | ms   |

| IVSOURCE                  | $V_{BUS}$ or $V_{IN}$ Input Validation Current                        |                                           |      | 50   |      | mA   |

| DIVC CONTROL              | LOOP                                                                  |                                           |      |      | JCP  |      |

| V <sub>SOURCE</sub> (LIM) | Input Voltage Loop Setpoint<br>Accuracy                               |                                           | -3   | DE   | +3   | %    |

| INPUT CURREN        | T LIMIT                                        |                                                              | EV   | 1    |      |    |

|---------------------|------------------------------------------------|--------------------------------------------------------------|------|------|------|----|

|                     | V <sub>BUS</sub> Input Current Limit Range     | R                                                            | 100  |      | 3000 |    |

|                     |                                                | ILIM = HIGH (100 mA) FAN54513A<br>Only                       | 86   | 93   | 100  |    |

|                     |                                                | ILIM = HIGH (500 mA) FAN54511A,<br>FAN54511AP Only           | 460  | 480  | 500  |    |

| I <sub>BUSLIM</sub> | V <sub>BUS</sub> Input Current Limit Threshold | ILIM = LOW (1.5 A); FAN54511A,<br>FAN54511AP, FAN54513A Only | 1380 | 1440 | 1500 | mA |

|                     |                                                | 1BUSLIM (REG 14h[6:0]) = "00h"                               | 86   | 93   | 100  |    |

|                     |                                                | IBUSLIM (REG 14h[6:0]) = "10h"                               | 460  | 480  | 500  |    |

|                     | SNGE                                           | IBUSLIM (REG 14h[6:0]) = "74h"                               | 2760 | 2880 | 3000 |    |

|                     | V <sub>IN</sub> Input Current Limit Range      |                                                              | 325  |      | 2000 |    |

| I <sub>INLIM</sub>  | A harvet Current Limit Throughold              | INLIM (REG 16h[6:0]) = "1Bh"                                 | 920  | 960  | 1000 | mA |

| ,19                 | VIN Input Current Limit Threshold              | INLIM (REG 16h[6:0]) = "43h"                                 | 1840 | 1920 | 2000 |    |

LOW DROP OUT REGULATOR

| V <sub>LDOACC</sub>               | LDO Voltage Accuracy                      | V <sub>PMID</sub> ≥[]¥ <sub>LDO</sub> + 500 mV; I <sub>LDO</sub> = 1 mA            | -5 |     | +5 | %  |

|-----------------------------------|-------------------------------------------|------------------------------------------------------------------------------------|----|-----|----|----|

| I <sub>LDO</sub>                  | Current Rating                            | $V_{PMID} = V_{LDO} + 500 \text{ mV}$                                              | 10 |     |    | mA |

| VLDO <sub>DROP</sub><br>(Note 10) | Drop Out Voltage                          | I <sub>OUT</sub> = 10 mA                                                           |    | 170 |    | mV |

| RLDO <sub>PD</sub>                | LDO Pull Down Resistance when<br>Disabled | LDO Off                                                                            |    | 1.2 |    | kΩ |

| IQ <sub>LDO</sub>                 | LDO Quiescent Current                     | LDO On, V <sub>PMID</sub> = V <sub>LDO</sub> + 500 mV                              |    | 20  | 40 | μA |

| REG <sub>LDO</sub>                | LDO Load Regulation                       | V <sub>PMID</sub> = V <sub>LDO</sub> + 500 mV;<br>10 μA < I <sub>OUT</sub> ≤[]0 mA |    | 50  |    | mV |

#### Table 8. ELECTRICAL SPECIFICATIONS (continued)

**Battery Detection Time**

t<sub>DETECT</sub>

Unless otherwise specified:  $V_{BUS}$  = 5.0 V;  $V_{BAT}$  = 3.7 V; HZMODE = "0"; BOOSTEN = "0" (Charge Mode); TREGTH = 120°C;  $I_{REG}$  =  $I_{LDO}$  = 0 A; SCL, SDA = 0 or 1.8 V; and typical values are for  $T_A$  = 25°C

| Symbol                           | Parameter                                                      | Conditions                                             | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Тур. | Max.  | Uni        |

|----------------------------------|----------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|

| GPO1, GPO2 (F                    | AN54511A, FAN54511AP, FAN54513A                                | ÓNLY)                                                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |       |            |

| V <sub>(OL)</sub>                | Output Low                                                     | I <sub>SINK</sub> = 5 mA                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 0.3   | V          |

| V <sub>(OH)</sub>                | Output High                                                    | I <sub>SOURCE</sub> = 5 mA                             | V <sub>LDO</sub> –<br>200 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |       | v          |

| V <sub>REF</sub> BIAS GEN        | ERATOR                                                         |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |            |

|                                  | Bias Regulator Voltage                                         | $V_{SOURCE} > V_{SOURCE(MIN)}$                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.8  |       | V          |

| V <sub>REF</sub>                 | Short-Circuit Current Limit                                    |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5  |       | μA         |

| /STAT, /BUSOK,                   | /INOK, /INT, SDA                                               |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |            |

| V <sub>(OL)</sub>                | Output Low                                                     | I <sub>SINK</sub> = 5 mA                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 0.4   | V          |

| I <sub>(OH)</sub>                | Output High Leakage Current                                    | VDD = 5 V                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 2 1   | μA         |

| LOGIC LEVELS                     | : SDA, SCL, /SHIP, ILIM, DIS                                   |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10×  |       |            |

| V <sub>IH</sub>                  | High-Level Input Voltage                                       |                                                        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |       | V          |

| V <sub>IL</sub>                  | Low-Level Input Voltage                                        |                                                        | in the second se | 1    | 0.4   | V          |

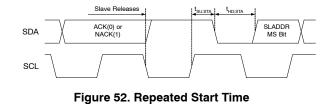

| I <sub>IN</sub>                  | Input Bias Current                                             | Input Tied to GND or V <sub>BUS</sub>                  | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.01 | 1.00  | μA         |