# LED Controller, 6-Channel, with Fault Diagnostics

## **Description**

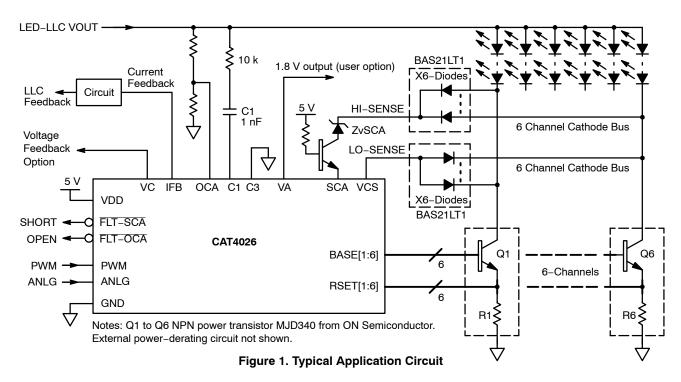

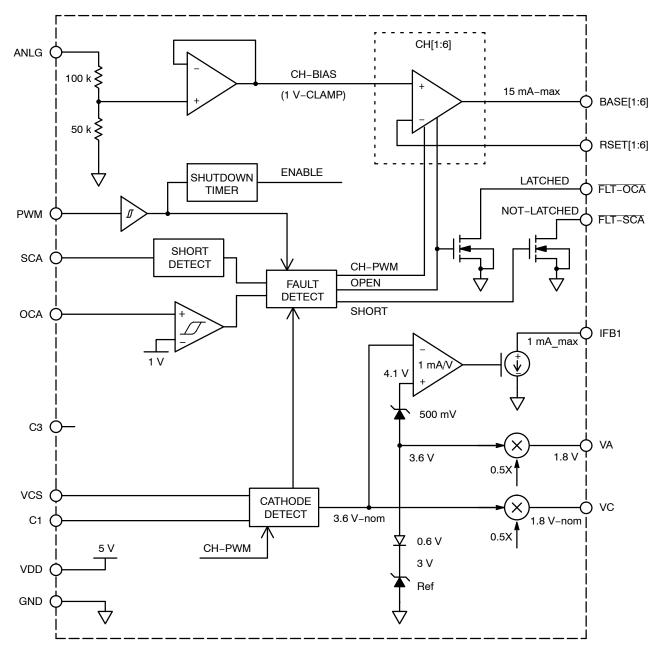

The CAT4026 is a high performance, large panel LED controller designed to control six constant current high voltage LED strings. Added control circuitry monitors the lowest cathode voltage and generates a feedback control signal to an external Switch Mode Power Supply (SMPS) to provide a low cost and efficient solution for large panel high voltage LED backlighting.

Each LED channel current is accurately matched and controlled by sensing an external resistor in series with a low cost bipolar power transistor. This allows current and heat dissipation concerns to be mitigated from the CAT4026 device package.

For added system reliability, both Open-Cathode-Anode (OCA) and Shorted-Cathode-Anode (SCA) fault detection circuitry has been included along with independent Fault flag logic outputs for diagnostic purposes.

LED current dimming in all six channels can be precisely controlled by either a Pulse Width Modulation signal via the PWM input pin or by an analog dimming voltage applied at the ANLG pin. In addition the ANLG pin provides a convenient method for limiting the overall maximum power dissipation in the event of excessive LED shorting within any LED string.

The device will automatically enter low current shutdown mode by taking the PWM pin low for an extended length of time.

#### **Features**

- 6 Channel LED Controller

- Adaptive Feedback Control to External SMPS for Better Efficiency

- PWM and Analog Mode Dimming

- Short Cathode-Anode (SCA) Fault Protection

- Open Cathode-Anode (OCA) Fault Protection

- Over-Voltage Protection

- Thermal Shutdown Protection

- Automatic Inactivity Power Down Mode

- SOIC-28L Package

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

## **Typical Applications**

- LCD-TV LED Backlighting

- LED General Lighting

## ON Semiconductor®

http://onsemi.com

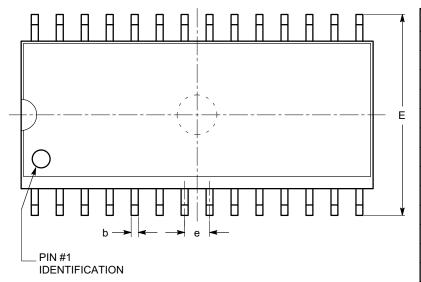

SOIC-28 V SUFFIX CASE 751BM

#### **PIN CONNECTIONS**

| VDD   | Щ              | $0^{1}$ | 28 | þ  | GND     |

|-------|----------------|---------|----|----|---------|

| PWM   | ш              | 2       | 27 | ь  | SCA     |

| ANLG  | Ш              | 3       | 26 | ь  | VCS     |

| BASE1 | Ш              | 4       | 25 | ь  | BASE6   |

| RSET1 | Ш              | 5       | 24 | ┢╸ | RSET6   |

| BASE2 | Ш              | 6       | 23 | ┢╸ | BASE5   |

| RSET2 | Щ              | 7       | 22 | ⊨  | RSET5   |

| BASE3 | Щ              | 8       | 21 | ┢╸ | BASE4   |

| RSET3 | ш              | 9       | 20 | ┢╸ | RSET4   |

| OCA   | ш              | 10      | 19 | ь  | FLT-OCA |

| C1    | ш              | 11      | 18 | ь  | C3      |

| N.C.  | Ш              | 12      | 17 | ь  | FLT-SCA |

| VA    | Ш              | 13      | 16 | ┢╸ | IFB     |

| N.C.  | $\blacksquare$ | 14      | 15 | þ  | VC      |

|       |                | -       |    |    |         |

(Top View)

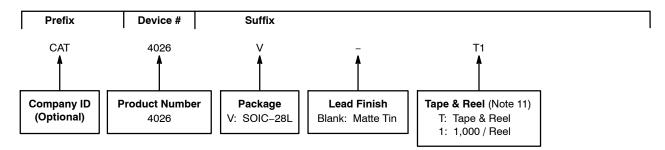

## **MARKING DIAGRAM**

L = Assembly Location Code

3 = Mark "3" for (lead finish Matte-Tin) A = Product Revision: Fixed as "A"

CAT4026V = Specific Device Code

YY = Production Year (Last Two Digits)

WW = Production Week (Two Digits)

XXXX = Last Four Digits of Assembly Lot Number

## **ORDERING INFORMATION**

| Device      | Package   | Shipping    |

|-------------|-----------|-------------|

| CAT4026V-T1 | SOIC-28   | 1,000/      |

| (Note 1)    | (Pb-Free) | Tape & Reel |

1. Matte Tin Plated Finish (RoHS-compliant)

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                            | Symbol              | Value                                                         | Unit |

|-----------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------|------|

| VDD Voltage Range                                                                 | V <sub>in</sub>     | -0.3 to 7                                                     | V    |

| PWM, ANLG, FLT-OCA, FLT-SCA Voltage Range                                         | PWM                 | -0.3 to 7 V or (V <sub>in</sub> + 0.3),<br>whichever is lower | V    |

| RSET[x], BASE[x]                                                                  |                     | -0.3 to 7 V or (V <sub>in</sub> + 0.3),<br>whichever is lower | V    |

| Maximum Junction Temperature                                                      | T <sub>J(max)</sub> | 150                                                           | °C   |

| Storage Temperature Range                                                         | T <sub>STG</sub>    | -65 to 150                                                    | °C   |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>    | 260                                                           | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 2. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- This device meets latchup tests defined by JEDEC Standard JESD78.

- 3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **Table 2. THERMAL CHARACTERISTICS**

| Rating                                        | Symbol          | Value | Unit |

|-----------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, SOIC-28              |                 |       | °C/W |

| Thermal Resistance, Junction-to-Air (Note 4)  | $R_{\theta,JA}$ | 79    |      |

| Thermal Resistance, Junction-to-Case (Note 4) | $R_{\psiJC}$    | 23    |      |

<sup>4.</sup> Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

## **Table 3. OPERATING RANGES**

| Rating              | Symbol          | Min | Max | Rating |

|---------------------|-----------------|-----|-----|--------|

| Input Voltage       | V <sub>in</sub> | 4.5 | 5.5 | V      |

| Ambient Temperature | $T_A$           | -40 | 85  | °C     |

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS ($V_{DD} = 5$ V, $V_{PWM} = V_{DD}$, $V_{ANLG} = 3.3$ V, for typical values $T_A = 25^{\circ}C$, for min/max values $T_A = -40^{\circ}C$ to +85^{\circ}C$; unless otherwise noted.) }$

| Parameter                                                                              | Test Conditions                                                                                                                          | Symbol                                       | Min    | Тур        | Max  | Unit |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------|------------|------|------|

| RSET[x] pin voltage                                                                    |                                                                                                                                          | V <sub>RSET</sub>                            | 0.97   | 1.00       | 1.03 | V    |

| RSET channel to channel voltage matching                                               | (V <sub>RSET</sub> - V <sub>RSETAVR</sub> ) / V <sub>RSETAVR</sub> ,<br>Nominal current 100 mA per channel                               | V <sub>RSET-MA</sub>                         |        | ±0.6       | ±2.0 | %    |

| RSET device to device matching                                                         |                                                                                                                                          | V <sub>RSET-D</sub>                          |        | ±0.6       | ±2.5 | %    |

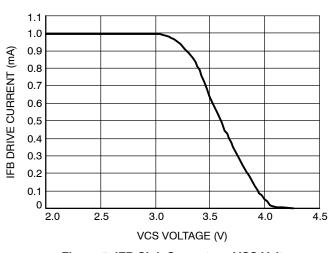

| IFB sink current                                                                       | V <sub>VCS</sub> = 3.6 V                                                                                                                 | I <sub>IFB</sub>                             |        | 0.5        |      | mA   |

| VA output voltage                                                                      | VA pin no load                                                                                                                           | $V_{VA}$                                     |        | 1.8        |      | V    |

| VA output resistance                                                                   | 100 μA load                                                                                                                              | R <sub>VA</sub>                              |        | 250        |      | Ω    |

| VC output voltage                                                                      | VC pin no load, VCS pin = 3.6 V                                                                                                          | V <sub>VC</sub>                              |        | 1.8        |      | V    |

| VC output resistance                                                                   | 100 μA load                                                                                                                              | R <sub>VC</sub>                              |        | 360        |      | Ω    |

| VCS pull-up resistance to V <sub>DD</sub>                                              | V <sub>PWM</sub> = 5 V                                                                                                                   | R <sub>VCS</sub>                             |        | 50         |      | kΩ   |

| SHUTDOWN, DISABLE, QUIESCENT CUR                                                       | RENTS                                                                                                                                    |                                              |        |            |      |      |

| Shutdown Current                                                                       | Shutdown mode (PWM low for > 50 ms)                                                                                                      | l <sub>OFF</sub>                             | -      | 50         |      | μΑ   |

| Disable Current                                                                        | V <sub>PWM</sub> = 0 V, all channels off<br>(PWM low for < 20 ms)                                                                        | I <sub>DIS</sub>                             | -      | 1.5        |      | mA   |

| Quiescent Current (Note 5)                                                             | $V_{PWM}$ = 5 V, R1 to R6 = 10 $\Omega$ (100 mA load per channel), application circuit as shown with 0.8 mA BASE pin current per channel | ΙQ                                           | -      | 16         |      | mA   |

|                                                                                        | No external circuit components present, all BASE[x] and RSET[x] pins floating                                                            |                                              |        | 7.6        |      | mA   |

| Short Circuit Supply Current                                                           | V <sub>VCS</sub> = GND, all BASE[x] shorted to Ground                                                                                    | I <sub>Q-MAX</sub>                           | _      | 118        |      | mA   |

| LOGIC I/OS                                                                             |                                                                                                                                          | •                                            | •      |            |      |      |

| PWM pull-down resistance                                                               | V <sub>PWM</sub> = 5 V                                                                                                                   | R <sub>PWM</sub>                             | 80     | 120        | 200  | kΩ   |

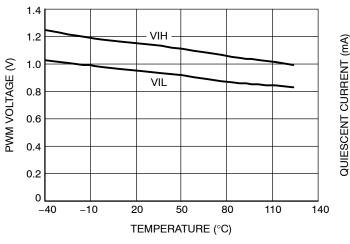

| PWM Input Threshold Voltage<br>V <sub>IH</sub> Logic High<br>V <sub>IL</sub> Logic low |                                                                                                                                          | V <sub>PWM-VIH</sub><br>V <sub>PWM-VIL</sub> | _<br>_ | 1.2<br>1.0 | -    | V    |

| ANLG divider network pull-down resistance                                              |                                                                                                                                          | R <sub>ANLG</sub>                            | 120    | 150        | 180  | kΩ   |

| ANLG to RSET pin voltage ratio (V <sub>ANLG</sub> / V <sub>RSET</sub> )                | $V_{ANLG} \le$ 3.0 V, all outputs on, R1–R6 = 10 $\Omega$                                                                                | V <sub>ANLG</sub><br>/V <sub>RSET</sub>      |        | 3          |      | -    |

| OPEN CATHODE-ANODE FAULT DIAGNO                                                        | STICS                                                                                                                                    | 1                                            |        |            |      |      |

| OCA open-LED threshold voltage                                                         |                                                                                                                                          | V <sub>OCA</sub>                             | 0.97   | 1.00       | 1.03 | V    |

| FLT-OCA pin pull-down voltage                                                          | Open Cathode Anode fault is active,<br>5 mA sink current                                                                                 | V <sub>FLT-OCA</sub>                         |        | 65         |      | mV   |

| FLT-OCA open-drain leakage                                                             | Open Cathode Anode fault is inactive                                                                                                     | I <sub>FLT-OCA</sub>                         |        | 0.2        |      | μΑ   |

| FLT-OCA fault delay                                                                    | Delay between OCA fault and FLT-OCA active                                                                                               | T <sub>FLT-OCA</sub>                         |        | 1          |      | μS   |

| SHORT CATHODE-ANODE FAULT DIAGN                                                        | OSTICS                                                                                                                                   |                                              |        |            |      |      |

| SCA fault detection threshold sink current                                             | FLT-SCA transitions to active state (low)                                                                                                | I <sub>SCA-ON</sub>                          |        | 1.3        |      | mA   |

| SCA fault cleared threshold sink current                                               | FLT-SCA transitions to inactive state (high)                                                                                             | I <sub>SCA-OFF</sub>                         |        | 0.4        |      | mA   |

| FLT-SCA pin pull-down voltage                                                          | Short Cathode Anode fault is active,<br>5 mA sink current                                                                                | V <sub>FLT-SCA</sub>                         |        | 65         |      | mV   |

| FLT-SCA fault delay                                                                    | Delay between SCA fault and FLT-SCA active                                                                                               | T <sub>FLT-SCA</sub>                         |        | 35         |      | μs   |

|                                                                                        |                                                                                                                                          |                                              |        |            |      |      |

<sup>5.</sup> The quiescent current depends on the external bipolar transistors used (ON Semiconductor MJD340) and more specifically of its DC current gain (h<sub>FE</sub>).

| Parameter                                                  | Test Conditions                                                                                                       | Symbol           | Min | Тур | Max | Unit |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| TIMING                                                     | FIMING                                                                                                                |                  |     |     |     |      |

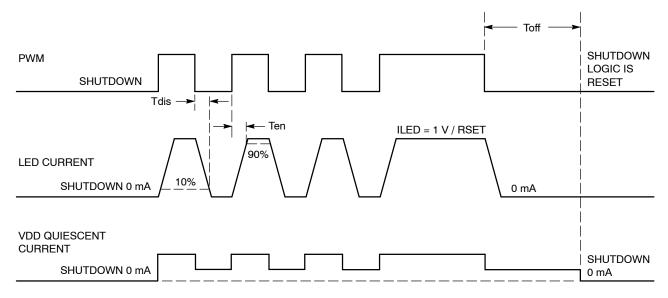

| PWM Enable Time                                            | V <sub>PWM</sub> = 0 V to V <sub>DD</sub><br>I <sub>out</sub> = 0 mA to 90% of I <sub>out(nom)</sub>                  | t <sub>EN</sub>  |     | 800 |     | ns   |

| PWM Disable Time                                           | V <sub>PWM</sub> = V <sub>DD</sub> to 0 V<br>I <sub>out</sub> = I <sub>out(nom)</sub> to 10% of I <sub>out(nom)</sub> | t <sub>DIS</sub> |     | 1   |     | μs   |

| Turn-off Shutdown Time,<br>PWM falling to shutdown         | V <sub>PWM</sub> = 5 V to 0 V<br>I <sub>out</sub> = I <sub>out(nom)</sub> to shutdown mode                            | t <sub>OFF</sub> |     | 25  |     | ms   |

| Channel to channel turn on and turn off delay (staggering) |                                                                                                                       | t <sub>CC</sub>  |     | 50  |     | ns   |

| THERMAL SHUTDOWN                                           |                                                                                                                       |                  |     |     |     |      |

| Thermal Shutdown Temperature                               |                                                                                                                       | T <sub>SD</sub>  | -   | 150 | -   | °C   |

| Thermal Shutdown Hysteresis                                |                                                                                                                       | T <sub>SH</sub>  | _   | 20  | _   | °C   |

Figure 2. Timing Diagram

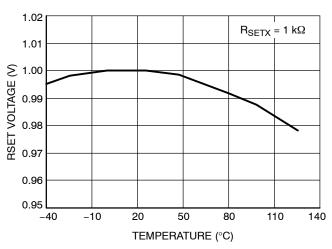

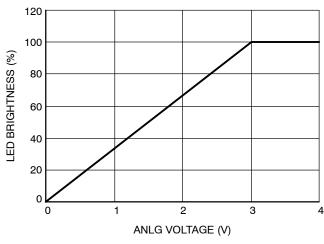

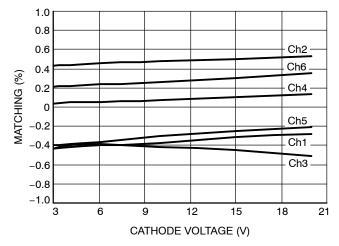

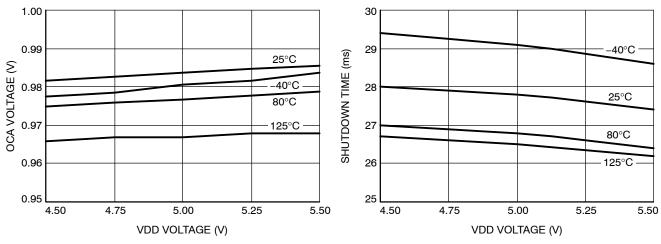

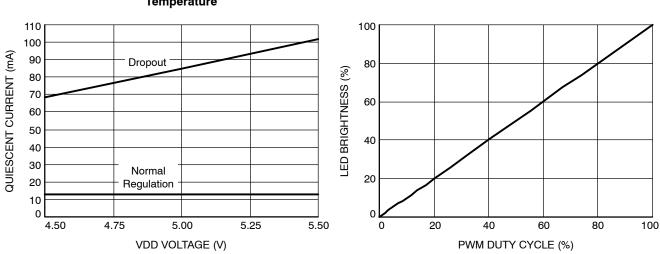

## TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{DD} = V_{PWM} = 5 \text{ V}, V_{ANLG} = 3.3 \text{ V}, T_{AMB} = 25^{\circ}\text{C}$  unless otherwise specified.)

16 12 12 25°C -40°C 4 0 4.50 4.75 5.00 5.25 5.50 VDD VOLTAGE (V)

Figure 3. PWM Threshold Voltage vs. Temperature

Figure 4. Quiescent Current vs. Temperature

Figure 5. IFB Sink Current vs. VCS Voltage

Figure 6. RSET Voltage vs. Temperature

Figure 7. LED Brightness vs. ANLG Voltage

Figure 8. Matching Channel-to-Channel vs. Cathode Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS

( $V_{DD}$  =  $V_{PWM}$  = 5 V,  $V_{ANLG}$  = 3.3 V,  $T_{AMB}$  = 25°C unless otherwise specified.)

Figure 9. OCA Threshold Voltage vs. Temperature

Figure 10. Shutdown Time vs. Temperature

Figure 11. Quiescent Current vs. Supply Voltage (Note 6)

Figure 12. LED Brightness vs. PWM Duty Cycle

6. At initial power up, the CAT4026 will draw a higher quiescent current equal to the "dropout" current until it reaches normal regulation.

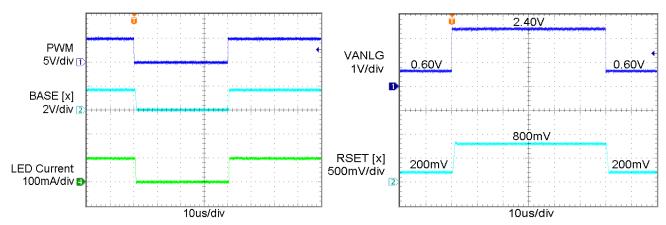

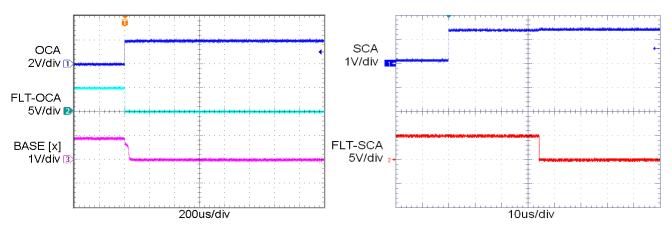

## TYPICAL PERFORMANCE CHARACTERISTICS

( $V_{DD}$  =  $V_{PWM}$  = 5 V,  $V_{ANLG}$  = 3.3 V,  $T_{AMB}$  = 25°C unless otherwise specified.)

Figure 13. LED Current Transient During PWM Dimming

Figure 14. ANLG Transient, 20% to 80% Brightness

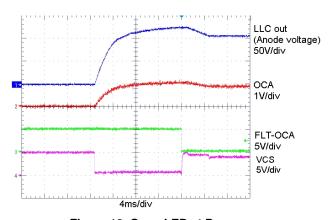

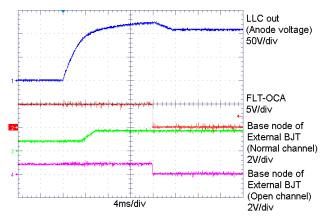

Figure 15. Open Cathode-Anode Waveform

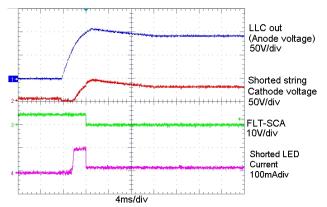

Figure 16. Short Cathode-Anode Waveform

## **Table 5. PIN DESCRIPTION**

| Pin#                   | Name       | Function                                                                                                                                                                              |

|------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | VDD        | Supply Bias voltage input for controller                                                                                                                                              |

| 2                      | PWM        | Digital PWM input control to globally PWM all channels                                                                                                                                |

| 3                      | ANLG       | ANLG input bias signal to globally adjust full scale brightness. (intended for external power derating circuit for SCA conditions)                                                    |

| 4, 6, 8, 21,<br>23, 25 | BASE [1:6] | Base drive connection for external channel high voltage BJT                                                                                                                           |

| 5, 7, 9, 20,<br>22, 24 | RSET [1:6] | Current setting resistor for LED channel (Full Scale Brightness of 1 V)                                                                                                               |

| 10                     | OCA        | Open Cathode Anode over-voltage threshold trigger input (sets maximum allowed LED Anode voltage, 1 V trigger)                                                                         |

| 11                     | C1         | LED Anode capacitor                                                                                                                                                                   |

| 12                     | N.C.       | Do not connect, leave floating                                                                                                                                                        |

| 13                     | VA         | Internal cathode reference voltage (divided by 2 and buffered to 1.8 V). Intended to provide reference bias for external circuitry, such as the power derating operational amplifier. |

| 14                     | N.C.       | Do not connect, leave floating                                                                                                                                                        |

| 15                     | VC         | Cathode voltage with compensation (divided by 2 and buffered). Leave floating if not used.                                                                                            |

| 16                     | IFB        | Current sink feedback (1 mA max) used with external circuit to control of LED Anode supply voltage                                                                                    |

| 17                     | FLT-SCA    | Shorted Cathode-Anode Fault output logic signal (open-drain, active low) indicating presence of excessive cathode voltage                                                             |

| 18                     | СЗ         | Connect pin to GND                                                                                                                                                                    |

| 19                     | FLT-OCA    | Open Cathode-Anode Fault output logic signal (open-drain, active low) indicating an Open-channel condition                                                                            |

| 26                     | VCS        | Lowest LED Cathode sense input (connect to sensing diode anodes)                                                                                                                      |

| 27                     | SCA        | Highest LED Cathode sense input (connect to external high voltage transistor and zener/diode network)                                                                                 |

| 28                     | GND        | Ground reference for all pins                                                                                                                                                         |

#### **Pin Functions**

#### **VDD**

The VDD input is the positive supply to the devices. VDD should be nominally 5 V.

#### **PWM**

The PWM control input provides multiple functions. When the first rising edge is applied to PWM input, the CAT4026 will immediately power-up and remain powered up until the PWM input has been held low for at least typically 25 ms, at which point the device will enter full shutdown mode and draw zero current.

When PWM is active (high level), all LED channels are enabled. When PWM is inactive (low level), all LED channels are disabled. For PWM dimming frequencies in the 300 Hz range, duty cycles as low as 0.1% are supported.

An internal pull–down resistor (120 k $\Omega$  typical) exists on the PWM input. PWM logic high and low detection levels are typically set at 1.2 V and 1.0 V respectively.

#### **ANLG**

The ANLG controlled input allows the full scale brightness level of all channels to be globally reduced. When the ANLG control is taken below 3 V, the maximum LED brightness will be equal to 1/3 of the ANLG pin voltage. If the ANLG pin is taken above 3 V, it will have no further effect and the brightness will remain at the full scale (100%) setting.

An internal resistive network to ground (150 k $\Omega$  typical) exists on the ANLG pin. The external source resistance driving this input should be taken into consideration when controlling the ANLG input.

A simple power derating external circuit can be applied to the ANLG pin whenever excessive voltage is present on any LED cathode.

If the ANLG control function is not required, the pin should be pulled high (above 3 V) to ensure full scale brightness is maintained.

## BASE[1:6]

The BASE output pin drives the base of the external NPNs to regulate the LED current in the associated string to the preset value. External high-voltage bipolar junction transistors, such as MJD340, are recommended.

Operating base currents up to 5 mA can be powered from each of the BASE pins in normal operating conditions. In the event of any BASE pin being shorted directly to GND, internal protection circuitry will limit the drive current to 15 mA (typically).

## **RSET[1:6]**

The RSET input pins sense the voltage of the external LED current bias resistors. Each RSET pin is accurately regulated to a voltage of 1.0 V under the full scale brightness condition (ANLG > 3.0 V).

Each RSET pin contains internal compensating circuitry to eliminate the operating base current, thereby maintaining extremely accurate LED matching on all channels.

#### FLT-OCA

The  $\overline{FLT}$ – $\overline{OCA}$  flag output is active low (open–drain) and is latched whenever an Open Cathode–Anode fault condition has been detected on any LED string. An external pull–up resistor (10 k $\Omega$ ) should be connected to  $\overline{FLT}$ – $\overline{OCA}$ .

For systems requiring complete shutdown upon detection of any open–LED channel, the FLT–OCA output can be used to drive the shutdown control of the LED power supply.

For systems which must continue operation under open–LED channels, the FLT–OCA should only be used for diagnostic purposes (not for system shutdown).

The FLT-OCA is cleared upon power-down of the CAT4026 device.

#### FLT-SCA

The  $\overline{FLT}$ – $\overline{SCA}$  flag output is active low (open–drain) and becomes active whenever any LED cathode terminal exceeds a user programmed voltage level (at the SCA pin, set by an external zener diode). An external pull–up resistor (10 k $\Omega$ ) should be connected to the  $\overline{FLT}$ – $\overline{SCA}$  pin.

For systems requiring complete shutdown upon detection of any faulty LED channel, the FLT–SCA output can be used to drive the shutdown control of the LED power supply.

For systems which must continue operation under faulty LED channels, the FLT-SCA should only be used for diagnostic purposes (not for system shutdown). In this case, the FLT-SCA flag can be used to trigger an external power derating circuit reducing the applied voltage at the ANLG control input, thereby reducing the power dissipated in the external bipolar channel transistors.

Note: If an Open–LED channel is present, the FLT–SCA flag may become temporary active (depending on the user threshold levels) while the system is diagnosing the Open–channel fault. When the system has eventually cleared (disabled) the open–channel, the fault FLT–SCA will automatically clear itself once the system has stabilized and returned back to normal operating conditions.

#### **IFB**

The IFB pin is a pull-down current sink with a drive level determined by the lowest LED cathode voltage as shown below.

| VCS Voltage | IFB Drive Current (typ) |

|-------------|-------------------------|

| > 4.1 V     | 0 mA                    |

| 3.3 V       | 0.5 mA                  |

| < 3.1 V     | 1.0 mA                  |

VCS = Vcathode + Vdiode

External adjustment of LED Anode supply voltage is controlled by the IFB current sink in conjunction with an external feedback circuit. The external circuit should be configured so that 1 mA drive signal will achieve the desired necessary dynamic adjustment range for expected worst case maximum LED string operating voltage range

A linear transconductance relationship exists for the drive current (1 mA/V) for Cathode operation between 2.5 V and 3.5 V.

#### C<sub>1</sub>

Connect a capacitor of 1 nF and a 10 k $\Omega$  resistor from the C1 pin to the LED Anode voltage. Capacitor voltage rating must be greater than the highest LED anode voltage.

#### C

Connect pin to GND.

#### SCA

The SCA pin is used to detect a severe mismatch in LED string voltage, such as the occurrence of an Anode–Cathode short. The SCA pin is connected to each LED cathode via a diode array and a voltage level translator. The threshold voltage of the detector can be adjusted by using an external Zener diode.

A conduction level of 1.5 mA into the SCA pin will trigger a FAULT condition. The FAULT condition will be cleared upon the conduction current level falling below 0.5 mA and normal operation will resume.

### OCA

The OCA input is used to detect and protect against abnormally high LED Anode condition. An external resistive divider connected to the OCA pin, from the LED Anode voltage, will trigger a FLT-OCA condition once the OCA input level exceeds 1.0 V. Any open-LED channel will automatically be disabled and removed from the feedback loop when OCA is triggered. This method provides an auto-recovery feature for the system to resume normal operation ensuring only the 'good' LED channels are included in the feedback loop.

If the open–LED function is not used, the OCA pin should be tied to GND.

#### vcs

The VCS pin is connected to each LED cathode via a diode array. This pin detects the lowest LED cathode voltage and sets the feedback signaling to allow the SMPS to adjust the LED Anode voltage to the appropriate levels for optimum efficiency (3 V operating point for the minimum cathode voltage on any string). An external high voltage diode array such as BAS21LT is recommended.

#### VA

The VA output pin is optional and allows the user to power an external feedback control circuit for setting the common LED Anode operating voltage level.

This output is a buffered voltage signal, which tracks 50% of the internal reference being used to control and set the nominal operating level of the lowest LED Cathode string voltage. An internal source impedance of 250  $\Omega$  is present on this output and the nominal voltage is set to 1.8 V (thermal compensation exists to cancel out the external sensing diode temperature coefficient present on the VCS pin).

#### VC

The VC pin is a buffered voltage signal, which tracks 50% of the voltage level present at the VCS input pin (i.e. the VC voltage is determined by the lowest operating Cathode voltage present on any LED string).

This signal provides a convenient feedback control method for systems which use standalone converters to generate the LED Anode supply voltage (as opposed to a current feedback option). An external suitable resistive divider, at the VC pin, can be used to directly control the feedback input of the standalone converter.

During shutdown mode, the VC pin is forced into high impedance mode, while during normal operation an output source impedance of 360  $\Omega$  is present on the VC pin.

# **Simplified Block Diagram**

Figure 17. Simplified Block Diagram

#### **APPLICATION INFORMATION**

## Operation with Open and Shorted LED

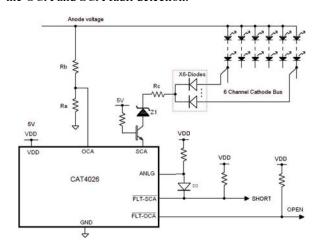

The CAT4026 can detect both open and shorted LED strings through two diode–OR circuits connected respectively to the VCS and SCA pins, as shown in the application circuit in Figure 1.

### Open LED

When one of the channel becomes open or disconnected, its cathode voltage drops to zero pulled down by the current sensing resistor (R1-R6). The lowest cathode voltage is sensed through a diode at the VCS pin (VCS pin is around 0.6 V above the lowest cathode voltage). This causes the CAT4026 current feedback pin (IFB) current to increase to 1 mA and the power supply to increase the anode voltage VOUT until the OCA pin exceeds 1 V threshold and latches on the FLT-OCA fault (the pin is pulled low). At that time, the CAT4026 disables the open channel (corresponding BASE pin voltage goes to GND) and will ignore that channel until the driver is shutdown. The FLT-OCA pin remains low until the CAT4026 goes to shutdown mode or is powered down. The output voltage VOUT now returns to normal operation level where the lowest cathode voltage is around 3.2 V (VCS pin around 3.6 V). The anode voltage is sensed at the OCA pin through a resistor divider (Ra, Rb) as shown in Figure 21.

Figure 18. Open LED at Power-up

Figure 19. Open LED at Power-up, Base Voltages

#### **Shorted LED**

In some cases, the LED string voltage may be different between different strings (channel voltage mismatch). This can be due to LED forward voltage variation or some LEDs becoming shorted in one of the string. One of the string would have a total LED forward voltage lower than other channels. In operation, the cathode voltage of the "shorted" channel will be higher than the other channels causing more power to be dissipated in the external transistor of that channel. Therefore, it is useful to detect this condition and, if needed, derate the LED channel current. The highest cathode voltage is sensed at the SCA pin through a diode-OR network. A zener in series with the diodes, shown in Figure 21, allows to adjust the cathode threshold voltage. Once the SCA pin sinks more than about 1.3 mA, the FLT-SCA fault is triggered and the pin is pulled low. Figure 20 shows a power-up waveform for a threshold voltage at about 45 V. In this example, when the fault is triggered, the LED current decreases from 100 mA to 20 mA.

Figure 20. Shorted LED Channel at Power-up

Figure 21 shows a partial application schematic relative to the OCA and SCA fault detection.

Figure 21. Schematic for Open/Short Detection

## **Unused LED Channels**

For applications that require less than 6 LED channels, the unused channel BASE and RSET pins should be left floating. All the other used channels will operate normally.

## **Example of Ordering Information** (Note 9)

- 7. All packages are RoHS-compliant (Lead-free, Halogen-free).

- 8. The standard lead finish is Matte Tin.

- 9. The device used in the above example is a CAT4026V-T1 (SOIC-28L, Matte Tin, Tape & Reel, 1,000/Reel).

- 10. For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.

- 11. For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

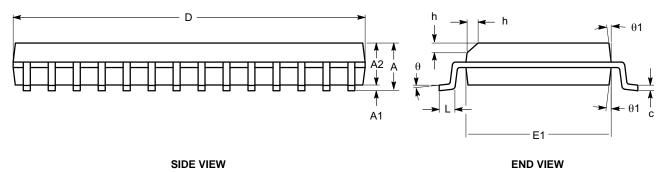

SOIC-28, 300 mils CASE 751BM ISSUE O

**DATE 19 DEC 2008**

| SYMBOL | MIN   | NOM      | MAX   |

|--------|-------|----------|-------|

| А      | 2.35  |          | 2.65  |

| A1     | 0.10  |          | 0.30  |

| A2     | 2.05  |          | 2.55  |

| b      | 0.31  |          | 0.51  |

| С      | 0.20  |          | 0.33  |

| D      | 17.78 |          | 18.03 |

| E      | 10.11 |          | 10.51 |

| E1     | 7.34  |          | 7.60  |

| е      |       | 1.27 BSC |       |

| h      | 0.25  |          | 0.75  |

| L      | 0.40  |          | 1.27  |

| θ      | 0°    |          | 8°    |

| θ1     | 5°    |          | 15°   |

**TOP VIEW**

#### Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MS-013.

| DOCUMENT NUMBER: | 98AON34296E       | Electronic versions are uncontrolled except when accessed directly from the Document Report Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOIC-28, 300 MILS |                                                                                                                                                                             | PAGE 1 OF 1 |  |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales