#### **Outline of User Guide**

3

Introduction to Self-Service PLECS Model Generator:

What is it and What are the benefits

Step by Step Tool Flow

Deploying PLECS Models in Elite Power Simulator and PLECS Stand Alone

#### **Outline of User Guide**

1

Introduction to Self-Service PLECS Model Generator: What is it and What are the benefits

2

Step by Step Tool Flow

3

Deploying PLECS Models in Elite Power Simulator and PLECS Stand Alone

#### **PLECS Basics**

- PLECS is a system level simulator that facilitates the modeling and simulation of complete systems with optimized device models for maximum speed and accuracy.

PLECS is not a SPICE-based circuit simulator, where the focus is on low-level behavior of circuit components.

- Power transistors are treated as simple switches that can be easily configured to demonstrate losses associated with conduction and switching transitions.

- The PLECS models, referred to as "thermal models", are composed of lookup tables for conduction and switching losses, along with a thermal chain in the form of a Cauer or Foster equivalent network.

- During simulation, PLECS interpolates and/or extrapolates using the loss tables to get the bias point conduction and switching losses for the circuit operation. Access the onsemi Elite Power Simulator powered by plegs

www.onsemi.com/elite-power-simulator

#### onsemi's State-of-the-Art PLECS Models:

Typical industry PLECS models are composed of measurement based loss tables that are consistent with datasheets provided by the manufacturer.

#### There are <u>four major problems</u> with this approach:

- 1. The switching energy loss data is dependent on the parasitics of the measurements set ups and circuits.

- 2. The conduction and switching energy loss data is limited and thus is often not dense enough to ensure accurate interpolation and minimal extrapolation by PLECS.

- 3. The loss data is based on nominal semiconductor process conditions only.

- 4. The switching energy loss data comes from datasheet double pulse generated loss data. This means the PLECS models are only valid for hard switching topology simulation. The models are highly inaccurate if used in soft switching topology simulation.

- onsemi's Self-Service PLECS Model Generator (SSPMG) provides solutions to all four problems.

- Ultimate power is delivered to the user to build PLECS models tailored for the user's application.

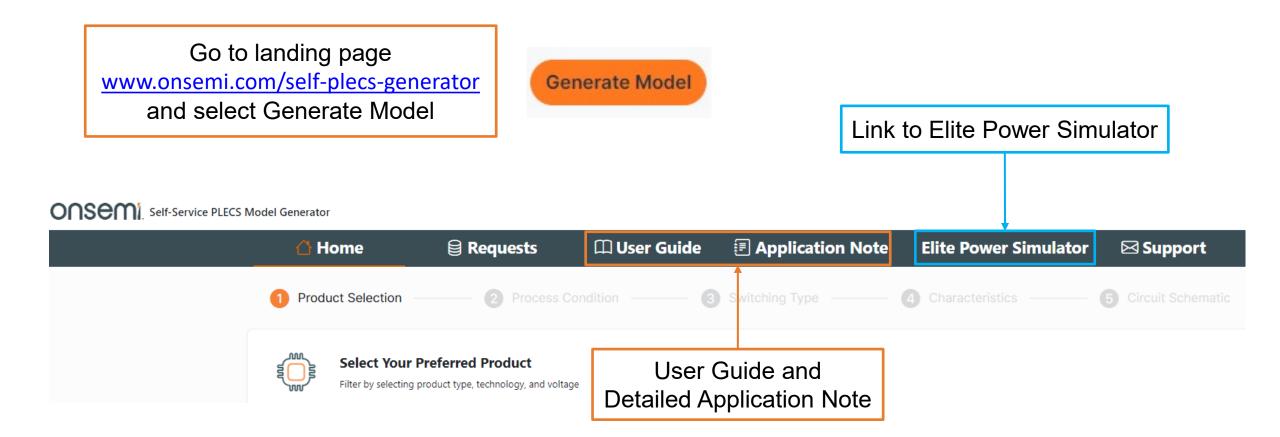

Unleash the power here: <a href="www.onsemi.com/self-plecs-generator">www.onsemi.com/self-plecs-generator</a>

### Measurement Parasitics Influence on Switching Performance

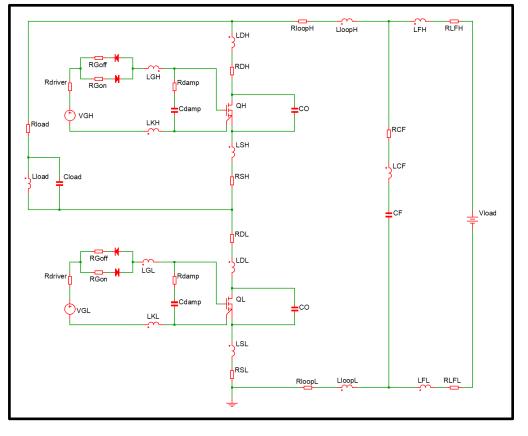

#### **Switching Schematic with Parastics**

#### **Example Datasheet**

| Parameter   | Switching<br>Loss |

|-------------|-------------------|

| Eon [uJ]    | 490               |

| Eoff [uJ]   | 221               |

| Etotal [uJ] | 711               |

#### **Customer Application**

| Parameter   | Switching<br>Loss |

|-------------|-------------------|

| Eon [uJ]    | 415               |

| Eoff [uJ]   | 231               |

| Etotal [uJ] | 646               |

- Crucial to understand that the lab test circuit's passives, parasitics, gate driver performance, etc. all affect losses.

- Where does this leave the user for a PLECS model? The user application will surely have a different environment than any of the component supplier's lab and board setups.

**Loss Table Density and Limits Influence Results**

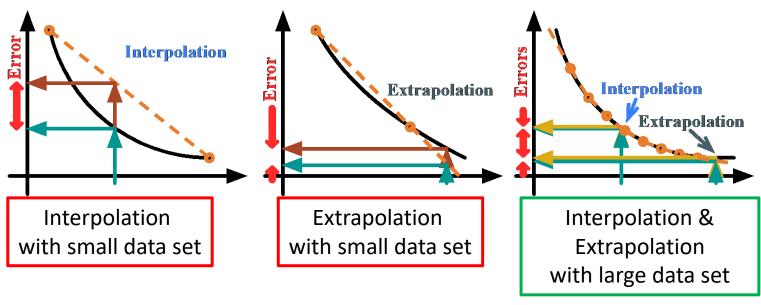

- Datasheet data is often not dense enough to ensure accurate <u>interpolation</u> by PLECS in nonlinear environments.

- Datasheet data limits often do not bound the entire operating range causing highly inaccurate <u>extrapolation</u> by PLECS.

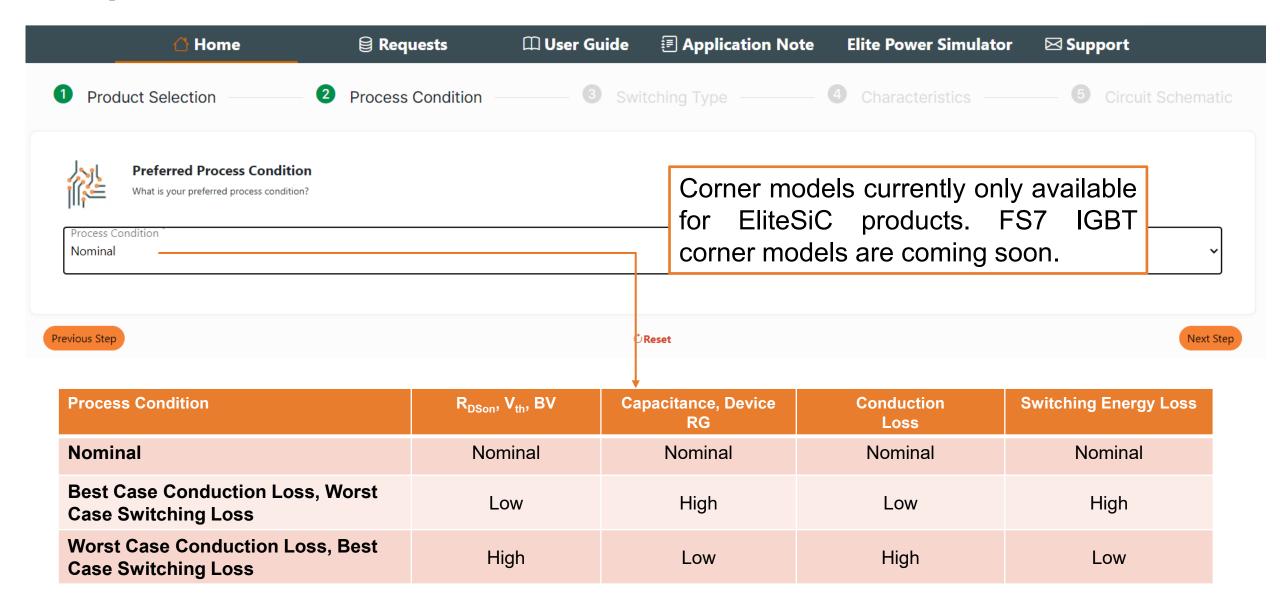

#### **Corner PLECS Models**

- Conventional PLECS models based on measurements are only valid for the typical or nominal process case in manufacturing. onsemi has developed accurate corner PLECS models based on real manufacturing distribution.

- Physics dictates that worst case conduction and switching losses do not happen simultaneously for example.

- Depending on the application, the influence of conduction and switching energy losses on the overall system

performance will vary. The onsemi corner PLECS models provide the user the flexibility to investigate the entire

correlated space.

- Corner models currently only available for EliteSiC products. FS7 IGBT corner models are coming soon.

- Accurate corner and statistical modeling covered in detail in

- SiC MOSFET Corner and Statistical SPICE Model Generation Proceeding of International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 154-147, September 2020

| <b>Process Condition</b>                                | R <sub>DSon</sub> , V <sub>th</sub> , BV | Capacitance,<br>Device RG | Conduction<br>Loss | Switching Energy<br>Loss |

|---------------------------------------------------------|------------------------------------------|---------------------------|--------------------|--------------------------|

| Nominal                                                 | Nominal                                  | Nominal                   | Nominal            | Nominal                  |

| Best Case Conduction Loss, Worst Case<br>Switching Loss | Low                                      | High                      | Low                | High                     |

| Worst Case Conduction Loss, Best Case<br>Switching Loss | High                                     | Low                       | High               | Low                      |

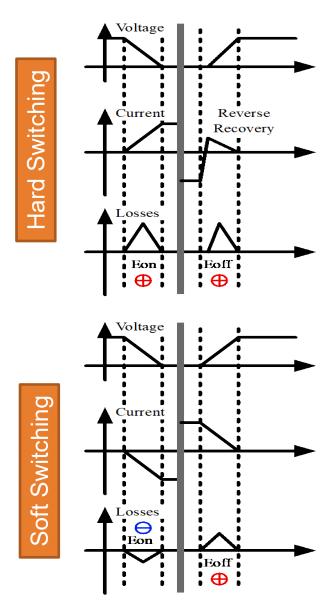

### **Soft Switching Energy Losses**

Soft

Switching

Simulation\*

onsemi provides industry first PLECS models valid for soft switching simulation of applications such as DC-DC LLC and CLLC Resonant, Dual Active Bridge, and Phase Shifted Full Bridge.

The Double Pulse Test is **NOT** representative of Soft Switching. Using double pulse switching energy losses in the simulation of a Soft Switching Topology is highly inaccurate.

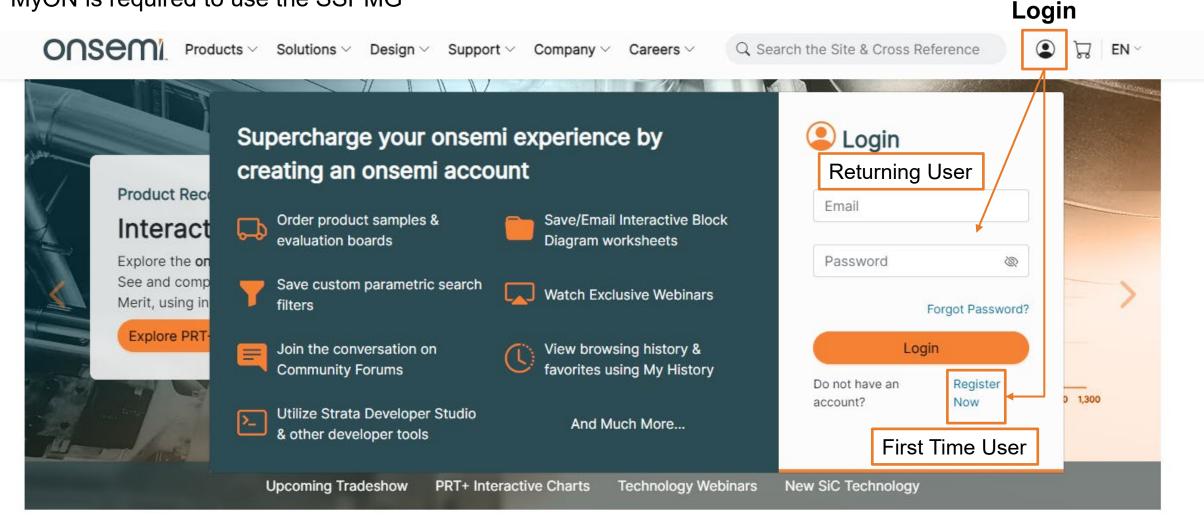

#### **Access SSPMG with MYON Account**

MyON is required to use the SSPMG

**MYON**

#### **Outline of User Guide**

Introduction to Self-Service PLECS Model Generator

What is it and What are the benefits

Step by Step Tool Flow

Deploying PLECS Models in Elite Power Simulator and PLECS Stand Alone

### **Getting Started**

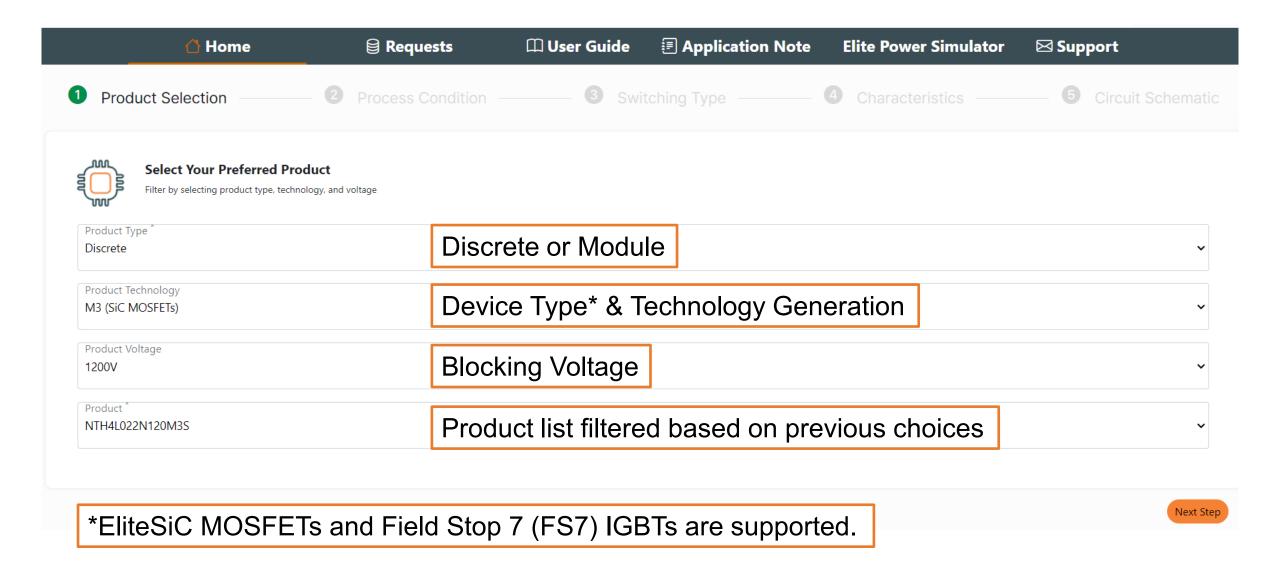

### **Step 1: Select Product**

### **Step 2: Set Process Condition**

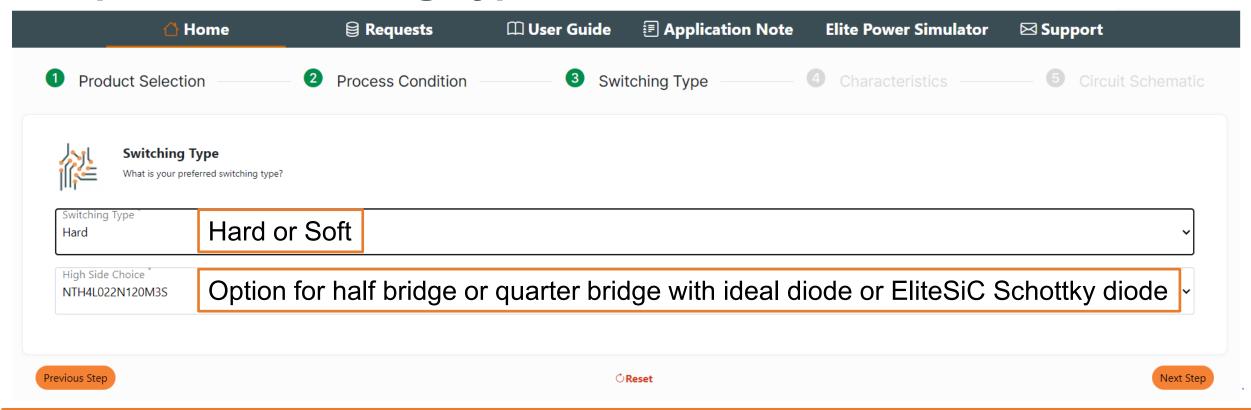

### **Step 3: Set Switching Type**

- Choose the switching type based on the intended application or topology.

- If hard switching chosen, user has choice for high side device to be in half bridge configuration or quarter bridge with ideal diode

or EliteSiC Schottky diode on the high side.

- Example Soft Switching Topologies include DC-DC LLC and CLLC Resonant, Dual Active Bridge, and Phase Shifted Full Bridge.

- Subsequent step 4 "Characteristics" change slightly based on the Switching Type.

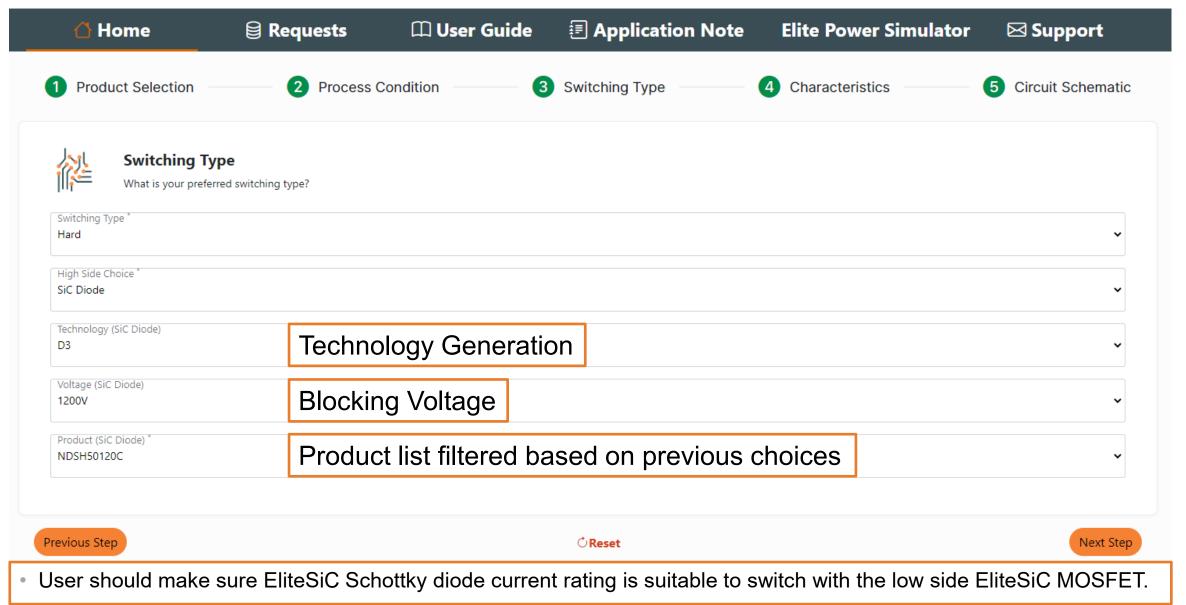

## Step 3: Quarter Bridge with EliteSiC Schottky Diode

onsemi

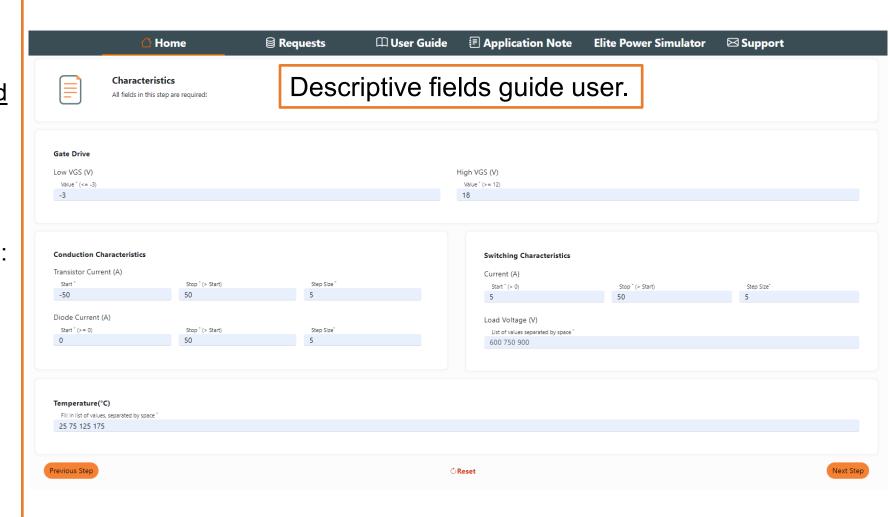

### Step 4: Set Characteristics (Hard Switching)

- Drain current can be in 1<sup>st</sup> and/or 3<sup>rd</sup> quadrant, so positive and/or negative.

- Diode Current is for diode <u>forward</u> conduction mode. Values are given in absolute scale.

- If (Stop-Start)/(Step Size)!= Integer

Then the last point=Stop. Example: Start=1 Stop=9 Step Size=3 Simulated points are: 1 4 7 9

- Gate drive High VGS must be >=10V for SiC MOSFETs/IGBTs to ensure current carrying capability

- Gate drive Low VGS must be

<=0 to ensure full device turn off.</li>

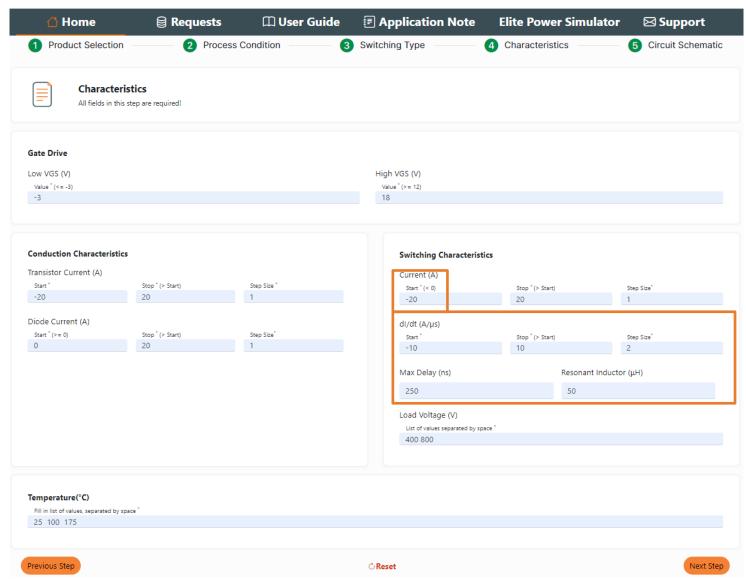

## **Step 4: Set Characteristics (Soft Switching)**

- Soft Switching Changes:

- Drain current can be in 1st and/or 3rd quadrant, so positive and/or negative when a switching event happens

- Soft Switching Additions:

- dl/dt: in the resonant inductor when the switching event happens. This dl/dt is directly linked to the resonant inductor voltage by the Faraday's law of induction E=L\*di/dt. "didt" is a PLECS circuit parameter passed into the PLECS model to evaluate the losses in soft switching.

- Max Delay: maximum dead time allowed between high side and low side switches for the resonant transition to occur

- Resonant Inductor

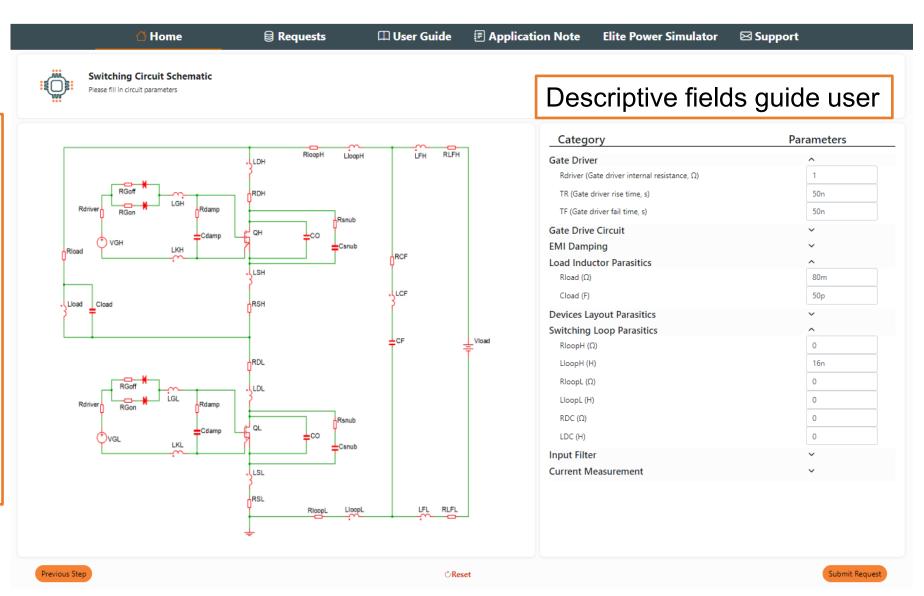

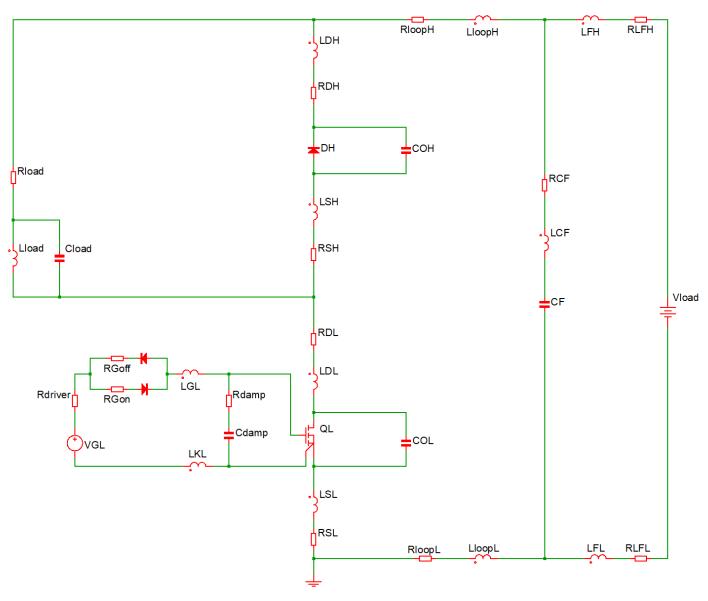

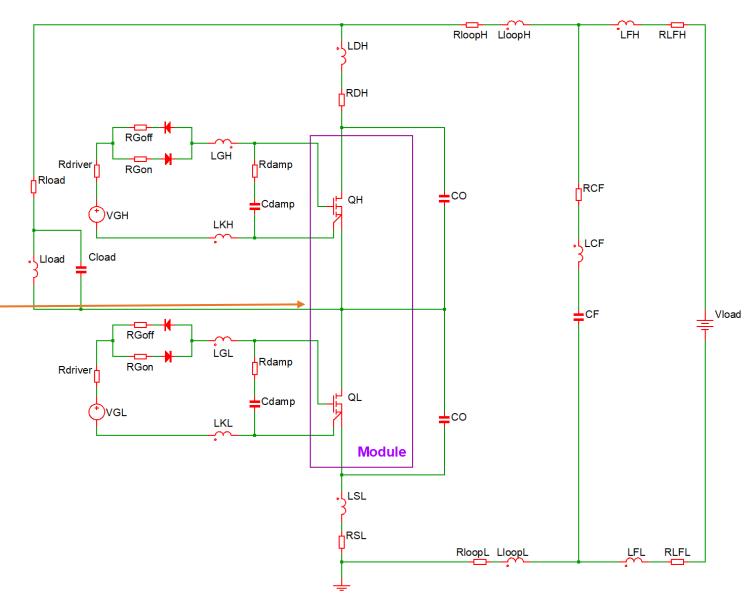

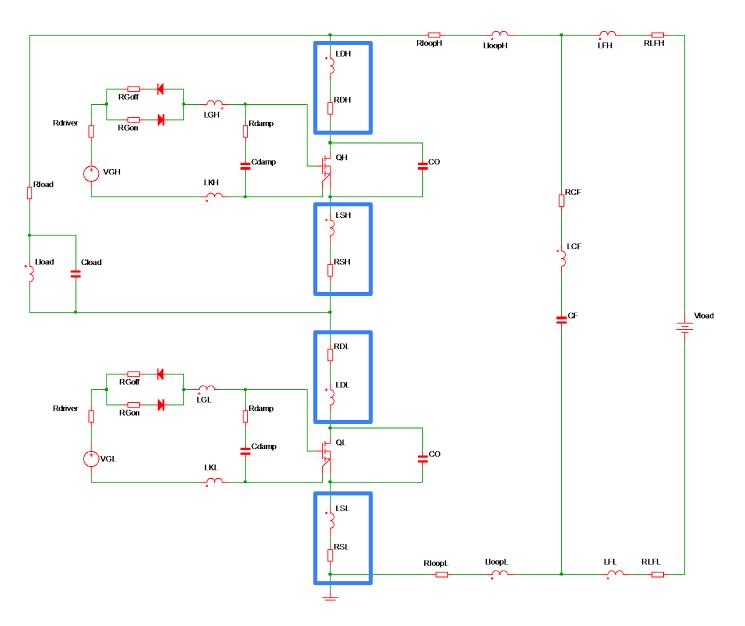

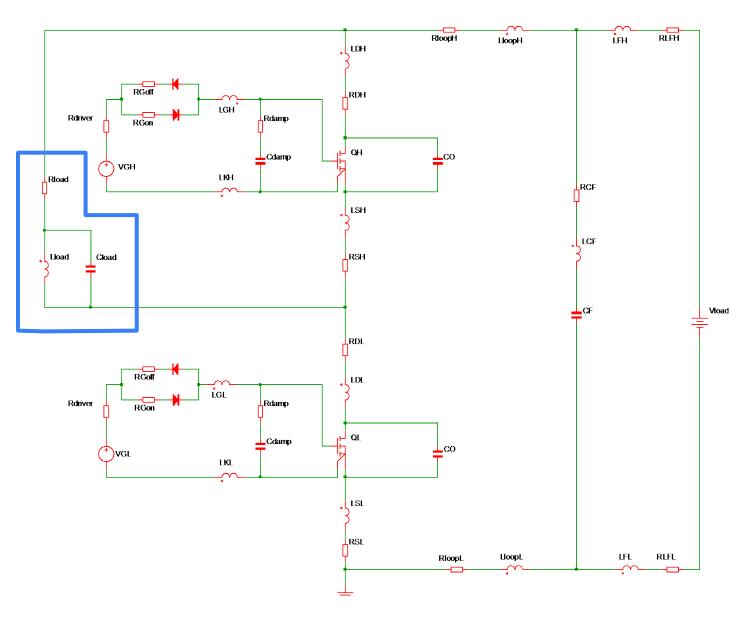

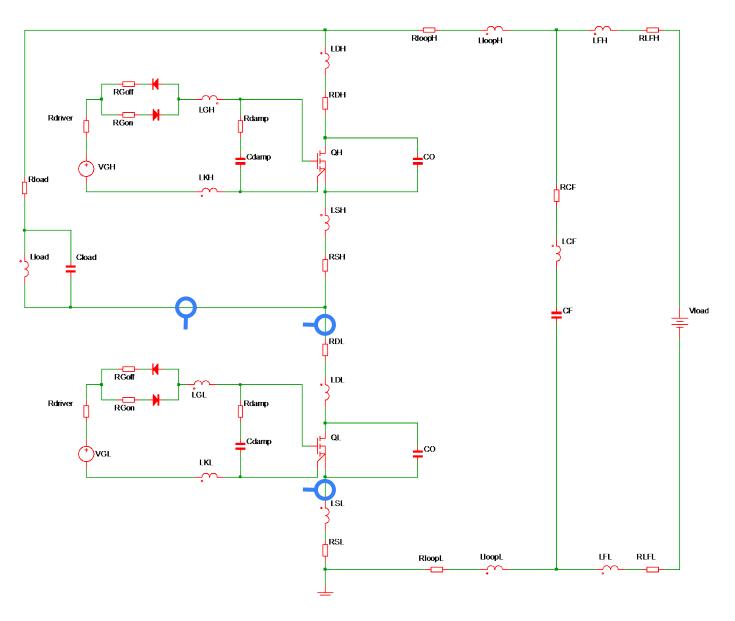

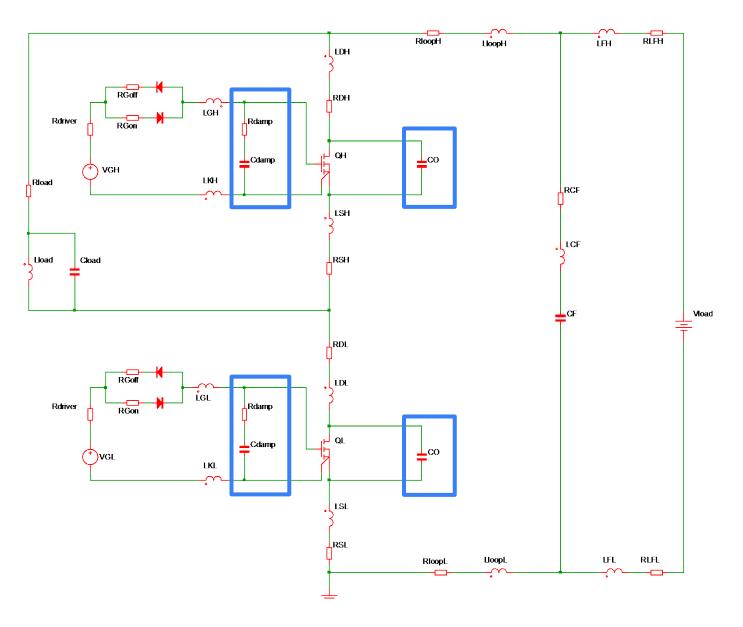

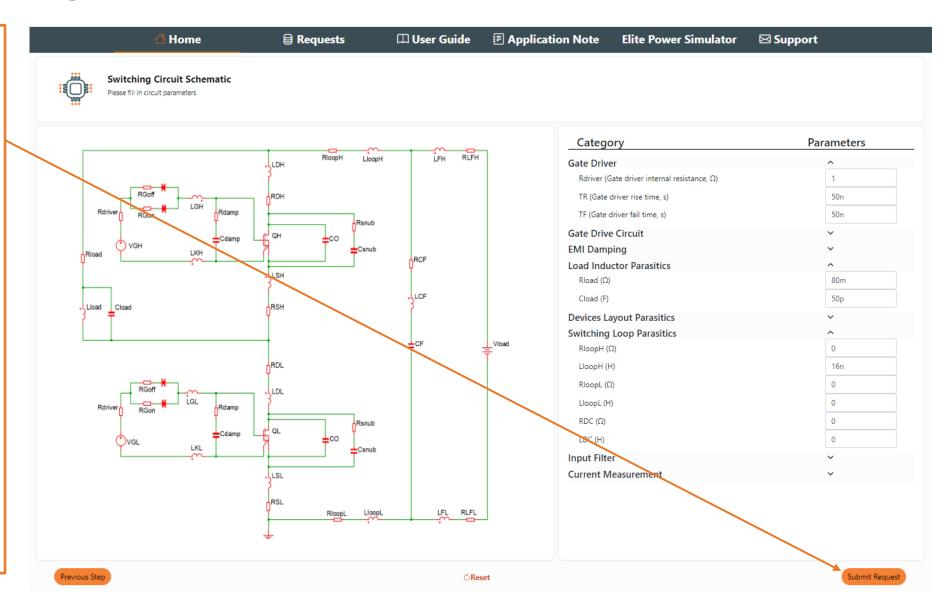

## Step 5: Circuit Schematic (Half Bridge Discrete)

- Table of parameters matches circuit schematic.

- Default parameters are generally 0, allowing user to just enter needed values.

- Min and Max Gate

Resistance parameter

facilitate RG scaling in the PLECS model.

- Gate drive signal can be modeled through Rdriver, TF, and TR.

## **Step 5: Circuit Schematic (Quarter Bridge Discrete)**

- High side choice can be:

- Ideal diode with capacitance=0

- EliteSiC Schottky diode

- Parasitic output capacitor is split into high side (COH) and low side (COL).

### **Step 5: Circuit Schematic (Half Bridge Module)**

- All module parasitics are included in power module SPICE model.

- Remaining parameters are the same as discrete version.

### **Step 5: Circuit Parameters – Full list**

| Gate Drive Circuit                             | ^  |

|------------------------------------------------|----|

| RGoff (Default OFF Gate Resistance, $\Omega$ ) | 2  |

| RGon (Default ON Gate Resistance, $\Omega$ )   | 2  |

| RGoffMIN (Min OFF Gate Resistance, $\Omega$ )  | 2  |

| RGoffMAX (Max OFF Gate Resistance, $\Omega$ )  | 10 |

| RGonMIN (Min ON Gate Resistance, $\Omega$ )    | 2  |

| RGonMAX (Max ON Gate Resistance, $\Omega$ )    | 10 |

| LGH (H)                                        | 5n |

| LKH (H)                                        | 5n |

| LGL (H)                                        | 5n |

| LKL (H)                                        | 5n |

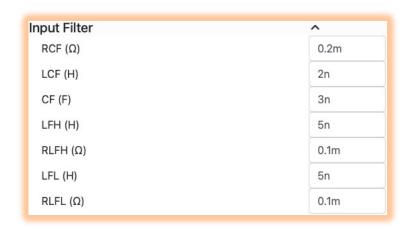

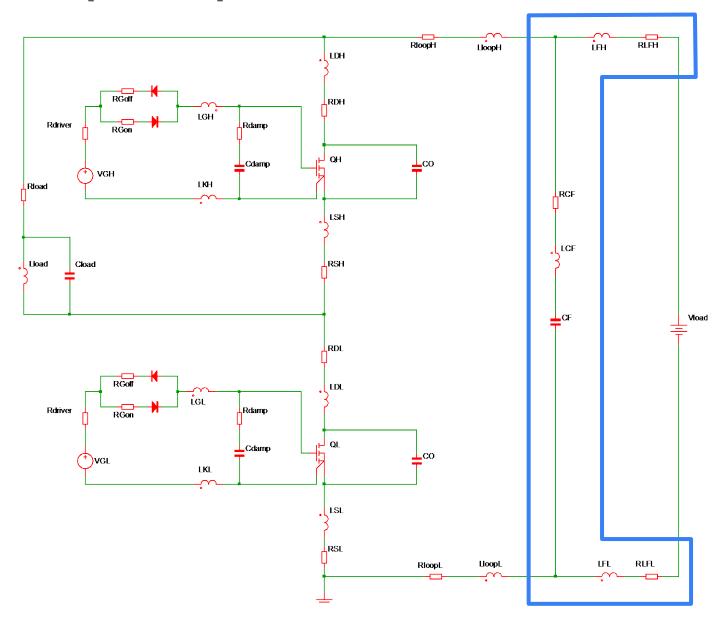

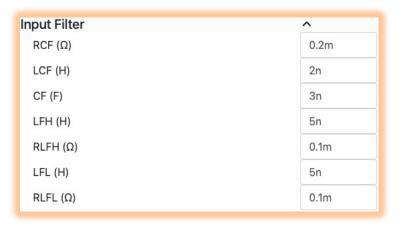

#### **Step 5 : Input Filter Parameters**

LFx (with RLFx as series resistance) is the PCB leakage inductance or a discrete filtering inductor.

The filter capacitor or decoupling capacitor CF includes ESL and ESR parameters.

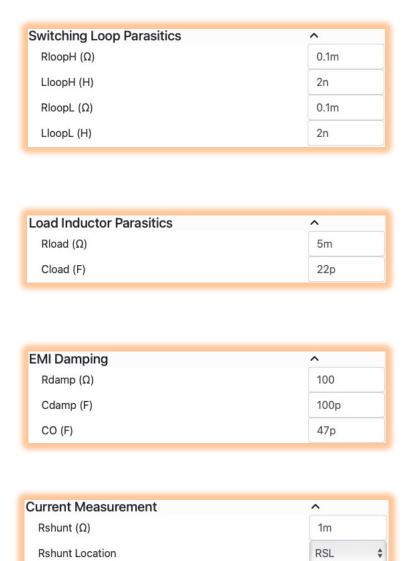

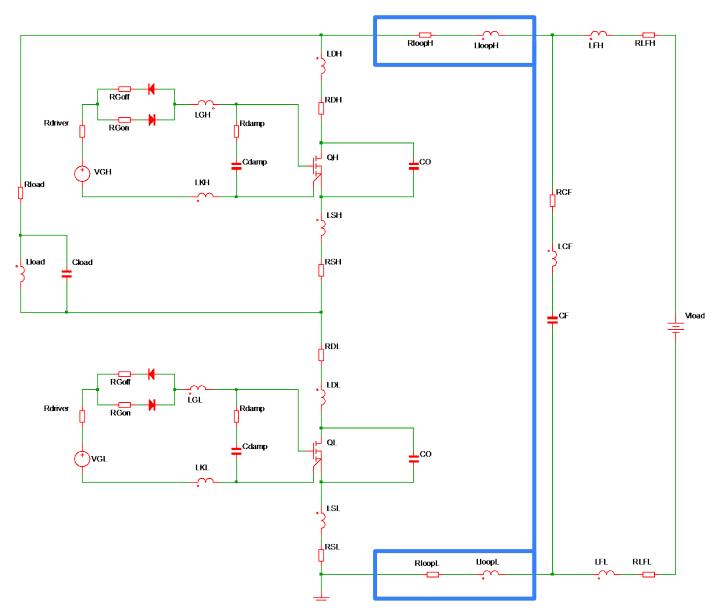

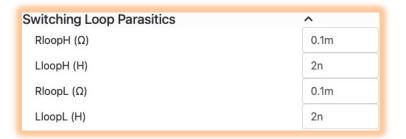

### **Step 5 : Switching Loop Leakage Inductances**

The switching loop inductance (in between the decoupling capacitor and the switching cell) is represented by Lloopx (with Rloopx as series resistance) on the positive and negative branch.

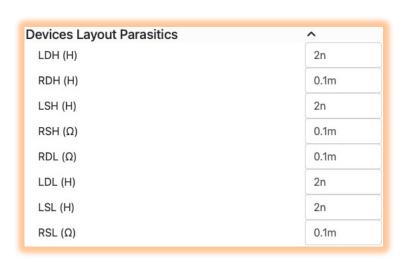

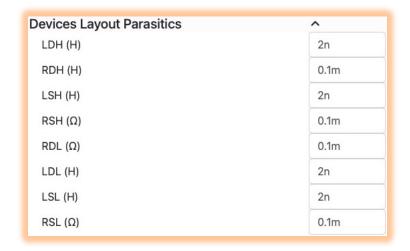

### **Step 5 : Interconnections leakage inductances**

Drain and Source interconnections can also be modeled by inductances (with series resistances). There are 4 in total for the two switching devices.

#### **Step 5 : Load parameters**

In hard switching, results are independent of switching or load inductor. Its value is linked to current value and time.

However, the inductor quality or performances can be defined by its equivalent series resistance and its equivalent parallel parasitic capacitor.

### **Step 5 : Input Filter parameters**

A current sense measurement based on a shunt resistor can be included in the loop in various place :

- in switching device Drain,

- in switching device Source

- in switching inductor

If the shunt is located in the other device drain or source, the interconnection series resistance can be increased accordingly.

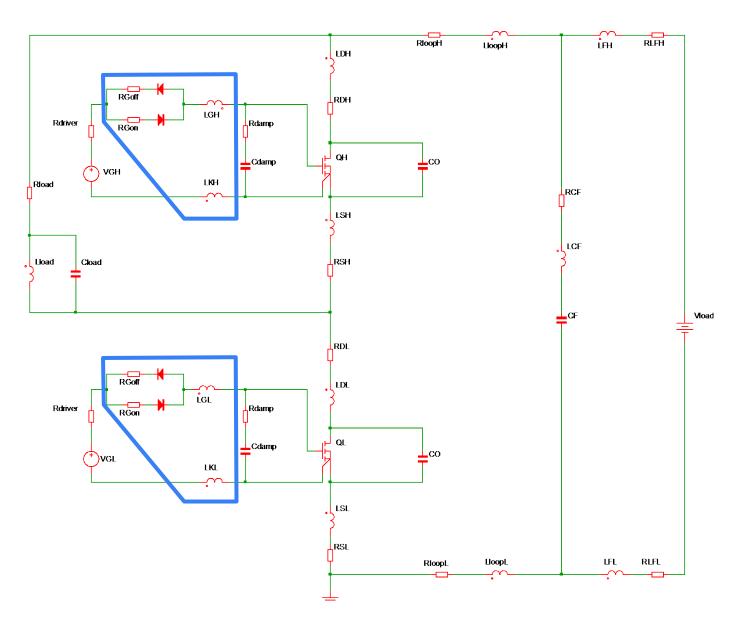

### **Step 5 : Gate Drive Circuit parameters**

| Gate Drive Circuit                             | ^  |

|------------------------------------------------|----|

| RGoff (Default OFF Gate Resistance, $\Omega$ ) | 2  |

| RGon (Default ON Gate Resistance, $\Omega$ )   | 2  |

| RGoffMIN (Min OFF Gate Resistance, $\Omega$ )  | 2  |

| RGoffMAX (Max OFF Gate Resistance, $\Omega$ )  | 10 |

| RGonMIN (Min ON Gate Resistance, $\Omega$ )    | 2  |

| RGonMAX (Max ON Gate Resistance, $\Omega$ )    | 10 |

| LGH (H)                                        | 5n |

| LKH (H)                                        | 5n |

| LGL (H)                                        | 5n |

| LKL (H)                                        | 5n |

The gate drive circuit includes two parasitic inductances LGx and LKx for interconnection and split gate resistors (RGon and RGoff) to control turn-on and turn-off speed.

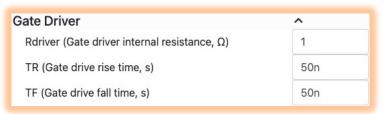

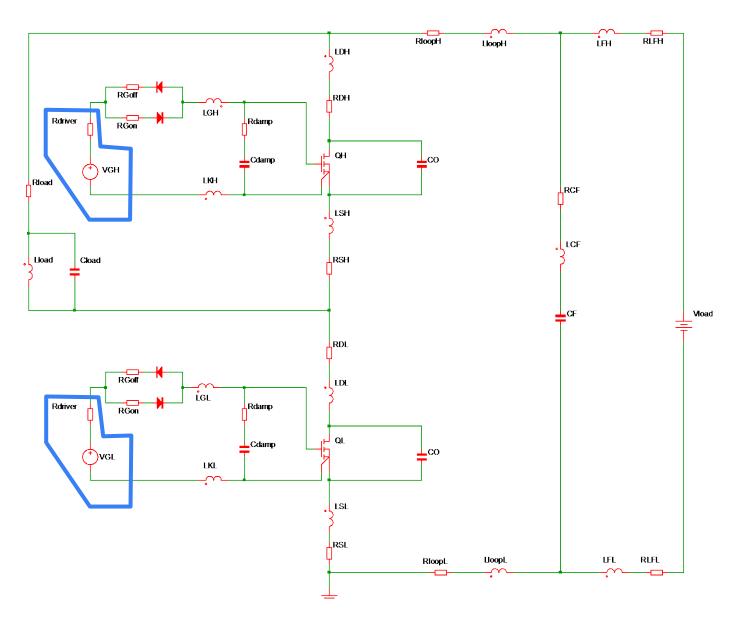

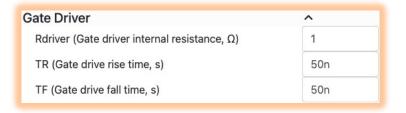

### **Step 5: Driver extra parameters**

The driver is model by a pulse voltage source with Minimum and Maximum (ON and Off) voltage defined in Step 4.

In Step 5, the user defines the Rise (TR) and Fall (TF) times. The user can also give the driver internal resistance value Rdriver.

### **Step 5 : EMI Damping parameters**

For EMI reduction, two damping circuits can be added.

Between Drain to Source, a parallel capacitor linearizes the switching device output capacitor.

Between Gate and (Kelvin) Source, an R-C series damping network will damp the Miller effect ringing.

#### **Step 6: Submit Request**

- From the 5 Circuit

Schematic Tab, once all circuit parameters are entered, Submit Request button becomes active.

- User clicks on Submit Request and is brought to the Request Details page

- Requests take several minutes to complete depending on the density of the input characteristics.

- Modules take longer due to higher complexity compared to discretes.

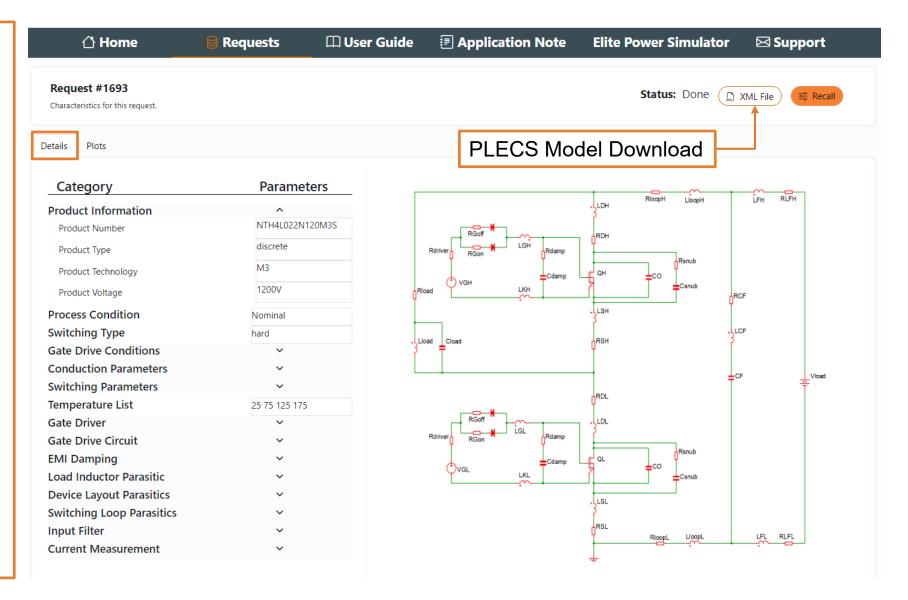

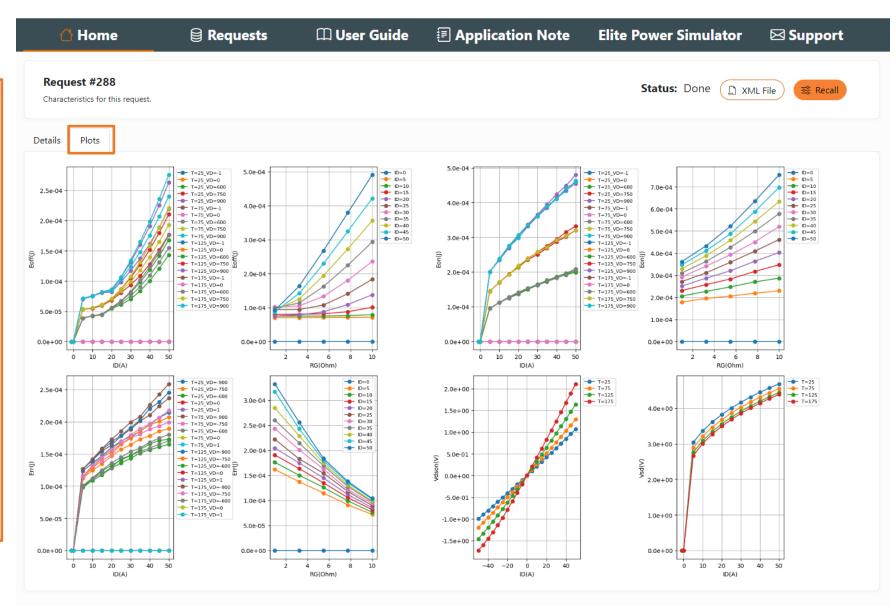

### **Step 7: Review Request Details Page**

- The Request Details page provides user with

- Details of the input parameters

- Plots of the simulation results

- Status field:

- Pending simulation in queue

- Running simulation running

- Done simulation completed

- PLECS Model (XML File) download

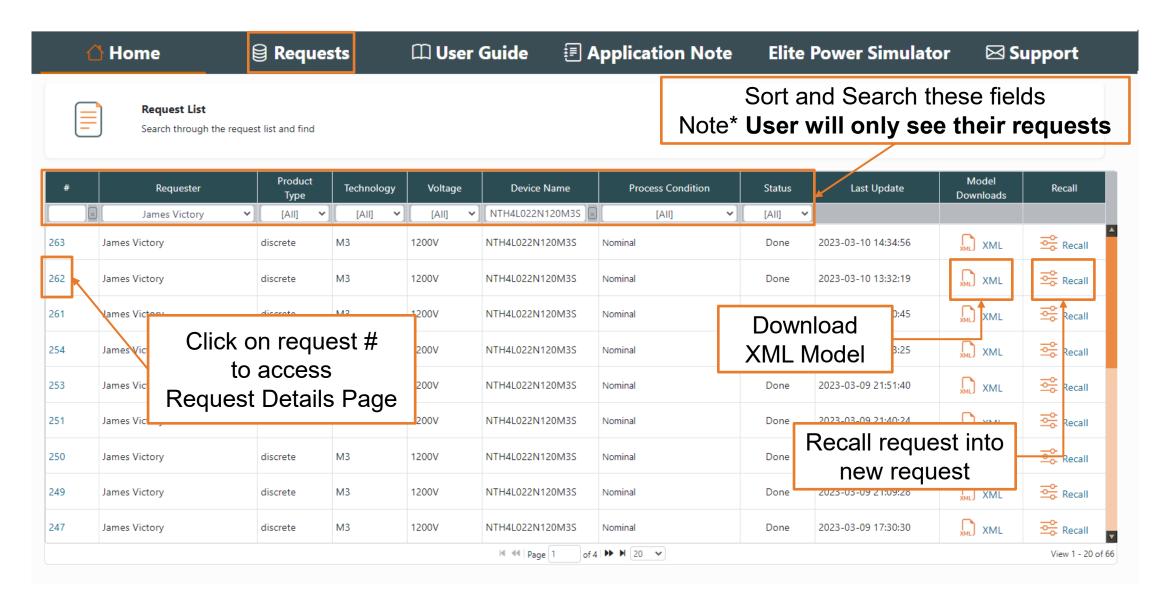

- Recall button: Enable users to recall the current request into a new request where changes can be made before submitting the new request. The current request is maintained.

### Step 7: Review Request Details Page – Plots Tab

- The Plots tab provides users with multiple plots representing the data in the XML file.

- Eoff, Eon, Err vs. ID (current) for different temperatures and voltage @default RG

- Eoff, Eon, Err vs. RG for different currents @maximum temperature and voltage.

- Transistor conduction plot VDSon vs. ID for different temperatures.

- Diode conduction plot Vsd vs.

ID for different temperatures.

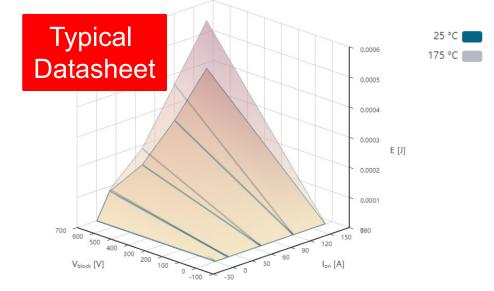

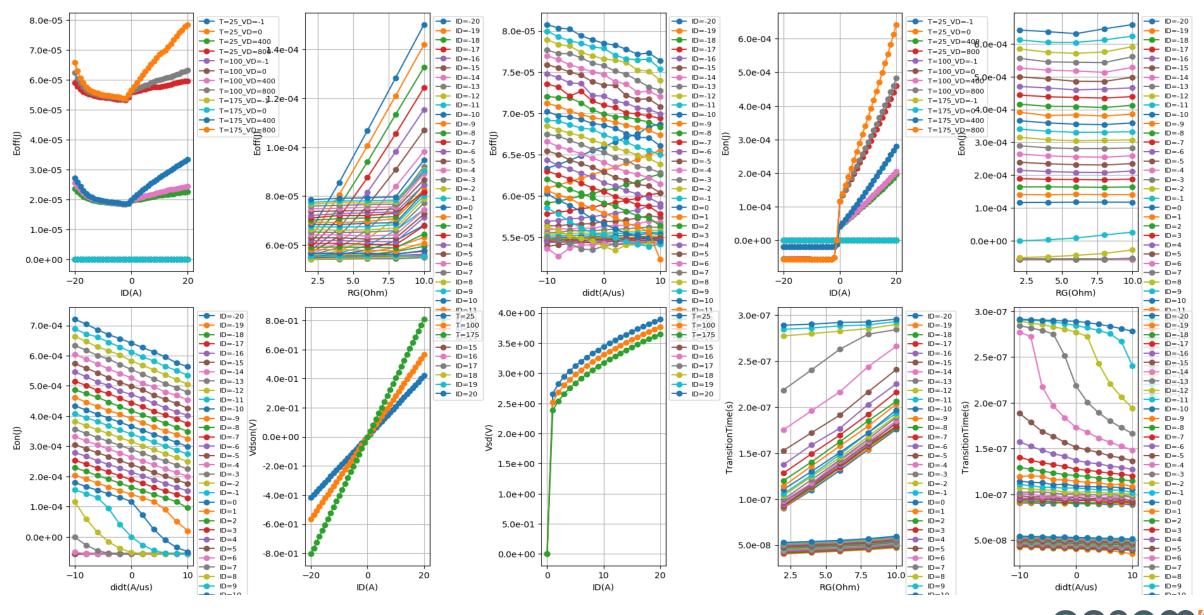

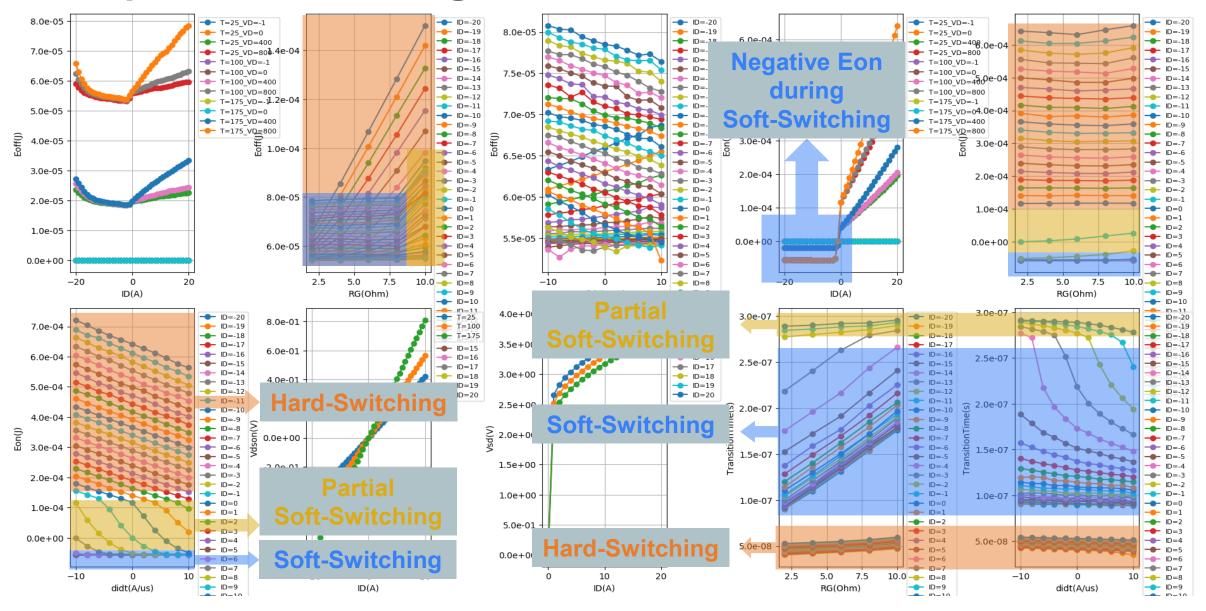

#### **Example Soft Switching Model Results**

#### **Example Soft Switching Model Results**

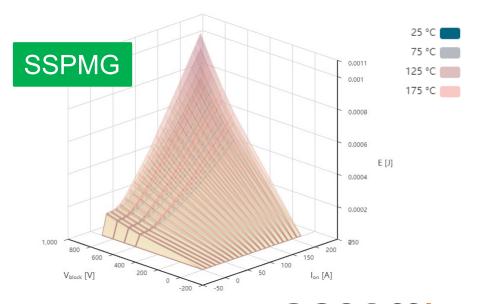

# **Example Soft Switching Model Results: 3D View**

### **Step 8: Review Requests Summary Page**

#### FAQ: Common Causes of SSPMG Failed Runs

- Very small switching current step (<1A) causing very long simulation times while not really improving the accuracy of the table model.

- Switching currents too close to 0 (<1A). In the EOFF extraction, 1% ID point by IEC standard will yield very small curents which can cause extraction errors due to leakage. For example, when ID=0.1A,the 1%ID will be only 1mA,which could be less than the leakage for some high temparture conditions.

- Switching load voltages are too low. Very low Vload can cause errors in the EON extraction, in which we need to measure 3%VDS by IEC standard.

- Switching load voltage too close to the device breakdown voltage BV can cause issues if there is overshoot of VDS in turn off. If the overshoot is higher than BV, the breakdown current will generate strange behaviors.

- For soft switching, users put very small negative current.. For these inputs, there would be only 1 or 2 points for negative current yielding poor results. There should be at least 3 points in the negative current range.

- Iswitch min=-1 Iswitch max=50 Iswitch step=5

- Iswitch\_min=-10 Iswitch\_max=50 Iswitch\_step=5

- Very large dl/dt could cause convergence issues or very strange behavior.

- In general check ranges of parasitics. Unreasonable large inductors, resistors and capacitors can cause issues.

For example, large CLOAD/CO could cause very long turn on/off edge.

#### **Outline of User Guide**

3

Introduction to Self-Service PLECS Mod

What is it and What are the ber

Step by Step Tool Flow

Deploying PLECS Models in Elite Power Simulator and PLECS Stand Alone

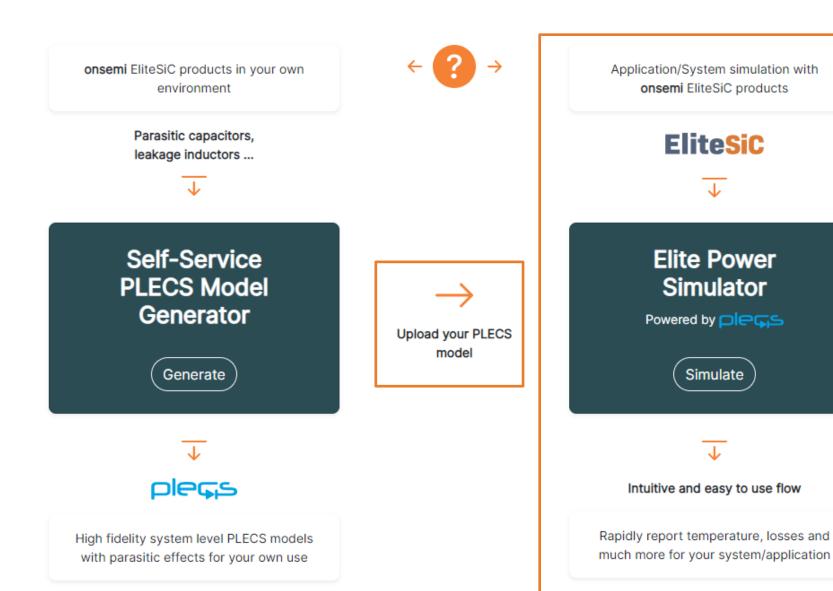

### **Deploying PLECS Models in Elite Power Simulator**

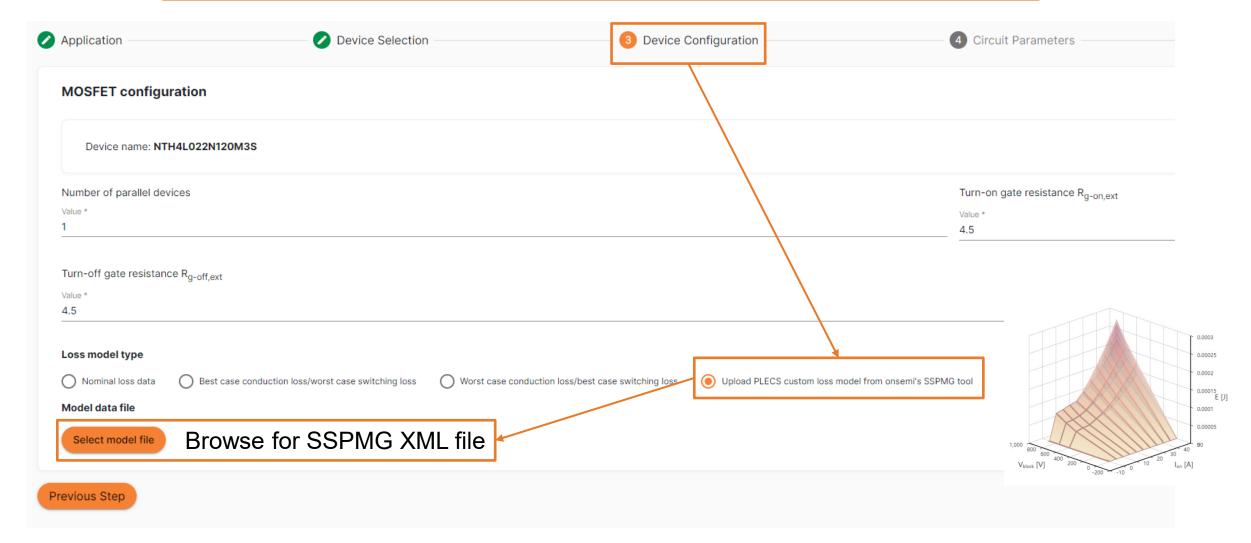

#### Load SSPMG models into Elite Power Simulator

In Device Configuration Tab, user can select to upload SSPMG generated model

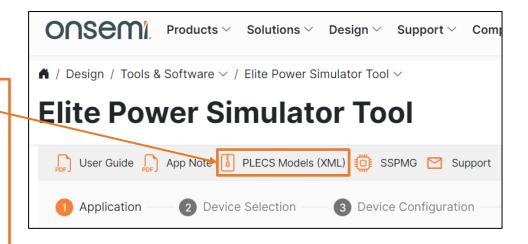

#### Load SSPMG models into PLECS Stand Alone

- First download PLECS models from Elite Power Simulator and follow instructions in "Install.txt" file.

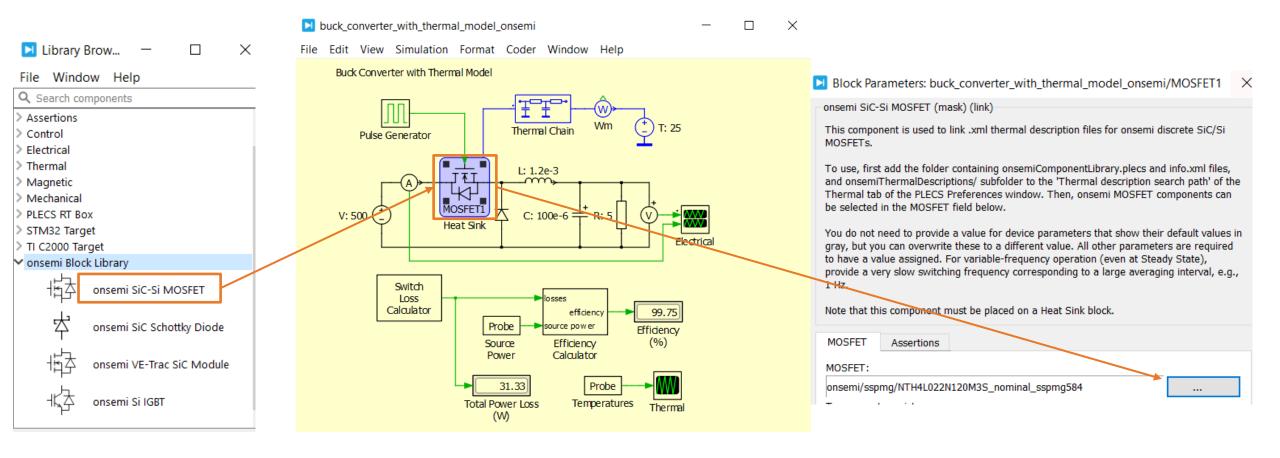

- To install the onsemi SiC library components and corresponding thermal descriptions (XML files), simply add this directory (containing the "onsemiThermalDescriptions/" folder, "onsemiComponentLibrary\_public.plecs" PLECS model, and "info.xml" file) into the list of thermal description search paths in the Thermal tab of the PLECS Preferences window. Click the Refresh button on the left side of the list and click OK to load the onsemi files into PLECS. Then a new entry in the PLECS Library Browser should appear "onsemi Block Library" containing several components that can be dragged into your own circuit models and directly be used with the provided thermal descriptions.

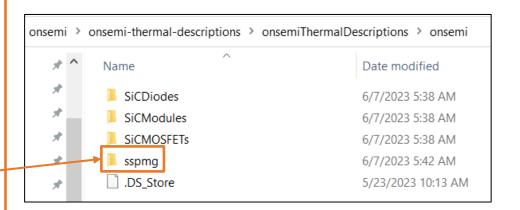

- Create subfolder sspmg here and place SSPMG XML files in this directory. Note folder can be any name.

#### Load SSPMG models into PLECS Stand Alone

- Place an onsemi SiC-Si MOSFET or Si IGBT in PLECS schematic.

- Double click MOSFET/IGBT symbol and browse for SSPMG XML file.

#### Load SSPMG models into PLECS Stand Alone

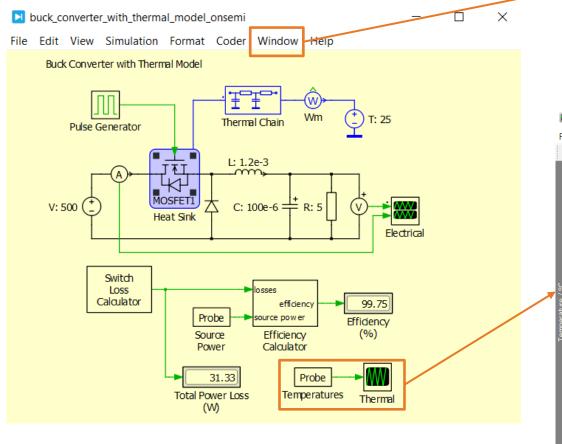

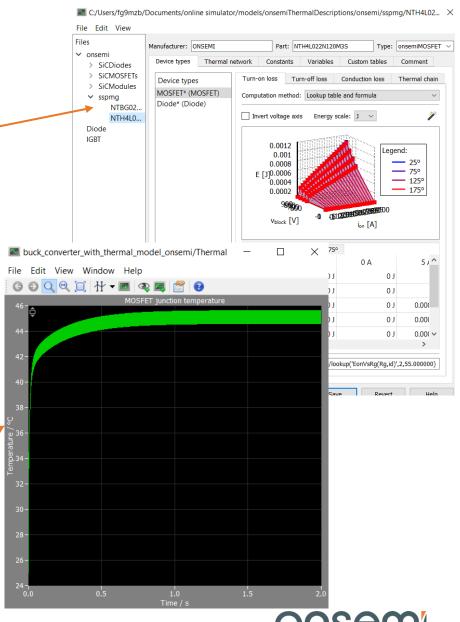

- Review XML data under Window →Thermal Library Browser

- Run simulation

#### **Questions?**

Have questions, comments, or need support with your Self-Service PLECS Model Generator needs? We're here to help! Write us an email at **sspmg@onsemi.com**.

Self-Service PLECS Model Generator:

www.onsemi.com/self-plecs-generator

Elite Power Simulator:

www.onsemi.com/elite-power-simulator

Intelligent Technology. Better Future.

Follow Us @onsemi

www.onsemi.com