# Fully-Configurable Port Companion for Displays

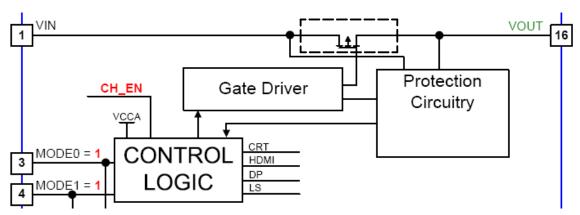

The NLPS591 is a fully-configurable port companion for display applications. The device supports 4 externally selectable modes: (1) 4–Ch autosensing logic level translator mode, (2) CRT mode, (3) HDMI mode and (4) DisplayPort (DP) mode. The device provides switchable power to the connected display and the level shifting necessary for the different display modes. It also provides high–level ESD protection on the connector side.

#### **Features**

- Modes supported:

- ◆ 4-Ch Logic Level Translator (LT) Mode

- CRT Mode

- HDMI Mode

- DisplayPort (DP) Mode

- Wide V<sub>CCA</sub> Operating Range: 1.65 V to 5.5 V

- Wide V<sub>IN</sub> Range: 3.0 to 5.5 V (Power Modes)

- 1.65 V to 5.5 V (Level Translator Mode)

- Low R<sub>DSON</sub> Load Switch:  $300 \text{ m}\Omega$  @  $V_{IN} = 3.3 \text{ V}$

- Soft-start Control for Load Switch

- Protection Provided: Overcurrent, Overvoltage, Backdrive

- Power Consumption: < 10 mW with Load Switch On

- < 1 mW with Load Switch Off

- High Drive VESA-compliant Translator SYNC Level Translators in CRT Mode

- Integrated Pull-ups for the Autosensing Bidirectional Translators

- Low Input Capacitance for Translator Inputs: C<sub>IN</sub> < 10 pF

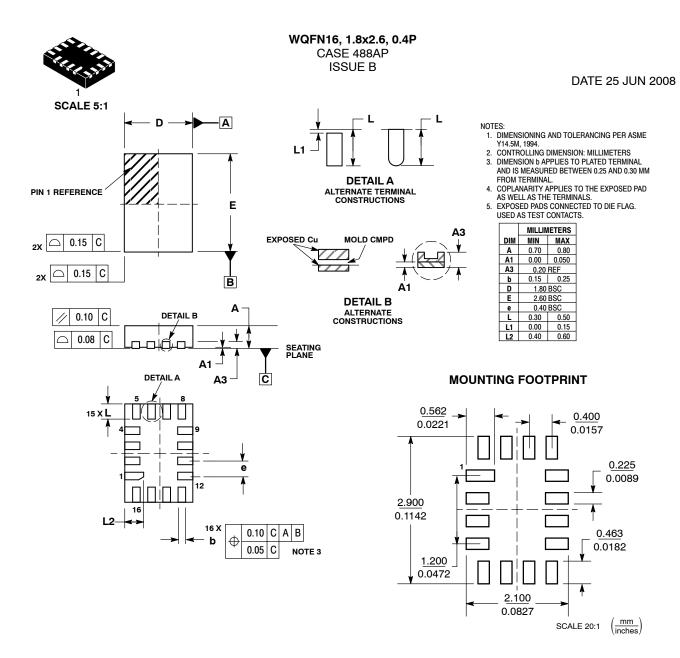

- Small, Space Saving Package

- 1.8 mm x 2.6 mm WQFN16

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

### **Typical Applications**

- · Laptops, Desktops

- Tablets, SmartPhones

#### **Important Information**

- ESD Protection for All Pins

- ♦ Human Body Model (HBM) > 2000 V

## ON Semiconductor®

www.onsemi.com

#### **MARKING DIAGRAM**

AJ = Specific Device Code

M = Date Code

= Pb-Free Package

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NLPS591MNTWG | WQFN16<br>(Pb-Free) | 3000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

1

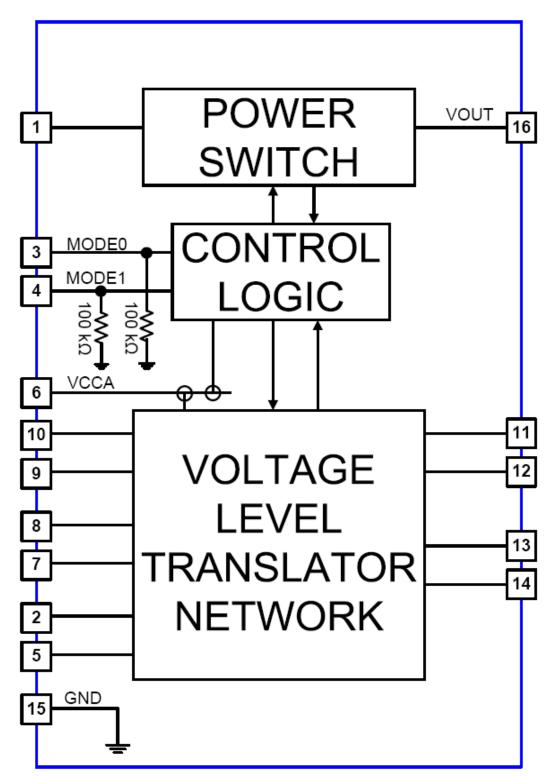

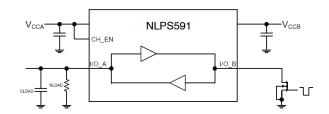

Figure 1. Function Diagram

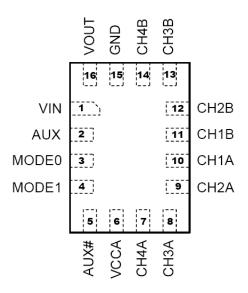

## **PINOUT DIAGRAM**

Figure 2. WQFN16 (Top-Through View)

**Table 1. PIN DESCRIPTIONS**

| Р     | in     |             | Pir          | n Function per Mode |            |            |

|-------|--------|-------------|--------------|---------------------|------------|------------|

| Name  | Number | LT          | DP0          | DP1                 | НОМІ       | CRT        |

| VIN   | 1      | VCC_I2C_1_B | VIN          | VIN                 | VIN        | VIN        |

| AUX   | 2      | VCC_I2C_0_B | AUX_A        | -                   | CEC3V      | -          |

| MODE0 | 3      | "O"         | "0"          | "0"                 | "1"        | "1"        |

| MODE1 | 4      | "O"         | "1"          | "1"                 | "0"        | "1"        |

| AUX#  | 5      | CH_EN       | AUX_A#       | -                   | CH_EN      | CH_EN      |

| VCCA  | 6      | VCCA        | VCCA         | VCCA                | VCCA       | VCCA       |

| CH4A  | 7      | I2C_0_SDA_A | -            | DDC_DATA_A          | DDC_DATA_A | DDC_DATA_A |

| СНЗА  | 8      | I2C_0_SCL_A | -            | DDC_CLK_A           | DDC_CLK_A  | DDC_CLK_A  |

| CH2A  | 9      | I2C_1_SDA_A | HPD_A        | HPD_A               | HPD_A      | HSYNC_A    |

| CH1A  | 10     | I2C_1_SCL_A | -            | -                   | CEC_A      | VSYNC_A    |

| CH1B  | 11     | I2C_1_SCL_B | CA_DET_B = 0 | CA_DET_B = 1        | CEC_B      | VSYNC_B    |

| CH2B  | 12     | I2C_1_SDA_B | HPD_B        | HPD_B               | HPD_B      | HSYNC_B    |

| СНЗВ  | 13     | I2C_0_SCL_B | AUX_B        | DDC_CLK_B           | DDC_CLK_B  | DDC_CLK_B  |

| CH4B  | 14     | I2C_0_SDA_B | AUX_B#       | DDC_DATA_B          | DDC_DATA_B | DDC_DATA_B |

| GND   | 15/EP* | GND         | GND          | GND                 | GND        | GND        |

| VOUT  | 16     | -           | VOUT         | VOUT                | VOUT       | VOUT       |

<sup>\*</sup> EP – Exposed Pad for QFN–16 Package is connected to GND.

## **Table 2. MODE FUNCTION TABLE**

| Inp   | out   |                                 |

|-------|-------|---------------------------------|

| MODE0 | MODE1 | Operating Mode                  |

| 0     | 0     | Level Translator – LT (Default) |

| 0     | 1     | DisplayPort – DP                |

| 1     | 0     | HDMI                            |

| 1     | 1     | CRT                             |

#### **OPERATING MODES**

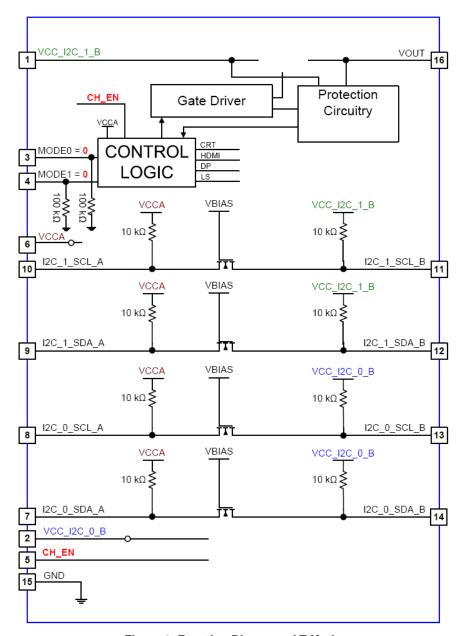

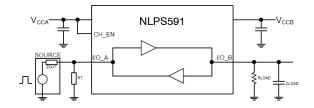

#### **Level Translator Mode – LT (Default Mode)**

When MODE0 = 0 and MODE1 = 0, the NLPS591 enters level translator mode. In this mode, the power switch is always off.

When CH\_EN = 1, the device is configured as an autosensing 4-channel bidirectional logic level translator.

The function diagram is shown below. The A-side I/Os are referred to VCCA (pin 6). The B-side I/Os are referred to either VCC\_I2C\_1\_B (pin 1) or VCC\_I2C\_0\_B (pin 2).

When CH\_EN = 0, the 4-ch level translator is disabled, and the I/O pins (pins 7, 8, 9, 10, 11,12, 13, 14) go into high-impedance.

Figure 3. Function Diagram - LT Mode

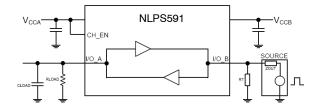

#### **DP Mode**

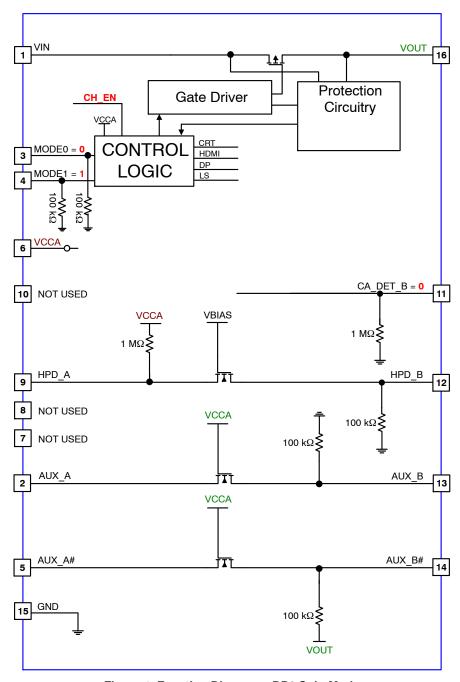

When MODE0 = 0 and MODE1 = 1, the NLPS591 enters DP (DisplayPort) mode. The device is configured as a DP-compliant logic level translator for the control signals. A power switch provides power to the connected display. An unidirectional translator for HPD is provided.

A CA\_DET\_B input is provided to detect the use of an HDMI dongle. When there is no HDMI dongle attached (CA\_DET\_B = 0), the device goes into DP0 sub-mode, where AUX and AUX# signals are passed. The function diagram is shown below.

#### DP0 Sub-Mode

Figure 4. Function Diagram - DP0 Sub-Mode

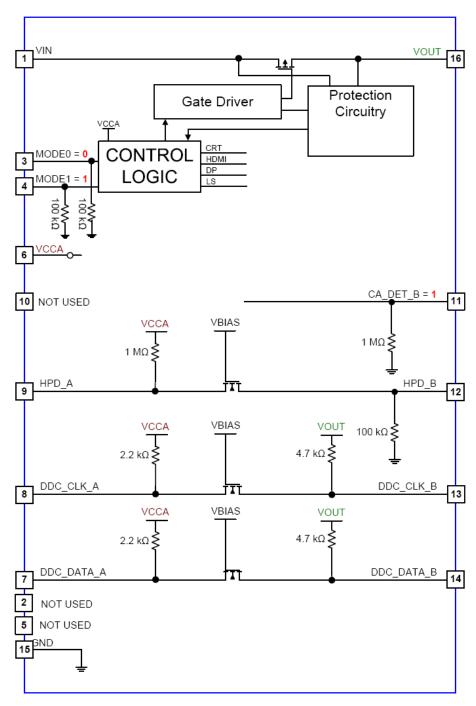

When an HDMI dongle is attached (CA\_DET\_B = 1), the device enters DP1 sub-mode. Two autosensing bidirectional logic level translators for DDC signals are

provided. A-side I/Os are referred to VCCA (pin 1), while B-side I/Os are referred to VOUT (pin 16). The function diagram is shown below.

#### DP1 Sub-Mode

Figure 5. Function Diagram - DP1 Sub-Mode

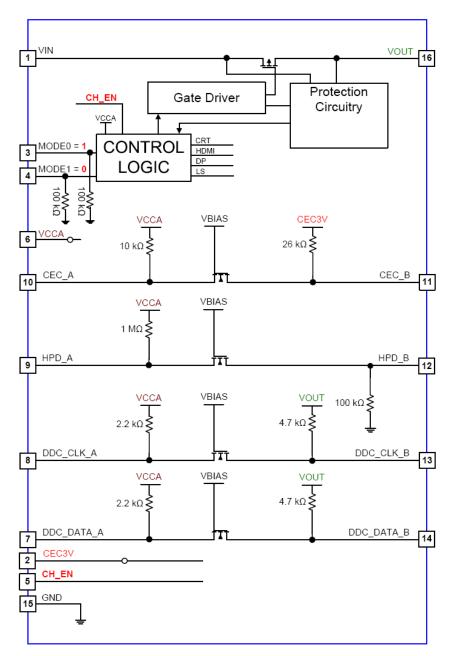

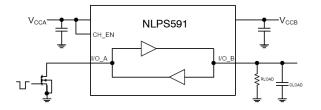

#### **HDMI Mode**

When MODE0 = 1 and MODE1 = 0, the NLPS591 enters HDMI mode.

When CH\_EN = 1, the device is configured as a HDMI-compliant logic level translator for the control signals. An unidirectional translator for HPD and three autosensing bidirectional level translators for the DDC and CEC signals are provided. A-side I/Os are referred to

VCCA (pin 1), while B-side I/Os, except for CEC\_B, are referred to VOUT (pin 16). A CEC3V (pin 2) input is also provided to power the connector-side pull-up of the CEC translator. A power switch provides power to the connected display. The function diagram is shown below.

When CH\_EN = 0, the device is disabled. The power switch turns off, VOUT is pulled to GND, and the I/O pins (pins 7, 8, 9, 10, 11,12, 13, 14) go into high-impedance.

Figure 6. Function Diagram - HDMI Mode

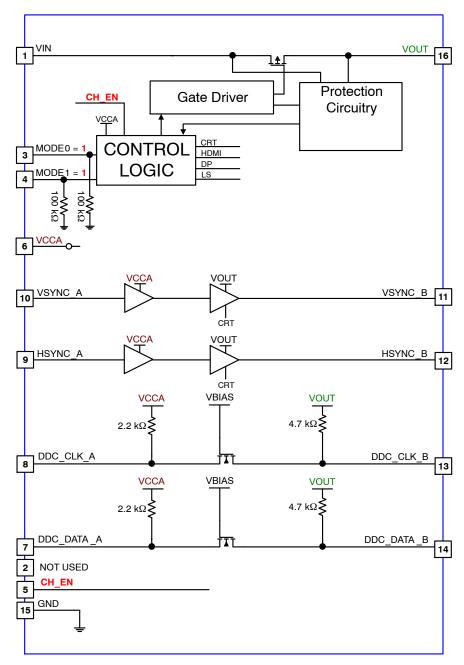

#### **CRT Mode**

When MODE0 = 1 and MODE1 = 1, the NLPS591 enters CRT mode.

When CH\_EN = 1, the device is configured as a VESA-compliant logic level translator for the CRT control signals. Two unidirectional high-drive translators for the HSYNC and VSYNC signals and two autosensing

bidirectional level translators are provided for the DDC signals. A power switch provides power to the connected display. The function diagram is shown below.

When CH\_EN = 0, the device is disabled. The power switch turns off, VOUT is pulled to GND and the I/O pins (pins 7, 8, 9, 10, 11,12, 13, 14) go into high-impedance.

Figure 7. Function Diagram - CRT Mode

#### **Power Switch**

A power switch is provided for CRT, HDMI and DP modes, but not for LT mode. The power switch is used to provide power to a connected display. In the CRT and HDMI modes, the power may be turned on or off under user control through the CH\_EN pin. When the power switch starts turning on, VOUT is held LOW momentarily before VOUT is released and follows VIN.

In the DP Mode, the CH\_EN is not available, hence, the power switch is always on.

The output (VOUT) of the power switch is current-limited. The switch is protected against extended exposure to high current flows by a thermal shutdown protection circuit. The switch is back-drive protected preventing reverse current flow from VOUT to VIN.

Figure 8. Function Diagram - Power Switch

**Table 3. MAXIMUM RATINGS**

| Symbol                                        | Parameter                                                                         | Value                                        | Condition                        | Unit |

|-----------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------|----------------------------------|------|

| VIN / CEC3V /<br>VCC_I2C_0_B /<br>VCC_I2C_1_B | DC Supply Voltage                                                                 | -0.5 to +7.0                                 |                                  | V    |

| V <sub>CCA</sub>                              | Logic DC Supply Voltage                                                           | −0.5 to +7.0                                 |                                  | V    |

| V <sub>OUT</sub>                              | Load Switch Output Voltage                                                        | −0.5 to +7.0                                 |                                  | V    |

| V <sub>IOA</sub>                              | A-Side DC Input/Output Voltage (Power Down)                                       | -0.5 to +7.0                                 | V <sub>CCA</sub> = 0 V           | V    |

|                                               | (Active)                                                                          | -0.5 to (V <sub>CCA</sub> + 0.5)             | V <sub>CCA</sub> Active          |      |

| V <sub>IOB</sub>                              | B-Side DC Input/Output Voltage (Power Down)                                       | −0.5 to +7.0                                 | V <sub>CCB</sub> (Note 1) = 0 V  | V    |

|                                               | (Active)                                                                          | -0.5 to (V <sub>CCB</sub><br>(Note 1) + 0.5) | V <sub>CCB</sub> (Note 1) Active |      |

| T <sub>STG</sub>                              | Storage Temperature                                                               | -65 to +150                                  |                                  | °C   |

| ESD                                           | ESD Protection<br>Connector–Side (VOUT, CH1B, CH2B, CH3B, CH4B)<br>All Other Pins | 8<br>2                                       |                                  | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 4. RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                                   | Min  | Max                       | Unit |

|------------------|---------------------------------------------|------|---------------------------|------|

| $V_{CCA}$        | Logic DC Supply Voltage                     | 1.65 | 5.5                       | V    |

| V <sub>IN</sub>  | Load Switch Input Voltage LT Mode           | 1.65 | 5.5                       | V    |

|                  | CRT / HDMI Mode                             | 4.5  | 5.5                       |      |

|                  | DP Mode                                     | 3.0  | 3.6                       |      |

| V <sub>OUT</sub> | Load Switch Output Voltage                  | GND  | 5.5                       | V    |

| $V_{IOA}$        | A-Side DC Input/Output Voltage (Power Down) | GND  | 5.5                       | V    |

|                  | (Active)                                    | GND  | V <sub>CCA</sub>          |      |

| V <sub>IOB</sub> | B-Side DC Input/Output Voltage (Power Down) | GND  | 5.5                       | V    |

|                  | (Active)                                    | GND  | V <sub>CCB</sub> (Note 1) |      |

| Δt/ΔV            | Input Transition Rise and Fall Rate         |      | 100                       | ns/V |

|                  | Control Input                               |      | 10                        |      |

| T <sub>A</sub>   | Operating Temperature Range                 | -40  | +85                       | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

1. V<sub>CCB</sub> refers to the supply powering the translator B–side I/O pin. This supply could be VOUT, CEC3V, VCC\_I2C\_0\_B or VCC\_I2C\_1\_B, depending on the device function mode.

Table 5. DC ELECTRICAL CHARACTERISTICS ( $V_{CCA} = 1.65 \text{ V}$  to 5.5 V,  $V_{CCB}$  (Note 2) = 1.65 V to 5.5 V, unless otherwise specified)

|                                           |                                                                                                                                      |                                                                                      | -40°C to +85°C         |                     |                        |      |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------|---------------------|------------------------|------|

| Symbol                                    | Parameter                                                                                                                            | Test Conditions (Note 2)                                                             | Min                    | Typ<br>(Notes 2, 3) | Max                    | Unit |

| CONTRO                                    | L PINS - MODE0, MODE1                                                                                                                |                                                                                      |                        |                     |                        |      |

| $V_{IH}$                                  | Input HIGH Voltage                                                                                                                   |                                                                                      | 2/3 * V <sub>CCA</sub> |                     |                        | V    |

| V <sub>IL</sub>                           | Input LOW Voltage                                                                                                                    |                                                                                      |                        |                     | 1/3 * V <sub>CCA</sub> | V    |

| I <sub>IH</sub>                           | Input HIGH Leakage                                                                                                                   | VCCA = 5.5 V                                                                         |                        | 55                  | 70                     | μΑ   |

| Ι <sub>ΙL</sub>                           | Input LOW Leakage                                                                                                                    | VCCA = 5.5 V                                                                         |                        |                     | 1                      | μΑ   |

| CONTRO                                    | L PIN – AUX# (CH_EN in LT, HDMI a                                                                                                    | nd CRT Modes)                                                                        |                        |                     |                        |      |

| $V_{IH}$                                  | Input HIGH Voltage                                                                                                                   |                                                                                      | 2/3 * V <sub>CCA</sub> |                     |                        | V    |

| $V_{IL}$                                  | Input LOW Voltage                                                                                                                    |                                                                                      |                        |                     | 1/3 * V <sub>CCA</sub> | V    |

| I <sub>I</sub> L                          | Input Leakage Current                                                                                                                | VCCA = 5.5 V                                                                         |                        |                     | ±1                     | μΑ   |

| POWER S                                   | SWITCH (VIN = 3.0 V to 5.5 V)                                                                                                        |                                                                                      |                        |                     |                        |      |

| R <sub>DSON</sub>                         | Static ON-State Resistance                                                                                                           | VIN = 5 V, I <sub>LOAD</sub> < 300 mA                                                |                        |                     | 240                    | mΩ   |

|                                           |                                                                                                                                      | VIN = 3.3 V, I <sub>LOAD</sub> < 300 mA                                              |                        |                     | 300                    |      |

| t <sub>R</sub>                            | Output Rise Time                                                                                                                     | VIN = 5 V, I <sub>LOAD</sub> = 100 mA                                                | 0.2                    |                     | 1.0                    | ms   |

| tϝ                                        | Output Fall Time                                                                                                                     | VIN = 5 V, I <sub>LOAD</sub> = 100 mA                                                |                        |                     | 0.01                   | ms   |

| t <sub>ON</sub>                           | Gate Turn-On Time                                                                                                                    | VIN = 5 V, From VIN applied to VOUT = 10% of fully on                                |                        | 0.5                 | 1.5                    | ms   |

|                                           |                                                                                                                                      | VIN = 3.3 V, From VIN applied to VOUT = 10% of fully on                              |                        |                     | 1.7                    |      |

| I <sub>REV</sub>                          | Reverse Current Protection                                                                                                           | V <sub>CCA</sub> ≥ 1.65 V, Switch Enabled, No<br>Load, (VOUT – VIN) ≥ 0.5 V (Note 4) |                        |                     | 40                     | μΑ   |

| I <sub>LIM</sub>                          | Current Limit Threshold                                                                                                              | ΔV <sub>SW</sub> = 400 mV (Note 5)                                                   | 0.45                   |                     | 0.8                    | Α    |

| t <sub>DET</sub>                          | Response Time to Short Circuit                                                                                                       | (Note 6)                                                                             |                        | 5                   |                        | μS   |

| T <sub>SHUT</sub>                         | Thermal Shutdown                                                                                                                     | Shutdown Threshold, TRIP Temperature                                                 |                        | 140                 |                        | °C   |

|                                           |                                                                                                                                      | Hysteresis                                                                           |                        | 12                  |                        |      |

| V <sub>OVP</sub>                          | Output Overvoltage Protection                                                                                                        | Trip Voltage                                                                         |                        | 5.9                 |                        | ٧    |

|                                           |                                                                                                                                      | Hysteresis                                                                           |                        | 0.3                 |                        | 1    |

| CRT and I<br>IDMI Mod<br>V <sub>IHA</sub> | (I <sup>2</sup> C Translator Channels) DP1 Modes (DDC Translator Channele (CEC and DDC Translator Channele A Side Input High Voltage |                                                                                      | V <sub>CCA</sub> – 0.4 |                     |                        | V    |

| $V_{IHB}$                                 | B Side Input High Voltage                                                                                                            |                                                                                      | V <sub>CCB</sub> – 0.4 |                     |                        | V    |

| $V_{ILA}$                                 | A Side Input Low Voltage                                                                                                             |                                                                                      |                        |                     | 0.15                   | V    |

| $V_{ILB}$                                 | B Side Input Low Voltage                                                                                                             |                                                                                      |                        |                     | 0.15                   | V    |

| $V_{OHA}$                                 | A Side Output High Voltage                                                                                                           | A Side Source Current = 20 μA                                                        | 2/3 * V <sub>CCA</sub> |                     |                        | V    |

| V <sub>OHB</sub>                          | B Side Output High Voltage                                                                                                           | B Side Source Current = 20 μA                                                        | 2/3 * V <sub>CCB</sub> |                     |                        | V    |

| V <sub>OLA</sub>                          | A Side Output Low Voltage                                                                                                            | A Side Sink Current = 20 μA                                                          |                        |                     | 1/3 * V <sub>CCA</sub> | V    |

| $V_{OLB}$                                 | B Side Output Low Voltage                                                                                                            | B Side Sink Current = 20 μA                                                          |                        |                     | 1/3 * V <sub>CCB</sub> | ٧    |

| I <sub>OZA</sub>                          | Output Leakage Current on A Side in "Disabled" Modes                                                                                 |                                                                                      |                        |                     | 1                      | μΑ   |

|                                           | †                                                                                                                                    | <del> </del>                                                                         |                        | 1                   |                        | -    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Typical values are for V<sub>CCB</sub> = +3.3 V, V<sub>CCA</sub> = +1.8 V and T<sub>A</sub> = +25°C. V<sub>CCB</sub> may refer to VIN, AUX or VOUT depend on the operating mode.

3. All units are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

4. Reverse current protection is activated only when a reverse current threshold of about 200 mA is reached.

5.  $\Delta V_{SW}$  is the voltage difference across the power switch.

6. Guaranteed by design.

μΑ

Output Leakage Current on B Side

in "Disabled" Modes

6. Guaranteed by design.

**I**OZB

Table 6. DC ELECTRICAL CHARACTERISTICS (V<sub>CCA</sub> = 1.65 V to 5.5 V, V<sub>CCB</sub> (Note 7) = 3.0 V to 5.5 V, unless otherwise specified)

|                 |                          |                                                                                                                | -4                     | 10°C to +85°C       |                      |      |

|-----------------|--------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|---------------------|----------------------|------|

| Symbol          | Parameter                | Test Conditions (Note 7)                                                                                       | Min                    | Typ<br>(Notes 7, 8) | Max                  | Unit |

| CRT Mod         | e (HSYNC/VSYNC Unidire   | ectional Translator Drivers)                                                                                   |                        |                     |                      |      |

| $V_{IH}$        | Input HIGH Voltage       | VCCA = 4.5 to 5.5 V                                                                                            | 2.0                    |                     |                      | V    |

|                 |                          | VCCA = 3.0 to 3.6 V                                                                                            | 1.8                    |                     |                      | 1    |

|                 |                          | VCCA = 2.3 to 2.7 V                                                                                            | 1.6                    |                     |                      |      |

|                 |                          | VCCA = 1.65 to 1.95 V                                                                                          | 1.4                    |                     |                      | 1    |

| $V_{IL}$        | Input LOW Voltage        | VCCA = 4.5 to 5.5 V                                                                                            |                        |                     | 0.8                  | V    |

|                 |                          | VCCA = 3.0 to 3.6 V                                                                                            |                        |                     | 0.7                  | 1    |

|                 |                          | VCCA = 2.3 to 2.7 V                                                                                            |                        |                     | 0.5                  | 1    |

|                 |                          | VCCA = 1.65 to 1.95 V                                                                                          |                        |                     | 0.3                  | 1    |

| V <sub>OH</sub> | Output HIGH Voltage      | $V_I = V_{IH}$ , $I_{OH} = -20 \mu A$                                                                          | V <sub>OUT</sub> - 0.1 |                     |                      | V    |

|                 |                          | I <sub>OH</sub> = - 24 mA                                                                                      | 2.0                    |                     |                      | 1    |

| V <sub>OL</sub> | Output LOW Voltage       | $V_I = V_{IL}$ , $I_{OL} = 20 \mu A$                                                                           |                        |                     | 0.1                  | ٧    |

|                 |                          | I <sub>OL</sub> = 24 mA                                                                                        |                        |                     | 0.8                  | 1    |

| HPD Driv        | er (HPD_B to HPD_A Trai  | nslator for DP and HDMI Modes)                                                                                 |                        |                     |                      |      |

| V <sub>IH</sub> | Input HIGH Voltage       | VCCA $\leq$ 2 V; VOUT $\geq$ 3 V;<br>R <sub>HPD_B2VOUT</sub> $\leq$ 40 k $\Omega$ , HPD_A Open                 | 2.0                    |                     |                      | V    |

| V <sub>IL</sub> | Input LOW Voltage        | $VCCA \le 2 \text{ V}; VOUT \ge 3 \text{ V};$<br>$R_{HPD\_B2VOUT} \le 40 \text{ k}\Omega, HPD\_A \text{ Open}$ |                        |                     | 0.4                  | V    |

| V <sub>OH</sub> | Output HIGH Voltage      | $V_I = V_{IH}$ , $I_{OH} = -0.1 \mu A$                                                                         | V <sub>CCA</sub> - 0.5 |                     |                      | V    |

| $V_{OL}$        | Output LOW Voltage       | $V_I = V_{IL}$ , $I_{OL\_SINK} = 20 \mu A$                                                                     |                        |                     | V <sub>IL</sub> +0.1 | V    |

| CA_DET_         | B Input (CH1B for DP Mo  | odes)                                                                                                          |                        |                     |                      |      |

| $V_{IH}$        | Input HIGH Voltage       |                                                                                                                | 1.0                    |                     |                      | V    |

| $V_{IL}$        | Input LOW Voltage        |                                                                                                                |                        |                     | 0.35                 | ٧    |

| I <sub>IH</sub> | Input HIGH Leakage       | VCCA = 5.5 V                                                                                                   |                        | 5.5                 | 7.0                  | μΑ   |

| I <sub>IL</sub> | Input LOW Leakage        | VCCA = 5.5 V                                                                                                   |                        |                     | 1                    | μΑ   |

| OPO Mode        | e (AUX, AUXN Level Shift | ters) See Figures 16 and 17.                                                                                   |                        |                     |                      |      |

| R <sub>ON</sub> | ON-State Resistance      | I <sub>LOAD</sub> = 5mA, V <sub>CCA</sub> = 3.0 V, VI = 1.3 V to 1.7 V                                         |                        | 10                  | 40                   | Ω    |

|                 |                          | I <sub>LOAD</sub> = 5mA, V <sub>CCA</sub> = 4.5 V, VI = 2.7 V to 3.1 V                                         |                        | 4                   | 10                   | 1    |

<sup>7.</sup> Typical values are for V<sub>CCB</sub> = +3.3 V, V<sub>CCA</sub> = +1.8 V and T<sub>A</sub> = +25°C. V<sub>CCB</sub> may refer to VIN, AUX or VOUT depend on the operating mode. 8. All units are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

Table 7. DC ELECTRICAL CHARACTERISTICS (V<sub>CCA</sub> = 1.65 V to 5.5 V, V<sub>CCB</sub> (Note 9) = 1.65 V to 5.5 V, unless otherwise specified)

|                    |                                                   |                                                                                                                            | -   |                          |     |      |  |

|--------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|-----|------|--|

| Symbol Parameter T |                                                   | Test Conditions (Note 9)                                                                                                   | Min | <b>Typ</b> (Notes 9, 10) | Max | Unit |  |

| SUPPLY A           | AND LEAKAGE CURRENTS                              |                                                                                                                            |     |                          |     |      |  |

| I <sub>VCCA</sub>  | I <sub>VCCA</sub> V <sub>CCA</sub> Supply Current | LT Mode: VIN = 5.5 V, AUX = 5.5 V, AUX# = V <sub>IHA</sub> or V <sub>ILA</sub> , all other pins open                       |     |                          |     |      |  |

|                    |                                                   | DP Mode: VIN = 3.3 V, all other pins left open                                                                             |     |                          | 130 | 1    |  |

|                    |                                                   | HDMI Mode: VIN = 5 V, AUX# = V <sub>IHA</sub> or V <sub>ILA</sub> , all other pins left open                               |     |                          | 130 |      |  |

|                    |                                                   | CRT Mode: VIN = 5 V, AUX# = V <sub>IHA</sub> or V <sub>ILA</sub> ,<br>CH1A = CH2A = 0 V, all other pins left open          |     |                          | 10  |      |  |

| I <sub>VIN</sub>   | V <sub>IN</sub> Supply Current                    | LT Mode: VIN = 1.65 to 5.5 V, $V_{CCA}$ = AUX = 5.5 V, AUX# = $V_{IHA}$ or $V_{ILA}$ , all other pins left open            |     |                          | 60  | μΑ   |  |

| l <sub>OZ</sub>    | I/O Tristate Leakage Current                      | LT, HDMI or CRT Mode: CH_EN = L                                                                                            |     | 0.1                      | 1.0 | μΑ   |  |

| I <sub>OFF</sub>   | I/O Power-Off Leakage Cur-<br>rent                | All Modes: V <sub>CCB</sub> = 0 V, V <sub>CCA</sub> = 0 to 5.5 V, or V <sub>CCB</sub> = 0 to 5.5 V, V <sub>CCA</sub> = 0 V |     |                          | 1.0 | μΑ   |  |

<sup>9.</sup> Typical values are for  $V_{CCB}$  = +3.3 V,  $V_{CCA}$  = +1.8 V and  $T_A$  = +25°C.  $V_{CCB}$  may refer to VIN, AUX or VOUT depend on the operating mode. 10. All units are production tested at  $T_A$  = +25°C. Limits over the operating temperature range are guaranteed by design.

#### Table 8. PULLUP / PULLDOWN RESISTOR CONFIGURATIONS

|            | Typical, $T_A = +25^{\circ}C$ ( $\Omega$ ) |               |               |              |              |  |  |  |  |  |

|------------|--------------------------------------------|---------------|---------------|--------------|--------------|--|--|--|--|--|

|            | Function Mode                              |               |               |              |              |  |  |  |  |  |

| Pin / Mode | LT                                         | CRT HDMI      |               | DP0 (AUX)    | DP1          |  |  |  |  |  |

| CH1A       | 10K to VCCA                                |               | 10K to VCCA   | Hi–Z         | Hi–Z         |  |  |  |  |  |

| CH2A       | 10K to VCCA                                |               | 1M to VCCA    | 1M to VCCA   | 1M to VCCA   |  |  |  |  |  |

| СНЗА       | 10K to VCCA                                | 2.2 K to VCCA | 2.2K to VCCA  | Hi–Z         | 2.2K to VCCA |  |  |  |  |  |

| CH4A       | 10K to VCCA                                | 2.2 K to VCCA | 2.2K to VCCA  | Hi–Z         | 2.2K to VCCA |  |  |  |  |  |

| CH1B       | 10K to VIN                                 |               | 26K to CEC3V  | 1M to GND    | 1M to GND    |  |  |  |  |  |

| CH2B       | 10K to VIN                                 |               | 100K to GND   | 100K to GND  | 100K to GND  |  |  |  |  |  |

| СНЗВ       | 10K to AUX                                 | 4.7K to VOUT  | 4.7 K to VOUT | 100K to GND  | 4.7K to VOUT |  |  |  |  |  |

| CH4B       | 10K to AUX                                 | 4.7K to VOUT  | 4.7 K to VOUT | 100K to VOUT | 4.7K to VOUT |  |  |  |  |  |

| AUX        | Hi–Z                                       | Hi–Z          | Hi–Z          |              | Hi–Z         |  |  |  |  |  |

| AUXN       | Hi–Z                                       | Hi–Z          | Hi–Z          |              | Hi–Z         |  |  |  |  |  |

## Table 9. TIMING CHARACTERISTICS in Rail-to-Rail Driving Configuration for Bidirectional Transfer Channels:

CH1, CH2, CH3, CH4 in LT Mode for VCCA = 1.65 V to 5.5 V and VCCB = 1.65 V to 5.5 V; CH3, CH4 in DP1 Mode for VCCA = 1.65 V to 5.5 V and VCCB = 3.0 V to 3.6 V;

CH1, CH3, CH4 in HDMI Mode for VCCA = 1.65 V to 5.5 V and VCCB = 4.5 V to 5.5 V;

CH3, CH4 in CRT Mode for VCCA = 1.65 V to 5.5 V and VCCB = 4.5 V to 5.5 V.

$(R_{PU\_INT}$  = 10 k $\Omega$ ,  $C_{LOAD}$  = 15 pF, driver output impedance  $\leq$  50  $\Omega$ ,  $R_{LOAD}$  = 50 k $\Omega$ , unless otherwise specified. See Figures 9, 10, 13, 14 and 15.)

|                                     |                                     |            | -40°C to +85°C                         |     |                                      |      |                                      |      |      |

|-------------------------------------|-------------------------------------|------------|----------------------------------------|-----|--------------------------------------|------|--------------------------------------|------|------|

|                                     |                                     | Conditions | V <sub>CCB</sub> =<br>1.65 V to 1.95 V |     | V <sub>CCB</sub> =<br>3.0 V to 3.6 V |      | V <sub>CCB</sub> =<br>4.5 V to 5.5 V |      |      |

| Parameter                           | Symbol                              |            | Min                                    | Max | Min                                  | Max  | Min                                  | Max  | Unit |

| V <sub>CCA</sub> = 1.65 V to 1.95 V |                                     |            |                                        |     |                                      |      |                                      |      |      |

| A Side Rise Time                    | t <sub>RA</sub>                     |            |                                        | 32  |                                      | 25   |                                      | 22.6 | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     |            |                                        | 32  |                                      | 24   |                                      | 17   | nS   |

| A Side Fall Time                    | t <sub>FA</sub>                     |            |                                        | 7   |                                      | 6    |                                      | 15   | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     |            |                                        | 4.7 |                                      | 12.2 |                                      | 25   | nS   |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub>                  |            |                                        | 20  |                                      | 14   |                                      | 13   | nS   |

| B Side to A Side Propagation Delay  | t <sub>PDB-A</sub>                  |            |                                        | 20  |                                      | 15   |                                      | 12   | nS   |

| Translator Enable Time (Note 11)    | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H  |                                        | 100 |                                      | 90   |                                      | 120  | nS   |

| Translator Disable Time (Note 11)   | $t_{PHZ}$ , $t_{PLZ}$               | CH_EN = L  |                                        | 220 |                                      | 370  |                                      | 500  | nS   |

| Maximum Data Rate                   | MDR                                 |            | 20                                     |     | 20                                   |      | 20                                   |      | Mbps |

| V <sub>CCA</sub> = 3.0 V to 3.6 V   |                                     |            |                                        |     |                                      |      |                                      |      |      |

| A Side Rise Time                    | t <sub>RA</sub>                     |            |                                        | 16  |                                      | 13   |                                      | 12.3 | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     |            |                                        | 25  |                                      | 14   |                                      | 9    | nS   |

| A Side Fall Time                    | t <sub>FA</sub>                     |            |                                        | 9   |                                      | 4    |                                      | 3.5  | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     |            |                                        | 6   |                                      | 4    |                                      | 5    | nS   |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub>                  |            |                                        | 15  |                                      | 3.5  |                                      | 6.3  | nS   |

| B Side to A Side Propagation Delay  | t <sub>PDB-A</sub>                  |            |                                        | 14  |                                      | 4    |                                      | 3    | nS   |

| Translator Enable Time (Note 11)    | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H  |                                        | 80  |                                      | 30   |                                      | 30   | nS   |

| Translator Disable Time (Note 11)   | $t_{PHZ}$ , $t_{PLZ}$               | CH_EN = L  |                                        | 600 |                                      | 200  |                                      | 330  | nS   |

| Maximum Data Rate                   | MDR                                 |            | 20                                     |     | 20                                   |      | 20                                   |      | Mbps |

| V <sub>CCA</sub> = 4.5 V to 5.5 V   |                                     |            |                                        |     |                                      |      |                                      |      |      |

| A Side Rise Time                    | t <sub>RA</sub>                     |            |                                        | 17  |                                      | 13.5 |                                      | 10.5 | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     |            |                                        | 23  |                                      | 13.3 |                                      | 8    | nS   |

| A Side Fall Time                    | t <sub>FA</sub>                     |            |                                        | 13  |                                      | 5    |                                      | 3    | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     |            |                                        | 20  |                                      | 9.6  |                                      | 3    | nS   |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub>                  |            |                                        | 13  |                                      | 4    |                                      | 6.5  | nS   |

| B Side to A Side Propagation Delay  | t <sub>PDB-A</sub>                  |            |                                        | 13  |                                      | 6    |                                      | 7    | nS   |

| Translator Enable Time (Note 11)    | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H  |                                        | 85  |                                      | 20   |                                      | 20   | nS   |

| Translator Disable Time (Note 11)   | t <sub>PHZ</sub> , t <sub>PLZ</sub> | CH_EN = L  |                                        | 200 |                                      | 350  |                                      | 260  | nS   |

| Maximum Data Rate                   | MDR                                 |            | 20                                     |     | 20                                   |      | 20                                   |      | Mbps |

<sup>11.</sup> These parameters apply to the LT, HDMI and CRT modes only. The power switch turn-on time should be added to translator enable time for HDMI and CRT modes. Maximum CH EN frequency is 10 kHz with minimum high pulse duration of 30 μs.

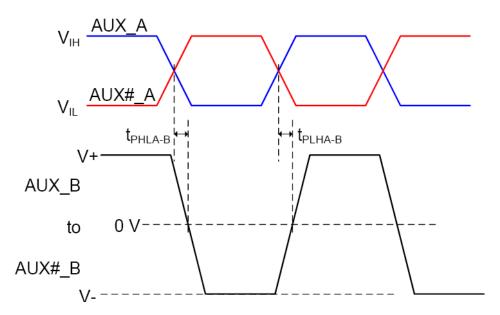

## Table 10. TIMING CHARACTERISTICS in Open Drain Driving Configuration for Bidirectional Transfer Channels:

CH1, CH2, CH3, CH4 in LT Mode for VCCA = 1.65 V to 5.5 V and VCCB = 1.65 V to 5.5 V; CH3, CH4 in DP1 Mode for VCCA = 1.65 V to 5.5 V and VCCB = 3.0 V to 3.6 V;

CH1, CH3, CH4 in HDMI Mode for VCCA = 1.65 V to 5.5 V and VCCB = 4.5 V to 5.5 V;

CH3, CH4 in CRT Mode for VCCA = 1.65 V to 5.5 V and VCCB = 4.5 V to 5.5 V.

(R<sub>PU</sub> I<sub>NT</sub> = 10 kΩ, C<sub>LOAD</sub> = 15 pF, driver output impedance ≤ 50 Ω, R<sub>LOAD</sub> = 1 MΩ, unless otherwise specified.

See Figures 11, 12, 13, 14 and 15.)

|                                     |                                     |                                | −40°C to +85°C                         |     |                                   |     |                                      |     |      |

|-------------------------------------|-------------------------------------|--------------------------------|----------------------------------------|-----|-----------------------------------|-----|--------------------------------------|-----|------|

|                                     |                                     |                                | V <sub>CCB</sub> =<br>1.65 V to 1.95 V |     | V <sub>CCB</sub> = 3.0 V to 3.6 V |     | V <sub>CCB</sub> =<br>4.5 V to 5.5 V |     |      |

| Parameter                           | Symbol                              | Conditions                     | Min                                    | Max | Min                               | Max | Min                                  | Max | Unit |

| V <sub>CCA</sub> = 1.65 V to 1.95 V |                                     |                                |                                        |     |                                   |     |                                      |     |      |

| A Side Rise Time                    | t <sub>RA</sub>                     | R <sub>PU_INT</sub> =<br>10 kΩ |                                        | 145 |                                   | 110 |                                      | 200 | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     | 10 kΩ                          |                                        | 155 |                                   | 110 |                                      | 200 | nS   |

| A Side Fall Time                    | t <sub>FA</sub>                     | 1                              |                                        | 20  |                                   | 15  |                                      | 20  | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     | 1                              |                                        | 20  |                                   | 28  |                                      | 38  | nS   |

| A Side to B Side Propagation Delay  | t <sub>PHLA-B</sub>                 | 1                              |                                        | 10  |                                   | 15  |                                      | 17  | nS   |

|                                     | t <sub>PLHA-B</sub>                 | 1                              |                                        | 50  |                                   | 40  |                                      | 40  | 1    |

| B Side to A Side Propagation Delay  | t <sub>PHLB-A</sub>                 | 1                              |                                        | 10  |                                   | 10  |                                      | 14  | nS   |

|                                     | t <sub>PLHB-A</sub>                 | 1                              |                                        | 50  |                                   | 10  |                                      | 12  | 1    |

| Translator Enable Time (Note 12)    | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H                      |                                        | 30  |                                   | 25  |                                      | 22  | nS   |

| Translator Disable Time (Note 12)   | t <sub>PHZ</sub> , t <sub>PLZ</sub> | CH_EN = L                      |                                        | 60  |                                   | 82  |                                      | 80  | nS   |

| Maximum Data Rate                   | MDR                                 |                                | 2                                      |     | 2                                 |     | 2                                    |     | Mbps |

| V <sub>CCA</sub> = 3.0 V to 3.6 V   |                                     |                                |                                        |     | •                                 | •   |                                      |     |      |

| A Side Rise Time                    | t <sub>RA</sub>                     | R <sub>PU INT</sub> =          |                                        | 105 |                                   | 130 |                                      | 105 | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     | 10 kΩ                          |                                        | 135 |                                   | 130 |                                      | 170 | nS   |

| A Side Fall Time                    | t <sub>FA</sub>                     |                                |                                        | 25  |                                   | 20  |                                      | 20  | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     | 1                              |                                        | 25  |                                   | 20  |                                      | 30  | nS   |

| A Side to B Side Propagation Delay  | t <sub>PHLA-B</sub>                 | 1                              |                                        | 10  |                                   | 10  |                                      | 15  | nS   |

|                                     | t <sub>PLHA-B</sub>                 | 1                              |                                        | 20  |                                   | 10  |                                      | 17  |      |

| B Side to A Side Propagation Delay  | t <sub>PHLB-A</sub>                 | 1                              |                                        | 15  |                                   | 25  |                                      | 15  | nS   |

|                                     | t <sub>PLHB-A</sub>                 | 1                              |                                        | 30  |                                   | 10  |                                      | 10  |      |

| Translator Enable Time (Note 12)    | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H                      |                                        | 34  |                                   | 15  |                                      | 16  | nS   |

| Translator Disable Time (Note 12)   | t <sub>PHZ</sub> , t <sub>PLZ</sub> | CH_EN = L                      |                                        | 72  |                                   | 80  |                                      | 80  | nS   |

| Maximum Data Rate                   | MDR                                 |                                | 2                                      |     | 2                                 |     | 2                                    |     | Mbps |

| V <sub>CCA</sub> = 4.5 V to 5.5 V   |                                     |                                |                                        | -   |                                   | •   | -                                    |     |      |

| A Side Rise Time                    | t <sub>RA</sub>                     | R <sub>PU_INT</sub> =          |                                        | 85  |                                   | 90  |                                      | 125 | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     | 10 kΩ                          |                                        | 120 |                                   | 110 |                                      | 130 | nS   |

| A Side Fall Time                    | t <sub>FA</sub>                     | 1                              |                                        | 40  |                                   | 30  |                                      | 30  | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     | 1                              |                                        | 25  |                                   | 20  |                                      | 30  | nS   |

| A Side to B Side Propagation Delay  | t <sub>PHLA-B</sub>                 | 1                              |                                        | 12  |                                   | 11  |                                      | 20  | nS   |

|                                     | t <sub>PLHA-B</sub>                 | 1                              |                                        | 10  |                                   | 10  |                                      | 5   | 1    |

| B Side to A Side Propagation Delay  | t <sub>PHLB-A</sub>                 | 1                              |                                        | 25  |                                   | 15  |                                      | 20  | nS   |

|                                     | t <sub>PLHB-A</sub>                 | 1                              |                                        | 30  |                                   | 10  |                                      | 8   | 1    |

| Translator Enable Time (Note 12)    | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H                      |                                        | 30  |                                   | 13  |                                      | 10  | nS   |

| Translator Disable Time (Note 12)   | t <sub>PHZ</sub> , t <sub>PLZ</sub> | <br>CH_EN = L                  |                                        | 100 |                                   | 75  |                                      | 70  | nS   |

| Maximum Data Rate                   | MDR                                 | _                              | 2                                      |     | 2                                 |     | 2                                    |     | Mbps |

<sup>12.</sup> These parameters apply to the LT, HDMI and CRT modes only. The power switch turn-on time should be added to translator enable time for HDMI and CRT modes. Maximum CH\_EN frequency is 10 kHz with minimum high pulse duration of 30 μs.

#### Table 11. TIMING CHARACTERISTICS for HSYNC/VSYNC Drivers (CH1, CH2 in CRT Mode)

(VCCA = 1.65 V to 5.5 V, VCCB = 4.5 V,  $C_{LOAD}$  = 15 pF, driver output impedance  $\leq$  50  $\Omega$ ,  $R_{LOAD}$  = 50 k $\Omega$ ,  $t_R \leq$  3 ns and  $t_F \leq$  3 ns, unless otherwise specified. See Figures 9, 13, 14 and 15.)

|                                     |                                     |              | −40°C to +85°C                         |     |                                      |     |                                   |      |      |

|-------------------------------------|-------------------------------------|--------------|----------------------------------------|-----|--------------------------------------|-----|-----------------------------------|------|------|

|                                     |                                     | I Conditions | V <sub>CCB</sub> =<br>1.65 V to 1.95 V |     | V <sub>CCB</sub> =<br>3.0 V to 3.6 V |     | V <sub>CCB</sub> = 4.5 V to 5.5 V |      |      |

| Parameter                           | Symbol                              |              | Min                                    | Max | Min                                  | Max | Min                               | Max  | Unit |

| V <sub>CCA</sub> = 1.65 V to 1.95 V |                                     |              |                                        |     |                                      |     |                                   |      |      |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub>                  |              |                                        |     |                                      |     |                                   | 13   | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     |              |                                        |     |                                      |     |                                   | 5    | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     |              |                                        |     |                                      |     |                                   | 4    | nS   |

| Output Enable Time (Note 13)        | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H    |                                        |     |                                      |     |                                   | 1.2  | mS   |

| Output Disable Time                 | $t_{PHZ}$ , $t_{PLZ}$               | CH_EN = L    |                                        |     |                                      |     |                                   | 130  | nS   |

| Maximum Data Rate                   | MDR                                 |              |                                        |     |                                      |     | 90                                |      | Mbps |

| V <sub>CCA</sub> = 3.0 V to 3.6 V   |                                     |              |                                        |     |                                      |     |                                   |      |      |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub>                  |              |                                        |     |                                      |     |                                   | 6    | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     |              |                                        |     |                                      |     |                                   | 6    | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     |              |                                        |     |                                      |     |                                   | 4    | nS   |

| Output Enable Time (Note 13)        | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H    |                                        |     |                                      |     |                                   | 0.65 | mS   |

| Output Disable Time                 | $t_{PHZ}$ , $t_{PLZ}$               | CH_EN = L    |                                        |     |                                      |     |                                   | 130  | nS   |

| Maximum Data Rate                   | MDR                                 |              |                                        |     |                                      |     | 100                               |      | Mbps |

| V <sub>CCA</sub> = 4.5 V to 5.5 V   |                                     |              | -                                      |     |                                      |     | -                                 |      |      |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub>                  |              |                                        |     |                                      |     |                                   | 6    | nS   |

| B Side Rise Time                    | t <sub>RB</sub>                     |              |                                        |     |                                      |     |                                   | 5    | nS   |

| B Side Fall Time                    | t <sub>FB</sub>                     |              |                                        |     |                                      |     |                                   | 4    | nS   |

| Output Enable Time (Note 13)        | t <sub>PZH</sub> , t <sub>PZL</sub> | CH_EN = H    |                                        |     |                                      |     |                                   | 0.61 | mS   |

| Output Disable Time                 | $t_{PHZ}$ , $t_{PLZ}$               | CH_EN = L    |                                        |     |                                      |     |                                   | 130  | nS   |

| Maximum Data Rate                   | MDR                                 |              |                                        |     |                                      |     | 120                               |      | Mbps |

<sup>13.</sup> Output Enable Time takes into account turn-on time of the power switch. Maximum CH\_EN frequency is 10 kHz with minimum high pulse duration of 30  $\mu$ s.

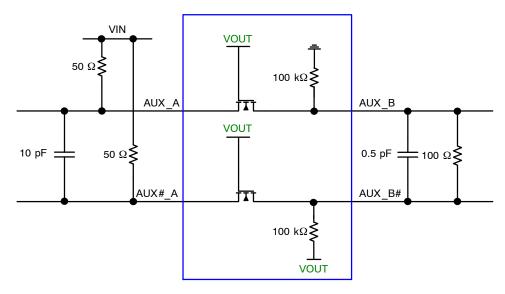

Table 12. TIMING CHARACTERISTICS for AUX\_A/AUX#\_A to AUX\_B/AUX#\_B (AUX-CH3B [AUX\_A-AUX\_B], AUX#-CH4B [AUX\_A#-AUX\_B#] in DP0 Mode) (VCCA = 1.65 V to 5.5 V and VOUT = 3.0 V to 3.6 V. See Figures 16 and 17.)

|                                     |                    |                           | -40°C to +85°C |                  |     |                 |     |                 |      |

|-------------------------------------|--------------------|---------------------------|----------------|------------------|-----|-----------------|-----|-----------------|------|

|                                     |                    |                           |                | JT =<br>o 1.95 V |     | JT =<br>o 3.6 V |     | JT =<br>o 5.5 V |      |

| Parameter                           | Symbol             | Conditions                | Min            | Max              | Min | Max             | Min | Max             | Unit |

| V <sub>CCA</sub> = 1.65 V to 1.95 V |                    |                           |                |                  |     |                 |     |                 |      |

| B Side Rise Time                    | t <sub>RB</sub>    | V <sub>IH</sub> = 0.65 V, |                |                  |     | 2.5             |     |                 | nS   |

| B Side Fall Time                    | t <sub>FB</sub>    | V <sub>IL</sub> = 0.25 V  |                |                  |     | 2.5             |     |                 | nS   |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub> | 1                         |                |                  |     | 0.2             |     |                 | nS   |

| Maximum Data Rate                   | MDR                |                           |                |                  | 100 |                 |     |                 | Mbps |

| V <sub>CCA</sub> = 3.0 V to 3.6 V   |                    |                           |                |                  |     |                 |     |                 |      |

| B Side Rise Time                    | t <sub>RB</sub>    | V <sub>IH</sub> = 2.0 V,  |                |                  |     | 2.5             |     |                 | nS   |

| B Side Fall Time                    | t <sub>FB</sub>    | V <sub>IL</sub> = 1.6 V   |                |                  |     | 2.5             |     |                 | nS   |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub> | 1                         |                |                  |     | 0.1             |     |                 | nS   |

| Maximum Data Rate                   | MDR                |                           |                |                  | 100 |                 |     |                 | Mbps |

| V <sub>CCA</sub> = 4.5 V to 5.5 V   |                    |                           |                |                  |     |                 |     |                 |      |

| B Side Rise Time                    | t <sub>RB</sub>    | V <sub>IH</sub> = 3.5 V,  |                |                  |     | 2.5             |     |                 | nS   |

| B Side Fall Time                    | t <sub>FB</sub>    | V <sub>IL</sub> = 3.1 V   |                |                  |     | 2.5             |     |                 | nS   |

| A Side to B Side Propagation Delay  | t <sub>PDA-B</sub> | 1                         |                |                  |     | 0.05            |     |                 | nS   |

| Maximum Data Rate                   | MDR                | 1                         |                |                  | 100 |                 |     |                 | Mbps |

## **Test Setups**

Figure 9. Rail-to-Rail Driving A-side I/O

Figure 10. Rail-to-Rail Driving B-side I/O

Figure 11. Open-Drain Driving A-side I/O

Figure 12. Open-Drain Driving B-side I/O

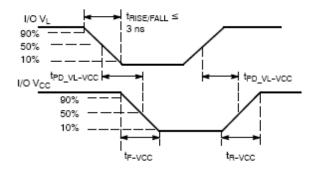

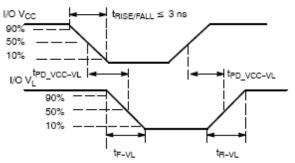

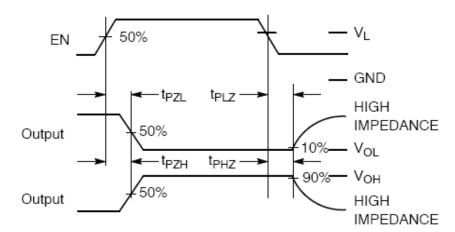

Figure 13. Definition of Timing Specification Parameters

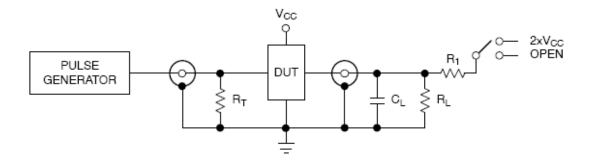

| Test                                | Switch              |  |  |  |

|-------------------------------------|---------------------|--|--|--|

| t <sub>PZH</sub> , t <sub>PHZ</sub> | Open                |  |  |  |

| $t_{PZL}$ , $t_{PLZ}$               | 2 x V <sub>CC</sub> |  |  |  |

$C_L$  = 15 pF or equivalent (Includes jig and probe capacitance)  $R_L$  =  $R_1$  = 50 k $\Omega$  or equivalent  $R_T$  =  $Z_{OUT}$  of pulse generator (typically 50  $\Omega$ )

Figure 14. Test Circuit for Translator Enable/Disable Time Measurements

Figure 15. LT, HDMI, CRT Mode Translator Enable/Disable Time Definition

Figure 16. DP0 Mode AUX Channels Test Circuit

Figure 17. DP0 Mode AUX Channels Propagation Delay Definition

| DOCUMENT NUMBER: | 98AON20790D             | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | WQFN16, 1.8 X 2.6, 0.4P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales