# **18-Channel Level Shifter**

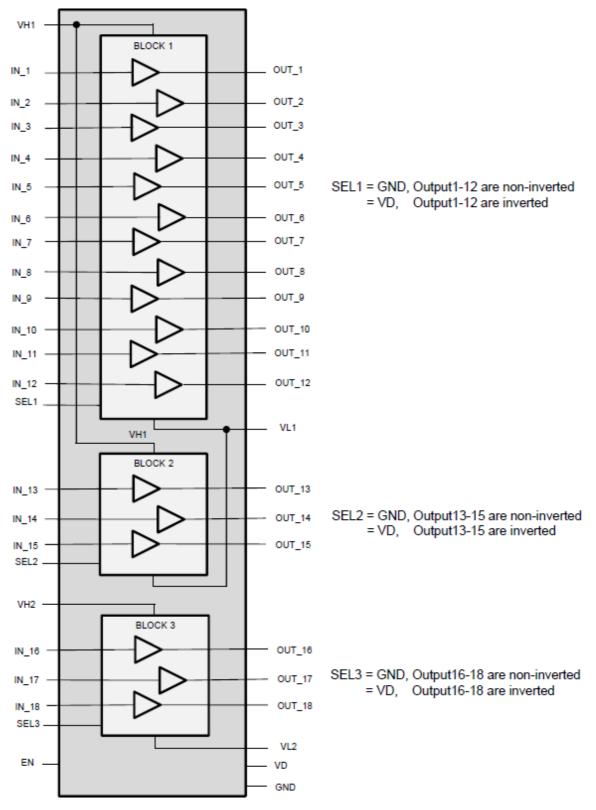

The NLHV18T3244 is an 18-channel level translator designed for high voltage level shifting applications such as displays. The 18 channels are divided into twelve and two three channel groups, with each group controlled by the inverting inputs SEL1, SEL2 and, SEL3; respectively. The EN input is used to select the 'ON' or power saving shutdown modes.

Each channel consists of a high voltage output buffer. The output buffers use N-channel low side and P-channel high side transistors. The output signal on pins OUT1 to OUT18 is pulled by the transistors to the positive high or negative low voltage on the  $V_{Hx}$  and  $V_{Lx}$  power supply pins, respectively, depending on the voltage of the inverting pins.

## Features

- 18 Non–Inverting / Inverting Channels

- V<sub>H1</sub>, V<sub>H2</sub> Supply Range: 5 V to 25 V

- V<sub>L1</sub>, V<sub>L2</sub> Supply Range: -13 V to 0 V

- $V_{Hx} V_{Lx}$  Difference Range: 5 V to 25 V

- $V_{L1}$  and  $V_{L2}$  can be tied together or connected to independent supply voltages as long as  $V_{L1} \le V_{L2}$

- V<sub>D</sub> Supply Range: 2 V to 5.5 V

- Outputs Specified with 1000 pF Capacitive Loads

- Disable Function

- Low Standby Current

- No Glitch on Power–Up

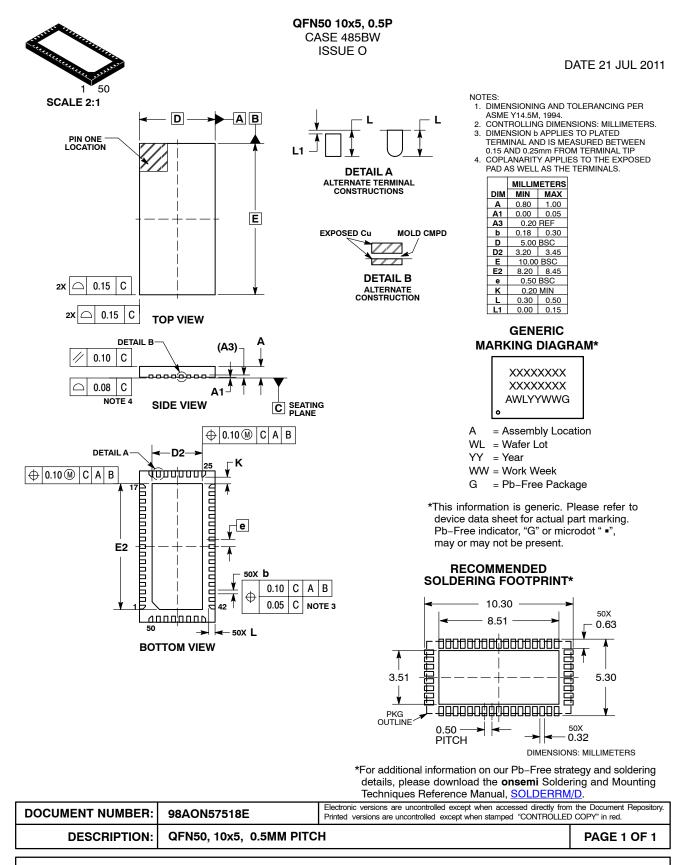

- Available in: 5 mm x 10 mm, 0.5 mm pitch, QFN50 Package

# **Typical Applications**

- OLED Drivers

- High Voltage Level Shifters

- Piezoelectric Motor Drivers

# **ON Semiconductor®**

http://onsemi.com

G = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

Figure 1. Simplified Schematic – Option I ( $V_{L1} \le V_{L2}$ )

|                | Input          |                |                | Output               |                         |                         |  |

|----------------|----------------|----------------|----------------|----------------------|-------------------------|-------------------------|--|

| EN             | SEL1           | SEL2           | SEL3           | Block 1 (OUT1-OUT12) | Block 2 (OUT13 – OUT15) | Block 3 (OUT16 – OUT18) |  |

| GND            | Х              | Х              | Х              | Hi–Z                 | Hi–Z                    | Hi–Z                    |  |

| VD             | GND            | GND            | GND            | Normal               | Normal                  | Normal                  |  |

| VD             | GND            | GND            | VD             | Normal               | Normal                  | Inverted                |  |

| VD             | GND            | VD             | GND            | Normal               | Inverted                | Normal                  |  |

| VD             | GND            | VD             | VD             | Normal               | Inverted                | Inverted                |  |

| V <sub>D</sub> | VD             | GND            | GND            | Inverted             | Normal                  | Normal                  |  |

| V <sub>D</sub> | VD             | GND            | V <sub>D</sub> | Inverted             | Normal                  | Inverted                |  |

| V <sub>D</sub> | V <sub>D</sub> | V <sub>D</sub> | GND            | Inverted             | Inverted                | Normal                  |  |

| V <sub>D</sub> | V <sub>D</sub> | V <sub>D</sub> | V <sub>D</sub> | Inverted             | Inverted                | Inverted                |  |

FUNCTION TABLE (X Input = 'Don't Care, Hi-Z = High Impedance Tri-State Output)

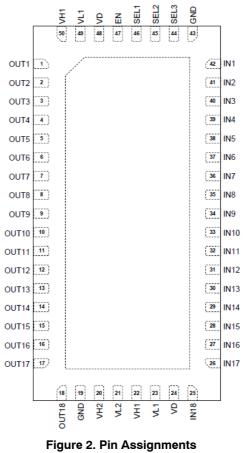

(Top View)

| Pin Name | Pin Number | Pin Name | Pin Number | Pin Name   | Pin Number |

|----------|------------|----------|------------|------------|------------|

| OUT1     | 1          | OUT18    | 18         | IN8        | 35         |

| OUT2     | 2          | GND      | 19         | IN7        | 36         |

| OUT3     | 3          | VH2      | 20         | IN6        | 37         |

| OUT4     | 4          | VL2      | 21         | IN5        | 38         |

| OUT5     | 5          | VH1      | 22         | IN4        | 39         |

| OUT6     | 6          | VL1      | 23         | IN3        | 40         |

| OUT7     | 7          | VD       | 24         | IN2        | 41         |

| OUT8     | 8          | IN18     | 25         | IN1        | 42         |

| OUT9     | 9          | IN17     | 26         | GND        | 43         |

| OUT10    | 10         | IN16     | 27         | SEL3       | 44         |

| OUT11    | 11         | IN15     | 28         | SEL2       | 45         |

| OUT12    | 12         | IN14     | 29         | SEL1       | 46         |

| OUT13    | 13         | IN13     | 30         | EN         | 47         |

| OUT14    | 14         | IN12     | 31         | VD         | 48         |

| OUT15    | 15         | IN11     | 32         | VL1        | 49         |

| OUT16    | 16         | IN10     | 33         | VH1        | 50         |

| OUT17    | 17         | IN9      | 34         | No Connect | Center Tap |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                               | Parameter                                                                | Condition                                                                                                                            | Value                            | Unit |

|--------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|

| V <sub>Hx</sub>                      | High-side DC Supply Voltage                                              |                                                                                                                                      | –0.5 to +30                      | V    |

| $V_{Lx}$                             | Low-side DC Supply Voltage                                               |                                                                                                                                      | -15 to +0.5                      | V    |

| V <sub>Hx</sub> -<br>V <sub>Lx</sub> | Differential V <sub>H</sub> - V <sub>L</sub> Voltage                     |                                                                                                                                      | 0 to +30                         | V    |

| VD                                   | Logic Supply Voltage                                                     |                                                                                                                                      | –0.5 to +5.5                     | V    |

| VI                                   | Input (IN1 – IN18), Invert (SEL1 – SEL3)<br>and Enable (EN) Control Pins |                                                                                                                                      | –0.5 to V <sub>D</sub> + 0.5     | V    |

| V <sub>OUT</sub>                     | Output Voltage Pins (OUT1 – OUT18)                                       |                                                                                                                                      | $V_{Lx}{-}0.5$ to $V_{Hx}$ + 0.5 | V    |

| Ι <sub>ΟUT</sub>                     | Continuous Output Current (OUT1 –<br>OUT18)                              | One channel is sinking or<br>sourcing current while the<br>remaining seventeen channels<br>are disconnected (I <sub>OUT</sub> = 0 A) | 100                              | mA   |

| I <sub>HX</sub>                      | DC Supply Current Through V <sub>HX</sub>                                |                                                                                                                                      | 100                              | mA   |

| $I_{LX}$                             | DC Supply Current Through V <sub>LX</sub>                                |                                                                                                                                      | 100                              | mA   |

| ۱ <sub>D</sub>                       | DC Supply Current Through V <sub>D</sub>                                 |                                                                                                                                      | 50                               | mA   |

| $R_{\thetaJA}$                       | Junction to Ambient Resistance                                           | (Note 1)                                                                                                                             | 68                               | °C/W |

| Τ <sub>J</sub>                       | Junction Temperature                                                     |                                                                                                                                      | +115                             | °C   |

| T <sub>STG</sub>                     | Storage Temperature                                                      |                                                                                                                                      | −65 to +150                      | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. 4 layer PCB with 100 sq. mm, 1 oz. heat spreading including traces, JEDEC 51.7 equivalent.

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol                | Parameter                                                                                                                          | Min             | Max             | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------|

| V <sub>H1</sub>       | High-side DC Supply Voltage                                                                                                        | 5               | 25              | V    |

| V <sub>H2</sub>       | High-side DC Supply Voltage (Note 2)                                                                                               | 5               | 25              | V    |

| V <sub>L1</sub>       | Low-side Negative DC Supply Voltage (Note 3) $(V_{L1} \leq V_{L2})$                                                                |                 | 0               | V    |

| V <sub>L2</sub>       | Low-side Negative DC Supply Voltage (Note 4)                                                                                       | V <sub>L1</sub> | 0               | V    |

| $V_{Hx} - V_{Lx}$     | Differential $V_H - V_L$ Voltage                                                                                                   | 5               | 25              | V    |

| VD                    | Logic Supply Voltage                                                                                                               | 2               | 5.5             | V    |

| VI                    | Input (IN1 – IN18), Invert (SEL1 – SEL3) and Enable (EN)                                                                           | GND             | VD              | V    |

| V <sub>OUT</sub>      | Output Voltage (OUT1 – OUT18)                                                                                                      |                 | V <sub>Hx</sub> | V    |

| T <sub>A</sub>        | Operating Temperature Range                                                                                                        | -40             | +85             | °C   |

| $\Delta t / \Delta V$ | Input Transition Rise or Rate V <sub>I</sub> , V <sub>IO</sub> from 30% to 70% of V <sub>D</sub> ; V <sub>D</sub> =3.3 $\pm$ 0.3 V | 0               | 10              | nS   |

V<sub>H1</sub> and V<sub>H2</sub> can be connected together.

V<sub>L1</sub> must be at the lowest DC supply voltage.

V<sub>L1</sub> and V<sub>L2</sub> can be connected together.

| <b>ELECTRICAL CHARACTERISTICS (V</b> | $_{\rm x}$ =15 V, V <sub>Lx</sub> = -5 V, V <sub>D</sub> = 2 to 5.5 V and EN = V | ר; unless otherwise specified) |

|--------------------------------------|----------------------------------------------------------------------------------|--------------------------------|

|--------------------------------------|----------------------------------------------------------------------------------|--------------------------------|

|                   |                                                        |                                      |                                                                                                                             | –40°C to +85°C   |      | 5°C                       |      |

|-------------------|--------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------|------|---------------------------|------|

| Symbol            | Parameter                                              | Parameter                            | Test Conditions                                                                                                             | Min              | Тур  | Max                       | Unit |

| POWER SU          | PPLY                                                   |                                      | •<br>•                                                                                                                      |                  |      |                           |      |

| Ι <sub>D</sub>    | Digital Supply Static                                  | Enabled (EN = V <sub>D</sub> )       | IN1 to IN18 = 0 V or                                                                                                        |                  | 2    |                           | mA   |

|                   | Current                                                | Disabled (EN = 0 V),<br>(Power Down) | IN1 to IN18 = V <sub>D</sub>                                                                                                |                  | 5    | 10                        | μΑ   |

| I <sub>H1</sub>   | Block 1 and 2 High<br>Voltage Supply Static<br>Current | Enabled (EN = V <sub>D</sub> )       | IN1 to IN18 = 0 V or                                                                                                        |                  | 2    |                           | mA   |

|                   |                                                        | Disabled (EN = 0 V),<br>(Power Down) | IN1 to IN18 = V <sub>D</sub>                                                                                                |                  | 5    |                           | μΑ   |

| I <sub>H2</sub>   | Block 3 High Voltage                                   | Enabled (EN = V <sub>D</sub> )       | IN1 to IN18 = 0 V or                                                                                                        |                  | 2    |                           | mA   |

|                   | Supply Static Current                                  | Disabled (EN = 0 V),<br>(Power Down) | IN1 to IN18 = V <sub>D</sub>                                                                                                |                  | 5    |                           | μΑ   |

| I <sub>L1</sub>   | Block 1 and 2 Low                                      | Enabled (EN = V <sub>D</sub> )       | IN1 to IN18 = 0 V or<br>IN1 to IN18 = V <sub>D</sub>                                                                        |                  | 2    |                           | mA   |

|                   | Voltage Supply Static<br>Current                       | Disabled (EN = 0 V),<br>(Power Down) |                                                                                                                             |                  | 5    |                           | μΑ   |

| I <sub>L2</sub>   | Block 3 Low Voltage                                    | Enabled (EN = V <sub>D</sub> )       | IN1 to $IN18 = 0$ V or                                                                                                      |                  | 2    |                           | mA   |

|                   | Supply Static Current                                  | Disabled (EN = 0 V),<br>(Power Down) | IN1 to IN18 = V <sub>D</sub>                                                                                                |                  | 5    |                           | μΑ   |

| V <sub>H1</sub>   | High-Side DC Supply                                    | 1                                    |                                                                                                                             | 5                | 15   | 25                        | V    |

| V <sub>H2</sub>   | High–Side DC Supply 2                                  |                                      |                                                                                                                             | 5                | 17   | 25                        | V    |

| V <sub>L1</sub>   | Low-Side DC Supply 1                                   |                                      | $\begin{array}{c} V_{L1} \leq V_{L2} \\ V_{L1} \text{ must be the lowest voltage in all} \\ \text{ conditions} \end{array}$ | -13              | -5   | 0                         | V    |

| $V_{L2}$          | Low-Side DC Supply 2                                   |                                      |                                                                                                                             | V <sub>L1</sub>  | -5   | 0                         | V    |

| $V_{Hx} - V_L$    | Differential $V_{Hx} - V_L V_C$                        | oltage                               |                                                                                                                             | 5                |      | 25                        | V    |

| NPUT (IN1         | – IN18, EN, SEL1 – SEL                                 | .3)                                  |                                                                                                                             |                  |      |                           |      |

| V <sub>IH</sub>   | Logic '1' Input Voltage                                |                                      |                                                                                                                             | $0.7 \times V_D$ |      |                           | V    |

| V <sub>IL</sub>   | Logic '0' Input Voltage                                |                                      |                                                                                                                             |                  |      | $0.3 \times V_D$          | V    |

| I <sub>IH</sub>   | Logic '1' Input Current                                |                                      | $V_I = V_{IH}$                                                                                                              |                  | 0.1  | 10                        | μA   |

| Ι <sub>ΙL</sub>   | Logic '0' Input Current                                |                                      | $V_I = V_{IL}$                                                                                                              |                  | 0.1  | 10                        | μA   |

| C <sub>IN</sub>   | Input Capacitance                                      |                                      | $T_A = 25^{\circ}C$                                                                                                         |                  | 3.5  |                           | pF   |

| R <sub>IN</sub>   | Input Resistance                                       |                                      | $T_A = 25^{\circ}C$                                                                                                         |                  | 50   |                           | MΩ   |

| OUTPUT (O         | UT1 – OUT18)                                           |                                      | •<br>•                                                                                                                      |                  |      |                           |      |

| V <sub>OH</sub>   | V <sub>OUT</sub> High Voltage                          |                                      | INx = 3.3 V, I <sub>L</sub> = 20 mA                                                                                         | $V_{HX}$ -0.2    |      |                           | V    |

| V <sub>OL</sub>   | V <sub>OUT</sub> Low Voltage                           |                                      | INx = 0 V, I <sub>L</sub> = 20 mA                                                                                           |                  |      | V <sub>LX</sub> +<br>0.12 | V    |

| R <sub>OH</sub>   | ON Resistance, V <sub>H</sub> to 0                     | CUTx                                 | I <sub>L</sub> = 20 mA                                                                                                      |                  | 5    | 8.5                       | Ω    |

| R <sub>OL</sub>   | ON Resistance, V <sub>L</sub> to 0                     | DUTx                                 | I <sub>L</sub> = 20 mA                                                                                                      |                  | 5    | 7.5                       | Ω    |

| I <sub>PEAK</sub> | Peak Output Current                                    |                                      | C <sub>L</sub> = 1000 pF                                                                                                    |                  | 1100 |                           | mA   |

| I <sub>OZ</sub>   | Output Tri-state Mode                                  | Leakage Current                      | INx = 3.3 V, V <sub>D</sub> = 3.3 V, EN = GND                                                                               |                  |      | 5                         | μA   |

|                    |                                                                     |                                                                                            | -4  | 0°C to +8 | 5°C |      |

|--------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----------|-----|------|

| Symbol             | Parameter                                                           | Test Conditions                                                                            | Min | Тур       | Max | Unit |

| t <sub>R</sub>     | Output Rise Time                                                    | Measured from 10% to 90%                                                                   |     | 20        | 35  | ns   |

| t <sub>F</sub>     | Output Fall Time                                                    | Measured from 90% to 10%                                                                   |     | 20        | 35  | ns   |

| t <sub>RFD</sub>   | Output Rise and Fall Time Mismatch (per channel)                    |                                                                                            |     | 5         |     | ns   |

| t <sub>SK</sub>    | Output Skew Matching (channel-to-channel)                           | Measured from 50% to 50%                                                                   |     | 5         |     | ns   |

| t <sub>D+</sub>    | Turn-On Propagation Delay                                           | Measured from 50% to 50%                                                                   |     | 55        |     | ns   |

| t <sub>D-</sub>    | Turn-Off Propagation Delay                                          | Measured from 50% to 50%                                                                   |     | 55        |     | ns   |

| t <sub>DD</sub>    | High-to-Low/Low-to-High Propagation<br>Delay Mismatch (per channel) | Measured from 50% to 50%                                                                   |     | 5         |     | ns   |

| SC# <sub>MAX</sub> | Maximum channels switched in 100 ns se-<br>quence                   | Delta between inputs of channels<br>must be 100 ns if channels are<br>switched in sequence |     |           | 6   |      |

| Con_OUT            | Outputs connected together to increase drive capability             |                                                                                            |     |           | 3   |      |

| f <sub>MAX</sub>   | Maximum switching Frequency                                         | For all $V_{Hx}$ and $V_{Lx}$ voltages                                                     |     |           | 100 | kHz  |

| t <sub>EN</sub>    | Enable Time                                                         | Measured from 50% EN to 50%<br>OUT_xx                                                      | 9.8 |           | 15  | μs   |

| t <sub>DIS</sub>   | Disable Time                                                        | Measured from 50% EN to 50%<br>OUT_xx_Hi-Z                                                 |     | 2.2       |     | μs   |

**DATA RATES** (C<sub>L</sub> = 1000 pF, V<sub>Hx</sub> = 15 V, V<sub>Lx</sub> = –5 V, V<sub>D</sub> = 3.3 V and EN = 3.3 V; unless otherwise specified)

| Channel                                                                                          | Conditions                                                                    | Data Rate | Unit |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------|------|

| IN1 – IN6 (Note 5) Simultaneous Switching (Turn ON and OFF in sequence, 100 ns between channels) |                                                                               | 120       | Hz   |

|                                                                                                  | Per Channel                                                                   | 56        | kHz  |

| IN7- IN12 (Note 5)                                                                               | Per Channel                                                                   | 120       | Hz   |

| IN13 – IN 15 (Note 5)                                                                            | Per Channel                                                                   | 120       | Hz   |

| IN16 – IN18 (Note 5)                                                                             | Simultaneous Switching<br>(Turn ON and OFF sequence, 100 ns between channels) | 120       | Hz   |

5. While IN1 – IN6 are switching, IN1 – IN18 are not switching.

#### **APPLICATIONS INFORMATION**

#### **Power-Up Sequence**

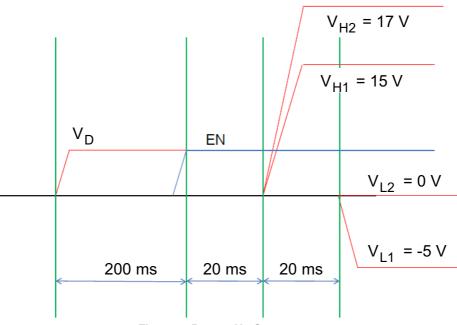

The recommended power-up sequence of the power supplies is provided in Figure 3.

Figure 3. Power–Up Sequence

#### **Power Supply Guidelines**

Supply voltage  $V_{L1}$  must be less than or equal to voltage  $V_{L2}$ . The substrate is connected to  $V_{L1}$ ; thus,  $V_{L1}$  must be the at lowest voltage potential to ensure proper biasing of the internal level shifting circuits. In addition, setting  $V_{L1}$  to the lowest voltage ensures proper operation of the overvoltage and ESD protection circuits connected on the supply voltage and input/output lines, respectively.

For optimal performance, 0.1 and 1  $\mu$ F decoupling capacitors are recommended for the V<sub>D</sub>, V<sub>L1</sub>, V<sub>L2</sub>, V<sub>H1</sub>, and

$V_{H2}$  power supply pins. High frequency ceramic or tantalum capacitors are good design choices to filter and bypass any noise signals on the supply voltage lines to the ground plane of the PCB. The noise immunity will be maximized by placing the capacitors as close as possible to the supply and ground pins, along with minimizing the PCB connection traces. In addition, a ferrite bead can be placed between the two decoupling capacitors to form a bi-directional LC Tee filter if additional noise immunity is required.

# **Recommended PCB Options**

## 2 Layer PCB

- Traces = 1.4 mm width, tin plating, copper 2 oz

- Routing of power lines will be in top layer

- In order to minimize inductance, returning current will be routed as close as possible to the power lines

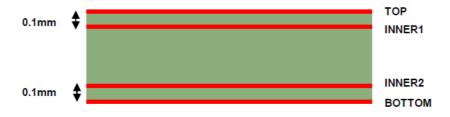

# 4 Layer PCB

- Traces = 1.4 mm width, tin plating, copper 2 oz

- In order to reduce inductance, construction of layers will be as drawing below

- Power lines will be routed in top and returning current will be routed in inner1 right below the power lines

Figure 4. Recommended 4Layer PCB Options

## **PCB Layout Instructions**

- The power devices should be placed as close as possible to each other in order to reduce inductance

- Decoupling filter capacitors should be placed as close as possible to the device in order to reduce ripple on supply.

- The V<sub>H</sub>, V<sub>L</sub> and V<sub>D</sub> decoupling filter capacitors connected between the power supply and GND should be constructed from scaled capacitors. A small value

capacitor of 0.1  $\mu$ F, which filters high frequency, should be placed as close as possible to the device. A larger value capacitor of 1  $\mu$ F, which filters low frequency should be placed adjacent to the small capacitor, but farther away from the device.

- All output line should be far from each other to prevent cross talk

- All input lines should be matched in length to meet skew timing

#### **ORDERING INFORMATION**

| Device           | Package             | Shipping <sup>†</sup> |

|------------------|---------------------|-----------------------|

| NLHV18T3244MNTWG | QFN–50<br>(Pb–Free) | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# onsemi

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>