# Onsemi

# **Synchronous Buck Controller, Automotive** Grade

# **NCV8856A**

The NCV8856A is an adjustable output, synchronous buck controller, which drives dual N-channel MOSFETs, ideal for high power applications. Average current mode control is employed for very fast transient response and tight regulation over wide input voltage and output load ranges. The IC incorporates an internal fixed 6.0 V low-dropout linear regulator (LDO), which supplies charge to the switch mode power supply's (SMPS) bottom gate driver, limiting the power lost to excess gate drive. The IC is designed for operation over an input voltage range of 4.5 V to 38 V and is capable of 10 to 1 voltage conversion at 500 kHz.

Additional controller features include undervoltage lockout, overvoltage shutdown, internal soft-start, low quiescent current sleep mode, programmable frequency, SYNC function, average current limiting, cycle-by-cycle overcurrent protection and thermal shutdown.

# Features

- Average Current Mode Control

- 0.8 V ±2% Reference Voltage

- Wide Input Voltage Range of 4.5 V to 38 V

- Operates through Load Dump Conditions

- 6.0 V Low-dropout Linear Regulator (LDO)

- Input UVLO (Undervoltage Lockout)

- Internal Soft-start

- 6.2 µA Maximum Quiescent Current in Sleep Mode

- Adaptive Non–overlap Circuitry

- 180 ns Minimum High-side Gate Off-time

- Programmable Fixed Frequency 170 kHz to 500 kHz

- External Clock Synchronization up to 600 kHz

- Average Current Limiting (ACL)

- Cycle-by-Cycle Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- This is a Pb–Free Device

#### Applications

- Automotive Systems Requiring High Current

- Pre-regulated Supply for Low-voltage SMPSs and LDOs

TSSOP-20 SUFFIX DB CASE 948E

#### MARKING DIAGRAM

- = Assembly Location

- = Wafer Lot

А

L

Y

w

- = Year

- = Work Week

#### **ORDERING INFORMATION**

| Device        | Package               | Shipping <sup>†</sup> |

|---------------|-----------------------|-----------------------|

| NCV8856ADBR2G | TSSOP-20<br>(Pb-Free) | 2500 / Tape<br>& Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

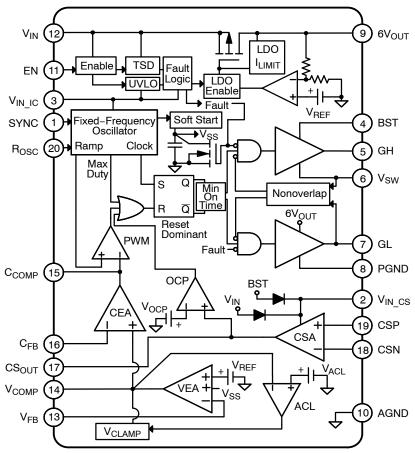

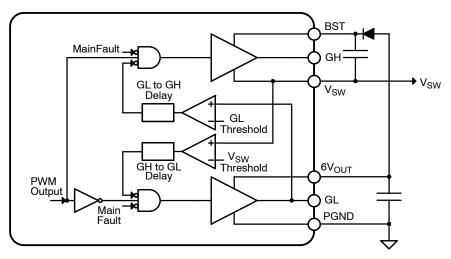

Figure 1. Functional Block Diagram

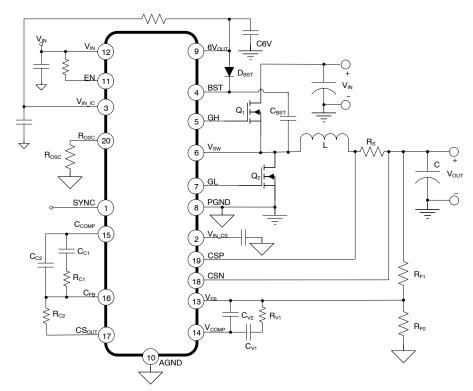

Figure 2. Application Schematic Note: This part is recommended for synchronous use only.

#### PACKAGE PIN DESCRIPTIONS - 20 Lead TSSOP

| Package Pin# | Pin Symbol         | Function                                                                                                                                                                                                           |

|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | SYNC               | External clock synchronization input.                                                                                                                                                                              |

| 2            | V <sub>IN_CS</sub> | Supply input for the internal current sense amplifier.                                                                                                                                                             |

| 3            | V <sub>IN_IC</sub> | Supply input for internal logic and analog circuitry.                                                                                                                                                              |

| 4            | BST                | Supply input for the floating top gate driver. An external diode, D <sub>BST</sub> , from 6V <sub>OUT</sub> and a 0.1 $\mu$ F to 1 $\mu$ F capacitor, C <sub>BST</sub> , to V <sub>SW</sub> forms a boost circuit. |

| 5            | GH                 | Gate driver output for the external high-side NMOS FET.                                                                                                                                                            |

| 6            | V <sub>SW</sub>    | Switch-node. This pin connects to the source of the high-side MOSFET and drain of the low-side MOSFET.                                                                                                             |

| 7            | GL                 | Gate driver output for the external low-side NMOS FET.                                                                                                                                                             |

| 8            | PGND               | Power Ground. Ground reference for the high-current LS FET gate drive.                                                                                                                                             |

| 9            | 6V <sub>OUT</sub>  | Output of internal fixed 6.0 V LDO.                                                                                                                                                                                |

| 10           | AGND               | Analog Ground. Ground reference for the internal logic and analog circuitry as well as $R_{OSC}$ and the compensators.                                                                                             |

| 11           | EN                 | Enable input. When disabled, the LDO, internal logic and analog circuitry and gate drivers enter sleep mode, drawing under 1 $\mu A.$                                                                              |

| 12           | V <sub>IN</sub>    | Supply input for the SMPS.                                                                                                                                                                                         |

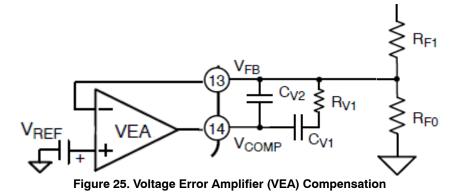

| 13           | V <sub>FB</sub>    | SMPS's voltage feedback. Inverting input to the voltage error amplifier. Connect to $V_{\text{OUT}}$ through a resistive divider.                                                                                  |

| 14           | V <sub>COMP</sub>  | SMPS's voltage error amplifier output and non-inverting input to the current error amplifier.                                                                                                                      |

| 15           | C <sub>COMP</sub>  | SMPS's current error amplifier output and inverting input to the PWM comparator.                                                                                                                                   |

| 16           | C <sub>FB</sub>    | SMPS's current feedback. Inverting input to the current error amplifier.                                                                                                                                           |

| 17           | CS <sub>OUT</sub>  | Single-ended output of the differential current sense amplifier. Connect to C <sub>FB</sub> through a resistor. Non-inverting input to the cycle-by-cycle overcurrent comparator.                                  |

| 18           | CSN                | Differential current sense amplifier inverting input.                                                                                                                                                              |

| 19           | CSP                | Differential current sense amplifier non-inverting input.                                                                                                                                                          |

| 20           | R <sub>OSC</sub>   | Oscillator's frequency adjust pin. Resistor to ground sets the oscillator frequency.                                                                                                                               |

MAXIMUM RATINGS (Voltages are with respect to GND unless otherwise indicated.) (Note 1)

| Rating                                                                            | Symbol                                                                                                              | Value                                       | Unit |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|

| Dc Supply Voltage<br>Peak Transient Voltage (Load Dump, EN = 0 V)                 | EN, V <sub>IN</sub>                                                                                                 | –0.3 to 40<br>45                            | V    |

| Dc Supply Voltage                                                                 | V <sub>IN_IC</sub>                                                                                                  | 6.5                                         | V    |

| Pin Voltage<br>t ≤ 50 ns                                                          | V <sub>SW</sub>                                                                                                     | -0.3 to 38<br>-2                            | V    |

| Pin Voltage                                                                       | V <sub>IN_CS</sub>                                                                                                  | –0.3 to 44                                  | V    |

| Pin Voltage                                                                       | BST, GH                                                                                                             | –0.3 to 44<br>–0.3 to 6 wrt V <sub>SW</sub> | V    |

| Pin Voltage                                                                       | GL                                                                                                                  | -0.3 to 7 wrt PGND                          | V    |

| Pin Voltage                                                                       | CSP, CSN                                                                                                            | –0.3 to 10                                  | V    |

| Pin Voltage                                                                       | V <sub>FB</sub> , V <sub>COMP</sub> , CS <sub>OUT</sub> ,<br>C <sub>FB</sub> , C <sub>COMP</sub> , R <sub>OSC</sub> | -0.3 to 3.6                                 | V    |

| Pin Voltage                                                                       | SYNC                                                                                                                | –0.3 to 6                                   | V    |

| Pin Voltage                                                                       | 6V <sub>OUT</sub>                                                                                                   | –0.3 to 7                                   | V    |

| Operating Junction Temperature                                                    | T <sub>J(max)</sub>                                                                                                 | -40 to 150                                  | °C   |

| Storage Temperature Range                                                         | T <sub>STG</sub>                                                                                                    | –65 to 150                                  | °C   |

| ESD Capability, Human Body Model (Note 2)                                         | ESD <sub>HBM</sub>                                                                                                  | 1.5                                         | kV   |

| Moisture Sensitivity Level                                                        | MSL                                                                                                                 | 1                                           |      |

| Lead Soldering Temperature<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>                                                                                                    | 260                                         | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe

Operating parameters.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

#### THERMAL CHARACTERISTICS

| Rating                                                                                                                                                                                     | Symbol                                                   | Value              | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|------|

| Thermal Characteristics (Note 4)<br>Thermal Resistance, Junction-to-Ambient (Note 5)<br>Thermal Resistance, Junction-to-CaseTop (Note 5)<br>Thermal Resistance, Junction-to-Board (Note 5) | R <sub>θJA</sub><br>R <sub>ψJT</sub><br>R <sub>ψJB</sub> | 99<br>16.1<br>63.1 | °C/W |

4. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

5. Values based on copper area of 50 mm<sup>2</sup> of 1 oz copper on 4-layer FR4 board per JEDEC 51\*-7.

# ELECTRICAL CHARACTERISTICS

$(-40^{\circ}C < T_J < 150^{\circ}C, \, 4.5 \ V < V_{IN} < 38 \ V, \, 4.5 \ V < V_{BST} - V_{SW} < 6 \ V, \ R_{OSC} = 51.1 \ k\Omega, \, unless otherwise specified)$

| Characteristic                                                                    | Conditions                                                                                                                          | Symbol                | Min        | Turn        | Мах         | llait |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|-------------|-------------|-------|

| Characteristic                                                                    | Conditions                                                                                                                          | Symbol                | Min        | Тур         | Max         | Unit  |

| GENERAL                                                                           |                                                                                                                                     | <b>L</b> .            | [          |             | r           | 1     |

| Quiescent Current<br>(I <sub>VIN</sub> + I <sub>VIN_CS</sub> + I <sub>BST</sub> ) | $\label{eq:VIN} \begin{array}{l} V_{IN} = 13.2 \ V, \ EN = 0 \ V, \ Sleep \ Mode, \\ -40^{\circ}C < T_A < 125^{\circ}C \end{array}$ | I <sub>Q,SLEEP</sub>  | -          | 4.25        | 6.2         | μΑ    |

|                                                                                   | $V_{IN}$ = 13.2 V, $V_{FB}$ = 1 V,<br>EN = 5 V, No Switching                                                                        | I <sub>Q2</sub>       | -          | 3.25        | 4.24        | mA    |

|                                                                                   | $V_{IN}$ = 13.2 V, $V_{FB}$ = 0 V,<br>EN = 5 V, Switching, No gate loads                                                            | I <sub>Q3</sub>       | 1          | 4.35        | 5.30        | mA    |

| LDO Current                                                                       | $V_{\text{IN}}$ = 13.2 V, $V_{\text{FB}}$ = 0 V, EN = 5 V, Switching, 3.3 nF on GH and GL                                           | I <sub>LDO</sub>      | 1          | 10          | 20          | mA    |

| Thermal Shutdown                                                                  | Guaranteed by Design                                                                                                                | T <sub>SD</sub>       | 150        | 180         | 210         | °C    |

| Thermal Shutdown Hysteresis                                                       | Guaranteed by Design                                                                                                                | T <sub>SD,HYS</sub>   | 1          | 10          | 20          | °C    |

| Undervoltage Lockout (V <sub>IN_IC</sub> )                                        | V <sub>IN_IC</sub> increasing<br>V <sub>IN_IC</sub> decreasing                                                                      | V <sub>UVLO</sub>     | 4.1<br>3.9 | 4.3<br>4.18 | 4.5<br>4.45 | V     |

| Undervoltage Lockout Hysteresis                                                   | _                                                                                                                                   | V <sub>UVHY</sub>     | 50         | 125         | 200         | mV    |

| SWITCHING REGULATOR                                                               |                                                                                                                                     |                       |            |             |             |       |

| Reference Voltage                                                                 |                                                                                                                                     | V <sub>ref</sub>      | 0.784      | 0.8         | 0.816       | V     |

| Minimum GH Off Time                                                               |                                                                                                                                     | t <sub>ON/MON</sub>   | 110        | 180         | 250         | ns    |

| Minimum GH Pulse Width                                                            | Static Operating                                                                                                                    | t <sub>P,MIN</sub>    | _          | 140         | 200         | ns    |

| OSCILLATOR                                                                        |                                                                                                                                     | <b>_</b>              |            |             |             |       |

| Switching Frequency                                                               | R <sub>OSC</sub> = 51.1 kΩ                                                                                                          | f <sub>ROSC</sub>     | 153        | 170         | 187         | kHz   |

|                                                                                   | $R_{OSC} = 23.2 \text{ k}\Omega$                                                                                                    |                       | 306        | 360         | 414         |       |

|                                                                                   | R <sub>OSC</sub> = 16.2 kΩ                                                                                                          |                       | 425        | 500         | 575         | N     |

| Ramp Voltage Amplitude                                                            |                                                                                                                                     | V <sub>Ramp</sub>     | 0.9        | 1.1         | 1.3         | V     |

|                                                                                   | Output to ad hu Danim                                                                                                               |                       | 70         | 70          | r           |       |

| DC Gain                                                                           | Guaranteed by Design                                                                                                                | A <sub>VEA</sub>      | 70         | 73          | -           | dB    |

| Gain-Bandwidth Product                                                            | Guaranteed by Design                                                                                                                | BW <sub>VEA</sub>     | 8.0        | 10          | -           | MHz   |

| Charge Currents                                                                   | Source, V <sub>COMP</sub> = 0 V                                                                                                     | I <sub>VEA,SO</sub>   | 2          | 4           | -           | mA    |

|                                                                                   | Sink, V <sub>COMP</sub> = 1.75 V                                                                                                    | I <sub>VEA,SI</sub>   | 1.3        | 3           | -           | mA    |

| FB Bias Current                                                                   | Guaranteed by Design                                                                                                                | I <sub>VEA,BIAS</sub> | _          | 0.1         | 1.0         | μΑ    |

| CURRENT SENSE AMPLIFIER                                                           |                                                                                                                                     | 1                     |            | 1           | 1           |       |

| Common-Mode Range                                                                 |                                                                                                                                     | V <sub>CMR</sub>      | 0          | -           | 10.0        | V     |

| Amplifier Gain                                                                    | $\begin{array}{l} 0 \leq (\text{CSP-CSN}) \leq 100 \text{ mV} \\ 0 \text{ V} \leq \text{CSN} \leq 10.0 \text{ V} \end{array}$       | G <sub>CSA</sub>      | -          | 1           | -           | V/V   |

| CURRENT ERROR AMPLIFIER                                                           |                                                                                                                                     |                       |            |             |             |       |

| DC Gain                                                                           | Guaranteed by Design                                                                                                                | A <sub>CSA</sub>      | 70         | 73          | -           | dB    |

| Gain-Bandwidth Product                                                            | Guaranteed by Design                                                                                                                | BW <sub>CSA</sub>     | 8.0        | 10          | -           | MHz   |

| Charge Currents                                                                   | Source, C <sub>COMP</sub> = 1.75 V                                                                                                  | I <sub>CSA,SO</sub>   | 2          | 4           | -           | mA    |

|                                                                                   | Sink, C <sub>COMP</sub> = 1.75 V                                                                                                    | I <sub>CSA,SI</sub>   | 1.3        | 3           | -           | mA    |

| FB Bias Current                                                                   | Guaranteed by Design                                                                                                                | I <sub>CSA,BIAS</sub> | _          | 0.1         | 1.0         | μΑ    |

| Clamping Voltage                                                                  |                                                                                                                                     | V <sub>CSA,CLP</sub>  | 2.7        | 3.3         | -           | V     |

#### **ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}C < T_J < 150^{\circ}C, 4.5 \text{ V} < V_{IN} < 38 \text{ V}, 4.5 \text{ V} < V_{BST} - V_{SW} < 6 \text{ V}, \text{ R}_{OSC} = 51.1 \text{ k}\Omega, \text{ unless otherwise specified})$

|                                                                    | , BST SW , 666                                                                              | 1                                          | -                         |            | 1          | 1    |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------|------------|------------|------|

| Characteristic                                                     | Conditions                                                                                  | Symbol                                     | Min                       | Тур        | Max        | Unit |

| CURRENT LIMIT                                                      |                                                                                             |                                            |                           |            |            |      |

| Average Current Limit Threshold                                    | $\begin{array}{c} 1.2 \ V \leq CSN \leq 6.5 \ V \\ 6.5 \ V < CSN \leq 10.0 \ V \end{array}$ | V <sub>ILIM,AV</sub>                       | 80<br>72                  | 100<br>100 | 125<br>133 | mV   |

| Cycle-by-Cycle Current Limit<br>Threshold Voltage                  |                                                                                             | VILIMPK                                    | 115                       | 165        | 215        | mV   |

| Cycle-by-Cycle Current Limit<br>Response Time                      | Guaranteed by Design                                                                        | t <sub>LIM</sub>                           | -                         | 200        | -          | ns   |

| Cycle-by-Cycle and Average Cur-<br>rent Limit Threshold Difference |                                                                                             | V <sub>LIM.DIF</sub>                       | 20                        | -          | -          | mV   |

| SYNC                                                               |                                                                                             |                                            |                           | •          |            |      |

| SYNC Frequency Range                                               | $F_{SW}$ is defined by $R_{OSC}$ switching frequency                                        | f <sub>SYNC</sub>                          | 0.94 x<br>F <sub>SW</sub> | -          | 600        | kHz  |

| SYNC Pin Bias Current                                              | V <sub>SYNC</sub> = 0 V<br>V <sub>SYNC</sub> = 5.0 V                                        | f <sub>sync,bias</sub>                     |                           | 0.1<br>10  | 0.2<br>20  | μA   |

| SYNC Threshold Voltage                                             | Logic Low<br>Logic High                                                                     | V <sub>SYNC,L</sub><br>V <sub>SYNC,H</sub> | _<br>2.0                  | -          | 0.8<br>-   | V    |

| 6.0 V LDO                                                          | ·                                                                                           |                                            |                           |            |            |      |

| Output Voltage                                                     | I <sub>OUT</sub> = 20 mA                                                                    | V <sub>LDO</sub>                           | 5.8                       | 6.0        | 6.2        | V    |

| Dropout Voltage                                                    | l <sub>OUT</sub> = 20 mA                                                                    | V <sub>LDO,DO</sub>                        | -                         | -          | 220        | mV   |

| Current Limit                                                      |                                                                                             | I <sub>LDO,CL</sub>                        | 30                        | 75         | 120        | mA   |

| GATE DRIVERS                                                       |                                                                                             |                                            |                           |            |            |      |

| GH Sink Current                                                    | V <sub>GH</sub> = 2 V, V <sub>IN_IC</sub> = 6 V, Guaranteed by<br>Design                    | I <sub>GH,SINK</sub>                       | 1                         | 1.5        | 2          | A    |

| GH Source Current                                                  | V <sub>GH</sub> = 4 V, V <sub>IN_IC</sub> = 6 V, Guaranteed by<br>Design                    | I <sub>GH,SRC</sub>                        | 1                         | 1.5        | 2          | A    |

| GL Sink Current                                                    | V <sub>IN_IC</sub> = 6 V                                                                    | I <sub>GL,SINK</sub>                       | 1                         | 1.5        | 2          | A    |

| GL Source Current Guaranteed by Design                             |                                                                                             | I <sub>GL,SRC</sub>                        | 1                         | 1.5        | 2          | Α    |

| GH to GL Delay                                                     | V <sub>IN</sub> = 13.2 V                                                                    | t <sub>GHGL,D</sub>                        | _                         | 40         | 70         | ns   |

| GL to GH Delay                                                     | V <sub>IN</sub> = 13.2 V                                                                    | t <sub>GLGH,D</sub>                        | _                         | 40         | 70         | ns   |

| SOFT START                                                         |                                                                                             |                                            |                           |            |            | -    |

| Time                                                               | F <sub>SW</sub> = 170 kHz, See Figure 19                                                    | t <sub>SSO</sub>                           | -                         | 14         | -          | ms   |

| ENABLE (EN)                                                        |                                                                                             |                                            |                           |            |            |      |

| Input Threshold                                                    | Logic Low<br>Logic High                                                                     | V <sub>ENLO</sub><br>V <sub>ENHI</sub>     | -<br>2.0                  |            | 0.8        | V    |

| Input Current                                                      | EN = 2.0 V                                                                                  | I <sub>EN,I</sub>                          | -                         | 3.0        | 10         | μA   |

| Minimum Disable Time                                               |                                                                                             | t <sub>EN,DIS</sub>                        | _                         | _          | 20         | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

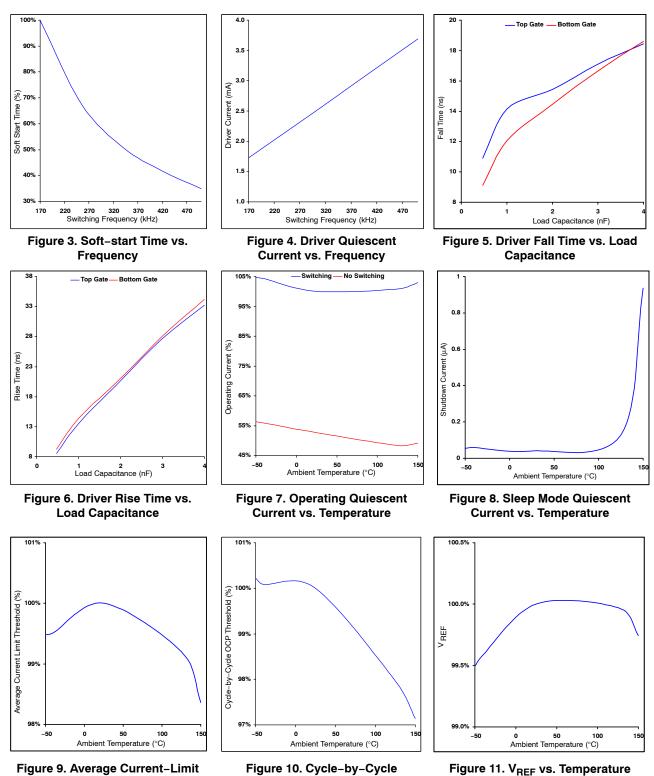

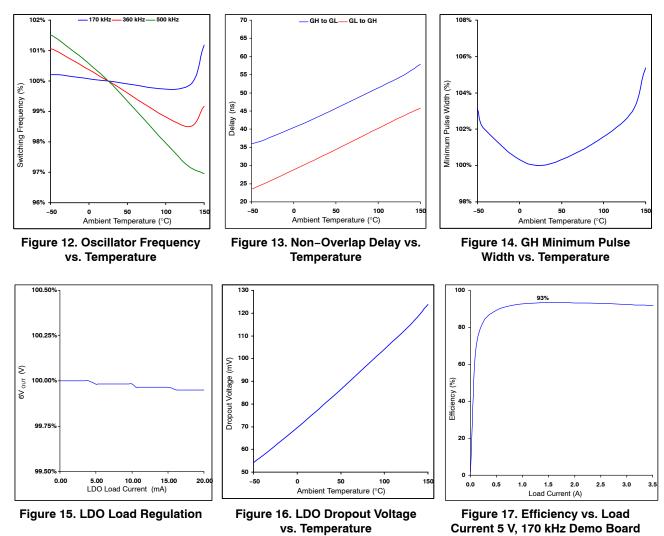

# **TYPICAL CHARACTERISTICS**

(T<sub>A</sub> = +25°C, V<sub>IN</sub> = 13.2 V, R<sub>OSC</sub> = 51.1 kΩ, unless otherwise noted)

Figure 11. V<sub>REF</sub> vs. Temperature

**Overcurrent Protection Threshold vs. Temperature**

Threshold vs. Temperature

# **TYPICAL CHARACTERISTICS**

(T<sub>A</sub> = +25°C, V<sub>IN</sub> = 13.2 V, R<sub>OSC</sub> = 51.1 kΩ, unless otherwise noted)

#### DETAILED OPERATING DESCRIPTION

#### General

The NCV8856A is a synchronous buck controller with internal 1.5 A gate drivers designed to drive N-channel MOSFETs. The internal gate drivers simplify design, improve performance and efficiency and minimize board area. The controller has an 800 mV, 2.0% reference, allowing a wide range of precise output voltage programmability. The NCV8856A operates at a fixed frequency over a range of 170 kHz to 500 kHz set by an external resistor to ground facilitating design tradeoffs such as efficiency versus component size and cost. An external clock signal can also be used to synchronize the NCV8856A to a higher operating frequency during operation.

To minimize the impact on the power handling components and the input power rail, inrush current during start-up is limited by an internally-controlled output voltage soft-start. Inductor current is also limited via

average current limiting (ACL) and cycle-by-cycle overcurrent protection (OCP). Thermal shutdown (TSD) is also implemented to protect the device from overheating.

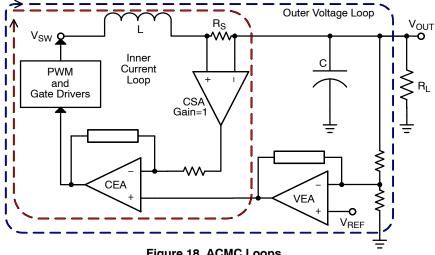

#### Average Current Mode Control

The NCV8856A employs an average current mode control (ACMC) architecture to regulate the output voltage. As implied by the name, ACMC regulates output voltage based on the average current supplied to the output, and is thereby better suited to applications sensitive to the behavior of either input or output current, such as power factor correction, LED lighting control, or operation in discontinuous conduction (DCM). As with peak current control, compensation for input voltage changes, and output current monitoring and limiting are inherent - with the additional ability of ACMC to base these functions on average current.

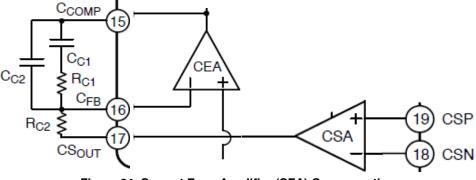

ACMC uses two loops, as shown in Figure 18. Through the unity gain current sense amplifier (CSA) and high-gain current error amplifier (CEA), the inner current loop controls the inductor current. The current loop reacts to input voltage changes - compensating for line transients. Using the voltage error amplifier (VEA), the outer voltage loop monitors the output voltage and reacts to output load changes - compensating for load transients.

Unlike voltage mode control (VMC) regulators - which typically require a Type-III compensation network for adequate transient response - ACMC regulators use two Type-II compensators. This simplifies the compensator design and optimization process, while offering faster transient response than a single Type-II compensation network. Type-II compensation places a zero and two poles in each of the error loops to stabilize converter operation. Each compensator requires a resistor and two capacitors (shown as complex impedances in Figure 18) in the feedback path the error amplifier. A resistor from the CSA

output to the CEA scales the CEA gain at all frequencies. A pair of resistors forms a resistive attenuator from the output to set the output voltage and scale the VEA gain at all frequencies.

#### ENABLE

The enable pin (EN) is a TTL-compatible input used to activate internal circuitry. The NCV8856A is disabled when the EN pin voltage is below the enable input low threshold - shutting off both external FETs, and putting the part into a low quiescent current sleep mode. Once the device has been disabled, it must remain disabled for the minimum disable time. When the EN pin voltage goes above the enable input high threshold, the 6VOUT output comes up, and then the soft-start begins. The EN pin can be tied to VIN in order to automatically enable the part.

#### 6VOUT

6VOUT is the output of a low dropout (LDO) linear regulator that regulates voltage from the VIN pin down to 6 V. A small ceramic capacitor must also be connected between 6VOUT and ground - close to the 6VOUT pin. When VIN voltage is sufficiently high, applying a high level to the EN pin activates the 6VOUT output. When the part is enabled and VIN is below the 6VOUT target voltage, the LDO is in dropout and tracks VIN. The LDO regulates its output once VIN voltage is above the 6VOUT target plus dropout voltage. The 6VOUT output directly powers the low-side gate driver, and must be externally connected through a low leakage (< 100 µA at Tmax) diode to the BST pin - charging the BST capacitor during the off-time to provide a floating voltage for the high-side driver. Since 6VOUT supplies charge to both the BST capacitor and the low-side driver, the LDO capacitor should be larger than the BST capacitor. A CLDO/CBST capacitor ratio of 10:1 is recommended along with a CLDO value of 1–4.7  $\mu F\!$ 6VOUT must also be connected externally to the VIN IC pin through a small RC filter network to power internal circuits. A short to ground or overcurrent condition on the 6VOUT pin will be current limited. Use of 6VOUT output current for additional external circuits will increase internal LDO dissipation, and must not produce an overcurrent condition. Such use should be limited to PCB locations close to the NCV8856A.

#### VIN\_IC

With the exception of the gate drivers, the NCV8856A is powered by the voltage connected to the VIN\_IC pin. A small (0.1  $\mu$ F recommended) ceramic capacitor should be connected between VIN\_IC and ground, and close to the VIN\_IC pin. A low value resistor must be connected between the VIN\_IC and 6VOUT pins.

#### UVLO

An Undervoltage Lockout (UVLO) monitor at the VIN\_IC pin ensures that unexpected behavior does not occur when VIN\_IC is too low to support internal NCV8856A circuits. If enabled, the IC will start up when VIN\_IC exceeds the increasing UVLO threshold (START threshold) and will shut down when VIN\_IC drops below the decreasing UVLO threshold (STOP threshold).

If VIN\_IC passes the UVLO threshold, but VIN remains below the VOUT setpoint after soft-start, the switcher will run at max duty cycle until VIN voltage is higher.

If EN is high and VIN\_IC is below the UVLO START threshold, a totally unloaded output will slowly rise above

zero volts. The high EN signal activates internal rails, allowing a small leakage current to flow out pins connecting to the output; the high side MOSFET also contributes leakage current directly from VIN. A 1k resistor connected from the power supply output to ground avoids a non-zero output voltage under these conditions.

#### **Thermal Shutdown**

The NCV8856A provides Thermal Shutdown (TSD), which monitors the die temperature and turns off the top and bottom gate drivers if an over temperature condition is detected. The internal soft-start capacitor is also discharged. A normal soft-start will occur when the die temperature falls below the TSD threshold minus TSD hysteresis.

#### **Duty Cycle and Maximum Pulse Width Limits**

In steady state operation, the duty cycle (ratio of GH time to switching period) stabilizes at an operating point roughly the ratio of output voltage to input voltage. A built in minimum GH off-time ensures that the bootstrap supply capacitor gets charged every cycle, which enforces a slightly different maximum duty cycle depending on switching frequency. The NCV8856A can achieve at least a 95% duty cycle while operating at frequencies up to 200 kHz (89% at up to 500 kHz).

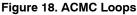

#### Internal Soft-Start

The NCV8856A features an internal soft-start function, which reduces inrush current and output voltage overshoot. Figures 19 and 20 show a typical soft-start sequence. Soft-start is achieved by ramping up the internal soft-start voltage (VSS), which is applied to the non-inverting input of the voltage error amplifier - effectively limiting the slew rate of VOUT rising. This ramp is generated by charging an internal soft-start capacitor based on the internal oscillator, causing the soft-start time to be inversely related to the frequency set by ROSC. The internal soft-start capacitor is discharged when the part is disabled, enters TSD, or enters UVLO - ensuring a proper start-up when the part is re-enabled, leaves TSD or leaves UVLO. This sequence begins when VIN IC passes the UVLO START threshold or when the part is enabled and the 6VOUT output has risen. After an initial delay to read internal memory, switching begins - with the output quickly rising to a low voltage followed by a controlled rise to target voltage. If VIN voltage is constant during soft-start, the duty cycle increases as VOUT climbs to the set point, or until maximum duty cycle is reached if VIN is insufficiently high.

Figure 19. Normal Start-up

#### Normal Shutdown Behavior and Sleep Mode

Normal shutdown occurs if the input supply drops below the UVLO STOP threshold, the part enters TSD, or the part is disabled by applying a low voltage to the EN pin. Under these conditions, GH and GL both go low to stop switching, the switch node enters a high impedance state and the output inductor and capacitors discharge through the load, and the internal soft–start capacitor is discharged. When disabled by applying a low voltage to the EN pin, the 6VOUT LDO turns off, its output capacitor is allowed to discharge, and VIN current reduces to the sleep mode quiescent current.

#### **Gate Drivers**

The NCV8856A includes 1.5 A gate drivers to switch external N-Channel MOSFETs. This allows the NCV8856A to address high-power, as well as low-power conversion requirements. The gate drivers also include adaptive non-overlap circuitry. The non-overlap circuitry minimizes power dissipation - increasing efficiency - by minimizing the body diode conduction time, while protecting against cross-conduction (shoot-through) of the MOSFETs. A detailed block diagram of the non-overlap and gate drive circuitry used in the chip and related external components is shown in Figure 21. A capacitor connected from VSW to BST, and a diode connected from 6VOUT to BST create a bootstrap supply at the BST pin for the floating, high-side gate driver. This ensures that the voltage on BST is about 6VOUT higher than VSW, less a diode drop vielding a gate drive voltage high enough to enhance the high-side MOSFET. The BST capacitor supplies the charge used by the gate driver to charge the high-side MOSFET input capacitance, and is typically chosen to be at least a decade larger than the input capacitance (0.1 µF recommended). Since the BST capacitor only recharges when the low-side MOSFET is on - pulling VSW down to ground - the NCV8856A enforces a minimum GH off-time.

Figure 21. Gate Driver Block Diagram

Careful selection and layout of external components is required to realize the full benefit of the onboard drivers. The capacitors between 6VOUT and GND and between BST and VSW must be placed as close as possible to the IC. The current paths for the GH and GL connections must minimize parasitic resistance and inductance.

#### **Current Limiting and Overcurrent Protection**

The NCV8856A implements average current limiting (ACL) and cycle-by-cycle overcurrent protection (OCP) to protect the power switches, inductor, current sense resistor and loads. The current through the inductor also flows through a current sense resistor – developing a voltage across the resistor proportional to current that is continuously sensed at the CSP and CSN pins, is summed with a bias voltage, and appears at the output of the Current Sense Amplifier (CSA).

# ACL

The current and voltage error amplifiers (CEA and VEA) make the VEA output voltage (VCOMP) equal the average CSA amplifier output voltage (CSOUT) after a small delay reflecting the averaging action of both error amplifiers. VCOMP voltage is compared to a fixed internal (ACL) voltage threshold. VCOMP is pulled down if it exceeds the threshold, and through the action of the CEA, this lower VCOMP voltage reduces the PWM pulsewidth – reducing the average current through the inductor until the average is at the ACL threshold. In steady–state operation, increasing the load while in ACL will cause the duty cycle and VOUT to decrease proportionally without jitter or skipping pulses. An advantage of this method of current limiting is that the NCV8856A will limit large transient currents yet resume normal operation on the following cycle. The current will not run away or latch the part off in case of a short, which is a characteristic of some other methods of current limiting.

# OCP

If the differential plus bias voltage exceeds the OCP threshold (which is above the ACL threshold), the PWM pulse is immediately terminated and will not switch back on until the current through the inductor has dropped the instantaneous CSA output voltage below the OCP threshold. Once the inductor current is below the OCP threshold, the part will begin switching again, although current may be limited by ACL until the inductor current drops below the ACL threshold.

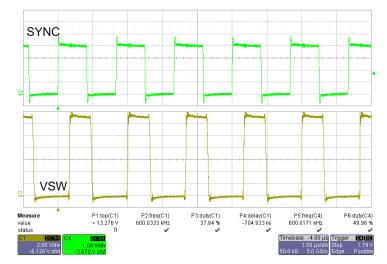

#### SYNC Feature

An external clock signal can synchronize the NCV8856A to a frequency higher than that programmed by the resistance at the ROSC pin. The rising edge of the SYNC pulse turns on the power switch after a 0.5  $\mu$ s delay to start a new switching cycle, as shown in Figure 22. The SYNC threshold is TTL logic compatible, and the duty cycle of the SYNC pulses can vary from 10% to 90%. The SYNC frequency (if used) is typically chosen to meet important EMC requirements, and the Rosc controlled frequency should be set relative to that SYNC frequency (see the Switching Frequency Selection Section of the Design Methodology). The highest SYNC frequency must not exceed the SYNC Frequency Range maximum limit.

Figure 22. Synchronization from 170 kHz to an external 600 kHz signal

# **APPLICATIONS INFORMATION**

# **Design Methodology**

Choosing external components for the NCV8856A entails the following design process:

- 1. Determine operational requirements

- 2. Select switching frequency

- 3. Select current sensor

- 4. Select output inductor

- 5. Select output capacitors

- 6. Select input capacitors

- 7. Select current loop compensator components

- 8. Select components to set output voltage

- 9. Select voltage loop compensator components

# (1) Operational Parameter Definition

Before selecting components, certain operational requirements must be determined. These are application-dependent and include the following:

V<sub>IN(max)</sub>: maximum input voltage [V]

V<sub>IN(typ)</sub>: typical input voltage [V]

V<sub>IN(min)</sub>: minimum input voltage [V]

V<sub>OUT</sub>: output voltage [V]

$I_{OUT}\!\!:$  output current, range from minimum to maximum, and during start-up [A]

I<sub>CL</sub>: desired typical current limit [A]

The following basic calculations will be used in several parts of the design process:

$$D_{MIN} = \frac{V_{OUT}}{V_{IN(max)}} \tag{eq. 1}$$

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}(\mathsf{typ})}} \tag{eq. 2}$$

$$\mathsf{D}_{\mathsf{MAX}} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}(\mathsf{min})}} \tag{eq. 3}$$

Where:

D<sub>MIN</sub>: minimum duty cycle [%]

D: typical duty cycle [%]

D<sub>MAX</sub>: maximum duty cycle [%]

These are ideal duty cycles. Actual duty cycles will be marginally higher than these calculated values due to voltage drops in the MOSFETs, inductor and current sense resistor caused by the output load.

# (2) Switching Frequency Selection

Determining the best switching frequency within the specified NCV8856A range should be based on several considerations:

- 1. The physical size or cost of the output filter components (inductor and capacitors)

- 2. The response speed needed for line and load transients

- 3. The amount of heat that can be removed from the controller and MOSFETs, or the required efficiency

- 4. The required minimum or maximum conversion ratio (ratio of minimum or maximum Vin, respectively, to Vout)

- 5. Avoiding producing EMI at frequencies that would interfere with nearby circuits

Operation at higher switching frequencies decreases the output inductor and capacitor values required to achieve acceptable current and voltage ripple. Lower value components are physically smaller and typically cost less.

Higher switching frequency improves regulator response time both by use of a lower value inductor to quickly support load current changes, and also by allowing use of a higher frequency 0dB loop gain crossover (see the Compensator Design section).

Operation at higher switching frequencies increases controller and MOSFET switching losses, which lead to higher temperatures and cooling requirements at maximum load. The decreased efficiency caused by the higher losses may be of special importance at light loads.

Besides the specified switching frequency limits, two other NCV8856A characteristics set limits on the maximum allowable switching frequency: minimum off-time and minimum on-time. These represent two different restrictions on maximum switching frequencies, as follows:

$$F_{SW(max)1} = \frac{1 - D_{MAX}}{T_{MinOff}}$$

[Hz] (eq. 4)

$$F_{SW(max)2} = \frac{D_{MIN}}{T_{MinOn}} \qquad [Hz] \qquad (eq. 5)$$

Where:

$F_{SW(max)1}$ : maximum switching frequency due to minimum off-time [Hz]

T<sub>MinOff</sub>: minimum off-time [s]

$F_{SW(max)2}$ : maximum switching frequency due to minimum on-time [Hz]

T<sub>MinOn</sub>: minimum on-time [s]

Alternatively, the minimum and maximum operational input voltage can be calculated as follows:

$$V_{IN(min)} = \frac{V_{OUT}}{1 - T_{MinOff} \cdot F_{SW}} \qquad [V] \qquad (eq. 6)$$

$$V_{IN(max)} = \frac{V_{OUT}}{T_{MinOn} \cdot F_{SW}} \qquad [V] \qquad (eq. 7)$$

Where:

F<sub>SW</sub>: switching frequency [Hz]

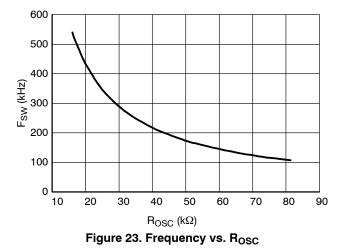

The switching frequency is programmed by selecting the resistor connected between the  $R_{OSC}$  pin and ground. The grounded side of this resistor should be directly connected to the AGND pin. Avoid running any noisy signals under the resistor, since injected noise could cause frequency jitter.

The graph in Figure 23 shows the relationship between  $R_{OSC}$  resistance and switching frequency. The following formula yields frequency programming resistance accurate to approximately 4%:

$$R_{OSC} = \frac{8300000}{F_{SW}}$$

[ $\Omega$ ] (eq. 8)

Where:  $R_{OSC}$ : frequency program resistor [ $\Omega$ ]

F<sub>SW</sub>: switching frequency [kHz]

Some specific values for switching frequency with standard 1% resistors may be found in Table 1.

Table 1. Frequency vs. R<sub>OSC</sub>

| F <sub>SW</sub> (kHz) | R <sub>OSC</sub> (kΩ) |

|-----------------------|-----------------------|

| 170                   | 51.1                  |

| 250                   | 34.8                  |

| 300                   | 28.7                  |

| 360                   | 23.2                  |

| 500                   | 16.2                  |

In cases where the switching frequency is selected to avoid interfering with signals known to be sensitive to certain frequencies,  $R_{OSC}$  should program frequency to a value that avoids sensitive frequencies by a margin exceeding the  $f_{ROSC}$  tolerance.

In cases where a SYNC signal is used to avoid sensitive frequencies, the  $R_{OSC}$  resistance should be chosen such that the maximum internal oscillator frequency ( $f_{ROSC}$  plus tolerance) is no more than 6% higher than the minimum SYNC frequency.

The equation relating minimum  $R_{OSC}$  resistance to the  $R_{OSC}$  resistor tolerance and minimum SYNC frequency is:

$$R_{OSC} \geq \frac{0.91 \times 8300 \times (1 + 1.6 \times R_{TOLERANCE})}{F_{SYNCmin}} [k\Omega]^{(eq. 9)}$$

Where:

$R_{TOLERANCE}$  is either 0.01 for 1% resistors or 0.05 for 5% resistors

$R_{OSC}$  is in k $\Omega$

F<sub>SYNCmin</sub> is in kHz

For the 1% resistor series, this equation becomes:

$$R_{OSC} \ge \frac{7674}{F_{SYNCmin}}$$

[k $\Omega$ ] (eq. 10)

The next-higher standard value should be chosen for the  $R_{OSC}$  resistor.

The soft-start time is a function of switching frequency and can be estimated as follows:

$$t_{SS} \approx \frac{F_0}{F_{SW}} \cdot t_{SS0} \qquad [ms] \qquad (eq. 11)$$

$F_0:$  frequency condition specified for  $t_{SS0}\,[\rm kHz]$

F<sub>SW</sub>: switching frequency [kHz]

$t_{SS0}$ : specified soft-start parameter [ms]

#### (3) Current Sensor Selection

Current sensing for average current mode control relies on the inductor current signal. This is translated by a current sensor into a voltage, which is then measured differentially by the current sense amplifier, which produces a single-ended output for use as a control signal. The easiest means of implementing the current sensor is by use of a sense resistor in series with the output inductor. Alternative methods, such as lossless inductor current sensing, are feasible but beyond the scope of this document. A sense resistor [ $\Omega$ ] should be selected as follows:

$$R_{S} = \frac{V_{CL}}{I_{CL}}$$

(eq. 12)

Where:

$V_{CL}$ : current limit threshold voltage [V] (either  $V_{ILIM.AV}$  or  $V_{ILIMPK}$ )

$I_{CL}:$  desired current limit [A] (corresponding to either  $V_{ILIM,AV} \mbox{ or } V_{ILIMPK})$

The size of the sense resistor should be chosen based on the power dissipated by the resistor as given by:

$$\mathsf{P}_{\mathsf{RS}} = \frac{\mathsf{V}_{\mathsf{CL}(\mathsf{max})}^{2}}{\mathsf{R}_{\mathsf{S}}} \qquad [\mathsf{W}] \qquad (\mathsf{eq. 13})$$

Where:

$V_{CL(max)}$ : the maximum limit specified for the current limit threshold voltage  $V_{ILIM,AV}$  [V]

#### (4) Output Inductor Selection

Inductors have many important characteristics. Among the most important for Automotive applications of the NCV8856A are:

- 1. Value

- 2. Saturation characteristic

- 3. DC resistance (DCR)

- 4. Operating Temperature range

- 5. Size including height

- 6. Cost

- 7. Mounting configuration including the ability to inspect solder joints

- 8. Containment of magnetic flux (shielding)

Decisions on most of these characteristics can be treated as "go/no-go" considerations.

Generally, a "shielded" inductor must be used in order to meet Automotive EMC requirements. And an inductor with "wetted flanks" should be used for easiest post–assembly inspection.

Since the inductor is often one of the largest components in the power supply, a low inductor value is preferred in space–constrained applications, since lower inductor values generally correspond to smaller physical size. Also – except for the very smallest inductors – the smaller sized inductors within a supplier's particular technology series are typically less expensive.

The inductor Operating Temperature Range must include the full application operating ambient temperature range plus additional range on the high end for internal inductor dissipation, which is dominated by the inductor DCR loss at the frequencies used by the NCV8856A. Most inductor suppliers offer an online tool to calculate inductor internal temperature rise for any chosen ambient and maximum application load current. Internal temperature above maximum inductor operating temperature requires selecting a different inductor. A lower value inductor within the same product series will have a lower DCR and therefore less internal temperature rise. A different inductor product series might have a lower thermal resistance – and therefore lower internal temperature rise – for the same DCR.

If inductor maximum temperature is within the inductor temperature rating, the impact of inductor dissipation on efficiency may still need to be considered. If the application requires higher efficiency than the online loss calculator predicts, inductor dissipation can be lowered by selecting a different inductor with lower DCR.

Many inductor manufacturers specify saturation current at a 30% decrease in inductance. To prevent such a large value change from affecting regulator stability in normal operation, the saturation current rating should be well above the peak overload current. For the NCV8856A, this is the combined average current limit (max limit) plus half of the peak-to-peak ripple current. Saturation current varies significantly with temperature for some inductors. Inductors with ferrite and other alloy cores (sometimes called "dust" cores) may fall into this category. Unless the core material is "powdered iron", the temperature variation of saturation current should be checked to be sure saturation current stays well above the peak current at maximum inductor temperature.

The inductor value should initially be chosen to produce a ripple current equaling 20–40% of the rated output current. If found to be necessary later in the design process in order to meet output ripple voltage or transient response requirements, this value can be increased or decreased, respectively.

The peak-to-peak ripple current [Ap-p] is given by the following equation:

$$\Delta i_{L} = \frac{V_{OUT} \times (1 - D)}{L \times F_{SW}}$$

[A] (eq. 14)

From this equation it is clear that the ripple current increases as L decreases,

The ripple current is at a maximum when the duty cycle is at a minimum value and vice versa, as follows:

$$\Delta i_{L(max)} = \frac{V_{OUT} \times (1 - D_{MIN})}{L \times F_{SW}} \quad [A]$$

(eq. 15)

$$\Delta i_{L(min)} = \frac{V_{OUT} \times (1 - D_{MAX})}{L \times F_{SW}}$$

[A] (eq. 16)

Where:

$\Delta_{iL(max)}$ : maximum inductor ripple current [Ap-p]  $\Delta_{iL(min)}$ : minimum inductor ripple current [Ap-p]

The peak and valley values of the triangular current waveform are as follows:

$$i_{L(pk)} = I_{OUT} + \frac{\Delta i_L}{2}$$

[A] (eq. 17)

$$i_{L(vly)} = I_{OUT} - \frac{\Delta i_L}{2} \qquad [A] \qquad (eq. 18)$$

Where:

$i_{L(pk)}$ : peak (maximum) value of ripple current [A]  $i_{L(vly)}$ : valley (minimum) value of ripple current [A]  $\Delta_{iL}$ : inductor ripple current at the input voltage of interest – usually  $\Delta i_{L(max)}$  [Ap–p]

Larger inductor values decrease the speed at which inductor current can change in response to output load changes. This increases the magnitude of output voltage perturbations, since output capacitance must supply (or absorb) the load change while inductor current changes. For a given load change, lower inductance produces either less output perturbation for a given output capacitance, or the same perturbation with less output capacitance, due to the faster inductor current change capability. But unless output capacitance is increased, lower inductance increases output voltage ripple.

#### (5) Output Capacitor Selection

One or more multilayer ceramic capacitors (MLCC) are recommended for use due to their low equivalent series resistance (ESR) and inductance (ESL), which reduce high-frequency output voltage noise components such as ripple voltage.

A good criterion for determining the minimum amount of MLCC output capacitance is the maximum amount of output voltage ripple that is acceptable at maximum DC load. Inductor ripple current causes a 90-degree lagging output voltage ripple [Vp-p] on the output capacitance:

$$V_{Q} = \frac{I_{L}}{2 \times \pi \times C_{MLCC} \times F_{SW}} \quad [V] \quad (eq. 19)$$

Where  $C_{MLCC}$  = total capacitance of MLCC output capacitors [F]

Also, the ripple current produces an in-phase voltage ripple [Vp-p] on the ESR of the output capacitors as follows:

$$V_{ESR} = i_L \times R_{ESR}$$

[V] (eq. 20)

Where:

$R_{ESR}$ : equivalent ESR of all output capacitors in parallel (both MLCC and bulk) [ $\Omega$ ]

The total output voltage ripple [Vp-p] in steady-state operation is:

$$V_{\text{RIP}} \approx V_{\text{Q}} + V_{\text{ESR}}$$

[V] (eq. 21)

The very low ESL of MLCC output capacitors does not contribute to output ripple voltage when output inductance is above 1uH. But the PCB trace between the output inductor and MLCC caps can add ESL, so MLCC capacitors should always be located between the load and the output inductor.

Output capacitance is a primary determinant of power supply response to a load transient. During the first few microseconds of a load step, output capacitance supplies the incremental load current, but discharges in the process. The controller recognizes the load step and increases the duty cycle, but the current slew rate is limited by the inductor, and output voltage temporarily dips. Similarly, during a load release, the output voltage exhibits a momentary peak. Higher output capacitance decreases the magnitude of these voltage perturbations.

Providing sufficient capacitance for acceptable transient performance at an acceptable cost may require bulk capacitors to be used in addition to MLCC capacitors. If so, aluminum polymer/hybrid bulk capacitors are recommended instead of aluminum electrolytic capacitors due to their low  $-40^{\circ}$ C/25°C ESR ratio. Use of bulk capacitors having a high  $-40^{\circ}$ C/25°C ESR ratio may result in an ineffective output filter along with decreased stability under cold operating temperature conditions.

For a given output voltage dip caused by a given load step-up, the following minimum total capacitance is required:

$$C_{MIN} = \frac{\Delta I_{OUT} \times \left(\frac{1}{4 \times F_{CO}} + \frac{1}{F_{SW}}\right)}{2 \times \Delta V_{DIP}} \qquad [F] \qquad (eq. 22)$$

Where:

$\Delta I_{OUT}$ : Load current step increase [A]

F<sub>CO</sub>: Control loop 0dB gain frequency [Hz]

$\Delta V_{DIP(max)}$ : Maximum allowed output voltage dip upon load step-up [V]

The worst-case output voltage peak occurs when load current initially at the current limit (with output voltage still in regulation) is released (goes to zero). The minimum capacitance for a given peak is:

$$C_{MIN} = \frac{L \cdot I_{CL}^2}{(V_{OUT} + \Delta V_{OS})^2 - V_{OUT}^2} \quad [F] \quad (eq. 23)$$

Where:

$V_{OS(max)}$ : output voltage overshoot peak on CMIN upon removal of an overload [V]

I<sub>CL</sub>: average current limit [A]

The minimum output capacitance should be chosen as the larger of that needed to limit both output voltage dip and overshoot. The worst-case overshoot peak for the chosen output capacitance ( $C_{OUT}$ ) is:

$$\Delta V_{OS} = \sqrt{\frac{L \cdot I_{CL}^2}{C} + V_{OUT}^2} - V_{OUT} \qquad (eq. 24)$$

During soft-start, inductor current must charge the output capacitance as well as supply the load. The sum of these currents should be no higher than the average current limit. For a given average current limit the maximum output capacitance is:

$$C_{MAX} = \frac{(I_{CL} - I_{OUT(i)}) \cdot t_{SS}}{V_{OUT}} \qquad (\text{eq. 25})$$

Where  $I_{OUT(i)}$  = highest instantaneous load current prior to output voltage reaching regulation [A]

The current needed from the input supply to charge this output capacitance during soft-start is:

$$I_{\text{INRUSH}} = \frac{C_{\text{OUT}} \cdot V_{\text{OUT}}}{t_{\text{SS}}} + D \times I_{\text{OUT(i)}} \quad (\text{eq. 26})$$

If the inrush current is higher than the steady-state input current with the maximum load, then the input fuse (if used) should be rated accordingly.

#### (6) Input Capacitor Selection

Input capacitors conduct the inductor current during the on time of the high–side MOSFET. The largest harmonic of the input capacitor ripple current is at the switching frequency, and at high loads, the RMS value of this current given by the following equation may be much higher than the inductor ripple current:

$$I_{\text{IN(RMS)}} = I_{\text{OUT}} \times \sqrt{D \cdot (1 - D)} \qquad [A] \qquad (\text{eq. 27})$$

The above equation reaches its maximum value with D = 0.5, where  $I_{IN(RMS)} = I_{OUT}/2$ . The input capacitors must be rated to handle a ripple current of one-half the maximum output current at the switching frequency. ESR is the major cause of losses in the input capacitors, so input capacitors need low ESR at the switching frequency to minimize loss, which is given by:

$$\mathsf{P}_{\mathsf{CIN}} = \mathsf{I}_{\mathsf{IN}(\mathsf{RMS})}^2 \cdot \mathsf{R}_{\mathsf{ESR}(\mathsf{CIN})} \qquad [\mathsf{W}] \qquad (\mathsf{eq. 28})$$

Where  $R_{ESR(CIN)}$  = equivalent series resistance of all input capacitors in parallel

Electrolytic, polymer and/or ceramic capacitors should be used. If a tantalum must be used, it must be surge protected to prevent against capacitor failure. Ceramic capacitors are recommended in parallel with bulk input capacitors, since their lower ESR will handle most of the ripple current with minimum power loss. An additional capacitor with a value of 0.01  $\mu$ F to 0.1  $\mu$ F is also recommended to be placed at the high-side MOSFET.

#### (7) Current Error Amplifier (CEA) Compensator Design

Compensator tuning stabilizes the converter with a minimum amount of (and minimum cost of) output capacitance.

The NCV8856A employs Average Current Mode Control (ACMC) which entails both an inductor current control feedback loop, and an output voltage control feedback loop. Separate error amplifiers are used for each loop – each with simple Type-II compensation. The Current Error Amplifier (CEA) compensation sets the characteristics of the "inner" current control loop, and the Voltage Error Amplifier (VEA) compensation sets the characteristics of the "outer" voltage control loop. "Closing" the CEA loop with inductor current feedback provides an additional gain block to the outer voltage feedback loop, without the phase lag that typically comes with such gain. The use of two amplifiers provides a large total amount of loop gain at low and mid-frequencies which allows lower output capacitance than many other control methods.

Compensator design involves determining the frequencies of zeros and poles in the CEA and VEA loops in order to stabilize the converter over the desired range of input voltage and output load. Initial compensator component values are derived from equations, and subsequently tuned through simulation, or measurement of output voltage response to line and load steps.

As shown in Figure 24, CEA compensation provides a low frequency pole (at the origin, via capacitor C<sub>C1</sub>), and a mid-frequency zero - above which, CEA gain is flat. Capacitor C<sub>C1</sub> and resistor R<sub>C1</sub> set the zero at a frequency at least as high as the pole formed by the peak current mode sampling effect in the power stage. The flat gain is then set (typically well above 1) by selecting a value of  $R_{C2}$  that amplifies (and inverts) inductor current downslope to no greater than the upslope of the internal ramp.

A second pole realized by C<sub>C2</sub> can reduce the impact of switching noise on the CEA loop if placed near the switching frequency.

Figure 24. Current Error Amplifier (CEA) Compensation

Since standard capacitor values are spaced much further apart than standard resistor values, compensation should start by choosing a standard value for the CEA low

frequency pole capacitance  $C_{C1}$  such as 2.2 nF. The CEA zero frequency is then set by resistor R<sub>C1</sub> from:

C<sub>C1</sub>: value chosen for the capacitor setting the low

$$R_{C1} = \frac{F_{SW} \times L_{MIN} \times R_{CS} \times V_{IN} \times R_{L} \times C_{OUT}}{1.1 \times C_{C1} \times (R_{L} \times (R_{CS}(0.5 \times V_{IN} - V_{OUT}) + F_{SW} \times L_{MIN} \times V_{R}) + F_{SW} \times L_{MIN} \times R_{CS} \times V_{IN})} [\Omega]$$

(eq. 29)

here:

$$C_{OUT}: \text{ total output capacitance } [F]$$

Where:

F<sub>SW</sub>: switching frequency [Hz] L<sub>MIN</sub>: inductor value at the low tolerance limit [H]  $R_{CS}$ : current sense resistance [ $\Omega$ ] V<sub>IN</sub>: minimum input voltage [V]  $R_L$ : minimum load resistance [ $\Omega$ ]

$$f_{ZC} = \frac{R_{L} \times \left(R_{CS} \times \left(0.5 \times V_{IN} - V_{OUT}\right) + F_{SW} \times L_{MIN} \times V_{R}\right) + R_{CS} \times V_{IN}}{2 \times \pi \times F_{SW} \times L_{MIN} \times R_{CS} \times V_{IN} \times R_{L} \times C_{OUT}}$$

$$[Hz] \qquad (eq. 30)$$

Where:

frequency pole [F]

V<sub>OUT</sub>: output voltage [V]

V<sub>R</sub>: minimum internal ramp voltage [V]

This sets the zero frequency at:

The value of  $R_{C2}$  to set the overall gain of the CEA is:

$$\mathsf{R}_{\text{C2}} = \frac{\mathsf{R}_{\text{CS}} \times \mathsf{V}_{\text{OUT}} \times \mathsf{R}_{\text{C1}} \times \mathsf{A}_{\text{CSA}}}{\mathsf{F}_{\text{SW}} \times \mathsf{L}_{\text{MIN}} \times \mathsf{V}_{\text{R}}} \quad [\Omega] \quad (\text{eq. 31})$$

$A_{CSA}$ : maximum current sense amplifier gain [V/V]

Another pole placed near the switching frequency to reduce the impact of switching noise on the CEA loop can be realized by  $C_{C2}$ :

$$C_{C2} = \frac{C_{C1}}{2 \times \pi \times f_{HFPC} \times R_{C1} \times C_{C1} - 1} \quad [F] \quad (eq. 32)$$

#### Where:

f<sub>HFPC</sub>: frequency desired for the CEA high frequency pole

#### (8) Setting Output Voltage

As shown in Figure 25, a resistive divider from the regulator output to the negative input of the VEA sets the

output voltage. This resistive divider is composed of a resistor ( $R_{F1}$ ) from the output voltage to the VEA negative input and a resistor ( $R_{F0}$ ) from the VEA negative input to ground.  $R_{F1}$  is usually between 30 k $\Omega$  and 100 k $\Omega$ , and the value of  $R_{F0}$  is calculated as follows:

$$R_{F0} = \frac{R_{F1} \times V_{REF}}{V_{OUT} - V_{REF}} \qquad [\Omega] \quad (eq. 33)$$

Where:

$R_{F1}$ : [ $\Omega$ ]

V<sub>REF</sub>: internal 0.8 V reference [V]

#### (9) Voltage Error Amplifier (VEA) Compensator Design

As shown in Figure 25, Voltage Error Amplifier (VEA) compensation requires a pole (at the origin, via capacitor  $C_{V1}$ ), and a mid-frequency zero that boosts phase at the 0 dB gain crossover frequency of the overall voltage-loop to assure adequate phase margin. A high frequency pole is also recommended to reduce gain at frequencies above which active regulation is not intended, and to avoid amplifying switching frequency output ripple voltage.

To set the zero, first select  $R_{V1}$  to set VEA gain such that overall voltage loop gain is 0 dB near  $F_{SW}/8$  by:

$$R_{V1} = \frac{R_{F1} \times R_{CS}}{ESR_{C}} \qquad [\Omega] \quad (eq. 34)$$

Where:

$R_{CS}$ : current sense resistance [ $\Omega$ ]

ESR<sub>C</sub>: Equivalent Series Resistance of the output capacitors

Select  $C_{V1}$  to place the VEA compensation zero half a decade below the 0 dB gain crossover frequency and produce flat VEA gain and boost phase at the crossover frequency by:

$$C_{V1} = \frac{24}{2 \times \pi \times F_{SW} \times R_{V1}} \quad [F] \quad (eq. 35)$$

Select  $C_{V1}$  to place the high frequency pole below the switching frequency to reduce the impact of switching noise on the regulation loop by:

$$C_{V2} = \frac{C_{V1}}{2 \times \pi \times f_{HFPV} \times R_{V1} \times C_{V1} - 1} \quad [F] \qquad (eq. 36)$$

Where:

f<sub>HFPV</sub>: frequency desired for the VEA high frequency pole

#### **Thermal Considerations**

The power dissipation of the NCV8856A varies with the MOSFETs used, the switching frequency, and  $V_{IN}$ . The average MOSFET gate current typically dominates the control IC power dissipation, which can be estimated as follows:

$$\mathsf{P}_{\mathsf{IC}} = \mathsf{V}_{\mathsf{IN}} \times \mathsf{I}_{\mathsf{Q}} + \mathsf{P}_{\mathsf{TG}} + \mathsf{P}_{\mathsf{BG}} \quad [\mathsf{W}] \qquad (\mathsf{eq. 37})$$

Where:

P<sub>IC</sub>: control IC power dissipation [W]

VIN: Input (battery) voltage

IQ: IC measured supply current (quiescent current) [A]

P<sub>TG</sub>: high-side MOSFET gate driver loss [W]

P<sub>BG</sub>: low-side MOSFET gate driver loss [W[

The high-side switching MOSFET gate driver loss is:

$$\mathsf{P}_{\mathsf{TG}} = \mathsf{Q}_{\mathsf{TG}} \times \mathsf{F}_{\mathsf{SW}} \times \mathsf{V}_{\mathsf{IN}} \tag{eq. 38}$$

Where:

Q<sub>TG</sub>: total high-side MOSFET gate charge at 6 V

The low-side synchronous rectifier MOSFET gate driver loss is:

$$\mathsf{P}_{\mathsf{BG}} = \mathsf{Q}_{\mathsf{BG}} \times \mathsf{F}_{\mathsf{SW}} \times \mathsf{V}_{\mathsf{IN}} \tag{eq. 39}$$

Where:

Q<sub>BG</sub>: total low-side MOSFET gate charge at 6 V

The junction temperature of the controller can then be estimated as follows:

$$T_{J} = T_{A} + P_{IC} \times R_{\theta JA} \qquad (eq. 40)$$

Where:

$T_{J}$  = junction temperature of the IC

$T_A$  = ambient temperature

$R_{\theta JA}$  = junction-to-ambient thermal resistance of the IC package

The package thermal resistance  $(R_{\theta JA})$  can be obtained from the specifications section of this data sheet. It should be noted that the physical layout of the board, the proximity of other heat sources such as MOSFETs and inductors, and the amount of metal connected to the IC impact the temperature of the device. These calculations may be used as a guide, but measurements should always be taken in the actual application.

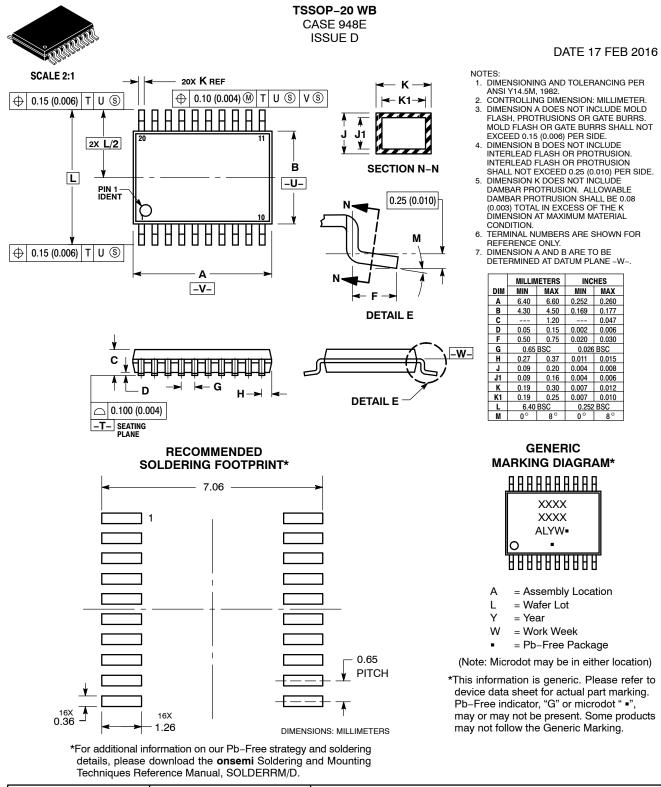

| DOCUMENT NUMBER: | 98ASH70169A | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | TSSOP-20 WB |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

|                  |             |                                                                                                                                                                                     |             |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.