# onsemi

# Series String Pixel Controller for Automotive (Front) Lighting

# NCV78343

# Introduction

The NCV78343 is a single-chip pixel controller with embedded switches to control individual LEDs in a series LED string, designed for automotive dynamic lighting applications and in particular for high current LEDs. In order to create a pixel lighting solution, the LEDs need to be powered by current sources such as NCV78763 or NCV78723. The NCV78343 pixel controller devices receive the pixel control parameters from the pixel light ECU which translates the required light pattern or light image into individual pixel dimming data.

One pixel controller device can control up–to 12 pixels of  $1 \times$  or  $2 \times$  1.4 A LEDs per pixel. The maximum LED string voltage has to be limited to 60 V.

When more than 12 pixels are to be controlled, multiple pixel controllers can be combined in a single system.

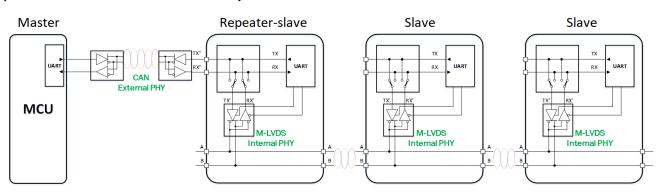

The NCV78343 uses two communication interfaces for connection with a microcontroller. A universal asynchronous receiver transmitter (UART), which supports the use of CAN transceiver and multipoint low voltage differential signaling (M–LVDS) for either local connection or connection with the MCU.

# Features

- Single Chip Compatible with IMS Board (Single Layer)

- 12 Integrated Switches with Multiple Configuration Options

- Minimum of External Components

- Communication Interfaces to the Pixel Light ECU via

- Integrated M–LVDS

- UART over CAN Interface

- Integrated Bridge between M-LVDS and UART

- Supports up to 32 Devices, 1Mbaud

- No Need for Local MCU and Precise Clock

- Interface to External I2C EEPROM

- Integrated 8 bit Analog to Digital Converter

- Dimming Controller

- PWM + Phase Shift Unit per Channel

- Over Temp Protection

- Individual Open/Short/OV LED Diagnostic Feedback

- Open LED Failure Automatic Bypass

- This is a Pb–Free Device

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

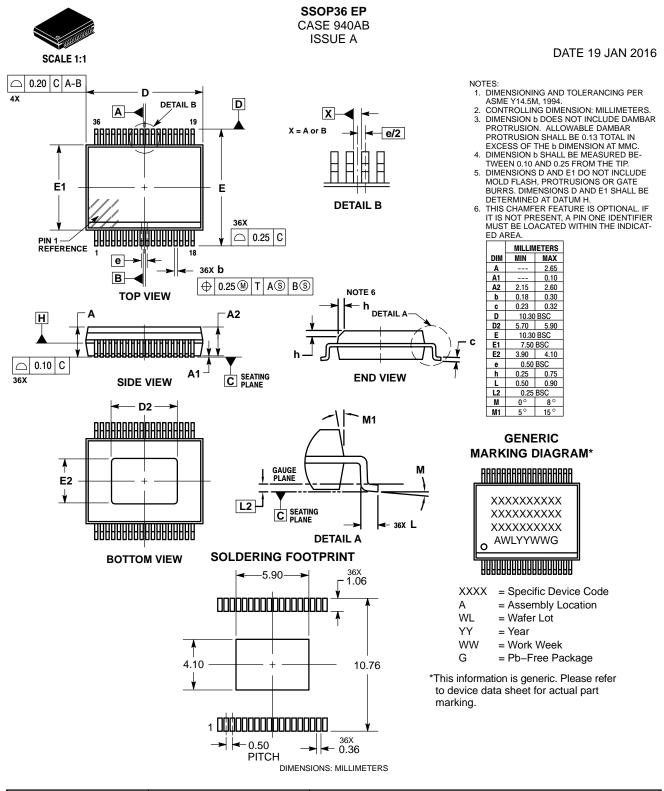

CASE 940AB

MARKING

DIAGRAM

# SAFETY DESIGN - ASIL B

ASIL B Product developed in compliance with ISO 26262 for which a complete safety package is available.

#### **ORDERING INFORMATION**

| Device         | Package               | Shipping <sup>†</sup> |

|----------------|-----------------------|-----------------------|

| NCV78343DQ0R2G | SSOP36 EP<br>(P-Free) | 1500 / Tape &<br>Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### **Typical Applications**

- Dynamic Adaptive Driving Beam Functions

- ♦ Glare-free High Beam

- Static Swiveling

- Beam Shaping

- Light Power Adjustment

- Animated Welcome Functions on Signal Lights

- Wiping Blinker

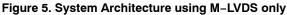

# PACKAGE AND PIN DESCRIPTION

| 1  |      |          | 1  |

|----|------|----------|----|

| 1  | C2P  | TST1     | 36 |

| 2  | C2N  | TST      | 35 |

| 3  | NC   | SW10     | 34 |

| 4  | SW30 | SW11     | 33 |

| 5  | SW31 | SW12     | 32 |

| 6  | SW32 | SW13     | 31 |

| 7  | SW33 | SW20     | 30 |

| 8  | SW40 | SW21     | 29 |

| 9  | SW41 | SW22     | 28 |

| 10 | SW42 | SW23     | 27 |

| 11 | SW43 | NC       | 26 |

| 12 | NC   | ADC0/SDA | 25 |

| 13 | RX   | ADC1/SCL | 24 |

| 14 | тх   | ADC2/ADR | 23 |

| 15 | Α    | VDD      | 22 |

| 16 | В    | GND      | 21 |

| 17 | NC   | Α        | 20 |

| 18 | VBB  | В        | 19 |

|    |      |          | J  |

Figure 1. Pin Connections – SSOP36–EP (Top View)

# Table 1. PIN DESCRIPTION

| Pin No.<br>SSOP36-EP | Pin Name | Description                                                             | І/О Туре    |

|----------------------|----------|-------------------------------------------------------------------------|-------------|

| 1                    | C2P      | Switch control capacitor connection                                     | HV in/out   |

| 2                    | C2N      | Switch control capacitor connection                                     | HV in/out   |

| 3, 12, 17, 26        | NC       | Not used (to be left floating)                                          | NC          |

| 31, 32, 33, 34       | SW1y     | Power switch to short LED                                               | HV in/out   |

| 27, 28, 29, 30       | SW2y     | Power switch to short LED                                               | HV in/out   |

| 4, 5, 6, 7           | SW3y     | Power switch to short LED                                               | HV in/out   |

| 8, 9, 10, 11         | SW4y     | Power switch to short LED                                               | HV in/out   |

| 13                   | RX       | Receive data input (To be tied to GND when not used)                    | HV60 in     |

| 14                   | ТХ       | Transmit data output (To be tied to GND or left floating when not used) | MV out      |

| 15, 20               | A        | M-LVDS IO pins (internally connected; to be shorted to B when not used) | MV in/out   |

| 16, 19               | В        | M-LVDS IO pins (internally connected; to be shorted to A when not used) | MV in/out   |

| 18                   | VBB      | Battery supply                                                          | HV60 supply |

| 21                   | GND      | Ground                                                                  | Ground      |

| 22                   | VDD      | 3V analog and logic supply                                              | LV supply   |

| 23                   | ADC2/ADR | ADC input 2 / Address                                                   | LV in       |

| 24                   | ADC1/SCL | ADC input 1 / I2C clock                                                 | LV in/out   |

| 25                   | ADC0/SDA | ADC input 0 / I2C data                                                  | LV in/out   |

| 35                   | TST      | Internal function. To be tied to GND or left floating                   | HV70 in     |

| 36                   | TST1     | Internal function. To be tied to GND                                    | LV in/out   |

| EP                   | EP       | To be tied to GND                                                       | Exposed Pad |

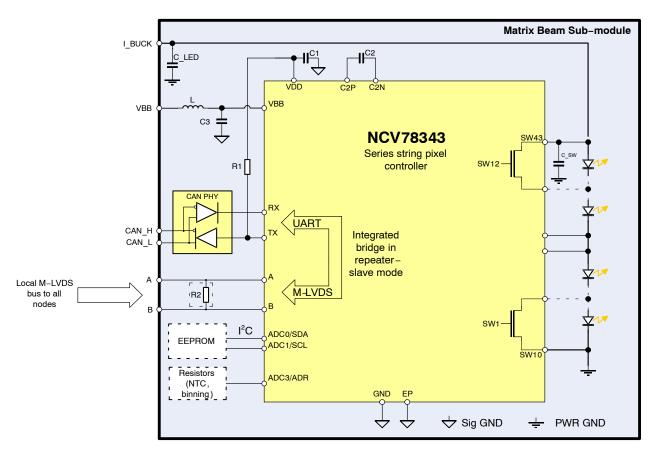

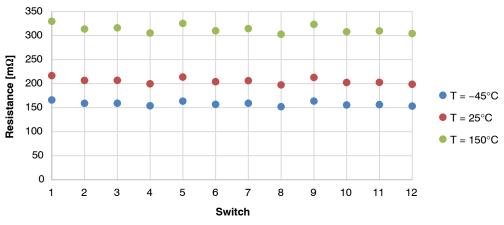

Figure 2. Application Diagram

| Component | Function                                                   | Typ. Value    | Unit |

|-----------|------------------------------------------------------------|---------------|------|

| C1        | Cap. for VDD regulator                                     | 470           | nF   |

| C2        | Cap. for switch control                                    | 220           | nF   |

| C3        | VBB decoupling cap.                                        | 100           | nF   |

| C_SW      | VLED decoupling cap.                                       | 22            | nF   |

| C_LED     | VLED decoupling cap.                                       | 22            | nF   |

| R1        | Tx pull-up resistor                                        | 100           | kΩ   |

| R2        | Terminating resistors (only for the first and last device) | 100           | Ω    |

| CAN       | CAN transceiver                                            | NCV7344       |      |

| M-LVDS    | M–LVDS transceiver                                         | NBA3N206S     |      |

| EEPROM    | External EEPROM                                            | CAT24C02      |      |

| L         | Ferrite bead *                                             | 600 @ 100 MHz | Ω    |

# Table 2. EXTERNAL COMPONENTS

\* It is recommended to place a ferrite bead at VBB net close to a VBB decoupling capacitor for a better electromagnetic immunity.

NOTE: Unused switches to be shorted externally. The switches should be grounded If a full section is not used.

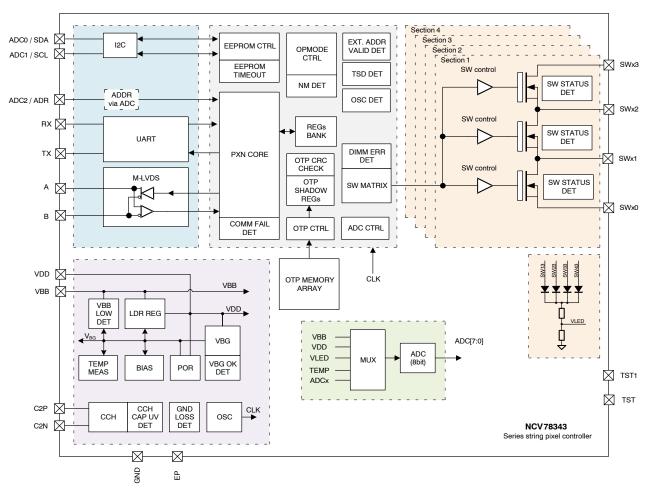

Figure 3. Block Diagram

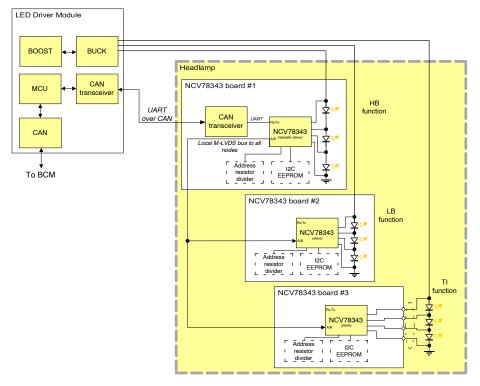

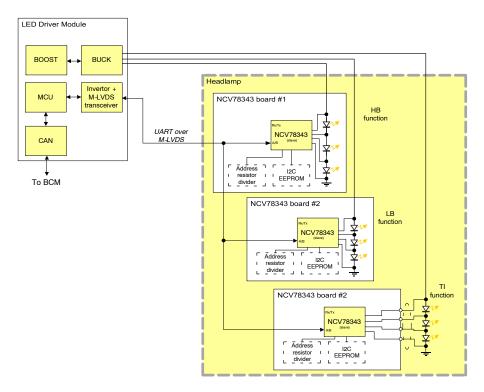

The NCV78343 supports two communication interfaces: UART and M–LVDS. It is possible to communicate over both interfaces, where the first example uses the UART interface over CAN physical layer as a master bus from the LED Driver Module to the first NCV78343 chip and the M-LVDS bus for local connection between submodules of each functional lights such as high beam, low beam, turn indicator, etc. The second example uses the M-LVDS bus only.

Figure 4. System Architecture using CAN-FD and M-LVDS

The advantage of sharing common heatsink for higher currents can be reached by placement of the NCV78343 together with the LEDs on same PCB (IMS type of board supported). This is not necessary for lower currents or application where the LED string is connected over two NCV78343 devices.

Figure 6. ESD Protection Schematic

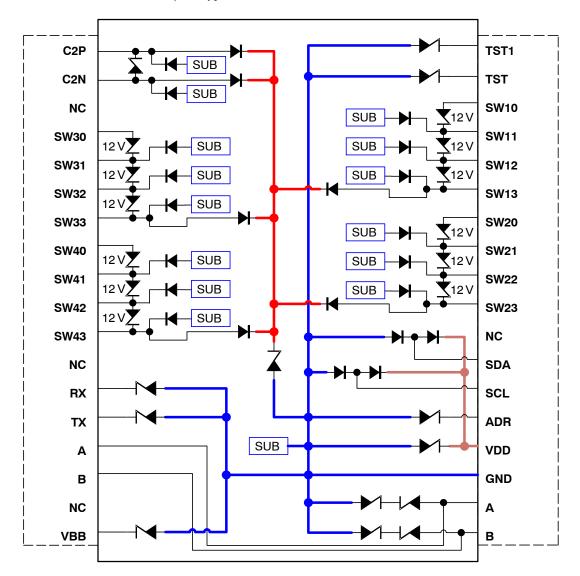

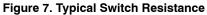

# **Typical Switch Resistance**

# **Typical Switch Section Resistance**

#### Table 3. ABSOLUTE MAXIMUM RATINGS

| Characteristic                                                              | Symbol                 | Min  | Max  | Unit |

|-----------------------------------------------------------------------------|------------------------|------|------|------|

| Battery Supply voltage (Note 1)                                             | V <sub>BB</sub>        | -0.3 | 60   | V    |

| Low voltage supply (Note 2)                                                 | V <sub>DD</sub>        | -0.3 | 3.6  | V    |

| High voltage control IO pins (Note 3)                                       | I <sub>OHV60</sub>     | -0.3 | 60   | V    |

| High voltage IO pins (Note 4)                                               | I <sub>OHV</sub>       | -0.3 | 68   | V    |

| Medium voltage IO pins (Note 5)                                             | I <sub>OMV</sub>       | -0.3 | 6.5  | V    |

| Medium voltage IO pins: M-LVDS (Note 6)                                     | IOMV_MLVDS             | -1.8 | 4    | V    |

| Low voltage IO pins (Note 7)                                                | I <sub>OLV</sub>       | -0.3 | 3.6  | V    |

| Low voltage supply for switch control: $V2 = C2P - C2N$                     | V <sub>2</sub>         | -0.3 | 3.6  | V    |

| Switch differential voltage (Note 8)                                        | V <sub>SWxx_DIFF</sub> | -0.3 | 12   | V    |

| Storage Temperature (Note 9)                                                | T <sub>strg</sub>      | -50  | 150  | °C   |

| Electrostatic discharge on component level Human<br>Body Model (Note 10)    | V <sub>ESD_HBM</sub>   | -2   | +2   | kV   |

| Electrostatic discharge on component level Charge<br>Device Model (Note 10) | V <sub>ESD_CDM</sub>   | -500 | +500 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Absolute maximum rating for pins: VBB

2. Absolute maximum rating for pins: VDD

3. Absolute maximum rating for pins: RX, TST

4. Absolute maximum rating for pins: C2P, C2N, SWxy for x={4+1} & y={3+0}

5. Absolute maximum rating for pins: TX

6. Absolute maximum rating for pins: A, B

7. Absolute maximum rating for pins: TST1, ADC0/SDA, ADC1/SCL, ADC2/ADR

8. Absolute maximum rating for pins: SWx\_(y+1) – SWxy for x={4+1} & y={2+0}

9. For limited time up to 100 hours. Otherwise the max storage temperature is 85°C.

10. This device series incorporates ESD protection and is qualified per AEC-Q100:

ESD Human Body Model Classification level H1C in according to the AEC-Q100-002 Rev-E

ESD Charge Device Model Classification C2b in according to the AEC-Q100-011 Rev-D

Latch – up Current Maximum Rating: ≤100 mA in according to the AEC-Q100-004 Rev-D JEDEC-Class II

Operating ranges define the limits for functional operation and parametric characteristics of the device. A mission profile (Note 11) is a substantial part of the operation conditions; hence the Customer must contact **onsemi** in order to mutually agree in writing on the allowed missions profile(s) in the application.

#### Table 4. RECOMMENDED OPERATING RANGES

| Characteristic                       | Symbol               | Min | Тур | Max  | Unit |

|--------------------------------------|----------------------|-----|-----|------|------|

| Battery supply voltage               | V <sub>BB</sub>      | 4.5 |     | 40   | V    |

| Switch differential voltage          | V <sub>SW_DIFF</sub> | 0   |     | 10   | V    |

| LED string voltage                   | V <sub>STRING</sub>  | 0   |     | 60   | V    |

| Buck switch output current           | I <sub>SW</sub>      |     |     | 1.4  | А    |

| PXN communication speed              | S <sub>PXN</sub>     | 125 |     | 1000 | kbit |

| Ambient temperature                  | T <sub>A</sub>       | -40 |     | 125  | °C   |

| Junction temperature range (Note 12) | TJ                   | -40 |     | 150  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

11. The circuit functionality is not guaranteed outside the Operating junction temperature range. A mission profile describes the application specific conditions such as, but not limited to, the cumulative operating conditions over life time, the system power dissipation, the system's environmental conditions, the thermal design of the customer's system, the modes, in which the device is operated by the customer, etc.

12. The circuit functionality is not guaranteed outside the junction temperature range. Also please note that the device is verified on bench for operation up to 170 °C but the production test guarantees 150 °C only.

#### **Table 5. THERMAL RESISTANCE**

| Characteristic                                       | Package   | Symbol | Min | Тур | Max | Unit |

|------------------------------------------------------|-----------|--------|-----|-----|-----|------|

| Thermal resistance junction to exposed pad (Note 13) | SSOP36-EP | Rthjp  |     | 3.5 |     | °C/W |

13. Includes also typical solder thickness under the Exposed Pad (EP).

# **ELECTRICAL CHARACTERISTICS**

NOTE: All Min and Max parameters are guaranteed over full junction temperature ( $T_{JP}$ ) range (-40 °C; 150 °C), unless otherwise specified.

# Table 6. CURRENT CONSUMPTION

| Characteristic                                  | Symbol               | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------------------|----------------------|--------------------------------------|-----|-----|-----|------|

| The VBB current consumption                     | I_VBB                |                                      |     | 19  | 25  | mA   |

| The VBB current consumption<br>UART only device | I_VBB_M-LVDS_<br>OFF | M-LVDS off; OTP bit M-LVDS_OFF = '1' |     | 6.5 | 10  | mA   |

# Table 7. OSC20M: SYSTEM OSCILLATOR CLOCK

| Characteristic                        | Symbol  | Conditions | Min  | Тур | Max  | Unit |

|---------------------------------------|---------|------------|------|-----|------|------|

| Oscillator output frequency (trimmed) | OSC_CLK |            | 18.2 | 20  | 21.8 | MHz  |

| Oscillator duty cycle                 | OSC_DC  |            | 30   | 50  | 70   | %    |

# Table 8. VDD: 3.45V LOW VOLTAGE ANALOG AND DIGITAL SUPPLY

| Characteristic                         | Symbol       | Conditions  | Min  | Тур  | Max  | Unit |

|----------------------------------------|--------------|-------------|------|------|------|------|

| VDD regulator output voltage           | VDD          | VBB > 4.5 V | 3.15 | 3.45 | 3.6  | V    |

| VDD regulator current limitation       | VDD_ILIM     | VBB > 4.5 V | 40   |      | 300  | mA   |

| OUT_OFF_REG comparator voltage         | V_OUT_OF_REG |             | 2.7  |      | 3.45 | V    |

| VDD POR threshold, VDD rising          | POR3V_H      |             | 2.7  |      | 2.95 | V    |

| VDD POR threshold, VDD falling         | POR3V_L      |             | 2.5  |      | 2.75 | V    |

| VDD POR hysteresis                     | POR3V_HYST   |             | 0.1  | 0.2  | 0.3  | V    |

| VBB POR threshold, VBB rising          | POR_VBB_H    |             | 3.8  |      | 4.3  | V    |

| VBB POR threshold, VBB falling         | POR_VBB_L    |             | 3.7  |      | 4.2  | V    |

| VBB POR hysteresis                     | POR_VBB_HST  |             | 0.05 | 0.1  | 0.25 | V    |

| OTP UV comparator threshold (VBB pin)  | OTP_UV       |             | 12.5 |      | 15   | V    |

| VBB supply during the OTP zapping      | VBB_ZAP      |             | 15   |      | 30   | V    |

| VBB current limitation for OTP zapping | IBAT_ZAPP    |             | 85   |      |      | mA   |

# Table 9. SWITCH CONTROL

| Characteristic                                           | Symbol       | Conditions                         | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------|--------------|------------------------------------|------|------|------|------|

| V(C2) under voltage threshold, V(C2) rising              | CCH _UVH     |                                    | 2.65 | 2.75 | 2.85 | V    |

| V(C2) under voltage threshold, V(C2) falling             | CCH_UVL      |                                    | 2.6  | 2.72 | 2.85 | V    |

| Current from VBB to charge C2 capacitor                  | CCH_IBB      |                                    | 2    |      | 15   | mA   |

| Current limitation from VDD (during start-up)            | CCH_ILIM_RST |                                    | 6    | 12   | 20   | mA   |

| Current limitation from VDD                              | CCH_ILIM     |                                    | 8    | 12   | 16   | mA   |

| Voltage drop between VDD and V(C2)                       | CCH_VDROP    |                                    |      | 120  | 270  | mV   |

| V(C2) voltage after recharge<br>CCH_V2 = VDD – CCH_VDROP | CCH_V2       |                                    |      | 3.33 |      | V    |

| Switch OFF time                                          | SOF_TRISE    | 5 mA, without decoupling capacitor | 1.5  | 1.6  | 2.5  | μs   |

| Switch gate voltage detection threshold                  | SOF_VTH_A    | At ambient temperature             | 0.4  | 0.8  | 1.6  | V    |

| Switch gate voltage detection threshold                  | SOF_VTH_C    | At cold temperature                | 0.9  | 1.3  | 1.7  | V    |

| Switch gate voltage detection threshold                  | SOF_VTH_H    | At hot temperature                 | 0.2  | 0.8  | 1.2  | V    |

| Switch Short detection voltage threshold                 | SSH_VTH      |                                    | 0.35 |      | 1    | V    |

| Switch Overvoltage detection threshold                   | SOV_TH       |                                    | 10   |      | 13.5 | V    |

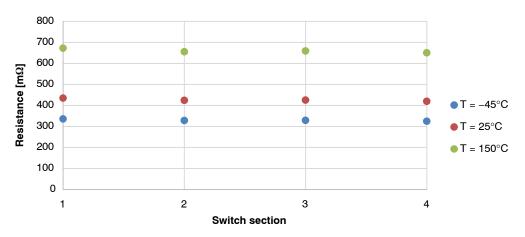

# Table 10. PIXEL SWITCHES

| Characteristic                              | Symbol  | Conditions | Min | Тур  | Max | Unit |

|---------------------------------------------|---------|------------|-----|------|-----|------|

| RON from SWx3 to SWx0 pin (3 switches)      | SW_3R   | At ambient |     | 0.43 | 1.1 | Ω    |

| RON from SWxy to SWx(y-1) pin (1 switch)    | SW_1R   | At ambient |     | 0.2  | 0.6 | Ω    |

| Current from SWxy pin to GND (see Figure 9) | SW_IGND |            | 40  | 53   | 70  | μA   |

# Table 11. ADC FOR MEASURING VBB, VDD, VLED, TEMP, $ADC_X$

| Characteristic                         | Symbol            | Conditions                                | Min   | Тур   | Max   | Unit |

|----------------------------------------|-------------------|-------------------------------------------|-------|-------|-------|------|

| ADC Resolution                         | ADC_RES           |                                           |       | 8     |       | Bits |

| Integral Non-linearity (INL)           | ADC_INL           | ADC_INL Best fitting straight line method |       |       | +1.5  | LSB  |

| Differential Non-linearity (DNL)       | ADC_DNL           | Best fitting straight line method         | -2.0  |       | +2.0  | LSB  |

| Full path gain error                   | ADC_GE            | VBB, VDD measurements                     | -3.25 |       | 3.25  | %    |

| Offset at output of ADC                | ADC_OFFSET        | VBB, VDD measurements                     | -2    |       | 2     | LSB  |

| Time for 1 SAR conversion              | ADC_CONV          |                                           | 6.67  | 8     | 10    | μs   |

| ADC full scale for VBB<br>measurement  | ADC_VBB           |                                           | 33.5  | 35    | 36.5  | V    |

| ADC full scale for VDD<br>measurement  | ADC_VDD           |                                           | 3.87  | 4     | 4.13  | V    |

| ADC full scale for VLED<br>measurement | ADC_VLED          |                                           |       | 66.1  | 68.6  | V    |

| ADC full scale for ADCx<br>measurement | ADC_ADCx          |                                           |       | 1.205 | 1.235 | V    |

| ADCx input current                     | I_ADCx            |                                           | 0.3   | 1     | 1.7   | μA   |

| TSD threshold level                    | ADC_TSD           | ADC measurement of junction temperature   | 163   | 170   | 177   | °C   |

| Accuracy of temperature meas at hot    | ADC_TEMP_ACC_HOT  | T = 155 °C                                | -7    |       | 7     | °C   |

| Accuracy of temperature meas at cold   | ADC_TEMP_ACC_COLD | T = -40 °C                                | -15   |       | 15    | °C   |

# Table 12. GND LOSS DETECTION

| Characteristic                                          | Symbol      | Conditions | Min | Тур | Max  | Unit |

|---------------------------------------------------------|-------------|------------|-----|-----|------|------|

| GND loss comparator threshold; both edges               | GNDLOSS_THR |            | 100 | 120 | 160  | mV   |

| GND loss comparator delay; both falling and rising edge | GNDLOSS_DEL |            |     | 800 | 1200 | ns   |

# Table 13. UART INTERFACE: RX, TX

| Characteristic                | Symbol      | Conditions                     | Min | Тур | Мах                                | Unit |

|-------------------------------|-------------|--------------------------------|-----|-----|------------------------------------|------|

| High-level input voltage      | RX_VIH      |                                | 2   |     |                                    | V    |

| Low-level input voltage       | RX_VIL      |                                |     |     | 0.8                                | V    |

| Input voltage hysteresis      | RX_VIhyst   |                                | 100 | 200 | 400                                | mV   |

| Input pull-down resistance    | RX_RPULL    |                                | 40  |     | 160                                | kΩ   |

| High-level output voltage     | тх_vон      | I <sub>LOAD</sub> = -3mA       | 2.1 |     | VDD or external<br>pull-up voltage | V    |

| Low-level output voltage      | TX_VOL      | I <sub>LOAD</sub> = 3mA        |     |     | 0.4                                | V    |

| TX pin leakage current in HiZ | TX_ILEAK    |                                | -1  |     | 1                                  | μA   |

| TX pin capacitance            | TX_C        |                                |     | 5   |                                    | pF   |

| Propagation delay             | TX_DL_50pF  | C <sub>LOAD</sub> up to 50 pF  |     |     | 40                                 | ns   |

| Propagation delay             | TX_DL_200pF | C <sub>LOAD</sub> up to 200 pF |     |     | 150                                | ns   |

# Table 14. M-LVDS INTERFACE: A, B

| Characteristic                                                                            | Symbol                                          | Conditions                                                                                                                                                                         | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Differential output voltage magnitude                                                     | M-LVDS_TX_VAB                                   | Rload_A-B = 49.9 Ω ±1%<br>Vtest = from -1 V to 3.4 V                                                                                                                               | 480  |     | 650  | mV   |

| Change in Differential output voltage magnitude between logic states                      | M-LVDS_TX_DVAB                                  | Rload_A-B = 49.9 Ω ±1%<br>Vtest = from -1 V to 3.4 V                                                                                                                               | -50  |     | 50   | mV   |

| Steady state common mode output voltage                                                   | M-LVDS_TX_VOS Rload_A-B = 49.9 $\Omega \pm 1\%$ |                                                                                                                                                                                    | 1    | 1.2 | 1.4  | V    |

| Change in Steady state common<br>mode output voltage between logic<br>states              | M-LVDS_TX _DVOS                                 | Rload_A-B = 49.9 $\Omega \pm 1\%$                                                                                                                                                  | -50  |     | 50   | mV   |

| Peak-to-peak common-mode output voltage                                                   | M-LVDS_TX_VOSPP                                 | Rload_A-B = 49.9 Ω ±1%                                                                                                                                                             |      |     | 150  | mV   |

| Maximum steady-state open-circuit<br>output voltage                                       | M-LVDS_TX_VOC                                   | Rload $\geq 1.62 \text{ k}\Omega$                                                                                                                                                  | 1.9  |     | 2.28 | V    |

| Short-circuit output current magnitude                                                    | M-LVDS_TX_IOS                                   | Vtest = from -1 V to 3.4 V                                                                                                                                                         |      |     | 43   | mA   |

| Voltage overshoot, low-to-high level output                                               | M-LVDS_TX_VPH                                   | VSS = 2·VAB                                                                                                                                                                        |      |     | 1.2  | VSS  |

| Voltage overshoot, high-to-low level output                                               | M-LVDS_TX _VPL                                  | VSS = 2·VAB                                                                                                                                                                        | -0.2 |     |      | VSS  |

| Differential Output rise and fall times                                                   | M-LVDS_TX_TE                                    |                                                                                                                                                                                    | 1    | 5   | 12   | ns   |

| Transmitter Propagation delay                                                             | M-LVDS_TX_TP                                    |                                                                                                                                                                                    | 5    | 10  | 20   | ns   |

| Positive-going Differential Input<br>voltage Threshold for BUS common<br>mode <0; 3.8> V  | M-LVDS_RX_VITP                                  |                                                                                                                                                                                    |      |     | 150  | mV   |

| Positive-going Differential Input<br>voltage Threshold for BUS common<br>mode <-1.4; 0> V | M-LVDS_RX_VITP_NCMM                             |                                                                                                                                                                                    |      |     | 160  | mV   |

| Negative-going Differential Input<br>voltage Threshold for BUS common<br>mode <0; 3.8> V  | M-LVDS_RX_VITN                                  |                                                                                                                                                                                    | 50   |     |      | mV   |

| Negative-going Differential Input<br>voltage Threshold for BUS common<br>mode <-1.4; 0> V | M-LVDS_RX<br>_VITN_NCMM                         |                                                                                                                                                                                    | 60   |     |      | mV   |

| Receiver Propagation delay                                                                | M-LVDS_RX_TP                                    |                                                                                                                                                                                    | 20   | 40  | 60   | ns   |

| A or B pin capacitance                                                                    | M-LVDS_C                                        |                                                                                                                                                                                    | Ì    | 5   |      | pF   |

| Transceiver input current in high impedance state (range 1)                               | M-LVDS_IOZ_1                                    | $0 V \le (VA \text{ or } VB) \le 2.4 V,$<br>other output at 1.2 V,<br>transmitter in HiZ                                                                                           | -20  |     | 20   | μA   |

| Transceiver input current in high impedance state (range 2)                               | M-LVDS_IOZ_2                                    | $\begin{array}{l} -1.4 \ V \leq (VA \ or \ VB) \leq 0 \ V \\ or \\ 2.4 \ V \leq (VA \ or \ VB) \leq 3.8 \ V, \\ other \ output \ at \ 1.2V, \\ transmitter \ in \ HiZ \end{array}$ | -32  |     | 32   | μA   |

# Table 15. I2C INTERFACE: SDA, SCL

| Characteristic                                          | Symbol     | Conditions                | Min | Тур     | Max | Unit |

|---------------------------------------------------------|------------|---------------------------|-----|---------|-----|------|

| High-level input voltage                                | I2C_VIH    |                           | 0.7 |         |     | VDD  |

| Low-level input voltage                                 | I2C_VIL    |                           |     |         | 0.3 | VDD  |

| Input voltage hysteresis                                | I2C_VIhyst |                           | 300 |         | 700 | mV   |

| Low-level output voltage                                | I2C_VOL    |                           |     |         | 0.4 | V    |

| High-level output voltage                               | I2C_VOH    | I <sub>LOAD</sub> = -3 mA |     | VDD-0.1 |     | V    |

| SDA or SCL pin capacitance                              | I2C_C      | I <sub>LOAD</sub> = 3 mA  |     | 5       |     | pF   |

| SCL to SDA and SDA to SCL propagation delay, both edges | I2C_DL     |                           | 5   |         | 60  | ns   |

# DETAILED OPERATING AND PIN DESCRIPTION

#### SUPPLY CONCEPT IN GENERAL

Low operating voltages become more and more required due to the growing use of start stop systems. In order to respond to this necessity, the NCV78343 is designed to support power–up starting from VBB = 4.5 V.

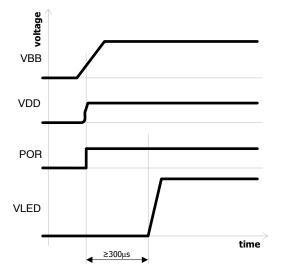

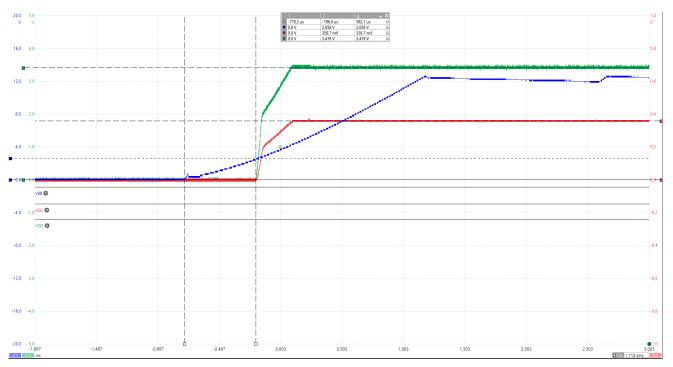

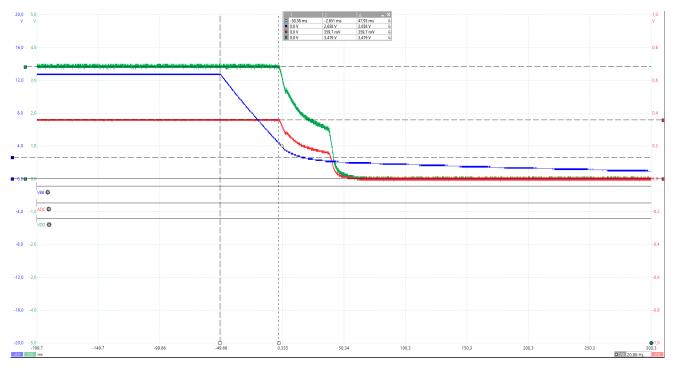

Figure 10. Power-up Sequence

A specific power–up and power–down sequences are shown in the Figure 20 and Figure 21.

There is no special circuit to disable switches in case of VBB power supply disconnection. The gate of the switch is discharged by SW–OFF circuit in case the VBB–LOW threshold is crossed. The gate of the switch is discharged by leakage currents when the supply is suddenly lost. Because of low leakage currents, the switch may stay enabled for a few seconds after power lost. Possible temperature rise speeds up opening the switch by higher leakage current.

#### **VDD Supply**

The VDD supply is the low voltage digital and analog supply for the chip, which is powered from VBB. VDD is supplying the internal analog and digital circuits as well as external components like I2C EEPROM and resistor divider on ADC inputs. The POR–circuit is monitoring both the VBB and VDD voltages.

#### **VLED Supply**

If the device is running but the LED current source is disconnected, the LEDs can light up because of the bias currents flowing through pins of the switches. Up to  $180 \,\mu\text{A}$  (typical) from switch current source may cause the bottom-most LED to shine. If needed, resistors can be connected in parallel to the switches to avoid undesired LED lighting (typically  $10 \,\text{k}\Omega$ ).

#### **INTERNAL CLOCK GENERATION**

The clocks are fully internally generated without the need for any trimming by the user. The accuracy is guaranteed under all operating conditions and independent of external component selection.

#### OSC20M Clock

The OSC20M clock is the system clock. All the internal timings as well as the internal PWM unit depend on OSC20M accuracy.

#### **Communication Clock**

The internal clock is also used for oversampling of UART incoming frame and I2C EEPROM, so there is no need for any external clock.

#### **DIMMING CONTROLLER**

Internal (built-in) dimming controller allows change of light intensity of individual LEDs in LED string by means of digital (PWM) dimming.

#### **Dimming Control Parameters**

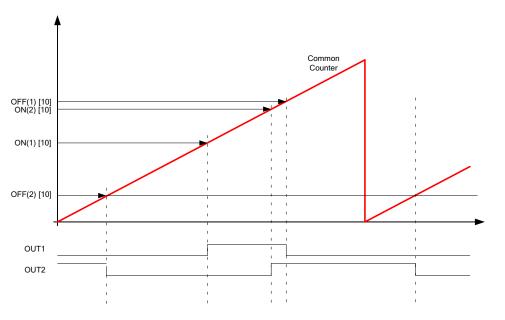

The dimming for all switches is controlled from 1 common 10-bit counter. The ON and OFF events are programmable per channel, each with a 10 bit counter value.

100% duty cycle is generated when ON time is set to min. value (0) and OFF time is set to max value (1023).

0% duty cycle is generated when ON time is equal to OFF time. When more than one 0% or 100% duty cycle is required, the TR (transition) slots must be used.

The dimming frequency is the DIMCLK frequency divided by 1024. The  $T_{DIMCLK}$  is the duration of one PWM tick. The duration of one PWM period is  $T_{PWM}$ . The required time for one switch ON sequence is  $T_{SW\_SEQ}$ . The ratio of  $T_{SW\_SEQ}$  and  $T_{DIMCLK}$  results in number of PWM ticks required for one switch ON sequence. The number of slots available for each DIMCLK is 1024 divided by the ratio. The recommended time for TR slots and recommended step between each switch ON request is shown in Table 43. When the TR slot technique is used, the ON values should not be set within this period.

#### **Dimming Mode**

The NCV78343 incorporates two modes of operation – ON/OFF dimming mode and direct mode.

- **ON/OFF mode** the NCV78343 controls the dimming duty cycle and phase shift for each switch individually. The time of ON event is set by means of <ONx[9:0]> register and the time of OFF event is set by means of <OFFx[9:0]> register.

- **Direct mode** in addition to ON/OFF dimming mode, the state of the switches can be controlled directly by means of <SWx> register.

Figure 11. Dimming Operation (dimming ON/OFF event)

#### **Dimming Transition Vector Insertion**

Transition vectors are required in case of pattern changes (update of dimming settings) for avoiding multiple switching events at the same time and minimizing brightness error.

Fully closed switch (100% duty cycle) requires ON event equal to 0. It can happen that such switch ON event is required on more switches at the same time, which is not allowed. Therefore a transition slot technique is used for consecutive activation of those switches (which need to be changed to 100% duty cycle). When overlapping multiple switch ON events are invoked despite this, the <DIMERR> error is raised. When overlapping switch OFF events occur, the <DIMWARN> status bit is set and processing of this pattern continues. However, multiple switch OFF events may cause large LED string voltage changes.

Transition vector inserts additional transition either ON or OFF event at the beginning of next PWM period (in transition slots space). This helps to reduce brightness error significantly and the duty cycle is affected only in one period. The error is proportionate to duration of transition slot.

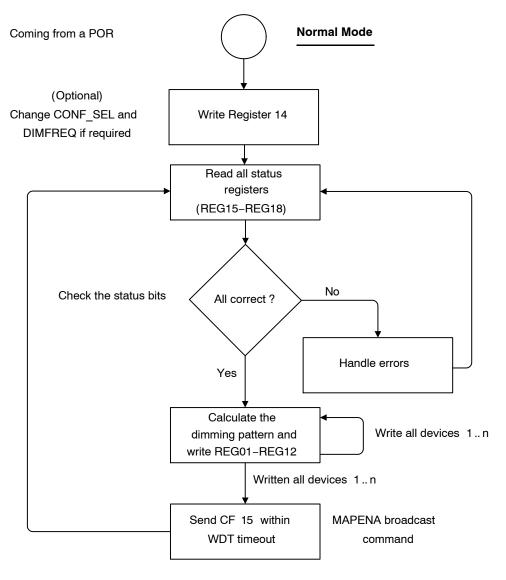

Pattern is updated when common PWM counter overflows and <MAPENA> = '1' (see Table 64) is set.

The NCV78343 contains 12 channels, so with unique settings of  $\langle TRx[3:0] \rangle$  for each switch 12 different Transient Vector values are needed in the worst case ("0x0" to "0xB"). When  $\langle TRx[3:0] \rangle = '0xC'$ , '0xD', '0xE' or '0xF', the  $\langle TRx[3:0] \rangle$  is ignored and transition vectors are not applied. In this case the switch status from previous PWM period is kept unchanged until next ON or OFF event into opposite direction.

#### PWM dimming clock

Selection of internal dimming clock is done by means of <DIMFREQ[4:0]> register, which shall be used to select dimming frequencies in range of 125 kHz to 1 MHz (see Table 43. PWM Frequency Settings).

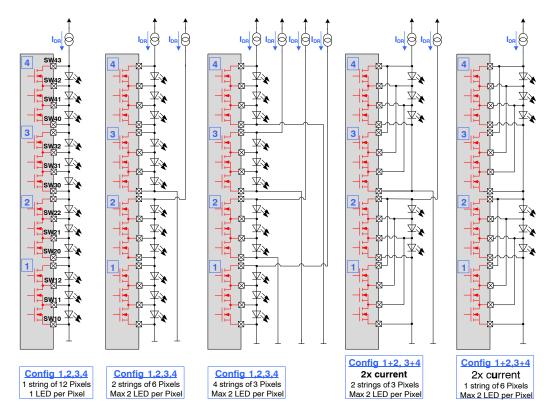

#### SWITCH CONFIGURATIONS

The 12 integrated switches are typically organized as  $12 \times 1$  switch of 1.4 A, but can be organized in  $6 \times 2$  switches in parallel to offer  $6 \times 1$  switch of 2.8 A. Examples of switch configurations are shown in Figure 12.

Selection of the switch configuration is done by <CONF\_SEL[2:0]> register. Detailed information about switch configuration is available in Table 16.

| CONF_SEL<br>[2:0] | Conf.<br>Code<br>Name | Description                             |

|-------------------|-----------------------|-----------------------------------------|

| 000               | 1, 2, 3, 4            | $12 \times PWM$ channels                |

| 001               | 1+2, 3, 4             | $9 \times PWM$ channels (PWM 1=2)       |

| 010               | 1+2, 3+4              | $6 \times PWM$ channels (PWM 1=2 & 3=4) |

| 011               | 1, 2+3, 4             | 9 $\times$ PWM channels (PWM 2=3)       |

| 100               | 1, 2, 3+4             | 9 $\times$ PWM channels (PWM 3=4)       |

| 101               | 1+4, 2+3              | $6 \times PWM$ channels (PWM 1=4 & 2=3) |

| 110               | 1+4, 2, 3             | 9 $\times$ PWM channels (PWM 1=4)       |

| 111               | 1, 2, 3, 4.           | Same as 0000, 12 $\times$ PWM channels  |

Table 16. SWITCH CONFIGURATIONS

In case of configurations with  $2\times$  current, PWM signals of sections with higher index are controlled with PWM signals from lower index section. For example in case of

configuration "101", the PWM signals of section 1 is controlling section 4; control signals of section 2 is controlling section 3.

Figure 12. Example of Switch Configurations

Parallel combination is used where the  $I_{DR}$  current exceeds maximum switch current 1.4 A. This is not for use in redundant applications.

The following consequence must be taken into account when using parallel switches:

The OTP safe–state bits should be zapped to "0" to avoid sequentially switching ON which might cause that the higher current will flow through one switch.

#### **Analog Input**

The analog input AIN is an input channel that can be used for different types of measurements, like e.g. LED temperature or battery voltage. The converted voltage is calculated with the following formula:

$$V_{ADC_x} = ADC\_RES_{X_{[7:0]}} \cdot \frac{1.205}{255} [V]$$

(eq. 1)

where

ADC\_RES<sub>X</sub> is saved in register 0x11

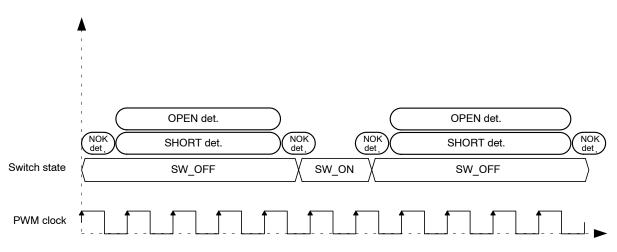

Figure 13. OPEN, SHORT and FAIL Status Detection Timing

Following the figure above, the OPEN and SHORT flags are detected only during the switch OFF state. The On/Off Failed flag detection is triggered by the transition between the switch ON and the switch OFF event. The SHORT and On/Off Failed status flags are cleared upon a successful read out of register 0x0F. Due to this behavior and the diagram above, the read status might alternate between the SHORT and On/Off Failed, following the duty cycle of the specific switch. When the buck current is disabled, the device reports SHORT status for all switches.

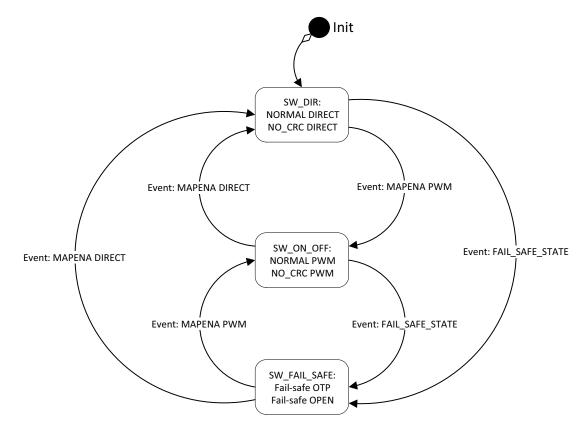

NOTE: MAPENA DIRECT means writing into REG 0x00. MAPENA PWM means either writing into REG 0x0D or sending CF15.

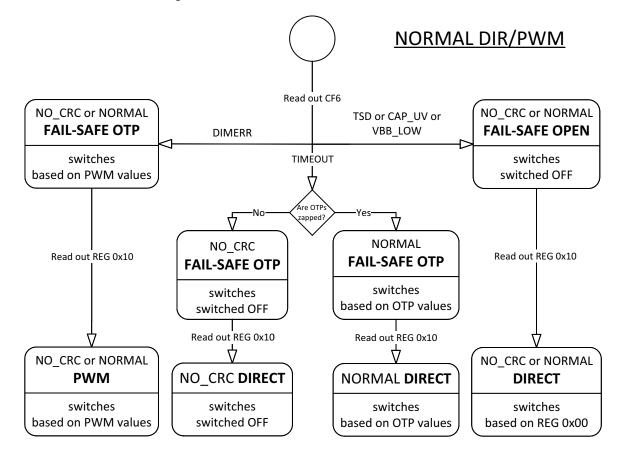

# Figure 14. Normal Mode State Machine

# **Pixel Light Network**

The PXN is a proprietary network technology developed primarily for communication with and within the LED matrix head light system (see Figure 15).

The LED matrix head light system may incorporate a various number of sub-systems interconnected using PXN technology. The connection of such sub-system to a local network is realized using M-LVDS physical interface and a twisted-pair cable. Termination is required at both ends of the twisted-pair cable. Nominally, it is 100  $\Omega$  across the pair. Transmitter on the bus sees both termination resistors in parallel, thus the nominal bus load is actually 50  $\Omega$ .

The LED matrix head light system can be integrated into a superior system through an optional physical interface, e.g. differential low speed CAN. The choice of the external physical interface is application specific.

The PXN protocol for communication over PXN is based on UART communication standard, i.e. one start bit, 8 data bits (LSB first), one stop bit, no parity bit.

Rx pin is 5 V tolerant and has CMOS compatible threshold levels. External pull-up resistor is required on Tx pin.

Figure 15. PXN Topology Inside LED Matrix Head Light System

| UART RX Input Pin | M-LVDS Differential Voltage A-B                                                  | UART TX Output Pin |

|-------------------|----------------------------------------------------------------------------------|--------------------|

| LOW               | POSITIVE (A–B > 150 mV)                                                          | LOW                |

| HIGH              | NEGATIVE<br>(A–B < 50 mV; in M–LVDS push–pull mode;<br>valid for repeater–slave) | HIGH               |

The table above must be taken into account when using only M–LVDS slaves cluster. The master MCU generates UART signal, which is connected to the M–LVDS transceiver, where the A and B pins are connected to the A and B pins on the devices. Since the M–LVDS signal is inverted to the UART signal, there must be placed an invertor on the Tx pin from the MCU to M–LVDS transceiver and another invertor on the Rx pin from the M–LVDS transceiver to the MCU.

#### **PXN Switch**

The PXN switch is responsible for PXN frame routing within a particular PXN node connected to network.

#### **PXN Media Access Layer**

The MAC layer is responsible for a PXN frame composition on a transmitting side, the PXN frame decomposition on a receiving side, a transmission of composed PXN frames, a reception of PXN frames and PXN network error detection and confinement.

#### **PXN Frame**

A message is transferred over PXN bus in a form of PXN frame, which is depicted in Figure 16. The PXN protocol for communication over PXN is based on UART communication standard, i.e. one start bit, 8 data bits (LSB first), one stop bit, no parity bit.

The PXN frame consists of a header and a response. The header is always transmitted by PXN master while the response can either be transmitted by master, in case of write frames or by slave, in case of read frames. The header and the response are separated by in-frame response space.

The header consists of a BREAK field (logic 0 for a certain time), a SYNC field (0x55 byte) and two protected identifiers PID1 and PID2. The response consists of an arbitrary number of DATA bytes within a range from 1 to 12 followed by CRC. The particular bytes are separated by inter-byte space. Minimal delay of 1 Tbit is required before starting new PXN frame. The minimum length for the BREAK field is 13 Tbits (52 µs for the default

communication speed 250 kbps). The BREAK field stop bit (BREAK field delimiter) is minimum 1 Tbit and maximum according to the selected watchdog time. If the device is not responding through the repeater–slave, the extended break (26 Tbits) can be required to recover communication to slave devices. Such case can occur when Read frame is addressed non assigned address. In case of only M–LVDS slave cluster, the DE pin on the M–LVDS transceiver (e.g. NBA3N206S) must be set LOW within 1 Tbit after the Header part to allow device response.

The PXN protocol supports two frame types:

- configuration frame

- register bank frame

#### **PXN Configuration Frame**

The configuration PXN frame allows activation and monitoring of selected configuration service.

#### Table 18. PXN CONFIGURATION FRAME

|      |       | Contents      |          |          |           |          |          |          |          |

|------|-------|---------------|----------|----------|-----------|----------|----------|----------|----------|

| Dute | Name  | Bit<br>7      | Bit<br>6 | Bit<br>5 | Bit<br>4  | Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 |

| Byte | Name  | '             | v        | v        | -         | Ŭ        | -        | •        | v        |

| 0    | PID1  | Р             | 1        | 1        | 1 SA[4:0] |          |          |          |          |

| 1    | PID2  | Р             | 0        | 0        | CSID[4:0] |          |          |          |          |

| 213  | DATAx | DATA[7:0] 011 |          |          |           |          |          |          |          |

| 3    | CRC   |               | CRC[7:0] |          |           |          |          |          |          |

PID1:

| Р        | odd parity bit           |

|----------|--------------------------|

| SA [4:0] | 5-bit slave node address |

PID2:

| Р          | odd parity bit                                   |

|------------|--------------------------------------------------|

| CSID[4:0]  | 5-bit configuration service identifier           |

| DATAx[7:0] | 8-bit data, from 1 up to 12 data bytes supported |

| CRC[7:0]   | 8-bit CRC                                        |

#### PXN Register Bank Frame

The register bank PXN frame provides an access, both read or write to selected register(s) of internal register bank.

| Table 19. | PXN    | REGISTER | BANK | FRAME |

|-----------|--------|----------|------|-------|

|           | 1 ///1 |          |      |       |

|      |       |          |          |          | Cont     | ents     |          |          |          |  |  |

|------|-------|----------|----------|----------|----------|----------|----------|----------|----------|--|--|

| Byte | Name  | Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 |  |  |

| 0    | PID1  | Р        | FT[      | 1:0]     | SA[4:0]  |          |          |          |          |  |  |

| 1    | PID2  | Р        | BC[      | 1:0]     | RBA[4:0] |          |          |          |          |  |  |

| 213  | DATAx |          |          | DA       | ATA[7:   | 0] 0     | 11       |          |          |  |  |

| 3    | CRC   |          |          |          | CRC      | [7:0]    |          |          |          |  |  |

PID1:

P odd parity bit

| FT [1:0]   | 2-bit frame type:<br>"00" – read frame<br>"01" – write frame to address node only<br>"10" – write frame to all nodes (broadcast) |

|------------|----------------------------------------------------------------------------------------------------------------------------------|

| SA [4:0]   | 5-bit slave node address                                                                                                         |

|            |                                                                                                                                  |

| PID2:      |                                                                                                                                  |

| Р          | odd parity bit                                                                                                                   |

| BC[1:0]    | 2-bit byte count                                                                                                                 |

| RBA[4:0]   | 5-bit register bank address                                                                                                      |

| DATAx[7:0] | 8-bit data, from 1 up to 12 data bytes supported                                                                                 |

| CRC[7:0]   | 8-bit CRC                                                                                                                        |

#### PXN Register Bank Frame Matched by Length

The PXN network supports devices with different logical organization of internal register bank. The following logical organizations of register bank are supported:

| TYPE1 | <ul> <li>– up to 32x24 bits</li> </ul> |

|-------|----------------------------------------|

| TYPE2 | <ul> <li>– up to 32x16 bits</li> </ul> |

| TYPE3 | <ul> <li>up to 32x8 bits</li> </ul>    |

Each of types above has predefined number of data bytes for given PID2.BC parameter in case PID1.FT="10" (broadcast frame).

# Table 20. BROADCAST PXN FRAME DATA BYTE COUNT

|              | Data Byte Count |       |       |  |  |  |  |  |  |  |  |  |  |

|--------------|-----------------|-------|-------|--|--|--|--|--|--|--|--|--|--|

| PID2.BC[1:0] | TYPE1           | TYPE2 | TYPE3 |  |  |  |  |  |  |  |  |  |  |

| 0x0          | 3               | 2     | 1     |  |  |  |  |  |  |  |  |  |  |

| 0x1          | 6               | 4     | 5     |  |  |  |  |  |  |  |  |  |  |

| 0x2          | 9               | 8     | 7     |  |  |  |  |  |  |  |  |  |  |

| 0x3          | 12              | 10    | 11    |  |  |  |  |  |  |  |  |  |  |

The NCV78343 supports only the TYPE1 register bank organization, since each register bank consists of 3 bytes.

This means that it is possible to read/write up to 4 registers in one frame, which can be for example used to write ON/OFF times for all 12 switches in only 3 PXN frames.

# **PXN Error Detection**

The PXN network supports detection of these errors:

- frame error

- timeout error

- synchronization error

- local communication error

- global communication error

# **PXN Application Layer**

List of supported configuration services:

# **Table 21. CONFIGURATION SERVICES**

| Configurat<br>Service |      |      | Cor  | nfigura | ation Frame                                |

|-----------------------|------|------|------|---------|--------------------------------------------|

| Name                  | Code | Name | CSID | Туре    | Description                                |

| Identification        | 0    | CF0  | 0x00 | R       | Slave Identification                       |

|                       |      | CF1  | 0x01 | w       | Write data to ext. I2C<br>EEPROM           |

| Ext.<br>EEPROM        | 1    | CF2  | 0x02 | w       | Request data from ext.<br>I2C EEPROM       |

|                       |      | CF3  | 0x03 | R       | Read Data from ext.<br>I2C EEPROM          |

| Auto-addres           |      | CF4  | 0x04 | w       | Enable/disable auto-<br>addressing mode    |

| sing                  | 2    | CF5  | 0x05 | W       | Assign address                             |

|                       |      | CF6  | 0x06 | R       | OP mode status                             |

| PXN mode              | 3    | CF7  | 0x07 | w       | Slave/repeater-slave<br>PXN mode selection |

|                       |      | CF8  | 0x08 | R       | Read PXN mode status                       |

|                       |      | CF9  | 0x09 | W       | Write data to OTP                          |

| OTP                   | 4    | CF10 | 0x0A | w       | Request data from<br>OTP                   |

|                       |      | CF11 | 0x0B | R       | Read data from OTP                         |

| UART                  | 5    | CF12 | 0x0C | w       | Set UART communication speed               |

|                       |      | CF13 | 0x0D | W       | Switch to normal mode                      |

| System                | 6    | CF14 | 0x0E | W       | Reset system                               |

| - Jotom               |      | CF15 | 0x0F | W       | Trigger MAPENA and/<br>or CNTRST           |

List of supported register bank access:

# Table 22. REGISTER BANK ACCESS

| Configurat<br>Service |      |      | Configuration Frame |                     |  |  |  |  |  |  |

|-----------------------|------|------|---------------------|---------------------|--|--|--|--|--|--|

| Name                  | Code | Name | Access Type         | Description         |  |  |  |  |  |  |

| Deed/M/vite           | 0    | WF1  | Read                | Write register bank |  |  |  |  |  |  |

| Read/Write            | 0    | RF1  | Write               | Read register bank  |  |  |  |  |  |  |

# **PXN Communication Modes**

The PXN node can operate in one of the two communication modes:

- slave mode

- repeater-slave mode

Depending on the mode selected, the PXN switch is configured to route the PXN frames the respective way. The repeater–slave device works as a bridge between UART bus and M–LVDS bus. It forwards frames from UART to M–LVDS and back from M–LVDS to UART when reading from a slave device.

# Addressing Options

- It is possible to set a device address in 3 different ways:

- Multi-level address pin

- Auto-addressing procedure

- OTP node address bits

Addressing using OTP memory is recommended for final application. Some of the other device parameters are saved in memory as well, which speeds up device setup after each power–on.

# Multi-level Address Pin

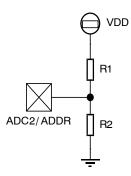

The PXN node address can be determined by connecting ADC2/ADR input to a voltage divider. The voltage divider, represented by resistors R1 and R2 are supplied from regulated 3.3 V VDD supply. The voltage space is divided into 10 ranges where only 8 of them are associated with valid address. The corresponding thresholds are calculated as follows:

| PXN  | Resisto | r Divider | ADC      | 2/VDD    |  |  |  |

|------|---------|-----------|----------|----------|--|--|--|

| Addr | R1 (kΩ) | R2 (kΩ)   | min. (–) | max. (-) |  |  |  |

| 7    | 91      | 27        | 0.75     | 0.79     |  |  |  |

| 6    | 68      | 15        | 0.59     | 0.63     |  |  |  |

| 5    | 91      | 15        | 0.46     | 0.49     |  |  |  |

| 4    | 82      | 10        | 0.35     | 0.38     |  |  |  |

| 3    | 91      | 8.2       | 0.27     | 0.29     |  |  |  |

| 2    | 51      | 3.3       | 0.20     | 0.21     |  |  |  |

| 1    | 82      | 3.6       | 0.14     | 0.15     |  |  |  |

| 0    | 51      | 1.3       | 0.08     | 0.09     |  |  |  |

Table 23. MULTI-LEVEL ADDRESS PIN

In case of valid address the node can process both the addressed and the broadcast frames. In case of invalid address the node can process the broadcast frames only.

# Figure 17. Voltage divided connected to ADC2/ADR Pin

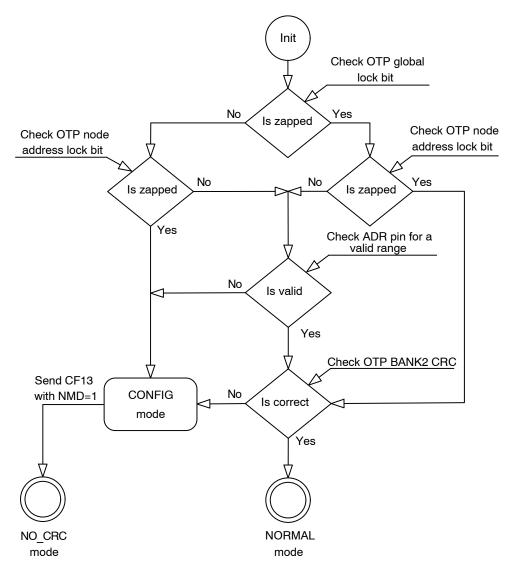

The Multi-level addressing procedure requires stable voltage level at ADC2/ADR pin in 200  $\mu$ s after POR. If the application cannot ensure this time, please follow the

Multi-level addressing procedure with long time delay recommendation in Application notes. If the Multi-level addressing is successful, a device stays in the OTP config mode (see Figure 23).

#### Auto-addressing Procedure

Regardless the node address assigned after the measurement of ADC2/ADR multi-level input, the auto-addressing procedure can still be invoked using the auto-address enable PXN frame. The auto-addressing is enabled/disabled on the PXN node upon receiving CF4 PXN configuration frame. The CF4 frame is accepted in the OTP\_CONFIG mode only (see Table 53).

The PXN node address, when auto-addressing is enabled is assigned upon receiving CF5 PXN configuration frame. The CF5 frame is accepted in AUTO\_ADDR mode only (see Table 54).

The auto-addressing procedure is described in the APPLICATION RELATED INFORMATION section.

# OTP Node Address

The OTP node address can be zapped by customer at EoL (End of Line) after the PXN node address was determined either by means of multi-level address pin measurement or by means of auto-addressing procedure. The value of OTP node address and OTP bank lock bit is obtained each time the PXN node is powered up and the custom OTP bank is read out. Loading of other device settings from OTP memory speeds up device setup after power-on. OTP memory zapping is necessary to fulfil ASIL B safety requirements.

# **PXN Communication Speed**

The PXN node can communicate at following speed:

- -125 kb/s

- 250 kb/s (default)

- 500 kb/s

- -1 Mb/s

Communication speed is changed upon receiving CF12 PXN communication frame in OTP\_CONFIG, AUTO ADDR and NORMAL modes only (see Table 61).

# OTP Bank – Custom Data

The custom OTP bank is typically zapped by customer at EOL and stored values are used for system operation customization.

# Table 24. OTP BANK

| OTP# | OTP Name                  |

|------|---------------------------|

| 0    | OTP lock bit              |

| 1    | OTP node address lock bit |

| 2    | OTP node address bit 0    |

| 3    | OTP node address bit 1    |

| 4    | OTP node address bit 2    |

| 5    | OTP node address bit 3    |

| 6    | OTP node address bit 4    |

| 7    | Fail safe state lock bit  |

| 8  | Fail safe state of LEDs in string 1 |

|----|-------------------------------------|

| 9  | Fail safe state of LEDs in string 2 |

| 10 | Fail safe state of LEDs in string 3 |

| 11 | Fail safe state of LEDs in string 4 |

| 12 | PXN lock bit                        |

| 13 | Mode (slave/repeater-slave)         |

| 14 | Communication speed bit 0           |

| 15 | Communication speed bit 1           |

| 16 | Global bit error detection disable  |

| 17 | M-LVDS OFF                          |

| 18 | UART OFF                            |

| 19 | EEPROM lock bit (write protect)     |

| 20 | CRC bit0                            |

| 21 | CRC bit1                            |

| 22 | CRC bit2                            |

| 23 | CRC bit3                            |

| 24 | CRC bit4                            |

| 25 | CRC bit5                            |

| 26 | CRC bit6                            |

| •  | •                                   |

<<u>OTP\_LOCK\_BIT></u> – custom OTP bank general lock bit. When zapped, any further zapping attempt of custom OTP bank is declined.

<u><OTP\_NODE\_ADDR\_LOCK\_BIT></u> – PXN node address lock bit. When zapped, any further zapping attempt of <OTP\_NODE\_ADDR> bits of custom OTP bank is declined.

<u><OTP\_NODE\_ADDR [4:0]></u> – 5-bit PXN node address. This address is taken into account only when the <OTP\_NODE\_ADDR\_LOCK\_BIT> is zapped.

<FAIL\_SAFE\_STATE\_LOCK\_BIT> – fail safe state of LED string lock bit. When zapped, any further zapping attempt of <FAIL\_SAFE\_STATE\_LED\_STRINGx> bits of custom OTP bank is declined.

<u><FAIL\_SAFE\_STATE\_LED\_STRINGx></u> – state of the LED string x,  $x=\{1,2,3,4\}$ , in case one of the following conditions is detected:

- NORMAL mode is entered or

- Timeout error occurred

The bits set directly the switch state. The fail safe state is taken into account only when

#### <FAIL SAFE STATE LOCK BIT> is zapped.

<u><PXN\_LOCK\_BIT></u> – PXN settings lock bit. When zapped, any further zapping attempt of PXN settings related bits of custom OTP bank is declined.

<u><PXN\_MODE></u> – PXN communication mode selection bit. Set '0' for slave mode and '1' for repeater–slave mode. The mode selection is taken into account only when the <PXN\_LOCK\_BIT> is set and the CRC is correct. <PXN\_COMMUNICATION\_SPEED [1:0]> - 2-bit PXN communication speed selection bit. The communication speed selection is taken into account only when the <PXN\_LOCK\_BIT> is set and the CRC is correct.

| COMMUNICATION_SPEED[1:0]<br>OTP Setting | PXN Communication<br>Speed [kb/s] |

|-----------------------------------------|-----------------------------------|

| 0x0                                     | 125                               |

| 0x1                                     | 250                               |

| 0x2                                     | 500                               |

| 0x3                                     | 1000                              |

#### Table 25. PXN COMMUNICATION SPEED

The default communication speed, when the <PXN LOCK BIT> is not zapped is 250 kbps.

<GLOBAL BIT ERR DTC DIS> – global bit error detection disable. In case the global bit error detection is enabled (<GLOBAL\_BIT\_ERR\_DTC\_DIS> is not zapped) the data transmitted on chip's TX output must be echoed back into chip's RX input. There are two ways to generate the TX echo. Either it can be ensured by a CAN transceiver connected between a chip and an MCU on UART bus or it can be generated by the MCU itself. When the echo is not present, chip stops transmitting and will wait for new incoming frame. When more than one device is present on the UART bus, the repeater-slave will always report <PXN GLOBAL COMM ERR> bit when reading from another device on the UART bus. In case the global bit error detection is disabled, the reading from an address not assigned to a physical device will block the further operation of the repeater-slave device. Such device must be unplugged from a battery voltage in order to make it operational again. The global bit error detection is enabled by default.

The device configured to act as a PXN repeater-slave shall always have the global bit error detection enabled, i.e. <GLOBAL\_BIT\_ERR\_DTC\_DIS> shall be not zapped. The setting of <GLOBAL\_BIT\_ERR\_DTC\_DIS> bit does not affect the communication over M-LVDS bus. The <GLOBAL\_BIT\_ERR\_DTC\_DIS> bit is taken into account only when the <PXN\_LOCK\_BIT> is set and the CRC is correct.

<u><UART\_OFF></u> – UART interface disable. The <UART\_OFF> selection is taken into account only when the <PXN\_LOCK\_BIT> is set and the CRC is correct.

<u><M-LVDS\_OFF></u> - M-LVDS interface disable. The <M-LVDS\_OFF> selection is taken into account only when the <PXN\_LOCK\_BIT> is set and the CRC is correct. Unused M-LVDS transceiver can be disabled to reduce current consumption by 12.5 mA (typical).

<u><EEPROM\_LOCK\_BIT></u> – external EEPROM lock bit. The EEPROM lock bit acts as an EEPROM write protection. When zapped, any further write attempts to external EEPROM is declined.

#### **OTP Memory Zapping**

The OTP zapping process is one-time programming process during which the OTP memory is written. This process cannot be undone. The OTP zapping is possible only in the OTP config mode. To ensure correct OTP zapping, the VBB voltage must be in range of 16 to 30 V with the current capability at least 85 mA during the OTP zapping process. The OTP memory zapping should be done at the EoL to fulfil the ASIL B requirements.

External MCU can read content of OTP memory. To do this, device must first receive CF10 PXN configuration frame followed by CF11 PXN configuration frame. This process is similar to reading from external I2C EEPROM.

# **Operating Modes**

The PXN node can operate in following modes:

- OTP Config mode

- Auto-addressing mode

- Normal Direct mode

- Normal PWM mode

- Normal Fail-safe OTP mode

- Normal Fail-safe OPEN mode

- NO CRC Direct mode

- NO\_CRC PWM mode

- Fail-safe OTP mode

- Fail-safe OPEN mode

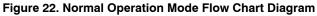

<u>OTP Config mode</u> – the chip enters this mode under the following circumstances: when the OTPs are not zapped and the voltage divider at ADR pin is in a valid range, or the OTPs are zapped but the OTP CRC BANK2 is wrong, or after successful auto-addressing process. Please see the following flow diagram 'Flow chart after POR' in the Application notes.

Chip with non-zapped OTP memory starts with both UART and M-LVDS interfaces enabled. To determine which one will be used, there is a 60 ms timer (typical) that starts once device enters OTP Config mode. After timer elapses, chip reads state of UART RX pin to determine if UART bus should remain enabled (RX pulled high) or disabled (RX pulled low). During this period, M-LVDS devices might be unable to communicate if their UART RX pin is pulled low. Timer can be stopped before elapsing by leaving OTP Config mode, typically by receiving CF13.

<u>Auto-addressing mode</u> – when the chip receives CF4 (see Table 53) configuration frame.

<u>Normal Direct/PWM mode</u> – this is the normal working mode, the chip enters this mode after the POR when the OTPs are zapped and the CRC is correct. Direct means that the switches are controlled directly by writing to the register 0x00. The PWM means that the switches are controlled by the PWM by writing ON and OFF values and sending CF15 (see Table 64).

<u>NO\_CRC Direct/PWM mode</u> – the device enters the NO\_CRC mode after receiving CF13 (see Table 62) in the OTP Config mode. The functionality of NO\_CRC Direct and PWM modes is same as Normal Direct and Normal PWM modes. NO\_CRC prefix means that the device detected invalid CRC in OTP memory bank 2 during power on, most likely because OTP memory is not written.

Please note that only device with written OTP memory achieves ASIL B safety rating.

<u>Fail-safe OTP mode</u> – when this fail-safe state is entered after watchdog timeout, OTP fail-safe data are loaded and applied on switches. Chip also enters this mode after DIMERR. To leave this mode, clear TIMEOUT or DIMERR flags set in register 0x10.

<u>Fail-safe OPEN mode</u> – this is the fail-safe state when the switches are automatically open under the following circumstances: TSD or CAP\_UV or VBB\_LOW appears. To leave this mode, please read out the register 0x10.

#### EEPROM

The external I2C EEPROM can be connected to SDO and SCL pins and supplied from the VDD net.

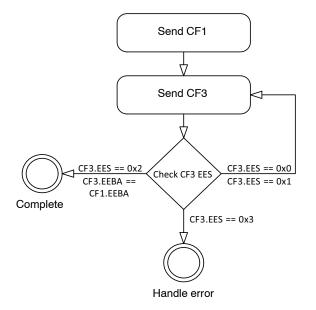

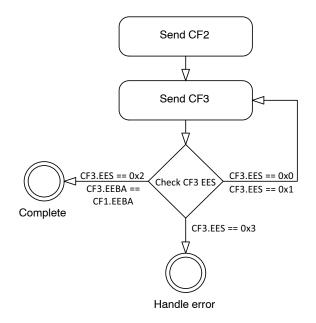

The PXN node writes data to EEPROM upon receiving CF1 PXN configuration frame (see Table 50). The PXN

node reads data from EEPROM upon receiving CF2 PXN configuration frame (see Table 51). The EEPROM data are stored in the internal buffer.

The PXN node provides the data, previously read from the EEPROM and stored in the internal buffer upon receiving CF3 configuration frame (see table 52). The EEPROM address is valid for "1010" + <EESA>.

The write and read operations are shown in the application notes chapter (EEPROM write and read operations).

#### **Cyclic Redundancy Check**

All PXN frames are covered by an 8-bit CRC, where the polynomial is 0x83 (Koopman's notation;  $x^{8}+x^{2}+x^{1}+1$ ) with 0xFF seed. The input bytes are bit swapped and LSB first. The CRC is calculated over PID1, PID2 and DATAx bytes.

The OTP bank 2 is covered by a 7-bit CRC, where the polynomial is 0x5B (Koopman's notation;  $x^7+x^5+x^4+x^2+x^1+1$ ) with 0x7F seed. The input is MSB first. The CRC is calculated over bits 0–19.

The code examples for both CRCs are shown in the APPLICATION RELATED INFORMATION chapter.

# Table 26. PXN REGISTER BANK ADDRESS MAP

|         |        |               |         |               |        |                                    |                                    |              |                     |                           |                               |                                         | BIT        |              |      |             |              |              |              |             |        |              |              |             |              |  |

|---------|--------|---------------|---------|---------------|--------|------------------------------------|------------------------------------|--------------|---------------------|---------------------------|-------------------------------|-----------------------------------------|------------|--------------|------|-------------|--------------|--------------|--------------|-------------|--------|--------------|--------------|-------------|--------------|--|

|         |        | 23            | 22      | 21            | 20     | 19                                 | 18                                 | 17           | 16                  | 15                        | 14                            | 13                                      | 12         | 11           | 10   | 9           | 8            | 7            | 6            | 5           | 4      | 3            | 2            | 1           | 0            |  |

|         |        |               |         |               | BY     | TE2                                |                                    |              |                     |                           |                               |                                         | BYTE1      |              |      |             |              |              |              |             | BY     | TE0          |              |             |              |  |

| Address | Access | 7             | 6       | 5             | 4      | 3                                  | 2                                  | 1            | 0                   | 7                         | 6                             | 5                                       | 4          | 3            | 2    | 1           | 0            | 7            | 6            | 5           | 4      | 3            | 2            | 1           | 0            |  |

| 0x0     | R/W    | SERVIO        | CE=0x0  | -             | -      | -                                  | -                                  | -            | -                   | -                         | -                             | -                                       | -          | SW12         | SW11 | SW10        | SW9          | SW8          | SW7          | SW6         | SW5    | SW4          | SW3          | SW2         | SW1          |  |

|         |        | SERVIO        | CE=0x1  | -             | -      | -                                  | -                                  | -            | -                   | -                         | -                             | -                                       | -          | -            | -    | -           | -            | -            | -            | -           | -      |              | SW_SEL       |             |              |  |

|         |        | SERVIO        | CE=0x2  |               |        |                                    |                                    |              |                     |                           |                               |                                         | R          | ESERVE       | D_1  |             |              |              |              |             |        |              |              |             |              |  |

|         |        | SERVIO        | CE=0x3  |               |        |                                    |                                    |              |                     |                           |                               | -                                       | R          | ESERVE       | D_2  |             |              |              |              |             |        | -            |              |             |              |  |

| 0x1     | R/W    |               |         |               |        | (                                  | DN1                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 1            |              |              |             |        |              | TF           | R1          |              |  |

| 0x2     | R/W    |               |         |               |        | (                                  | DN2                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 2            |              |              |             |        |              | TF           | 32          |              |  |

| 0x3     | R/W    |               |         |               |        | (                                  | DN3                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 3            |              |              |             |        |              | TF           | 33          |              |  |

| 0x4     | R/W    |               |         |               |        | (                                  | DN4                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 4            |              |              |             |        |              | TF           | 34          |              |  |

| 0x5     | R/W    |               |         |               |        | (                                  | DN5                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 5            |              |              |             |        | TR5          |              |             |              |  |

| 0x6     | R/W    |               |         |               |        | (                                  | DN6                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 6            |              |              |             | TR6    |              |              |             |              |  |

| 0x7     | R/W    |               |         |               |        | (                                  | DN7                                |              |                     |                           |                               |                                         | OFF7       |              |      |             |              |              | TR7          |             |        |              |              |             |              |  |

| 0x8     | R/W    |               |         |               |        | (                                  | DN8                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 3            |              |              |             |        | TR8          |              |             |              |  |

| 0x9     | R/W    |               |         |               |        | (                                  | DN9                                |              |                     |                           |                               |                                         |            |              |      | OFF         | 9            |              |              |             | TR9    |              |              |             |              |  |