Thank you for your interest in **onsemi** products.

Your technical document begins on the following pages.

# Your Feedback is Important to Us!

Please take a moment to participate in our short survey. At **onsemi**, we are dedicated to delivering technical content that best meets your needs.

Help Us Improve - Take the Survey

This survey is intended to collect your feedback, capture any issues you may encounter, and to provide improvements you would like to suggest.

# We look forward to your feedback.

To learn more about **onsemi**, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All opreating parameters, including "Typicals" must be validated for each customer application in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and ereasnable attorney fees arising out of, directly or indirectly, any claim of personal injury or death Action Employer. This literature is subject to all applicatione claimed as not for resale in any manner. Other names and brands may be claimed as the property of others.

# onsemi

# Inductive Position Sensor Interface

# NCV77320

#### Introduction

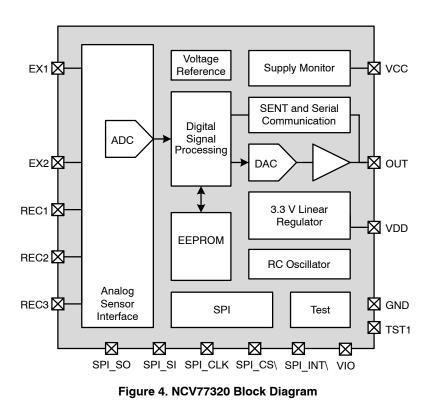

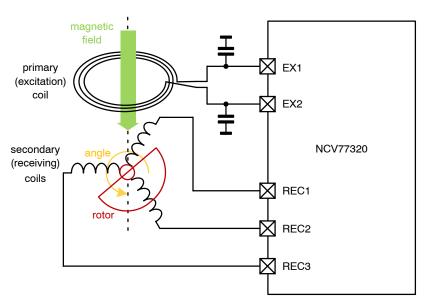

The NCV77320 is a single-chip inductive position sensor interface that, in combination with a *PCB*, forms a system that measures angular or linear positions accurately.

The operating principle of the inductive sensor is based on mutual inductance. The chip contains an excitation source, which generates an AC magnetic field through a primary coil on the PCB. The field mutually couples to the rotor. The rotor on its turn induces voltages in secondary coils. These voltages, measured by the chip, depend on the rotor position and give a measure for the position.

The NCV77320 contains 3 interfaces: A single ended analog output, a SENT interface with fast and slow channel and a SPI channel for direct interconnection to a micro controller.

The analog output is proportionally ratio metric with the supply voltage.

The NCV77320 has several fault detection circuitries. When a fault is detected, fault flags are set and available for readout. In case the analog output is used, OUT pin is put to HiZ and its voltage goes to fail band close to GND or VCC based on the pull–up or pull–down resistor assembled.

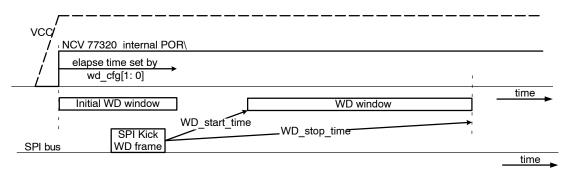

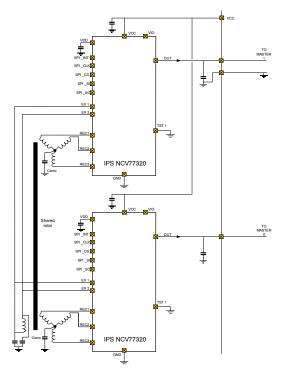

To address automotive functional safety, different kind of topologies can be implemented, e.g.:

- Two devices with independent supplies. There is no galvanic connection between the ICs. Each IC drives its own excitation coil and measures its own set of receiver coils.

- Two devices with their own supply but with a shared excitation coil connected to both ICs.

#### Features

- Integrated DSP Position Calculation with Flexible 15 Point Linearization

- Diagnostics, Including for Missing Wire / Wire Misconnection Tolerant

- Analog Output or SENT Output Configurable

- Temperature Sensor Embedded

- SPI Watchdog Feature

- Supply Voltage 5 V; -15 V to 30 V Tolerant Robustness

- Flexible SPI Operation with 3.3 V or 5 V Micro Controllers

- Maximum Rotational Speed of 10800 rpm

- Operating Ambient Temperature –40 to 150°C

- Developed According to the Automotive Safety Standard ISO26262

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

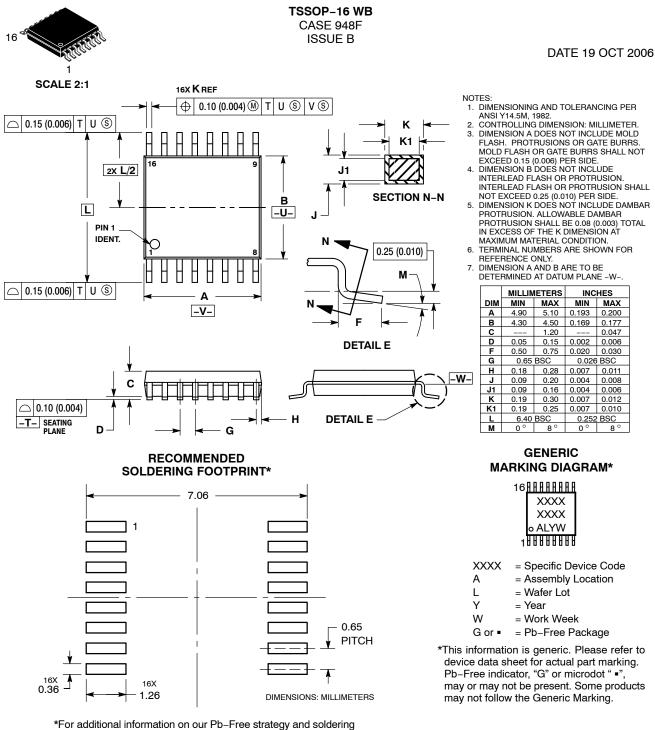

TSSOP-16 CASE 948F-01

#### **ORDERING INFORMATION**

| Device         | Package  | Shipping <sup>†</sup> |

|----------------|----------|-----------------------|

| NCV77320DB0R2G | TSSOP-16 | 4000 / Tape &<br>Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **Typical Applications**

- Angular Position Sensors Up to 360°, e.g. Pedal Position, Throttle Position, Chassis Height, Actuators Position Feedback etc.

- Linear Position Sensors, e.g. Lever Position, Linear Actuator, Level Sensors etc.

## QUICK REFERENCE DATA

Table 1. MAXIMUM RATINGS (Voltages are referred to the device ground GND and are DC level)

| Rating                                                                          | Min  | Max                          | Unit |

|---------------------------------------------------------------------------------|------|------------------------------|------|

| Power Supply VCC                                                                | –15  | 30                           | V    |

| SPI Power Supply VIO                                                            | -0.3 | 6                            | V    |

| Analog Output                                                                   | –15  | 30                           | V    |

| SPI Inputs                                                                      | -0.3 | VIO + 0.3 V, 6 V<br>absolute | V    |

| SPI Output                                                                      | -0.3 | VIO + 0.3 V, 6 V<br>absolute | V    |

| Storage Temperature, T <sub>STG</sub>                                           | -55  | 160                          | °C   |

| Junction Temperature (Note 1)                                                   | -40  | 170                          | °C   |

| Peak Reflow Soldering Temperature: Pb-Free, 60 to 150 Seconds at 217°C (Note 2) | -    | 265 peak                     | °C   |

| HBM Electrostatic Discharge Voltage                                             | -2   | +2                           | kV   |

| CDM Electrostatic Discharge Voltage; Corner Pins                                | -750 | +750                         | V    |

| CDM Electrostatic Discharge Voltage; All Other Pins                             | -500 | +500                         | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. For limited time during the operational lifetime, based on the mission profile.

2. For additional information, see or download **onsemi's** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D, and Application Note <u>AND8003/D</u>.

## **RECOMMENDED OPERATING RANGES**

#### Table 2. RECOMMENDED OPERATING CONDITIONS

| Symbol                      | Parameter                                                             | Min  | Max | Unit |

|-----------------------------|-----------------------------------------------------------------------|------|-----|------|

| VCC                         | Power Supply                                                          | 4.5  | 5.5 | V    |

| VIO                         | SPI Interface Power Supply                                            | 3.0  | 5.5 | V    |

| TST                         | Digital Inputs for Test Mode / to be Tied to GND for Normal Operation | -0.3 | 0.3 | V    |

| SPI_SI, SPI_CS∖,<br>SPI_CLK | SPI Inputs                                                            | -0.3 | 5.5 | V    |

| Т <sub>Ј</sub>              | Junction operating temperature (Note 3)                               | -40  | 170 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3. A mission profile describes the application specific conditions such as, but not limited to, the cumulative operating conditions over lifetime, the system's environmental conditions and the thermal design of the customer's system.

## APPLICATIONS

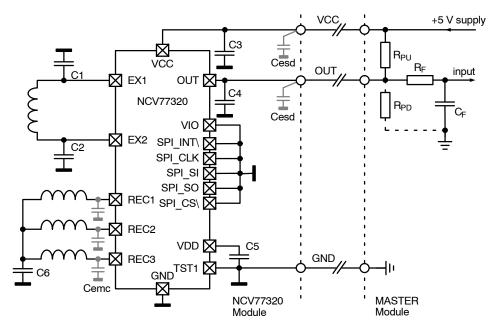

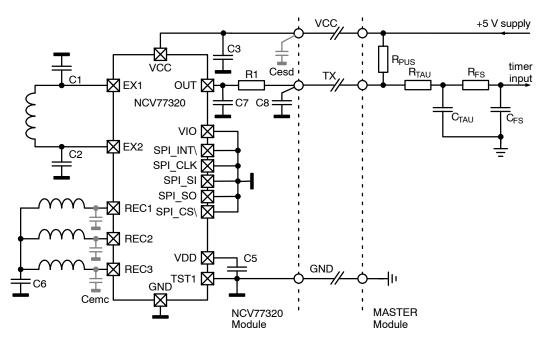

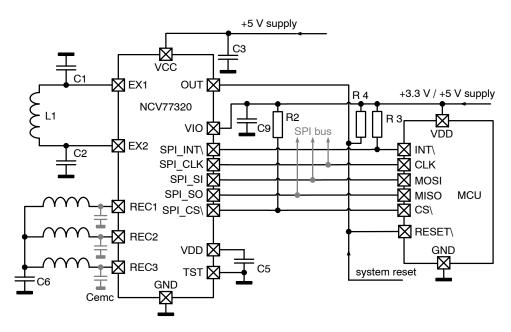

The NCV77320 is an inductive position sensor interface that is suited for applications where a contactless angular or linear position has to be measured with high accuracy. Figure 1 to Figure 3 give simplified application diagrams of the NCV77320 in single chip operation. Table 3 gives the parameters for system level operation.

#### Table 3. SYSTEM PARAMETERS

| Symbol      | Parameter                                                                                 | Conditions                                                   | Min | Тур  | Max  | Unit |

|-------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|------|------|------|

| ICC_A       | Current Consumption with Active Primary Coil Driven. Analog Output Operation without SPI. | VCC = 5.5 V<br>(Note 4)                                      | _   | -    | 11   | mA   |

| ICC_SENT    | Current Consumption with Active Primary Coil Driven. SENT Output Operation without SPI.   | VCC = 5.5 V<br>(Note 4)                                      | -   | -    | 12.5 | mA   |

| ICC_SPI     | Current Consumption with Active Primary Coil Driven. SPI Operation.                       | VCC = 5.5 V, VIO 5.5 V<br>(Note 4)                           | _   | -    | 9.5  | mA   |

| IDD_SPI_VIO | Current Consumption in VIO Pin with Active Primary<br>Coil Driven. SPI Operation Idle.    | VCC = 5.5 V, VIO 5.5 V<br>SPI communication idle<br>(Note 4) | -   | -    | 100  | μΑ   |

| V_MAX       | Angular Speed (Electrical)                                                                |                                                              | -   | -    | 180  | Rps  |

| POS_ACC     | Static Position Linearity Error (Excluding the Sensor)                                    | V_REC > 4 mV<br>(Note 5, 8)                                  | -   | _    | 0.15 | % FS |

| POS_NOISE   | Output Position rms Noise                                                                 | V_REC = 4 mV<br>(Note 6, 7, 8)                               | -   | 0.02 | -    | % FS |

| POS_RES     | Static Position Resolution Expressed as Effective Number of Bits (ENOB)                   | (Note 8)                                                     | -   | 14.5 | -    | Bit  |

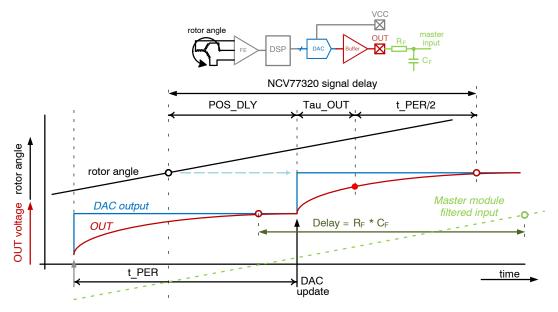

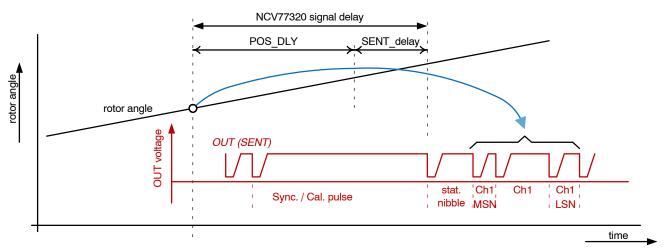

| POS_DLY     | Delay Time between Average Input Position to DSP<br>Output                                |                                                              | -   | 100  | -    | μs   |

| t_PER       | Position DSP Update Rate                                                                  |                                                              | -   | 216  | -    | μs   |

| t_INIT      | Power On Time                                                                             |                                                              | -   | -    | 2    | ms   |

4. Values based on design and characterization, not tested in production

5. Not including error of Analogue driver

6. Analogue driver – OUT rms noise is reduced by factor  $\sqrt{(t_PER / (2 * RF * CF))}$  for RF \* CF > 0.2 ms

7. Noise is inversely proportional to input voltage V\_REC. RMS noise level = POS\_NOISE \* 4 mV / V\_REC

8. PWL correction table set to slope equal to gain = 1

Figure 1. NCV77320 Single Chip Application Diagram with Analog Output

Figure 2. NCV77320 Single Chip Application Diagram with SENT Output

Figure 3. NCV77320 Single Chip Application Diagram with SPI Interface

## Table 4. EXTERNAL COMPONENTS

| Component                         | Description                                                                    | Min. Value               | Typ. Value                                      | Max. Value               | Note                                                                                                                                                  |

|-----------------------------------|--------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1, C2                            | Primary Coil Resonator Capacitor                                               | -                        | Refer to <u>LC</u><br><u>Oscillator</u> chapter | 3.3 nF                   | C0G type ceramic                                                                                                                                      |

| C3                                | Decoupling Capacitors                                                          | -                        | 100 nF                                          | -                        | X7R type ceramic                                                                                                                                      |

| C4                                | Output Stabilization Capacitor for<br>Analogue OUT Configuration               | 80 nF                    | 100 nF                                          | 390 nF                   | X7R type ceramic<br>C4 + Cesd < 390 nF<br>Place the output capacitor C4<br>as close as possible to the OUT<br>pin and returning GND pin.              |

| C5                                | Decoupling and Stabilization Capacitor                                         | 70 nF                    | 100 nF                                          | 100 μF                   | X7R type ceramic                                                                                                                                      |

| C6                                | Common Mode Decoupling Capacitor<br>Recommended for EMC Purposes               | -                        | -                                               | 1 nF                     | X7R, C0G type ceramic                                                                                                                                 |

| C7                                | Output Capacitor for SENT OUT<br>Configuration                                 | -20%                     | 6.8 nF                                          | +20%                     | X7R type ceramic<br>Place the output capacitor C7<br>as close as possible to the OUT<br>pin and returning GND pin.                                    |

| C8                                | $\pi$ Filter Capacitor for SENT OUT Configuration                              | -20%                     | 6.8 nF                                          | +20%                     | X7R type ceramic                                                                                                                                      |

| C9                                | Decoupling Capacitors                                                          | -                        | 100 nF                                          | -                        | X7R type ceramic                                                                                                                                      |

| Cemc                              | 3 x Input Capacitor Optional for<br>Improved EMC Performance                   | -                        | -                                               | 100 pF                   | C0G type ceramic                                                                                                                                      |

| Cesd                              | System Level ESD Optional Protection<br>Capacitor                              | 100 pF                   | -                                               | 100 nF                   | X7R type ceramic<br>C4 + Cesd < 390 nF                                                                                                                |

| C <sub>F</sub>                    | Master Side Filter Capacitor for<br>Analogue OUT Configuration                 | -                        | -                                               | 33 nF                    |                                                                                                                                                       |

| C <sub>TAU</sub>                  | SENT Receiver 1 <sup>st</sup> Stage Capacitor                                  | -30%                     | 2.2 nF                                          | +30%                     | Shall comply with SAE J2716                                                                                                                           |

| $C_{FS}$                          | SENT Receiver 2 <sup>nd</sup> Stage Capacitor                                  | 0.6 μs / R <sub>FS</sub> | Refer to SAE<br>J2716                           | 1.4 μs / R <sub>FS</sub> | Shall comply with SAE J2716                                                                                                                           |

| R1                                | $\pi$ Filter Resistor for SENT OUT Configuration                               | -5%                      | 120 Ω                                           | +5%                      | Power loss ≥ 125 mW                                                                                                                                   |

| R2                                | SPI CS\ Pull-up Resistor                                                       | 68 kΩ                    | -                                               | 220 kΩ                   |                                                                                                                                                       |

| R3                                | INT\ Pull-up Resistor for SPI Operation                                        | 3.3 kΩ                   | 10 kΩ                                           | 22 kΩ                    |                                                                                                                                                       |

| R4                                | RESET\ Pull-up Resistor for SPI<br>Operation                                   | 68 kΩ                    | _                                               | -                        |                                                                                                                                                       |

| R <sub>PU</sub> , R <sub>PD</sub> | Pull-up or Pull-down Resistor at Master<br>Side for Analogue OUT Configuration | 4.7 kΩ                   | -                                               | 22 kΩ                    | R <sub>PD</sub> or R <sub>PU</sub> shall be assembled.<br>Max value can be increased<br>following rules described in<br><u>Analog Output</u> chapter. |

| R <sub>F</sub>                    | Master Side Filter Resistor for Analogue<br>OUT Configuration                  | 10 kΩ                    | -                                               | -                        |                                                                                                                                                       |

| R <sub>PUS</sub>                  | SENT Receiver Pull-up Resistor                                                 | 10 kΩ                    | -                                               | 55 kΩ                    | Shall comply with SAE J2716                                                                                                                           |

| R <sub>TAU</sub>                  | SENT Receiver 1 <sup>st</sup> Filter Stage Resistor                            | -20%                     | 560 Ω                                           | +20%                     | Shall comply with SAE J2716                                                                                                                           |

| R <sub>FS</sub>                   | SENT Receiver 2 <sup>nd</sup> Filter Stage Resistor                            | 4 kΩ                     | _                                               | -                        | Shall comply with SAE J2716                                                                                                                           |

#### **BLOCK DIAGRAM**

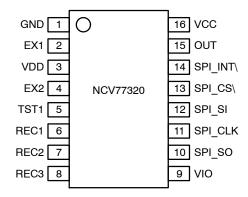

Figure 5. NCV77320 Pinout

| Pin No. | Name | Description                            | Pin No. | Name     | Description                                               |

|---------|------|----------------------------------------|---------|----------|-----------------------------------------------------------|

| 1       | GND  | Sensor ground                          | 16      | VCC      | Sensor Power supply 5 V                                   |

| 2       | EX1  | Primary coil oscillator                | 15      | OUT      | Analog output / SENT output / RST<br>function in SPI mode |

| 3       | VDD  | Digital 3.3 V Supply (only decoupling) | 14      | SPI_INT∖ | SPI Interrupt output (tri-state)                          |

| 4       | EX2  | Primary coil oscillator                | 13      | SPI_CS\  | SPI Chip Select input                                     |

| 5       | TST1 | Test Pin (to be tied to GND)           | 12      | SPI_SI   | SPI Serial input                                          |

| 6       | REC1 | Secondary coil input phase1            | 11      | SPI_CLK  | SPI Clock input                                           |

| 7       | REC2 | Secondary coil input phase2            | 10      | SPI_SO   | SPI Serial output (tri-state)                             |

| 8       | REC3 | Secondary coil input phase3            | 9       | VIO      | SPI supply pin 5 V / 3.3 V                                |

Table 6. OPERATING PARAMETERS (These parameters are guaranteed over temperature and all supplies in the operating range, unless otherwise specified. Convention: currents flowing into the circuit are defined as positive.)

| Parameter                                                                       | (Test) Conditions                                                      | Min   | Тур          | Max  | Unit |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------|-------|--------------|------|------|

| VCC RELATED                                                                     |                                                                        |       |              |      |      |

| VCC                                                                             |                                                                        | 4.5   | 5.0          | 5.5  | V    |

| VCC_OV; VCC over Voltage Threshold Level where the Outputs are going in High Z  |                                                                        | 5.55  | 6.15         | 6.7  | V    |

| t_service_max; Maximum Time after POR wherein the Service Mode Can be Entered   |                                                                        | -     | _            | 100  | ms   |

| VCC_UV; VCC under Voltage Threshold Level where the Outputs are going in High Z |                                                                        | 3.9   | 4.2          | 4.40 | V    |

| t_INIT                                                                          | Power On Initialization Time                                           | -     | -            | 2    | ms   |

| VIO SUPPLY                                                                      |                                                                        |       |              |      |      |

| VIO; SPI Interface Supply Voltage                                               |                                                                        | 3.0   | -            | 5.5  | V    |

| INTERNAL SUPPLY                                                                 |                                                                        |       |              |      |      |

| VDD; Regulated Voltage on Pin VDD                                               | VCC applied, full internal load                                        | 3.1   | 3.3          | 3.6  | V    |

| VDD_OV; Regulated Voltage High Threshold where the OUT goes High Z              |                                                                        | 3.65  | -            | 4.45 | V    |

| VDD_OVLD; VDD Regulator Overload Threshold where OUT goes High Z                |                                                                        | 3.0   | -            | -    | V    |

| POWER ON RESET                                                                  |                                                                        |       |              |      |      |

| POR_hi; POR Threshold Level                                                     | VCC applied                                                            | 2.5   | -            | 3.0  | V    |

| EXCITATION OSCILLATOR                                                           |                                                                        |       |              |      |      |

| V_osc; Primary Oscillator Voltage Amplitude                                     | $V_{osc} = (V(EX1) - V(EX2))$                                          | 1.0   | -            | 1.6  | Vp   |

| V <sub>osc_CMM;</sub> DC Common Mode Voltage                                    |                                                                        | -     | 0.5 x<br>VDD | -    | V    |

| f_PRIM; Primary Resonator Frequency                                             |                                                                        | 3.0   | -            | 4.0  | MHz  |

| RP PRIM; Primary Resonator Effective Loss Resistance                            | @ f_PRIM                                                               | 0.4   | -            | 5    | kΩ   |

| Q_PRIM; Primary Resonator Q-factor                                              | $Q_{PRIM} = \frac{R_{P_PRIM}}{L1} \cdot \frac{1}{2\pi \cdot f_{PRIM}}$ | 4.7   | -            | 170  |      |

| RECEIVER COILS                                                                  |                                                                        |       |              |      |      |

| V_REC; Input Voltage Amplitude Range for Operation                              |                                                                        | 4     | -            | 100  | mV   |

| ANALOG OUTPUT                                                                   |                                                                        |       |              |      | I    |

| Vout_hi; Voltage for Maximum Position Value                                     |                                                                        | -     | -            | 0.95 | VCC  |

| Vout_lo; Voltage for Minimum Position Value                                     |                                                                        | 0.05  | _            | -    | VCC  |

| Vout_offset                                                                     |                                                                        | -16   | _            | 16   | mV   |

| Vout_offset_drift                                                               | (Note 9)                                                               | -5    | _            | 5    | mV   |

| Vout_gainerr                                                                    |                                                                        | -1.3  | _            | 1.3  | %    |

| Vout_gainerr_drift                                                              | (Note 9)                                                               | -0.15 | _            | 0.15 | %    |

| Vout_Diag_Low; Diagnostics Low Level Output                                     |                                                                        | _     | _            | 4    | %VCC |

| Vout_Diag_High; Diagnostics High Level Output                                   |                                                                        | 96    | _            | -    | %VCC |

| Output Linearity Error                                                          |                                                                        | -     | _            | 0.1  | %VCC |

| Analog Output Step Output Settling Time to +/-1%                                | VOUT step from 5 to 95 % VCC,<br>VCC = 5 V, C4 < 390 nF                | _     | -            | 1.2  | ms   |

| TAU_OUT; Analogue Output Time Constant                                          | (Note 9)                                                               | 40    | 110          | 160  | μS   |

| t_DIAG_HOLD; Hold Time for Diagnostic State at OUT Line                         |                                                                        | _     | 50           | -    | ms   |

| Output Current Limitation                                                       |                                                                        | 4     | _            | 8    | mA   |

Table 6. OPERATING PARAMETERS (These parameters are guaranteed over temperature and all supplies in the operating range, unless otherwise specified. Convention: currents flowing into the circuit are defined as positive.) (continued)

| Parameter                                                                 | (Test) Conditions                              | Min          | Тур | Max                | Unit |

|---------------------------------------------------------------------------|------------------------------------------------|--------------|-----|--------------------|------|

| ANALOG OUTPUT                                                             |                                                |              |     |                    |      |

| Output Current Leakage with Deactivated OUT Drivers                       | Tj = 170°C                                     | -7           | -   | 7                  | μA   |

| SENT OUTPUT                                                               |                                                |              |     |                    |      |

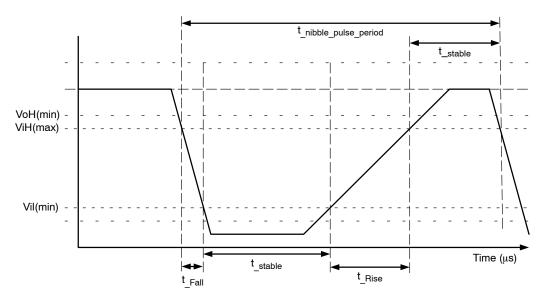

| t_SENT; SENT Clock Tick Time                                              |                                                | -7%          | 3   | +7%                | μs   |

| t_Fall; Fall Time Referred to the Receiver Input                          | From Vth = 3.8 V to Vtl = 1.1 V<br>(Note 10)   | -            | -   | 6.5                | μs   |

| t_Rise; Rise Time Referred to the Receiver Input                          | From Vtl = 1.1 V to Vth = 3.8 V<br>(Note 10)   | -            | -   | 18                 | μs   |

| t_Stable; Signal Time below 1.39 V or above 3.8 V                         | (Note 10)                                      | 6            | -   | -                  | μs   |

| t_ $\Delta$ _Fall; Edge to Edge Jitter                                    | (Note 10)                                      | -            | -   | 0.1                | μs   |

| V_OH; High State Voltage                                                  | (Note 10)                                      | 4.1          | -   | -                  | V    |

| V_OL; Low State Voltage                                                   | (Note 10)                                      | -            | -   | 0.5                | V    |

| I_Output_Max                                                              | Under short circuit condition, average current | -            | -   | 10                 | mA   |

| WATCHDOG RESET OUTPUT                                                     |                                                |              |     |                    |      |

| V_WD_RST; Vol; Open Drain Output Voltage                                  | 68 k pull up to VIO                            | -            | -   | 0.5                | V    |

| T_WD_RST; Watchdog Reset Time                                             |                                                | 18.6         | 20  | 21.4               | ms   |

| SPI DIGITAL INPUTS AND OUTPUTS                                            |                                                |              | •   |                    |      |

| Vih; Input High Level Voltage                                             | VIO = 3.3 V  or  VIO = 5 V                     | 2.3          | -   | VIO                | V    |

| Vil; Input Low Level Voltage                                              |                                                | 0            | -   | 0.8                | V    |

| Voh; SPI_SO Push Pull Driver with 3 State                                 | VIO = 3.3 V or VIO = 5 V,<br>2 mA load current | VIO –<br>0.4 | -   | VIO                | V    |

| Vohd; SPI_INT\ Push Pull Driver with 3 State                              |                                                | VIO –<br>1.3 | _   | VIO                | V    |

| Vol; SPI_SO, SPI_INT\ Push Pull Driver with 3 State                       |                                                | 0            | -   | 0.4                | V    |

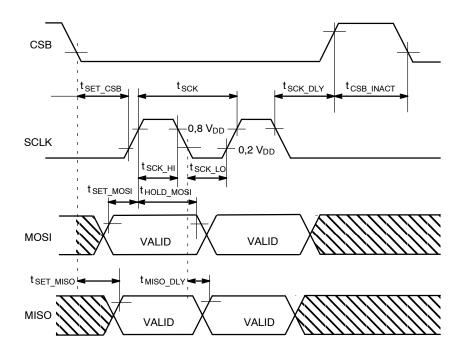

| t <sub>SCK;</sub> SPI Clock Period                                        |                                                | 700          | -   | -                  | ns   |

| t <sub>SCK_HI</sub> ; SPI_CLK High Time                                   |                                                | 200          | -   | -                  | ns   |

| t <sub>SCK_LO</sub> ; SPI_CLK Low Time                                    |                                                | 200          | -   | -                  | ns   |

| t <sub>SET_CSB</sub> ; SPI_CS\ Setup Time                                 |                                                | 400          | -   | -                  | ns   |

| t <sub>CSB_INACT</sub> ; SPI_CS\ Inactive Time                            |                                                | 500          | -   | -                  | ns   |

| t <sub>SET_MOSI;</sub> SPI_SI Setup Time                                  |                                                | 200          | -   | -                  | ns   |

| t <sub>HOLD_MOSI;</sub> SPI_SI Hold Time                                  |                                                | 200          | -   | -                  | ns   |

| t <sub>SET_MISO;</sub> SPI_SO Setup Time                                  | SPI_SO load capacitance: 200 pF                | -            | -   | 200                | ns   |

| t <sub>MISO_DLY</sub> SPI_SO Delay Time                                   | SPI_SO load capacitance: 200 pF                | -            | -   | 200                | ns   |

| $t_{SCK\_DLY;}SPI\_CS\!\!\setminus\!High$ after Last SPI_CLK Falling Edge |                                                | -            | -   | 200                | ns   |

| EEPROM                                                                    |                                                |              |     |                    |      |

| T <sub>PROG</sub> ; EEPROM Programming Time after PRG Command             | N is number of addresses                       | -            | _   | N x 9.9            | ms   |

| T <sub>VERIFY</sub> ; EEPROM Verification Time                            | N is number of addresses                       | -            | -   | N x 0.41<br>+ 14.2 | μS   |

9. Values based on design and characterization, not tested in production

nEEPROMwrite; Number of Write Cycles per Address

10. The NCV77320 is designed to be compliant with requirements of SAE J2716, if the external components fulfill requirements described in Table 4. EXTERNAL COMPONENTS and the supply voltage VCC is in range from 4.85 V to 5.15 V

Tj < 70°C

100

\_

#### Table 7. THERMAL ASPECTS

| Parameter             | Description                                                            | Тур        | Unit |

|-----------------------|------------------------------------------------------------------------|------------|------|

| VCC                   |                                                                        | 5.0        | V    |

| Rthja                 | Thermal resistance from junction to the ambient (Note 11)              | 170        | K/W  |

| Soldering Information | Please refer to our Soldering and Mounting Techniques Reference Manual | SOLDERRM/D |      |

11. The thermal resistance has been obtained by a simulation for the package assembled on 2S0P PCB with 10% copper coverage density with no forced convection at Ta = 180°C.

## **SPI TIMING PARAMETERS**

#### DESCRIPTION

#### **Memory Mapping**

The NCV77320 contains non-volatile EEPROM memory to store the programmed data. It contains two banks of volatile memory – Configuration memory and Run time memory. After POR, the contents of the EEPROM memory is loaded into Configuration memory. It contains calibration, configuration, PWL and programmed sent information. The Run time memory bank contains the real time information: the actual position, the ADC data and diagnostics.

Be aware, that there are different commands for accessing Configuration memory and Run time memory content.

#### LC Oscillator

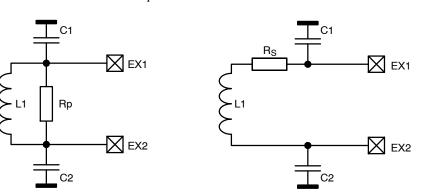

The LC oscillator is the primary excitation generator. The oscillator runs at the LC resonance frequency of around 3.5 MHz. For the maximum Q factor and phase relation, the LC values have to be selected to tune the resonance frequency.

The amplitude of the LC oscillator is kept within a certain window by an amplitude regulation circuit (Refer to the Operating parameter table: " $V_{osc}$ ").

The LC oscillator needs two external capacitors. The selected value needs to be matched to achieve the optimum

resonance frequency for the coil. The capacitors can be calculated as follows:

$$f\_PRIM \approx \frac{1}{2\pi \sqrt{\frac{C1 \cdot C2}{C1 + C2} \cdot L1}}$$

(eq. 1)

Where C1 and C2 are the external capacitors and L1 is the primary coil inductance. The resonant frequency shall conform to the limits given in Table 6.

The  $R_{P\_PRIM}$  represents losses at resonance frequency associated with the resonator. Exceeding the limits given in Table 6 might result in inability of the oscillator to keep the excitation voltage amplitude in the given limits for "V OSC".

In a practical design of the primary coil as PCB structure, the effective losses are often created by inductor series resistance  $R_S$ . In such a case, the following equation can be used:

$$R_{P_{PRIM}} \approx \frac{L1}{R_{S} \cdot \frac{C1 \cdot C2}{C1 + C2}}$$

(eq. 2)

Figure 8. Resonator Schematics Including Losses Equivalent Resistor

Primary coil diagnostics:

- *Primary frequency out of limits*: The oscillator frequency of the primary coil is compared with a frequency of a free running on-chip oscillator. The error flag is set if the "f\_PRIM" frequency is out of range.

- *Primary common mode out of range*: error flag is set if the common mode voltage is outside of the operating range.

- *Primary amplitude too low*: error flag is set when "V OSC" amplitude is too low.

Output states and "fail\_flags[15:0]" register mapping are listed in Table 18.

#### Main Receiver Coils Signal Inputs

The NCV77320 contains three semi differential inputs. The secondary coils of the sensor have to be connected in a star configuration. The mid-point of the star should be connected to the board GND via a decoupling capacitor (<1 nF).

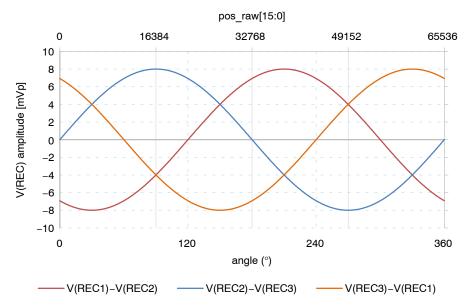

The coils connected should have a 120 phase related geometry to achieve the best full angular resolution of the system. The number of poles at the sensor board and rotor determine the unique electrical period to mechanical angular relationship (ratio is equal to one in Figure 9).

The AC signal at resonant frequency from the primary coil induces voltages in the secondary coils. The amplitude of the induced signal depends on mutual placement of a conductive rotor and the geometry of the input coils. A ratio of the amplitudes at RECx inputs depends on the rotor angular position.

Figure 9. Principle of Inductive Coupling Sensor

#### **Secondary Coil Diagnostics**

- Open of secondary coil is detected during measurement. Failure flag is set when open connection between two RECx pins is detected (including chip leads and bond wires).

- Short of secondary coil structure to supplies (GND, VDD, VCC) or primary coil (EX1, EX2) is detected during measurement. When a short is detected, the error flag is set. Output states and "fail flags[15:0]" register mapping are

listed in Table 18.

#### Analog Sensor Interface & DSP

The analog input signals are filtered and amplified for the AD conversion. The angular position is determined by a ratio of amplitudes of 120° shifted signals at the "f\_PRIM" frequency induced from the primary coil. The angular position and its corresponding value in a DSP register "pos\_raw[15:0]" with respect to signal ratios are shown in Figure 10. The calculated position in "pos\_raw[15:0]" register is updated with period "t\_PER".

Figure 10. RECx Differential Signal Amplitude at f\_PRIM vs. Angular Position

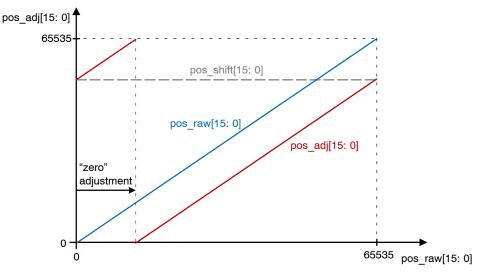

The calculated 16-bit position "pos\_raw[15:0]" can be adjusted to application "zero" position by "pos\_shift[15:0]" EEPROM parameter. This operation can replace a need for mechanical alignment of a rotor with a sensor PCB.

The adjustment is shown in Figure 11 and follows the modulo equation:

pos\_adj[15:0] = mod(pos\_raw[15:0] + pos\_shift[15:0], 65536) (eq. 3)

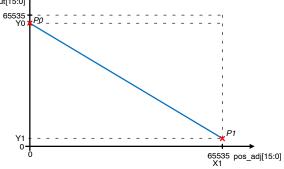

Figure 11. Zero Angle Adjustment Using "pos\_shift[15:0]" Register

#### **Multipoint PWL Correction Table**

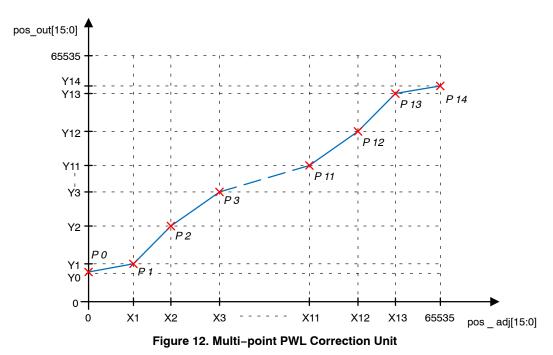

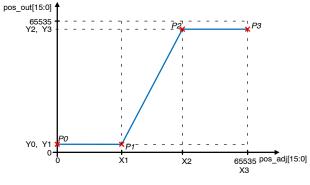

The adjusted position "pos\_adj[15:0]" is processed by an 15-point PWL (piece-wise-linear) correction unit. Up to 15 points " $P_k[X_k, Y_k]$ " are available (k < 0;14>). The points 0 and 14 have x-position bound to the minimum and the maximum of the "pos\_adj[15:0]" range, other points can be set to arbitrary values in ascending order as shown in Figure 12. Correction starts always with point  $P_0$  and continues with next points  $P_1, P_2, \ldots$  until a point which has value  $X_k = 65535$ .

When the analog output interface is used, it should be limited by programming the PWL table  $(Y_k)$  to stay within range of 5% to 95% Vcc, defined by parameters "V<sub>out\_hi</sub>" and "V<sub>out\_lo</sub>" in Table 6. The SENT output should be programmed with the PWL correction table to comply with the SENT specification for the output ranging between 1 and 4088. For the SPI interface, the full output range can be used.

| Point | X Coordinate  | Y Coordinate  |

|-------|---------------|---------------|

| P0    | 0             | pwl_y0[15:0]  |

| P1    | pwl_x1[15:0]  | pwl_y1[15:0]  |

| P2    | pwl_x2[15:0]  | pwl_y2[15:0]  |

| P3    | pwl_x3[15:0]  | pwl_y3[15:0]  |

| P4    | pwl_x4[15:0]  | pwl_y4[15:0]  |

| P5    | pwl_x5[15:0]  | pwl_y5[15:0]  |

| P6    | pwl_x6[15:0]  | pwl_y6[15:0]  |

| P7    | pwl_x7[15:0]  | pwl_y7[15:0]  |

| P8    | pwl_x8[15:0]  | pwl_y8[15:0]  |

| P9    | pwl_x9[15:0]  | pwl_y9[15:0]  |

| P10   | pwl_x10[15:0] | pwl_y10[15:0] |

| P11   | pwl_x11[15:0] | pwl_y11[15:0] |

| P12   | pwl_x12[15:0] | pwl_y12[15:0] |

| P13   | pwl_x13[15:0] | pwl_y13[15:0] |

| P14   | 65535         | pwl_y14[15:0] |

# Table 8. PWL CORRECTION TABLE – POINTS DEFINITION

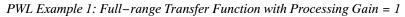

| Table | 9. P | WL | EXA | MPL | E 1 | SET | TINGS |

|-------|------|----|-----|-----|-----|-----|-------|

|       | •••• |    |     |     | _   |     |       |

| Point | Register     | Value |

|-------|--------------|-------|

| P0    | pwl_y0[15:0] | 0     |

| P1    | pwl_x1[15:0] | 65535 |

| P1    | pwl_y1[15:0] | 65535 |

#### Figure 13. Multi-point PWL Correction - Example 1

PWL Example 2: Full-range Input Inverted Transfer Function with 5% to 95% Output Range Scale pos\_out[15:0]

#### Table 10. PWL EXAMPLE 2 SETTINGS

| Point | Register        | Value |

|-------|-----------------|-------|

| P0    | P0 pwl_y0[15:0] |       |

| P1    | pwl_x1[15:0]    | 65535 |

| P1    | pwl_y1[15:0]    | 3277  |

#### Figure 14. Multi-point PWL Correction – Example 2

PWL Example 3: 120 ° Input Range Scaled over 5% to 95% Output

| Table 11 | . PWL | EXAMPL | E 2 SETTINGS |

|----------|-------|--------|--------------|

|----------|-------|--------|--------------|

| Point | Register     | Value |

|-------|--------------|-------|

| P0    | pwl_y0[15:0] | 3277  |

| P1    | pwl_x1[15:0] | 21846 |

| P1    | pwl_y1[15:0] | 3277  |

| P2    | pwl_x2[15:0] | 43691 |

| P2    | pwl_y2[15:0] | 62260 |

| P3    | pwl_x3[15:0] | 65535 |

| P3    | pwl_y3[15:0] | 62260 |

## Figure 15. Multi-point PWL Correction – Example 3

DSP diagnostics

- *"Signal amplitude too low"* is detected when the input signal amplitude drops below "V\_REC" low limit.

- "Direct coupling compensation error" is detected when "dcc\_cXY[7:0]" and "dcc\_pwr[2:0]" coefficients are off range, inconsistent or if the compensation vector is too large. The failure flag is also set in a case of missing rotor.

- *"Internal failure error"* flag is set when a failure is detected on internal circuitry (ADC overload, DSP over-or under-flow, gain error, etc.)

- "*PWL table monotonicity failure*" flag is set if Xi coordinates of used calibration points are not set in ascending order (e.g. X0 < X1 < X2 < ...etc.) and also is set if the last used Xi coordinate is not equal to 65535.

Output states and "fail\_flags[15:0]" register mapping are listed in Table 18.

#### POWER UP AND OPERATING MODES

The NCV77320 is in POR (power-on-reset) when regulated voltage (VDD pin) drops below "POR\_hi" voltage level. The release from POR is additionally conditioned by VCC supply voltage going above "VCC\_UV" threshold. A power-up sequencer is implemented in the NCV77320 to bring the device in different modes. The chip can be in two modes after power up:

- 1. Service mode

- 2. Operating mode

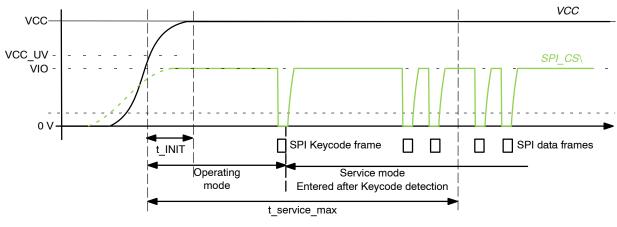

- 1) *Service mode* can be entered after POR within the "t\_service\_max" time window as specified in Table 6. Service mode can be achieved in two ways:

- a. With the serial communication bus operated via the OUT pin:

This interface is suitable for end of line programming for automotive applications, where only 3 output terminals are used to interface the sensor (GND, OUT and VCC). The interface is described in application note AND90288/D, which is available under NDA.

b. Via SPI:

To enter Service mode, the SPI Key-code should be send to the device. After reception of the Key-code, the specific calibration registers can be addressed (Service mode). The SPI Key-code must be received as a first SPI frame and must be received before "t\_service\_max" time elapses. The NCV77320 is ready to decode SPI Key-code after initialization phase "t\_INIT". The SPI Key-code can be received and SPI Service mode can be opened regardless of SPI activation EEPROM bit "spi\_ena". Figure 16 shows the diagram for entering Service mode via SPI.

For normal operation, the device needs to be brought to Operating mode via the "EXIT" SPI command.

2) *Operating mode* is achieved after appliance of the normal VCC operating voltage. After POR, the chip will load the operational EEPROM parameters into the device registers. The content of the registers defines behavior of the chip. When the device is brought into Operating mode from Service mode using the "EXIT" command, the EEPROM parameters are not loaded to the device registers.

Accessibility of the chip and pin function in Operating mode is summarized in Table 12. The OUT driver and/or SPI interface is activated after initialization phase "t\_INIT" elapses.

Figure 16. Service Mode Entry Using SPI

#### Table 12. OPERATING MODE OUTPUT ACCESS CONFIGURATION

|          | EEPROM Parameters            | Out | puts |          |

|----------|------------------------------|-----|------|----------|

| sent_drv | sent_drv spi_ena wd_cfg[1:0] |     |      | OUT Pin  |

| Х        | 1                            | >0  | YES  | RST∖     |

| 0        | 1                            | 0   | YES  | Analogue |

| 1        | 1                            | 0   | YES  | SENT     |

| 0        | 0                            | Х   | NO   | Analogue |

| 1        | 0                            | Х   | NO   | SENT     |

#### Analog Output

The analog driver consists of 16-bit DAC and voltage buffer operating in AB class. The DAC is supplied with the PWL correction unit output "pos\_out[15:0]". The possible voltage range of the Analogue OUT is specified from 5% to 95% VCC.

The output DAC uses the VCC supply voltage as reference. This gives a ratio-metric behavior of the output. For "pos\_out[15:0]", the OUT voltage follows equation:

$$V(OUT) = V(VCC) \cdot \frac{pos_out[15:0]}{65536}$$

(eq. 4)

The NCV77320 signal delay in the Analog OUT configuration is equal to Tau\_OUT + t\_PER / 2 + POS\_DLY. Additionally, filter delay at master module input formed by  $R_F$ ,  $C_F$  has to be taken into account.

Figure 17. Signal Propagation Using Analog OUT Configuration

The default output setting of the NCV77320 is the Analog mode. In this case, the SENT driver stage is in shut down and in high–Z state. When the device is programmed for SENT operation, the analog driver is placed in High–Z state.

#### Diagnostic Bands in Analogue OUT Configuration

In the case of failure detection, the OUT pin is switched off as defined in Table 18.

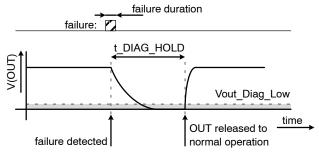

When diagnostic state is entered, minimum duration of the OUT voltage in diagnostic level is "t\_DIAG\_HOLD".

Figure 18. OUT Voltage in Diagnostic State

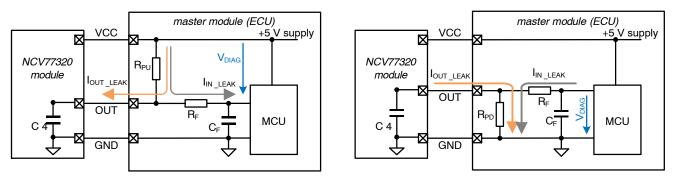

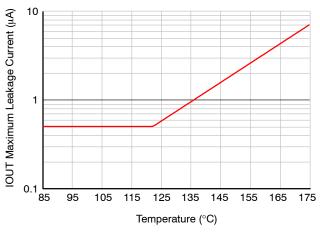

Pull-down  $R_{PD}$  or pull-up  $R_{PU}$  resistors assembled at the Master module are necessary to define the OUT wire potential in the case the OUT driver is switched off or when there is a missing VCC or GND connection. The voltage on the OUT wire measured by the master module (ECU) is defined by external resistors and the leakage currents of connected devices and the potential stray resistances on the wiring harness. NCV77320 OUT leakage current for the off state at specific die temperature  $T_J$  can be derived from the chart in Figure 20. If allowed by the maximum application temperature and by an application specific diagnostic voltage band, maximum specified value of  $R_{PD}$  or  $R_{PU}$  as given in Table 4 can be increased.

With OUT driver in off state, transition to Diagnostic level depends on external components, too. Total capacitance on OUT wire C4 +  $C_F$  together with  $R_{PD}$  or  $R_{PU}$  defines the time constant which should be short enough to allow the OUT voltage to settle within "t\_DIAG\_HOLD" time.

Figure 19. OUT Diagnostic Voltage Level Definition for Switched-off Driver for a) Pull-up, b) Pull-down Resistor

Figure 20. OUT leakage current

#### **SENT Output**

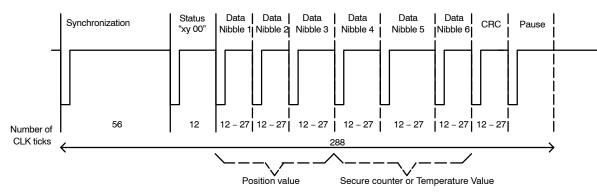

The SENT output complies with the standard SAE J2716 protocol. Refer to the SENT Protocol Standard SAE J2716 published April 2016 for the full description of the protocol. Figure 21 shows the standard SENT frame format.

There are two SENT frame formats implemented in NCV77320:

• H.1 – two 12 bit fast channels: position/angle in channel 1, temperature in channel 2

• H.4 – secure sensor with 12 bit fast channel: position/angle in channel 1, 8-bit counter incremented in each frame with rollover from 255 to 0 in channel 2.

Detail composition of the SENT frame is shown in Table 13.

The NCV77320 makes use of the Enhanced serial channel for diagnostic and device information.

Figure 21. Fast Channels SENT Frame Format

#### Table 13. SENT FRAME FORMAT

|                                   | Nibble content                                                                                               |                                                                       |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Pulse / Nibble                    | H.1 SENT Frame Format<br>sent_ch2_cnt = 0                                                                    | H.4 SENT Frame Format<br>sent_ch2_cnt = 1                             |  |  |  |

| Calibration/Synchronization pulse | 56 SENT t                                                                                                    | icks pulse                                                            |  |  |  |

| Status and Communication Nibble   | Bit 1, 0: channel error<br>Bit 3, 2: Serial message                                                          | Bit 0: channel1 data error<br>Bit 1: zero<br>Bit 3, 2: Serial message |  |  |  |

| Fast Channel 1, data nibble 1     | Clamped position/angle pos_out[15:12]                                                                        | Clamped position/angle pos_out[15:12]                                 |  |  |  |

| Fast Channel 1, data nibble 2     | Clamped position/angle pos_out[11:8]                                                                         | Clamped position/angle pos_out[11:8]                                  |  |  |  |

| Fast Channel 1, data nibble 3     | Clamped position/angle pos_out[7:4]                                                                          | Clamped position/angle pos_out[7:4]                                   |  |  |  |

| Fast Channel 2, data nibble 4     | Temperature temp[3:0]                                                                                        | Secure counter bits [7:4]                                             |  |  |  |

| Fast Channel 2, data nibble 5     | Temperature temp[7:4]                                                                                        | Secure counter bits [3:0]                                             |  |  |  |

| Fast Channel 2, data nibble 6     | Temperature temp[11:8]                                                                                       | Bit inversion of data nibble 1                                        |  |  |  |

| CRC/Checksum Nibble               | CRC is calculated according to SAE J2716, section 5.4.2.2 Recommended Imple                                  |                                                                       |  |  |  |

| Pause pulse (optional)            | If enabled by sent_pause_pls = 1, pause pulse follows CRC nibble to adjust SENT frame length to<br>4 * t_PER |                                                                       |  |  |  |

#### Calibration / Synchronization Pulse

Pulse length is derived from time elapsed between two falling edges. Calibration / Synchronization pulse is 56 SENT tick period long. Nominal tick pulse length is set to "t\_SENT" (3  $\mu$ s).

Calibration / Synchronization pulse is used for determination of the frame start and measurement of the tick time. Actual tick time per frame is obtained as calibration pulse length divided by 56.

Following nibbles value is then equal to nibble length / tick time minus 12. The value of the nibble is a 4 bit number in a range <0..15>.

#### **Status and Communication Nibble**

Nibble bit 0: error associated with data of fast channel 1 appeared.

Nibble bit 1: error associated with data of fast channel 2 appeared.

Nibble bits 2 and 3: Serial Data message bits.

#### Data Nibbles (Fast Channels)

Reserved signal ranges are defined by SAE J2716. Position/angle and temperature signal value ranges are limited to codes 1..4088 as shown in Table 14.

#### Table 14. DATA NIBBLE RESERVED VALUES

| Signal             | Value     | Description                                                                                    |

|--------------------|-----------|------------------------------------------------------------------------------------------------|

| Error<br>indicator | 4089 4095 | Codes reserved for error indicators.<br>Only value 4091 (Generic error) is<br>used in NCV77320 |

| Channel<br>data    | 1 4088    | Valid data range                                                                               |

| Initialization     | 0         | Not used in NCV77320. SENT driver is not enabled in t_INIT phase                               |

#### Position / Angle Signal

Position/angle is provided on Fast Channel 1. The SENT nibble encoder is supplied with the PWL correction unit output "pos\_out[15:4]".

The total signal delay in the SENT configuration with pause pulse enabled is equal to (SENT\_delay + POS\_DLY). The delay is taken to the 1st falling edge of the status nibble.

Without pause pulse, additional delay varies between  $0 \ \mu s$  and SENT frame length. SENT\_delay = 71  $\mu s$  at typ. clock.

Figure 22. Signal Delay in the SENT Frame

#### Temperature Signal

Temperature information is provided on Fast Channel 2. Temperature is coded as a 12–bit number according to SAE J2716 E.2.2.1:

- Slope  $S_{TF} = 8 LSB / K$

- Offset T<sub>OFFSET</sub> = 200 K temperature[11:0] = round(S<sub>TF</sub>. (T[K] – T\_OFFSET) / [K]) (eq. 5)

Numerical temperature output range is limited to 1 ... 4088 which corresponds to  $-73.025^{\circ}$ C to  $437.85^{\circ}$ C.

#### **SENT Enhanced Serial Message**

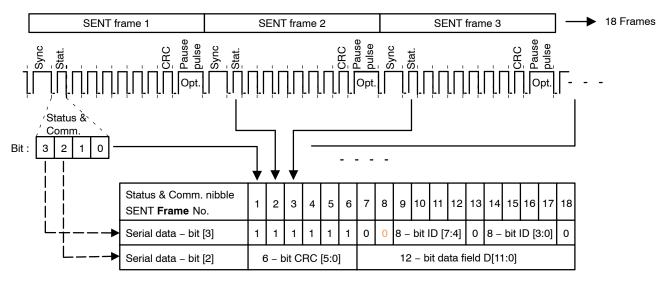

The NCV77320 makes use of the Enhanced serial channel for diagnostic and device information.

The Status bits 2 and 3 of the NCV77320 are used for the Enhanced serial channel operation. The drawing below shows the frame format. In total 18 SENT frames are used to build a full Enhanced serial message.

Bit 3 indicates the start of the Enhanced channel frame data when 6 consecutive "1" bits followed by one "0" is send. The configuration bit as being "0" and the 8 bits ID are following. Bit 2 contains only the CRC and 12 bits data content over the full Enhanced frame.

Figure 23. Enhanced Slow Channels SENT Frame Format

SENT serial communication is free running and not synchronized with any on chip failure. This means that depending on the error detected, the SENT driver is switched off (e.g. short at the output pin). The SENT serial communication does not necessarily start with SENT frame No.1 after the error is released and by that, the Master module always should resynchronize to the next full frame indicated by the start bits.

| Serial Message No. | Message ID                            | Description            | Data Field D[11:0]                       |

|--------------------|---------------------------------------|------------------------|------------------------------------------|

| 1                  | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 2                  | 0x23                                  | Temperature code       | temp[11:0]                               |

| 3                  | sent_idpg1[3:0] * 16 + sent_id11[3:0] | user data              | sent_data_11[11:0]                       |

| 4                  | sent_idpg1[3:0] * 16 + sent_id12[3:0] | user data              | sent_data_12[11:0]                       |

| 5                  | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 6                  | 0x03                                  | SENT sensor type       | sent_sensor_type[11:0]                   |

| 7                  | sent_idpg1[3:0] * 16 + sent_id13[3:0] | user data              | sent_data_13[11:0]                       |

| 8                  | sent_idpg1[3:0] * 16 + sent_id14[3:0] | user data              | sent_data_14[11:0]                       |

| 9                  | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 10                 | 0x05                                  | SENT manufacturer code | sent_manufacturer_code[11:0]             |

| 11                 | sent_idpg2[3:0] * 16 + sent_id21[3:0] | user data              | sent_data_21[11:0]                       |

| 12                 | sent_idpg2[3:0] * 16 + sent_id22[3:0] | user data              | sent_data_22[11:0]                       |

| 13                 | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 14                 | 0x06                                  | SENT protocol revision | sent_protocol_rev[11:0]                  |

| 15                 | sent_idpg2[3:0] * 16 + sent_id23[3:0] | user data              | sent_data_23[11:0]                       |

| 16                 | sent_idpg2[3:0] * 16 + sent_id24[3:0] | user data              | sent_data_24[11:0]                       |

| 17                 | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 18                 | 0x23                                  | Temperature code       | temp[11:0]                               |

| 19                 | sent_idpg3[3:0] * 16 + sent_id31[3:0] | user data              | sent_data_31[11:0]                       |

| 20                 | sent_idpg3[3:0] * 16 + sent_id32[3:0] | user data              | sent_data_32[11:0]                       |

| 21                 | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 22                 | 0x83                                  | EX current code        | D[11:8] = 0x0, D[7:0] = preset_curr[7:0] |

| 23                 | sent_idpg3[3:0] * 16 + sent_id33[3:0] | user data              | sent_data_33[11:0]                       |

| 24                 | sent_idpg3[3:0] * 16 + sent_id34[3:0] | user data              | sent_data_34[11:0]                       |

| 25                 | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 26                 | 0x85                                  | V_REC amplitude        | D[11:0] = vrec_amp[16:5]                 |

| 27                 | sent_idpg4[3:0] * 16 + sent_id41[3:0] | user data              | sent_data_41[11:0]                       |

| 28                 | sent_idpg4[3:0] * 16 + sent_id42[3:0] | user data              | sent_data_42[11:0]                       |

| 29                 | 0x01                                  | Failure flags          | D[11:9] = 0x0, D[8:0] = fail_flags[8:0]  |

| 30                 | 0x87                                  | SENT device ID         | sent_dev_id[11:0]                        |

| 31                 | sent_idpg4[3:0] * 16 + sent_id43[3:0] | user data              | sent_data_43[11:0]                       |

| 32                 | sent_idpg4[3:0] * 16 + sent_id44[3:0] | user data              | sent_data_44[11:0]                       |

#### Table 15. ENHANCED SERIAL MESSAGE SEQUENCE

Refer to the EEPROM data Table 19 and Table 20 for further information on the frame contents.

#### SENT Serial Message CRC

The CRC is computed as a function of the contents of serial data message bits [2] and [3] for status and communication nibbles / SENT frames 7–18 according to SAE J2716, section 5.2.4.3 Enhanced Serial Message Format CRC.

The SENT serial message CRC uses the polynomial X6 + X4 + X3 + X0 with initial seed of 'b010101. The CRC is calculated from serial data bits [2] and [3] starting with Frame 7 ending Frame 18. The order of bits is:

Frame 7 bit #2 (MSB of Data), Frame 7 bit #3 (as being 0), Frame 8 bit #2 (Bit 10 of Data), Frame 8 bit #3 (as being 0),

\_

Frame 18 bit #2 (Bit 0 of Data), Frame 18 bit #3 (as being 0).

\_

#### **SPI INTERFACE**

#### **Physical Interface**

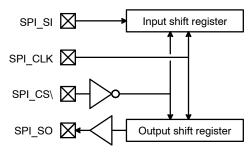

The NCV77320 has an SPI interface that is aside of the Analog output or SENT output operation active.

When the application does not require SPI operation, the "spi\_ena" bit in the EEPROM should be set to "0", the SPI\_CS\, SPI\_SI, SPI\_CLK and SPI\_SO pins should be tied to GND.

The VIO pin should be connected to the supply voltage (3.3 V or 5 V) of the micro controller that is used.

With the SPI interface, the NCV77320 is fully accessible and allows for event driven operation with the SPI INT\pin.

The SPI interface works in 32 bit mode but is compatible with 16 and 8 bit SPI interfaces. The high level block diagram of the SPI slave is shown in the following figure.

Figure 24. SPI High Level Block Diagram

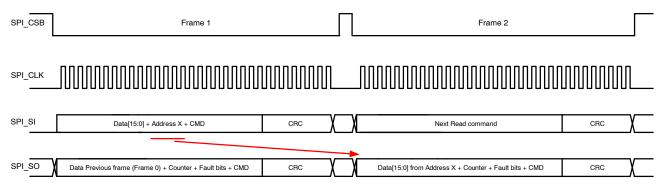

Each frame contains 32 clock cycles that might be composed from 1 x 32 bits, 2 x 16 bits or 4 x 8 bits. When the NCV77320 does not receive 32 bits within one frame or received frame has wrong CRC, the message is discarded and an error bit indicates the "spi\_err" for the next successful SPI cycle. Error bit "pos\_err" is set when "pos\_out[15:0]" does not contain correct position data.

The data transfer is initiated by the SPI\_CS\ going low. The data that is then loaded in the output shift register is defined by the address of the previous valid SPI transfer. The output shift register is clocked out on the rising edge of the SPI\_CLK, the input shift register is clocked at the rising edge as well.

When the SPI\_CS\ is high, any signal at the SPI\_CLK and SPI\_SI pins is ignored and SPI\_SO is forced into a high impedance state.

The NCV77320 has two different frame structures. In Service mode, all registers of the device are accessible. In Operational mode only single word read operations are available.

#### SPI in Operational Mode

During Operational mode, there are 4 commands available. Table 16 shows the commands. Figure 25 shows the frame structure.

| Command                  | CMD<br>[1:0] | ADDRESS<br>[5:0]              | SPI_SO<br>DATA[15:0]    | SPI_SO<br>CNT[3:0] | SPI_SO<br>spi_err | SPI_SO<br>pos_err | SPI_SI<br>DATA[15:0]                                 | Description                                                                                                               |

|--------------------------|--------------|-------------------------------|-------------------------|--------------------|-------------------|-------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Read Run<br>Time<br>Data | 0            | Memory_RT<br>ADDRESS<br>[5:0] | Memory_RT<br>DATA[15:0] | cnt[3:0]           | spi_err           | pos_err           | ignored                                              | read of a register indexed with the run time data address                                                                 |

| Read<br>Memory           | 1            | Memory<br>ADDRESS<br>[5:0]    | Memory<br>DATA[5:0]     | cnt[3:0]           | spi_err           | pos_err           | ignored                                              | read of a register indexed with the address                                                                               |

| Kick<br>Watchdog         | 2            | 0x3F                          | pos_out[15:0]           | cnt[3:0]           | spi_err           | pos_err           | [15:8] =<br>WD_stop_time<br>[7:0] =<br>WD_start_time | write watchdog refresh, update<br>WD window start and stop time<br>in ms; read of the position/angle<br>and failure flags |

| Write<br>Key–code        | 3            | 0x3E                          | pos_out[15:0]           | cnt[3:0]           | spi_err           | pos_err           | ignored                                              | write Key code to enter Service<br>mode; read of the position/angle<br>and failure flags                                  |

Table 16. COMMANDS OF THE SPI OPERATIONAL MODE

Counter cnt[3:0] is freely overflowing counter, which shall be incremented per each correctly received SPI frame.

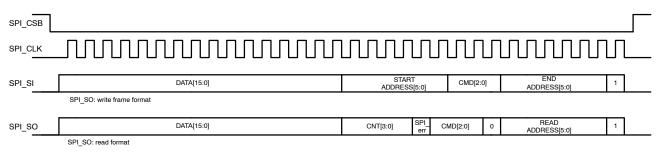

| SPI_CSB |                            |                              |          |          |  |

|---------|----------------------------|------------------------------|----------|----------|--|

| SPI_CLK |                            | uuuu                         | ГЛ       |          |  |

| SPI_SI  | DATA[15:0]                 | REGISTER<br>ADDRESS[5:0]     | CMD[1:0] | CRC[7:0] |  |

|         | SPI_SO: write frame format |                              |          |          |  |

| SPI_SO  | DATA[15:0]                 | CNT[3:0] SPI_POS_<br>err err | CMD[1:0] | CRC[7:0] |  |

|         | SPI_SO: read format        |                              |          |          |  |

#### Figure 25. SPI Frame Structure for Operational Mode Operation

#### Figure 26. SPI Read Structure for Operational Mode Operation

(eq. 6)

SPI CRC 8-bit code (ATM-8) is calculated over the whole data in the frame using polynomial 0x107, seed value is 0xFF.

Polynomial:

$x^8 + x^2 + x^1 + x^0$

#### SPI in Service Mode

Figure 27 shows the command structure for Service mode. Sixteen bits are used for data. Next is a 6 bit start address, which selects an SPI address from where the data should be written or read. The command is given in the third byte, it is 3 bits long. The end address is given by the last 6 bits. While the Service mode is only used for End of line calibration, the messages do not contain a CRC for error detection and correction.

#### Figure 27. SPI Frame Structure for Service Mode Operation

#### Table 17. COMMANDS OF THE SPI SERVICE MODE

| Command  | CMD[2] | CMD[1] | CMD[0] | Description                                                                                                                        |  |

|----------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------|--|

| WRITE    | 0      | 1      | 0      | Write DATA[15:0] to memory bank to START ADDRESS[5:0]; END ADDRESS[5:0] is not used                                                |  |

| READ     | 1      | 0      | 0      | Read DATA[15:0] from memory bank from address START ADDRESS[5:0]; END ADDRESS[5:0] is not used                                     |  |

| PROG     | 1      | 1      | 0      | Program EEPROM address space between START ADDRESS[5:0] and END<br>ADDRESS[5:0] with content from memory bank; DATA[15:0] not used |  |

| RFRH     | 0      | 0      | 0      | Refresh EEPROM address space between START ADDRESS[5:0] and END ADDRESS[5:0] to memory bank; DATA[15:0] not used                   |  |

| VERIFY   | 0      | 0      | 1      | Verify EEPROM content of address space between START ADDRESS[5:0] and END ADDRESS[5:0] with memory bank; DATA[15:0] not used       |  |

| WRITE_RT | 0      | 1      | 1      | Write DATA[15:0] to run time memory bank to START ADDRESS[5:0]; END ADDRESS[5:0] is not used                                       |  |

| READ_RT  | 1      | 0      | 1      | Read DATA[15:0] from run time memory bank from address START ADDRESS[5:0<br>END ADDRESS[5:0] is not used                           |  |

| EXIT     | 1      | 1      | 1      | Exit from Service mode to Operational mode; DATA[15:0], START ADDRESS[5:0] and STOP ADDRESS[5:0] are not used                      |  |

After "PROG" command, the device is busy for " $T_{PROG}$ " time with EEPROM programming. During that period, SPI response has all bits set to 1 and all incoming SPI frames are ignored.

After "VERIFY" command, master device should wait for " $T_{VERIFY}$ " and then "ee\_verify" (bit 15) can be checked by "READ RT" command of address 12.

Tables 19 and 20 show all the accessible registers and the description for the bit and word functions.

#### **SPI Interrupt Output**

The SPI interrupt is used to indicate to the micro controller that a new position/angle is available from the digital sampler or new ADC data is available in case of direct ADC data read out. After reset, the SPI\_INT\ pin is high (Pull-up required to VIO). When a sample scan is finished, the SPI\_INT\ pin goes low. After the SPI read of the position the SPI\_INT\ pin is brought back to a high state again.

#### Position/Angle Data Read Out (direct\_adc = 0)

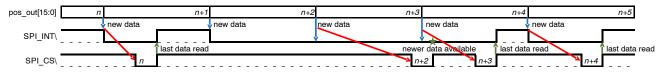

There are two modes of operation determined by the "spi\_int\_edge" parameter:

Level sensitive interrupt (spi\_int\_edge = 0) provides always latest available data via the "pos\_out[15:0]" register. If during the SPI transmission a new position becomes available, the SPI\_INT\ pin will stay low, to indicate that there is new data available again.

Figure 28. SPI Level Sensitive Interrupt spi\_int\_edge = 0

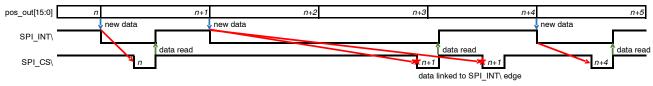

Edge sensitive interrupt (spi\_int\_edge = 1) provides the "pos\_out[15:0]" register data which was present at the SPI\_INT $\$  falling edge moment. If during the SPI

transmission a new position becomes available, the SPI\_INT $\$  pin will return to high level after the SPI transmission and the presence of the new data is not indicated.

Figure 29. SPI Edge Sensitive Interrupt spi\_int\_edge = 1

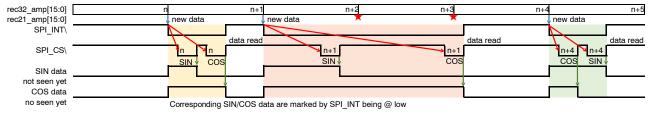

#### Direct ADC Data Read Out (direct\_adc = 1)

Direct ADC mode is implemented for systems, which use the NCV77320 only for input sample acquisition. With this acquired channel information, the master module can calculate the position externally.

As direct ADC mode requires sampling to be bound together and acquired under the same condition (AGC etc), it is recommended that the SPI operation is always using the interrupt. When the direct ADC mode is enabled, ADC data (registers "rec32 amp[15:0]" and "rec21\_amp[15:0]" in runtime memory) are available to be read out and SPI\_INT\ always behaves like Edge sensitive. Very important is that the master device is well aware of correct pairing based on the interrupt signal and that it never will ask for data when the interrupt signal is high. In direct ADC mode, internally calculated position is not correct and therefore register "pos\_out[15:0]" is kept reset to 0.

Figure 30. SPI Edge Sensitive Interrupt Direct\_adc = 1

SPI\_INT\ monitoring:

• SPI\_INT\ error: Is set when logic 0 is detected at SPI\_INT\ while no new position data is available (SPI\_INT\ should be high). Monitoring is active when

SPI is enabled and independently of whether level/edge sensitive interrupt is selected.

Output states and "fail\_flags[15:0]" register mapping are listed in Table 18.

#### Watchdog

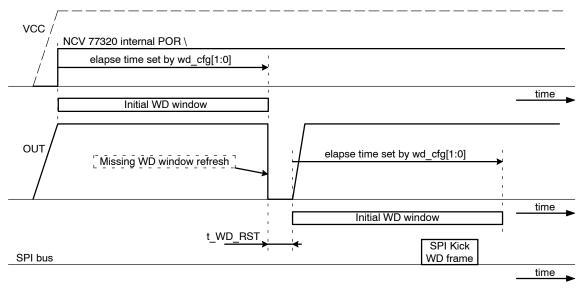

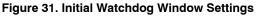

The NCV77320 contains a watchdog that can be operated when SPI mode ("SPI\_ENA" bit) is selected. The Watchdog should be enabled in Service mode by writing a value in the EEPROM bit "WD\_CFG[1:0]" that is >0. When the value is '0', the watchdog is disabled. The value of "WD\_CFG[1:0]" is specifying the initial watchdog comparator value that is used after power on reset. The initial watchdog comparator value is applied also after NCV77320 initiates reset pulse on the OUT pin and after the Service mode is finished by issuing of EXIT command. Watchdog is inactive in Service mode.

When the Watchdog is enabled, repetitive SPI write frames Kick Watchdog (CMD[1:0] = 2) should be received by the NCV77320 to stay in operation. This command resets the watchdog counter and writes the new values WD\_start\_time [ms] for the window start and WD\_stop\_time [ms] for window stop times. The next Kick Watchdog (CMD[1:0] = 2) SPI command should be send within the written window. When the Kick Watchdog SPI command arrives before start of the window (Early refresh) or didn't arrive before the end of the window (Late refresh), the OUT pin is forced low for a duration of "t\_WD\_RST" to reset or interrupt the system micro controller. The OUT pin is also forced low when Watchdog refresh contains invalid start and stop time, meaning start = 0 or start  $\geq$  stop.

Figure 32. Watchdog Window Control

# DIAGNOSTICS

The NCV77320 has several diagnostic circuitries to check for errors in the chip and connected coil structure in– and outputs.

#### Table 18. Diagnostics