## High-Efficiency Single Stage Power Factor Correction and Step-Down Controller

The NCP1652 is a highly integrated controller for implementing power factor correction (PFC) and isolated step down ac-dc power conversion in a single stage, resulting in a lower cost and reduced part count solution. This controller is ideal for notebook adapters, battery chargers and other off-line applications with power requirements between 75 W and 150 W. The single stage is based on the flyback converter and it is designed to operate in continuous conduction (CCM) or discontinuous conduction (DCM) modes.

The NCP1652 increases the system efficiency by incorporating a secondary driver with adjustable nonoverlap delay for controlling a synchronous rectifier switch in the secondary side, an active clamp switch in the primary or both. In addition, the controller features a proprietary Soft–Skip<sup>TM</sup> to reduce acoustic noise at light loads. Other features found in the NCP1652 include a high voltage startup circuit, voltage feedforward, brown out detector, internal overload timer, latch input and a high accuracy multiplier.

#### Features

- Dual Control Outputs with Adjustable Non Overlap Delay for Driving a Synchronous Rectifier Switch, an Active Clamp Switch on Both

- Voltage Feedforward Improves Loop Response

- Frequency Jittering Reduces EMI Signature

- Proprietary Soft-Skip<sup>™</sup> at Light Loads Reduces Acoustic Noise

- Brown Out Detector

- Internal 150 ms Fault Timer

- Independent Latch-Off Input Facilitates Implementation of Overvoltage and Overtemperature Fault Detectors

- Single Stage PFC and Isolated Step Down Converter

- Continuous or Discontinuous Conduction Mode Operation

- Average Current Mode Control (ACMC), Fixed Frequency Operation

- High Accuracy Multiplier Reduces Input Line Harmonics

- Adjustable Operating Frequency from 20 kHz to 250 kHz

- These are Pb-Free Devices

#### **Typical Applications**

- Notebook Adapter

- High Current Battery Chargers

- Front Ends for Distributed Power Systems

- High Power Solid State Lighting

## **ON Semiconductor®**

http://onsemi.com

= Pb-Free Package

G

#### **ORDERING INFORMATION**

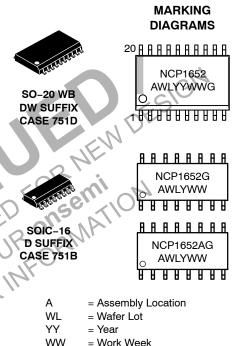

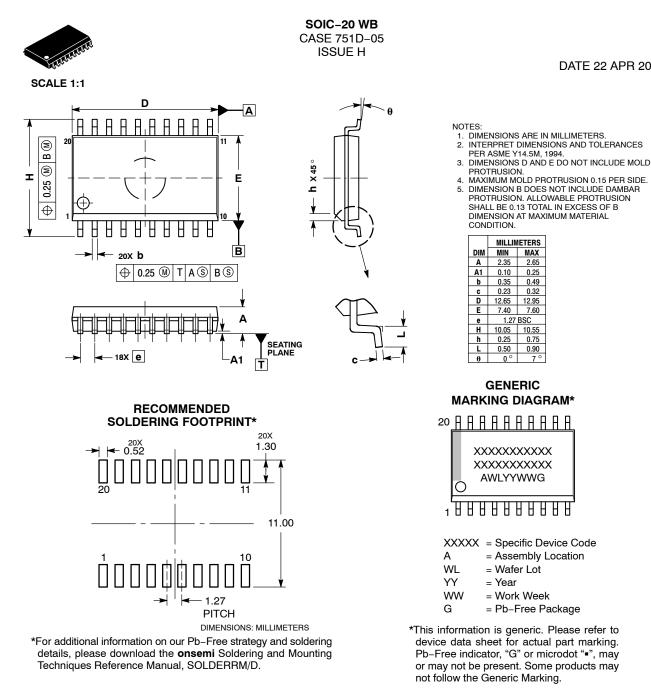

See detailed ordering and shipping information in the package dimensions section on page 32 of this data sheet.

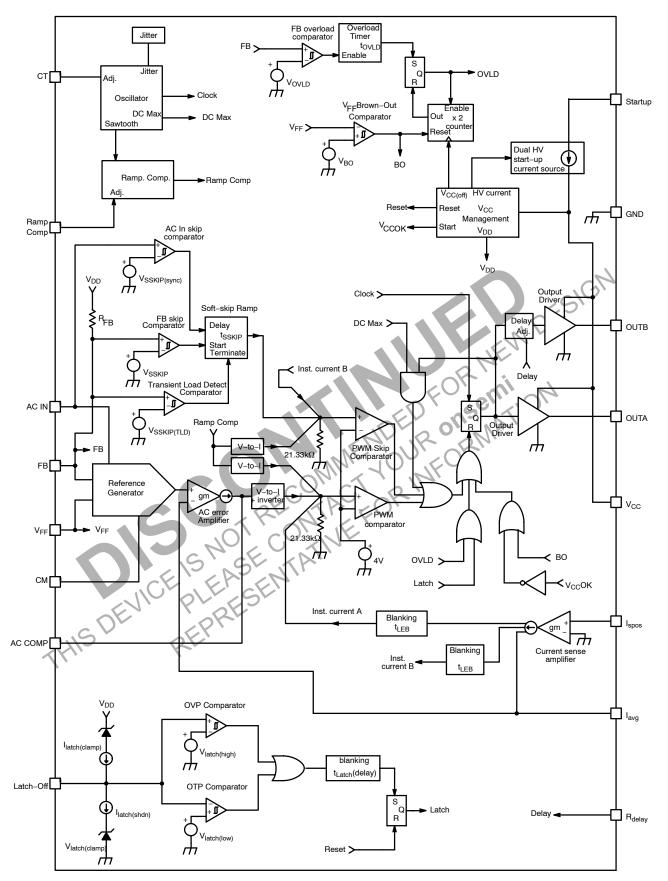

Figure 2. Detailed Block Diagram

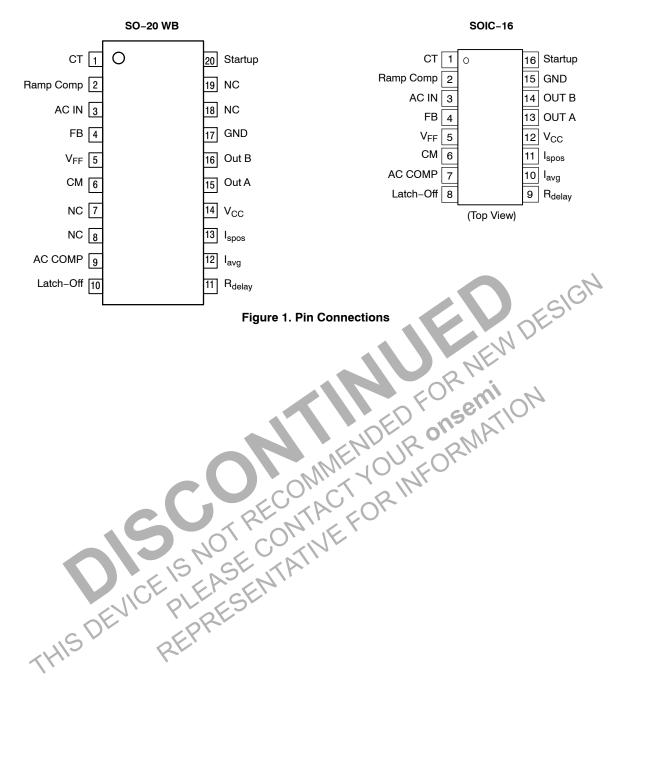

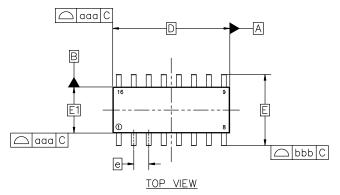

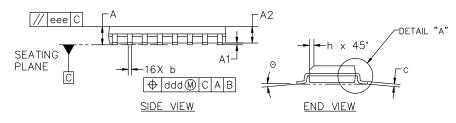

#### **PIN FUNCTION DESCRIPTION**

| Р      | in     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 Pin | 20 Pin | Symbol            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1      | 1      | CT                | An external timing capacitor ( $C_T$ ) sets the oscillator frequency. A sawtooth between 0.2 V and 4 V sets the oscillator frequency and the gain of the multiplier.                                                                                                                                                                                                                                                                                                                        |

| 2      | 2      | RAMP COMP         | A resistor ( $R_{RC}$ ) between this pin and ground adjust the amount of ramp compensation that is added to the current signal. Ramp compensation is required to prevent subharmonic oscillations. This pin should not be left open.                                                                                                                                                                                                                                                        |

| 3      | 3      | AC IN             | The scaled version of the full wave rectified input ac wave is connected to this pin by means of a resistive voltage divider. The line voltage information is used by the multiplier.                                                                                                                                                                                                                                                                                                       |

| 4      | 4      | FB                | An error signal from an external error amplifier circuit is fed to this pin via an optocoupler or other isolation circuit. The FB voltage is a proportional of the load of the converter. If the voltage on the FB pin drops below V <sub>SSKIP</sub> the controller enters Soft–Skip™ to reduce acoustic noise.                                                                                                                                                                            |

| 5      | 5      | VFF               | Feedforward input. A scaled version of the filtered rectified line voltage is applied by means of a resistive divider and an averaging capacitor. The information is used by the Reference Generator to regulate the controller.                                                                                                                                                                                                                                                            |

| 6      | 6      | СМ                | Multiplier output. A capacitor is connected between this pin and ground to filter the modulated output of the multiplier.                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7      | NC                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 8      | NC                | IEVV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7      | 9      | AC COMP           | Sets the pole for the ac reference amplifier. The reference amplifier compares the low frequen-<br>cy component of the input current to the ac reference signal. The response must be slow<br>enough to filter out most of the high frequency content of the current signal that is injected from<br>the current sense amplifier, but fast enough to cause minimal distortion to the line frequency<br>information. The pin should not be left open.                                        |

| 8      | 10     | Latch             | Latch–Off input. Pulling this pin below 1.0 V (typical) or pulling it above 7.0 V (typical) latches the controller. This input can be used to implement an overvoltage detector, an overtemperature detector or both. Refer to Figure 69 for a typical implementation.                                                                                                                                                                                                                      |

| 9      | 11     | Rdelay            | A resistor between this pin and ground sets the non-overlap time delay between OUTA and OUTB. The delay is adjusted to prevent cross conduction between the primary MOSFET and synchronous rectification MOSFET or optimize the resonant transition in an active clamp stage.                                                                                                                                                                                                               |

| 10     | 12     | lavg              | An external resistor and capacitor connected from this terminal to ground, to set and stabilizes the gain of the current sense amplifier output that drives the ac error amplifier.                                                                                                                                                                                                                                                                                                         |

| 11     | 13     | I <sub>Spos</sub> | Positive current sense input. Connects to the positive side of the current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12     | 14     | VccE              | Positive input supply. This pin connects to an external capacitor for energy storage. An internal current source supplies current from the STARTUP pin V <sub>CC</sub> . Once the voltage on V <sub>CC</sub> reaches approximately 15.3 V, the current source turns off and the outputs are enabled. The drivers are disabled once V <sub>CC</sub> reaches approximately 10.3 V. If V <sub>CC</sub> drops below 0.85 V (typical), the start-up current is reduced to less than 500 $\mu$ A. |

| 13     | 15     | OUTA 🤗            | Drive output for the main flyback power MOSFET or IGBT. OUTA has a source resistance of 13 $\Omega$ (typical) and a sink resistance of 8 $\Omega$ (typical).                                                                                                                                                                                                                                                                                                                                |

| 14     | 16     | OUTB              | Secondary output of the PWM Controller. It can be used to drive synchronous rectifier, and active clamp switch, or both. OUTB has source and sink resistances of 22 $\Omega$ (typical) and 11 (typical), respectively.                                                                                                                                                                                                                                                                      |

| 15     | 17     | GND               | Ground reference for the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | 18     | NC                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 19     | NC                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16     | 20     | HV                | Connect the rectified input line voltage directly to this pin to enable the internal startup regulator A constant current source supplies current from this pin to the capacitor connected to the $V_{CC}$ pin, eliminating the need for a startup resistor. The charge current is typically 5.5 mA. Maximum input voltage is 500 V.                                                                                                                                                        |

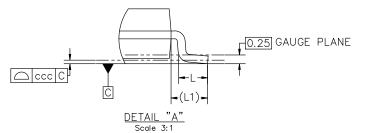

#### MAXIMUM RATINGS (Notes 1 and 2)

| Rating                                                                  | Symbol             | Value       | Unit |

|-------------------------------------------------------------------------|--------------------|-------------|------|

| Start_up Input Voltage                                                  | V <sub>HV</sub>    | −0.3 to 500 | V    |

| Start_up Input Current                                                  | I <sub>HV</sub>    | ± 100       | mA   |

| Power Supply Input Voltage                                              | V <sub>CC</sub>    | -0.3 to 20  | V    |

| Power Supply Input Current                                              | I <sub>CC</sub>    | ± 100       | mA   |

| Latch Input Voltage                                                     | V <sub>Latch</sub> | -0.3 to 10  | V    |

| Latch Input Current                                                     | I <sub>Latch</sub> | ± 100       | mA   |

| OUTA Pin Voltage                                                        | V <sub>outA</sub>  | -0.3 to 20  | V    |

| OUTA Pin Current                                                        | I <sub>outA</sub>  | ± 1.0       | A    |

| OUTB Pin Voltage                                                        | V <sub>outB</sub>  | -0.3 to 20  | V    |

| OUTB Pin Current                                                        | I <sub>outB</sub>  | ± 600       | mA   |

| All Other Pins Voltage                                                  |                    | −0.3 to 6.5 | V    |

| All Other Pins Current                                                  |                    | ± 100       | mA   |

| Thermal Resistance, Junction-to-Air<br>0.1 in" Copper<br>0.5 in" Copper | $\theta_{JA}$      | 130<br>110  | °C/W |

| Thermal Resistance, Junction-to-Lead                                    | R <sub>OJL</sub>   | 50          | °C/W |

| Maximum Power Dissipation @ T <sub>A</sub> = 25°C                       | P <sub>MAX</sub>   | 0.77        | w    |

| Operating Temperature Range                                             | Ту                 | -40 to 125  | °C   |

| Storage Temperature Range                                               | T <sub>STG</sub>   | -55 to 150  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device series contains ESD protection and exceeds the following tests:

16 pin package:

Pin 1–15: Human Body Model 2000 V per JEDEC standard JESD22, Method A114. Machine Model 200 V per JEDEC standard JESD22, Method A115. Pin 16 is the high voltage startup of the device and is rated to the maximum rating of the part, 500 V.

20 pin package:

Pin 1-19: Human Body Model 2000 V per JEDEC standard JESD22, Method A114. Machine Model 200 V per JEDEC standard JESD22, Method A115.

Pin 20 is the high voltage startup of the device and it is rated to the maximum

rating of the part, or 500 V.

rating of the part, or 500 V. 2. This device contains Latchup protection and exceeds ≥100 mA per JEDEC Standard JESD78.

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} (V_{CC} = 15 \text{ V}, V_{AC \text{ IN}} = 3.8 \text{ V}, V_{FB} = 2.0 \text{ V}, V_{FF} = 2.4 \text{ V}, V_{Latch} = \text{open}, V_{ISPOS} = -100 \text{ mV}, \\ C_{OUTA} = 1 \text{ nF}, C_T = 470 \text{ pF}, C_{IAVG} = 0.27 \text{ nF}, C_{Latch} = 0.1 \text{ nF}, C_M = 10 \text{ nF}, R_{IAVG} = 76.8 \text{ k}\Omega, R_{delay} = 49.9 \text{ k}\Omega, \\ C_{OUTB} = 330 \text{ pF}, R_{RC} = 43 \text{ k}\Omega, \text{ For typical Value } T_J = 25^{\circ}\text{C}, \text{ for min/max values } T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted}) \end{array}$

| Parameter                                                                  | Test Condition                                                                                            | Symbol                   | Min   | Тур  | Max  | Unit |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|-------|------|------|------|

| OSCILLATOR                                                                 | ·                                                                                                         |                          |       |      |      | -    |

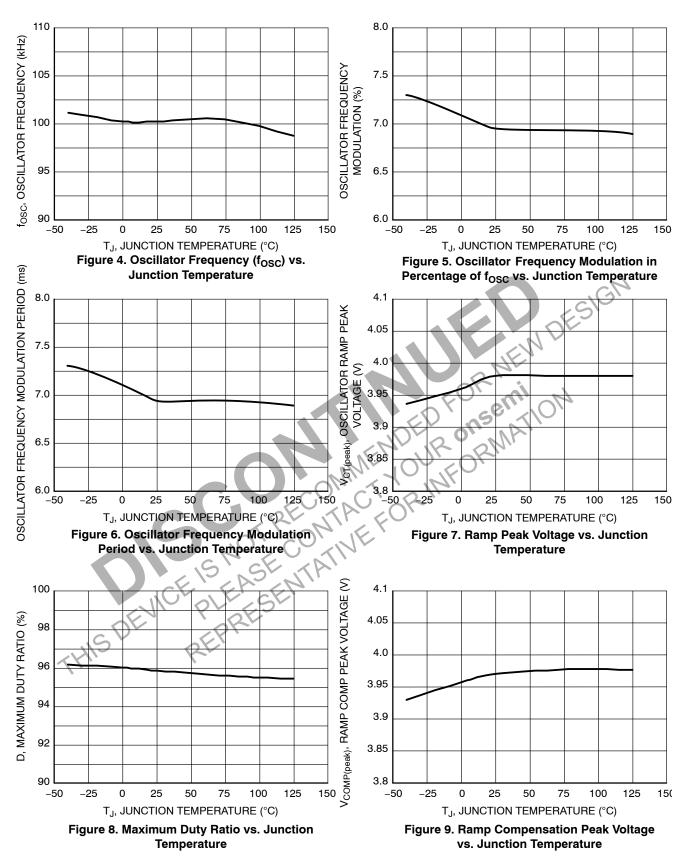

| Frequency                                                                  |                                                                                                           | f <sub>osc</sub>         | 90    | 100  | 110  | kHz  |

| Frequency Modulation in Percentage of $f_{OSC}$                            |                                                                                                           |                          | -     | 6.8  | -    | %    |

| Frequency Modulation Period                                                |                                                                                                           |                          | _     | 6.8  | -    | ms   |

| Ramp Peak Voltage                                                          |                                                                                                           | V <sub>CT(peak)</sub>    | _     | 4.0  | -    | V    |

| Ramp Valley Voltage                                                        |                                                                                                           | V <sub>CT(valley)</sub>  | _     | 0.10 | -    | V    |

| Maximum Duty Ratio                                                         | R <sub>delay</sub> = open                                                                                 | D                        | 94    | -    | -    | %    |

| Ramp Compensation Peak Voltage                                             |                                                                                                           | V <sub>RCOMP(peak)</sub> | -     | 4    | _    | V    |

| AC ERROR AMPLIFIER                                                         |                                                                                                           |                          |       |      | 2    | 1    |

| Input Offset Voltage (Note 3)                                              | Ramp I <sub>AVG</sub> , V <sub>FB</sub> = 0 V                                                             | ACVIO                    |       | 40   | G    | mV   |

| Error Amplifier Transconductance                                           |                                                                                                           |                          | -     | 100  | _    | μS   |

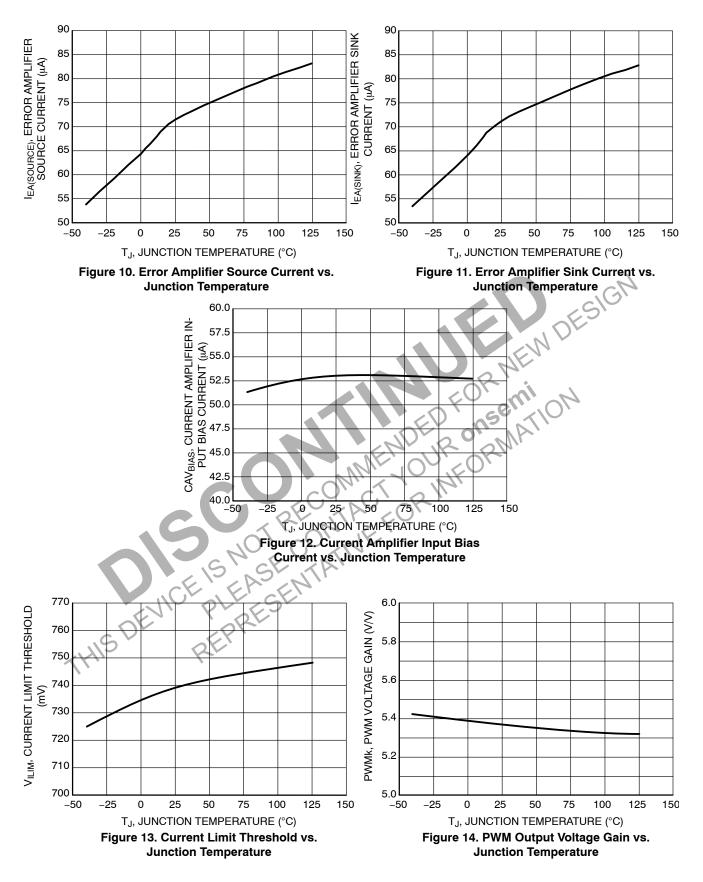

| Source Current                                                             | V <sub>AC COMP</sub> = 2.0 V, V <sub>AC IN</sub> = 2.0 V,<br>V <sub>FF</sub> = 1.0 V                      | I <sub>EA(source)</sub>  | 25    | 70   | -    | μΑ   |

| Sink Current                                                               | $V_{AC \ COMP} = 2.0 \ V, V_{A \ C \ IN} = 2.0 \ V, V_{FF} = 5.0 \ V$                                     | IEA(sink)                | -25   | -70  | _    | μA   |

| CURRENT AMPLIFIER                                                          |                                                                                                           | A Part                   |       | 14   |      |      |

| Input Bias Current                                                         | V <sub>ISPOS</sub> = 0 V                                                                                  | CAI <sub>bias</sub>      | 40    | 53   | 80   | μA   |

| Input Offset Voltage                                                       | V <sub>AC COMP</sub> = 5.0 V, V <sub>ISpos</sub> = 0 V                                                    | CAVIO                    | -20   | 0    | 20   | mV   |

| Current Limit Threshold                                                    | force OUTA high, V <sub>AC COMP</sub> = 3.0 V,<br>ramp V <sub>ISPOS</sub> , V <sub>Ramp_Comp</sub> = open | VILIM                    | 0.695 | 0.74 | 0.77 | V    |

| Leading Edge Blanking Duration                                             |                                                                                                           | t <sub>LEB</sub>         | _     | 200  | -    | ns   |

| Bandwidth                                                                  | RENTHEOU                                                                                                  |                          | _     | 1.5  | -    | MHz  |

| PWM Output Voltage Gain                                                    | $PWMk = \frac{4}{(V_{ILIM} - C_{AVIO})}$                                                                  | PWMk                     | 4.0   | 5.3  | 6.0  | V/V  |

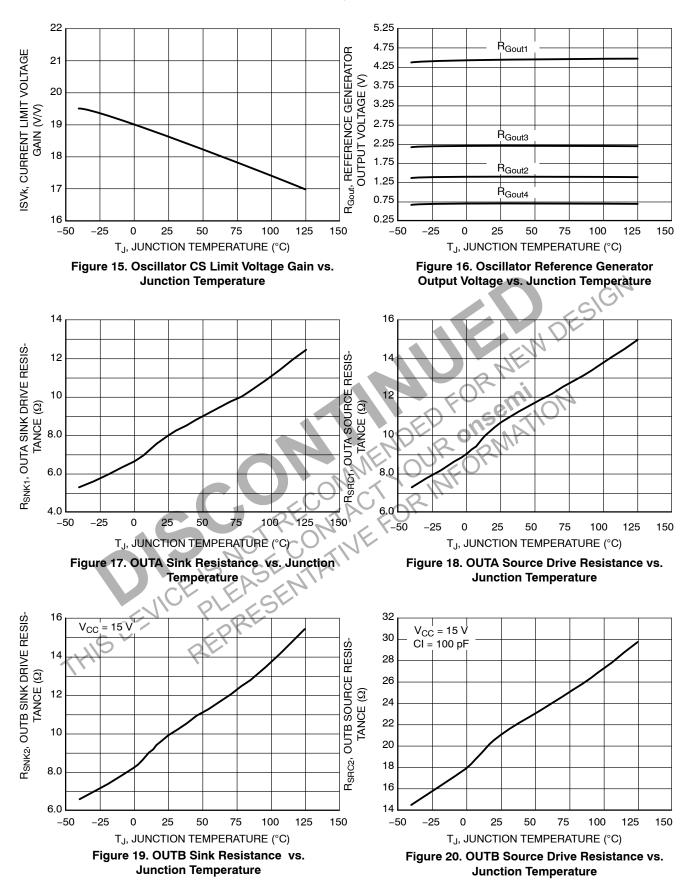

| Current Limit Voltage Gain (See<br>Current Sense Section)                  | $V_{(AVG)} = \frac{V_{(AVG)}}{VI_{SPOS}}$                                                                 | ISVk                     | 15.4  | 18.5 | 23   | V/V  |

| REFERENCE GENERATOR                                                        | pRL                                                                                                       |                          |       |      |      |      |

| Reference Generator Gain                                                   | $k = \frac{V_{AC\_REF} \cdot V_{FF}^{2}}{V_{FB} \cdot V_{AC\_IN}}$                                        | k                        | _     | 0.55 | -    | V    |

| Reference Generator output voltage (low input ac line and full load)       | V <sub>AC IN</sub> = 1.2 V, V <sub>FF</sub> = 0.765 V,<br>V <sub>FB</sub> = 4 V                           | RG <sub>out1</sub>       | 3.61  | 4.36 | 4.94 | Vpk  |

| Reference Generator output voltage (high input ac line and full load)      | $V_{AC \ IN} = 3.75 \ V, \ V_{FF} = 2.39 \ V, \\ V_{FB} = 4.0 \ V$                                        | RG <sub>out2</sub>       | 1.16  | 1.35 | 1.61 | Vpk  |

| Reference Generator output Voltage<br>(low input as line and minimum load) | $V_{AC \ IN}$ = 1.2 V, $V_{FF}$ = 0.765 V, $V_{FB}$ = 2.0 V                                               | RG <sub>out3</sub>       | 1.85  | 2.18 | 2.58 | Vpk  |

| Reference Generator output voltage (high input ac line and minimum load)   | $V_{AC\ IN}$ = 3.75 V, $V_{FF}$ = 2.39 V, $V_{FB}$ = 2.0 V                                                | RG <sub>out4</sub>       | 0.55  | 0.65 | 0.78 | Vpk  |

| Reference Generator output offset voltage                                  |                                                                                                           | RG <sub>offset</sub>     | -100  | -    | 100  | mV   |

3. Guaranteed by Design

http://onsemi.com 7

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} (V_{CC} = 15 \text{ V}, V_{AC \text{ IN}} = 3.8 \text{ V}, V_{FB} = 2.0 \text{ V}, V_{FF} = 2.4 \text{ V}, V_{Latch} = \text{open}, V_{ISPOS} = -100 \text{ mV}, \\ C_{OUTA} = 1 \text{ nF}, C_T = 470 \text{ pF}, C_{IAVG} = 0.27 \text{ nF}, C_{Latch} = 0.1 \text{ nF}, C_M = 10 \text{ nF}, R_{IAVG} = 76.8 \text{ k}\Omega, R_{delay} = 49.9 \text{ k}\Omega, \\ C_{OUTB} = 330 \text{ pF}, R_{RC} = 43 \text{ k}\Omega, \text{ For typical Value } T_J = 25^{\circ}\text{C}, \text{ for min/max values } T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted}) \end{array}$

| Parameter                                                                               | Test Condition                                                                                               | Symbol                                                                | Min              | Тур                 | Max               | Unit |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|---------------------|-------------------|------|

| AC INPUT                                                                                | -                                                                                                            |                                                                       |                  |                     |                   |      |

| Input Bias Current Into Reference<br>Multiplier & Current Compensation<br>Amplifier     |                                                                                                              | I <sub>AC IN(IB)</sub>                                                | _                | 0.01                | _                 | μΑ   |

| DRIVE OUTPUTS A and B                                                                   |                                                                                                              |                                                                       |                  |                     |                   |      |

| Drive Resistance (Thermally Limited)<br>OUTA Sink<br>OUTA Source                        | V <sub>OUTA</sub> = 1 V<br>I <sub>OUTA</sub> = 100 mA                                                        | R <sub>SNK1</sub><br>R <sub>SRC1</sub>                                |                  | 8<br>10.8           | 18<br>24          | Ω    |

| OUTB Sink<br>OUTB Source                                                                | V <sub>OUTB</sub> = 1 V<br>I <sub>OUTB</sub> = 100 mA                                                        | R <sub>SNK2</sub><br>R <sub>SRC2</sub>                                | -                | 10<br>21            | 22<br>44          |      |

| Rise Time (10% to 90%)<br>OUTA<br>OUTB                                                  |                                                                                                              | t <sub>r1</sub><br>t <sub>r2</sub>                                    | -                | 40<br>25            | A                 | ns   |

| Fall Time (90% to 10%)<br>OUTA<br>OUTB                                                  |                                                                                                              | t <sub>f1</sub><br>t <sub>f2</sub>                                    |                  | 20<br>10            |                   | ns   |

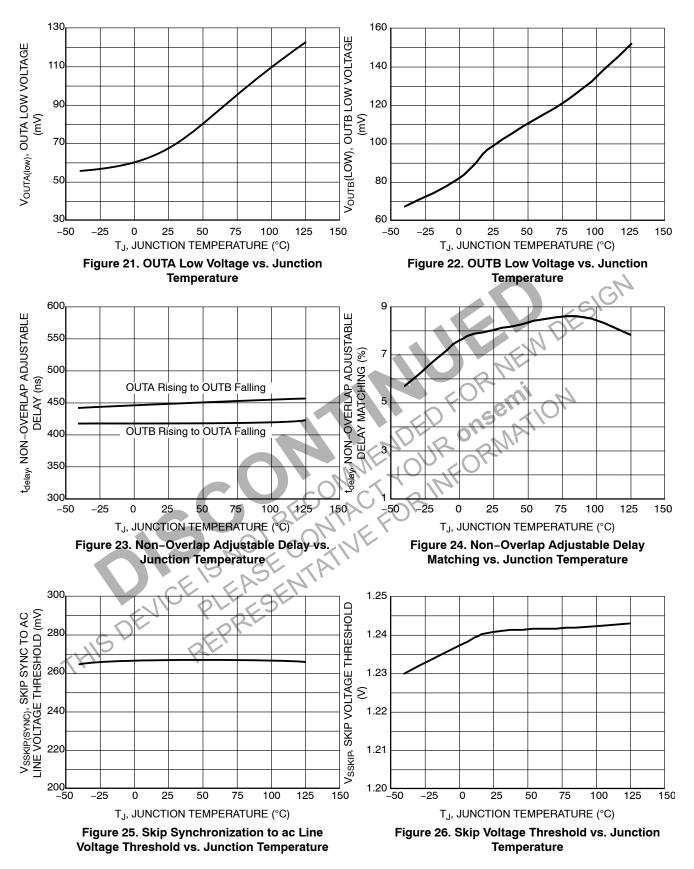

| DRV Low Voltage<br>OUTA<br>OUTB                                                         | I <sub>OUTA</sub> = 100 μA<br>I <sub>OUTB</sub> = 100 μA                                                     | V <sub>OUTA</sub> (low)<br>V <sub>OUTB</sub> (low)                    | -                | 1.0<br>1.0          | 100<br>100        | mV   |

| Non-Overlap Adjustable Delay Range<br>(Note 3)                                          |                                                                                                              | t <sub>delay(range)</sub>                                             | 0.08             | 7                   | 2.8               | μs   |

| Non-Overlap Adjustable Delay                                                            | Measured at 50% of V <sub>OUT</sub> ,                                                                        | 201                                                                   | 7.               |                     |                   | ns   |

| Leading<br>Trailing                                                                     | C <sub>OUTA</sub> = C <sub>OUTB</sub> = 100 pF<br>OUTA Rising to OUTB falling<br>OUTB Rising to OUTA falling | t <sub>delay(lead)</sub><br>t <sub>delay(trail)</sub>                 | 250<br>250       | 450<br>420          | 550<br>550        |      |

| Non-Overlap Adjustable Delay<br>Matching                                                | OUTA Rising to OUTB Falling or OUTB<br>Rising to OUTA Falling                                                | t <sub>delay(match)</sub>                                             | -                | -                   | 55                | %    |

| Soft–Skip™                                                                              | TRONIEFO                                                                                                     |                                                                       |                  |                     |                   |      |

| Skip Synchronization to ac Line<br>Voltage Threshold                                    | $V_{ACIN}$ Increasing, $V_{PB} = 1.5 V$                                                                      | V <sub>SSKIP(SYNC)</sub>                                              | 210              | 267                 | 325               | mV   |

| Skip Synchronization to ac Line<br>Voltage Threshold Hysteresis                         | V <sub>ACIN</sub> Decreasing                                                                                 | V <sub>SSKIP</sub><br>(SYNCHYS)                                       | I                | 40                  | 1                 | mV   |

| Skip Ramp Period (Note 3)                                                               | 0ES                                                                                                          | t <sub>SSKIP</sub>                                                    | 1                | 2.5                 | 1                 | ms   |

| Skip Voltage Threshold<br>NGP1652<br>NGP1652A                                           | 24-                                                                                                          | V <sub>SSKIP</sub>                                                    | 1.04<br>0.36     | 1.24<br>0.41        | 1.56<br>0.46      | V    |

| Skip Voltage Hysteresis                                                                 |                                                                                                              | V <sub>SSKIP(HYS)</sub>                                               | 45               | 90                  | 140               | mV   |

| Skip Transient Load Detect Threshold (Note 3)                                           | $V_{SSKIP(TLD)} = V_{SSKIP} + 0.55 V$                                                                        | V <sub>SSKIP(TLD)</sub>                                               | -                | 1.75                | -                 | V    |

| FEEDBACK INPUT                                                                          |                                                                                                              |                                                                       |                  |                     |                   |      |

| Pull-Up Current Source                                                                  | V <sub>FB</sub> = 0.5 V                                                                                      | I <sub>FB</sub>                                                       | 600              | 750                 | 920               | μA   |

| Pull–Up Resistor                                                                        |                                                                                                              | R <sub>FB</sub>                                                       | -                | 6.7                 | _                 | kΩ   |

| Open Circuit Voltage                                                                    |                                                                                                              | V <sub>FB(open)</sub>                                                 | 5.3              | 5.7                 | 6.3               | V    |

| STARTUP AND SUPPLY CIRCUITS                                                             |                                                                                                              |                                                                       |                  |                     |                   |      |

| Supply Voltage<br>Startup Threshold<br>Minimum Operating Voltage<br>Logic Reset Voltage | $V_{CC}$ Increasing $V_{CC}$ Decreasing $V_{CC}$ Decreasing                                                  | V <sub>CC(on)</sub><br>V <sub>CC(off)</sub><br>V <sub>CC(reset)</sub> | 14.3<br>9.3<br>– | 15.4<br>10.2<br>7.0 | 16.3<br>11.3<br>— | V    |

| Inhibit Threshold Voltage                                                               | $V_{HV}$ = 40 V, $I_{inhibit}$ = 500 $\mu$ A                                                                 | V <sub>inhibit</sub>                                                  | -                | 0.83                | 1.15              | V    |

3. Guaranteed by Design

$\textbf{ELECTRICAL CHARACTERISTICS} (V_{CC} = 15 \text{ V}, \text{ } V_{AC \text{ IN}} = 3.8 \text{ V}, \text{ } V_{FB} = 2.0 \text{ V}, \text{ } V_{FF} = 2.4 \text{ V}, \text{ } V_{Latch} = \text{open}, \text{ } V_{ISPOS} = -100 \text{ mV}, \text{ } V_{CC} = 100 \text{ mV}, \text{ } V_{CC$  $C_{OUTA} = 1 \text{ nF, } C_T = 470 \text{ pF, } C_{IAVG} = 0.27 \text{ nF, } C_{Latch} = 0.1 \text{ nF, } C_M = 10 \text{ nF, } R_{IAVG} = 76.8 \text{ k}\Omega, R_{delay} = 49.9 \text{ k}\Omega, C_{OUTB} = 330 \text{ pF, } R_{RC} = 43 \text{ k}\Omega, \text{ For typical Value } T_J = 25^{\circ}\text{C}, \text{ for min/max values } T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted})$

| Parameter                                                                                                                | Parameter Test Condition                                      |                                      | Min        | Тур          | Max        | Unit |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------|------------|--------------|------------|------|

| STARTUP AND SUPPLY CIRCUITS                                                                                              |                                                               |                                      |            | -            | -          |      |

| Inhibit Bias Current                                                                                                     | $V_{HV}$ = 40 V, $V_{CC}$ = 0.8 * $V_{inhibit}$               | I <sub>inhibit</sub>                 | 40         | -            | 500        | μA   |

| Minimum Startup Voltage                                                                                                  | $I_{start}$ = 0.5 mA, $V_{CC}$ = $V_{CC(on)}$ – 0.5 V         | V <sub>start(min)</sub>              | -          | -            | 40         | V    |

| Startup Current                                                                                                          | $V_{CC}$ = $V_{CC(on)}$ – 0.5 V, $V_{FB}$ = Open              | I <sub>start</sub>                   | 3.0        | 5.62         | 8.0        | mA   |

| Off-State Leakage Current                                                                                                | $V_{HV}$ = 400 V, $T_J$ = 25°C<br>$T_J$ = -40°C to 125°C      | I <sub>HV(off)</sub>                 | _          | 17<br>15     | 40<br>80   | μA   |

| Supply Current<br>Device Disabled (Overload)<br>Device Switching                                                         | $V_{FB}$ = Open<br>$f_{OSC} \approx 100 \text{ kHz}$          | I <sub>CC1</sub><br>I <sub>CC2</sub> | _          | 0.72<br>6.25 | 1.2<br>7.2 | mA   |

| FAULT PROTECTION                                                                                                         |                                                               |                                      |            |              | 2          |      |

| Overload Timer                                                                                                           |                                                               | tovld                                | 120        | 162          | 360        | ms   |

| Overload Detect Threshold                                                                                                |                                                               | V <sub>OVLD</sub>                    | 4.7        | 4.9          | 5.2        | V    |

| Brown–Out Detect Threshold (entering fault mode)                                                                         | $V_{FF}$ Decreasing, $V_{FB}$ = 2.5 V, $V_{AC \ IN}$ = 2.0 V  | V <sub>BO(low)</sub>                 | 0.41       | 0.45         | 0.49       | V    |

| Brown–Out Exit Threshold (exiting fault mode)                                                                            | $V_{FF}$ Increasing, $V_{FB}$ = 2.5 V,<br>$V_{AC IN}$ = 2.0 V | V <sub>BO(high)</sub>                | 0.57       | 0.63         | 0.69       | V    |

| Brown-Out Hysteresis                                                                                                     |                                                               | VBO(HYS)                             |            | 174          | -          | mV   |

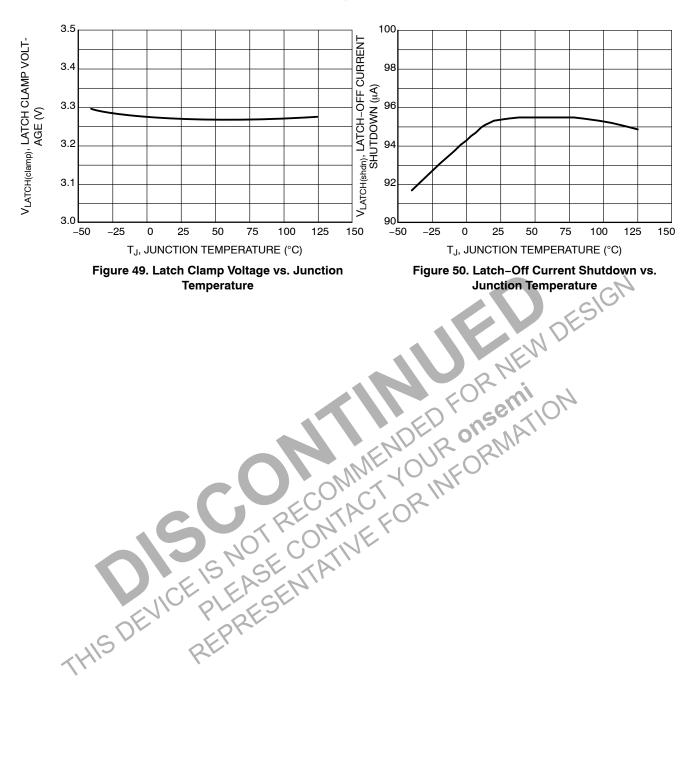

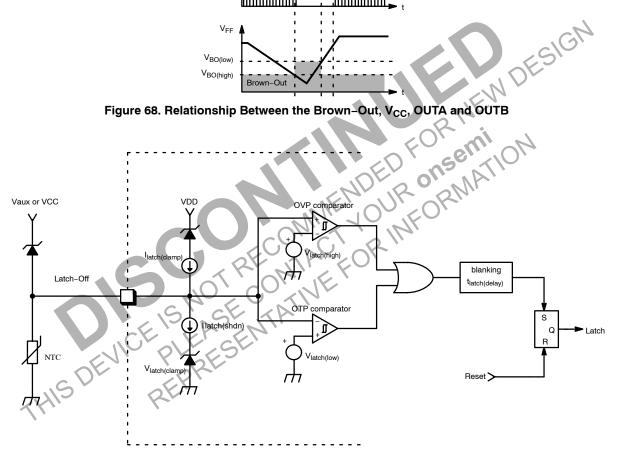

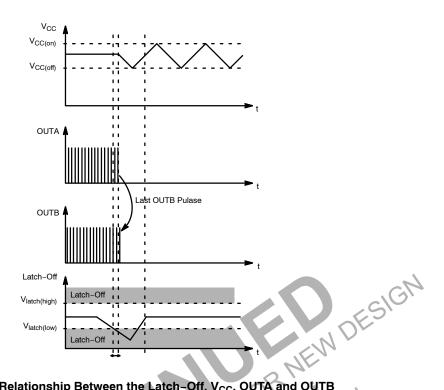

| LATCH INPUT                                                                                                              |                                                               | y ns                                 | $\sum_{i}$ |              |            |      |

| Pull-Down Latch Voltage Threshold                                                                                        | V <sub>Latch</sub> Decreasing                                 | Vlatch(low)                          | 0.9        | 0.98         | 1.1        | V    |

| Pull-Up Latch Voltage Threshold                                                                                          | V <sub>Latch</sub> Increasing                                 | Vlatch(high)                         | 5.6        | 7.0          | 8.4        | V    |

| Latch Propagation Delay                                                                                                  | $V_{\text{Latch}} = V_{\text{latch}(\text{high})}$            | t <sub>latch(delay)</sub>            | 30         | 56           | 90         | μs   |

| Latch Clamp Current (Going Out)                                                                                          | V <sub>Lateh</sub> = 1.5 V                                    | I <sub>latch(clamp)</sub>            | 42         | 51           | 58         | μA   |

| Latch Clamp Voltage (I <sub>Latch</sub> Going In)                                                                        | I <sub>Latch</sub> = 50 μA                                    | V <sub>latch(clamp)</sub>            | 2.5        | 3.27         | 4.5        | V    |

| Latch-Off Current Shutdown<br>(Going In)                                                                                 | V <sub>Latch</sub> Increasing                                 | I <sub>latch(shdn)</sub>             | -          | 95           | -          | μΑ   |

| Latch Clamp Voltage (I <sub>Latch</sub> Going In)<br>Latch-Off Current Shutdown<br>(Going In)<br>3. Guaranteed by Design | EASENIN                                                       |                                      |            |              |            |      |

#### DETAILED DEVICE DESCRIPTION

#### Introduction

The NCP1652 is a highly integrated controller combining PFC and an isolated step down ac-dc power conversion in a single stage, resulting in a lower cost and reduced part count solution. This controller is ideal for notebook adapters, battery chargers and other off-line applications with power requirements between 75 W and 150 W with an output voltage greater than 12 V. The single stage is based on the flyback converter and it is designed to operate in CCM or DCM modes.

#### **Power Factor Correction (PFC) Introduction**

Power factor correction shapes the input current of off-line power supplies to maximize the real power available from the mains. Ideally, the electrical appliance should present a load that emulates a pure resistor, in which case the reactive power drawn by the device is zero. Inherent in this scenario is the freedom from input current harmonics. The current is a perfect replica of the input voltage (usually a sine wave) and is exactly in phase with it. In this case the current drawn from the mains is at a minimum for the real power required to perform the needed work, and this minimizes losses and costs associated not only with the distribution of the power, but also with the generation of the power and the capital equipment involved in the process. The freedom from harmonics also minimizes interference with other devices being powered from the same source.

Another reason to employ PFC in many of today's power supplies is to comply with regulatory requirements. Today, electrical equipment in Europe must comply with the European Norm EN61000–3–2. This requirement applies to most electrical appliances with input power of 75 W or greater, and it specifies the maximum amplitude of line–frequency harmonics up to and including the 39<sup>th</sup> harmonic. While this requirement is not yet in place in the US, power supply manufacturers attempting to sell products worldwide are designing for compliance with this requirement.

#### Typical Power Supply with PFC

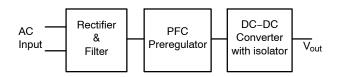

A typical power supply consists of a boost PFC preregulator creating an intermediate  $\sim 400$  V bus and an isolated dc-dc converter producing the desired output voltage as shown in Figure 51. This architecture has two power stages.

Figure 51. Typical Two Stage Power Converter

A two stage architecture allows optimization of each individual power stage. It is commonly used because of

designer familiarity and a vast range of available components. But, because it processes the power twice, the search is always on for a more compact and power efficient solution.

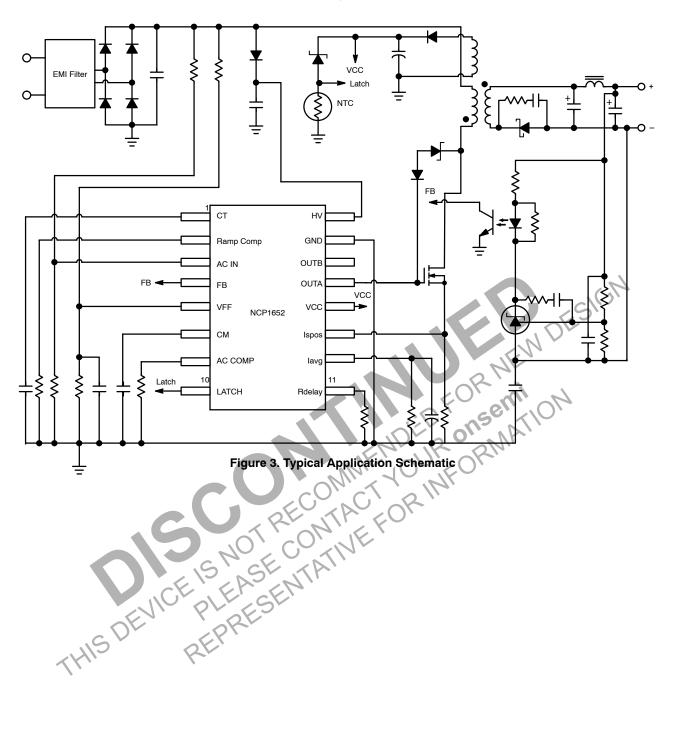

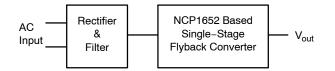

The NCP1652 controller offers the convenience of shrinking the front–end converter (PFC preregulator) and the dc–dc converter into a single power processing stage as shown in Figure 52.

Figure 52. Single Stage Power Converter

This approach significantly reduces the component count. The NCP1652 based solution requires only one each of MOSFET, magnetic element, output rectifier (low voltage) and output capacitor (low voltage). In contrast, the 2–stage solution requires two or more of the above–listed components. Elimination of certain high–voltage components (e.g. high voltage capacitor and high voltage PFC diode) has significant impact on the system design. The resultant cost savings and reliability improvement are often worth the effort of designing a new converter.

#### Single PFC Stage

While the single stage offers certain benefits, it is important to recognize that it is not a recommended solution for all requirements. The following three limitations apply to the single stage approach:

- The output voltage ripple will have a 2x line frequency component (120 Hz for North American applications) that can not be eliminated easily. The cause of this ripple is the elimination of the energy storage element that is typically the boost output capacitor in the 2-stage solution. The only way to reduce the ripple is to increase the output filter capacitance. The required value of capacitance is inversely proportional to the output voltage – hence this approach is not recommended for low voltage outputs such as 3.3 V or 5 V. However, if there is a follow-on dc-dc converter stage or a battery after the single stage converter, the low frequency ripple should not cause any concerns.

- The hold-up time will not be as good as the 2-stage approach again due to the lack of an intermediate energy storage element.

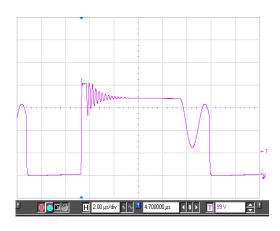

- In a single stage converter, one FET processes all the power that is both a benefit and a limitation as the stress on that main MOSFET is relatively higher. Similarly, the magnetic component (flyback transformer/inductor) can not be optimized as well as in

the 2–stage solution. As a result, potentially higher leakage inductance induces higher voltage spikes (like the one shown in Figure 53) on the MOSFET drain. This may require a MOSFET with a higher voltage rating compared to similar dc–input flyback applications.

Figure 53. Typical Drain Voltage Waveform of a Flyback Main Switch

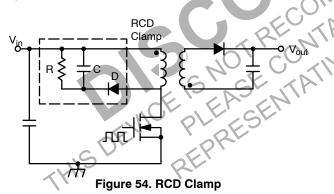

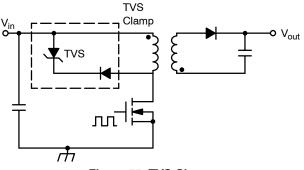

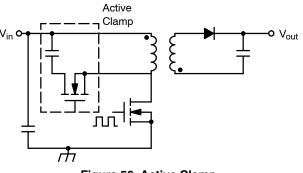

There are a few methods to clamp the voltage spike on the main switch, a resistor-capacitor-diode (RCD) clamp, a transient voltage suppressor (TVS) or an active clamp using a MOSFET and capacitor can be used as shown in Figures 54 to 56.

Figure 55. TVS Clamp

Figure 56. Active Clamp

The first two methods result in dissipation of the leakage energy in the clamping circuits – the dissipation is proportional to  $LI^2$  where L is the leakage inductance of the transformer and I is the peak of the switch current at turn–off. An RDC snubber is simple and has the lowest cost, but constantly dissipates power. A TVS provides good voltage clamping at a slightly higher cost and dissipates power only when the drain voltage exceeds the voltage rating of the TVS.

The active clamp circuit provides an intriguing alternative to the other methods. It requires addition of a MOSFET and a high voltage capacitor as part of the active clamp circuit, thus adding complexity, but it results in a complete reuse of the leakage inductance energy. As a result, the transformer construction is no longer critical and one can use cheaper cost solution. Also, the active clamp circuit reduces the voltage stress on the primary switch and that can lead to usage of lower cost or lower on resistance ( $R_{DS(on)}$ ) MOSFET. Finally, the turn-on switching losses are eliminated because the active clamp circuit allows the discharge of the MOSFET C<sub>OSS</sub> capacitance prior to the turn-on. The energy stored in the leakage inductance is utilized for this transition.

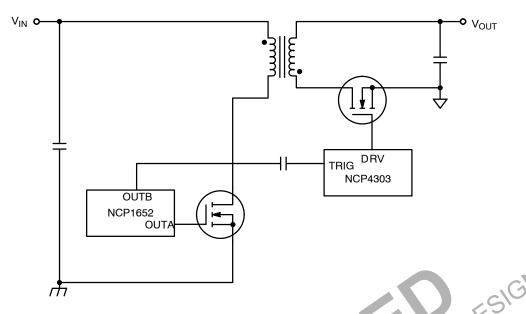

In many applications, the added complexity of the active clamp circuit may not be justified. However, the OUTB of the NCP1652 is also usable for another purpose, synchronous rectification control. Synchronous rectification for flyback converters is an emerging requirement for flyback converters. The OUTB signal from NCP1652 is ideal for interfacing with a secondary side synchronous rectifier controller such as NCP4303 as shown in Figure 57. As shown in Figure 57, using the OUTB (coupled through pulse transformer or Y-capacitor) as a trigger for the NCP4303 allows guaranteed turn-off of the secondary side synchronous MOSFET prior to turn-on of the primary switch. In any CCM flyback converter, this is a critical requirement to prevent cross-conduction and NCP1652 and NCP4303 combination is the first such chipset that guarantees the operation without cross-conduction.

Figure 57. NCP1652 and NCP4302 based single stage PFC with synchronous rectification.

The NCP1652 incorporates a secondary driver, OUTB, with adjustable non overlap delay for controlling a synchronous rectifier switch in the secondary side, an active clamp switch in the primary or both. In addition, the controller features a proprietary Soft–Skip<sup>™</sup> to reduce acoustic noise at light loads. Other features found in the NCP1652 include a high voltage startup circuit, voltage feedforward, brown out detector, internal overload timer, latch input and a high accuracy multiplier.

#### NCP1652 PFC Loop

The NCP1652 incorporates a modified version of average current mode control used for achieving the unity power factor. The PFC section includes a variable reference generator, a low frequency voltage regulation error amplifier (AC error AMP), ramp compensation (Ramp Comp) and current shaping network. These blocks are shown in the lower portion of the bock diagram (Figure 51).

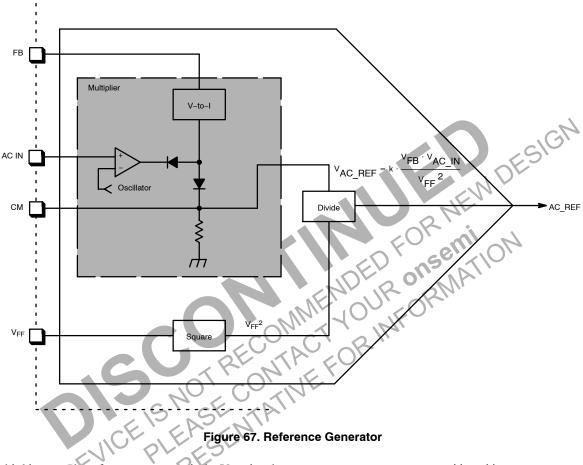

The inputs to the reference generator include feedback signal (FB), scaled AC input signal (AC\_IN) and feedforward input ( $V_{FF}$ ). The output of the reference generator is a rectified version of the input sine–wave scaled by the FB and  $V_{FF}$  values. The reference amplitude is proportional to the FB and inversely proportional to the square of the  $V_{FF}$ . This, for higher load levels and/or lower input voltage, the signal would be higher.

The function of the AC error amp is to force the average current output of the current sense amplifier to match the reference generator output. The output of the AC error amplifier is compensated to prevent response to fast events. This output ( $V_{error}$ ) is fed into the PWM comparator through a reference buffer. The PWM comparator sums the  $V_{error}$  and the instantaneous current and compares it to a 4.0 V threshold to provide the desired duty cycle control. Ramp

compensation is also added to the input signal to allow CCM operation above 50% duty cycle.

#### High Voltage Startup Circuit

The NCP1652 internal high voltage startup circuit eliminates the need for external startup components and provides a faster startup time compared to an external startup resistor. The startup circuit consists of a constant current source that supplies current from the HV pin to the supply capacitor on the V<sub>CC</sub> pin (C<sub>CC</sub>). The startup current ( $I_{start}$ ) is typically 5.5 mA.

The OUTA and OUTB drivers are enabled and the startup current source is disabled once the V<sub>CC</sub> voltage reaches V<sub>CC(on)</sub>, typically 15.3 V. The controller is then biased by the V<sub>CC</sub> capacitor. The drivers are disabled if V<sub>CC</sub> decays to its minimum operating threshold (V<sub>CC(off)</sub>) typically 10.3 V. Upon reaching V<sub>CC(off)</sub> the gate drivers are disabled. The V<sub>CC</sub> capacitor should be sized such V<sub>CC</sub> is kept above V<sub>CC(off)</sub> while the auxiliary voltage is building up. Otherwise, the system will not start.

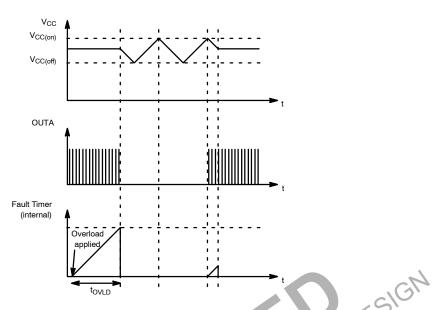

The controller operates in double hiccup mode while in overload or  $V_{CC(off)}$ . A double hiccup fault disables the drivers, sets the controller in a low current mode and allows  $V_{CC}$  to discharge to  $V_{CC(off)}$ . This cycle is repeated twice to minimize power dissipation in external components during a fault event. Figure 58 shows double hiccup mode operation. A soft-start sequence is initiated the second time  $V_{CC}$  reaches  $V_{CC(on)}$ . If the controller is latched upon reaching  $V_{CC(on)}$ , the controller stays in hiccup mode. During this mode,  $V_{CC}$  never drops below  $V_{CC(reset)}$ , the controller logic reset level. This prevents latched faults to be cleared unless power to the controller is completely removed (i.e. unplugging the supply from the AC line).

Figure 58. V<sub>CC</sub> Double Hiccup Operation with a Fault Occurring while the Startup Circuit is Disabled

An internal supervisory circuit monitors the  $V_{CC}$  voltage to prevent the controller from dissipating excessive power if the  $V_{CC}$  pin is accidentally grounded. A lower level current source (I<sub>inhibit</sub>) charges C<sub>CC</sub> from 0 V to V<sub>inhibit</sub>, typically 0.85 V. Once  $V_{CC}$  exceeds  $V_{inhibit}$ , the startup current source is enabled. This behavior is illustrated in Figure 59. This slightly increases the total time to charge  $V_{CC}$ , but it is generally not noticeable.

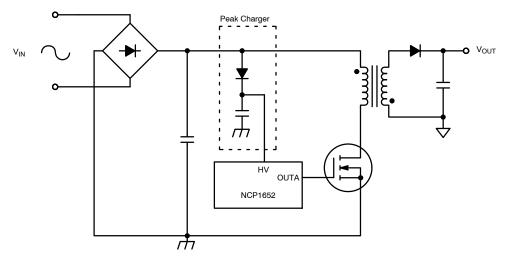

The rectified ac line voltage is provided to the power stage to achieve accurate PFC. Filtering the rectified ac line voltage with a large bulk capacitor distorts the PFC in a single stage PFC converter. A peak charger is needed to bias the HV pin as shown in Figure 60. Otherwise, the HV pin follows the ac line and the startup circuit is disabled every time the ac line voltage approaches 0 V. The  $V_{CC}$  capacitor is sized to bias the controller during power up.

Figure 60. Peak charger

The startup circuit is rated at a maximum voltage of 500 V. Power dissipation should be controlled to avoid exceeding the maximum power dissipation of the controller. If dissipation on the controller is excessive, a resistor can be placed in series with the HV pin. This will reduce power dissipation on the controller and transfer it to the series resistor.

#### **Drive Outputs**

The NCP1652 has out off phase output drivers with an adjustable non-overlap delay (t<sub>D</sub>). The main output, OUTA, drives the primary MOSFET. The secondary output, OUTB, is designed to provide a logic signal used to control a synchronous rectification switch in the secondary side, an active clamp switch in the primary or both. The outputs are biased directly from  $V_{CC}$  and their high state voltage is approximately  $V_{CC}$ .

OUTA has a source resistance of 13  $\Omega$  (typical) and a sink resistance of 8.0  $\Omega$  (typical) OUTB has a source resistance 22  $\Omega$  (typical) and a sink resistance of 10  $\Omega$  (typical). OUTB is a purposely sized smaller than OUTA because the gate charge of an active switch or logic used with synchronous rectification is usually less than that of the primary MOSFET. If a higher drive capability is required, an external discrete driver can be used.

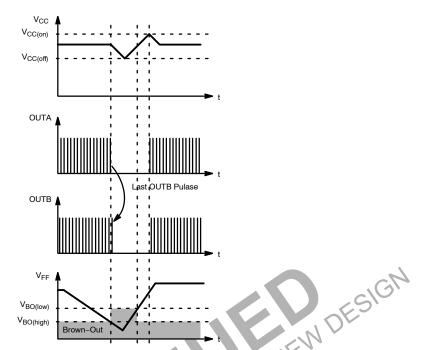

The drivers are enabled once  $V_{CC}$  reaches  $V_{CC(on)}$  and there are no faults present. They are disabled once  $V_{CC}$ discharges to  $V_{CC(off)}$ . OUTB is always the last pulse generated when the outputs are disabled due to a fault (latch-off,  $V_{CC(off)}$ , overload, or brown-out). The last pulse terminates at the end of the clock cycle. This ensures the active clamp capacitor is reset.

The high current drive capability of OUTA and OUTB may generate voltage spikes during switch transitions due to parasitic board inductance. Shortening the connection length between the drivers and their loads and using wider connections will reduce inductance–induce spikes.

#### Adjustable Dead Time

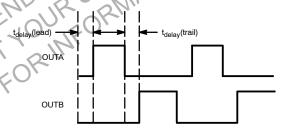

OUTA and OUTB have an adjustable dead time between transitions to prevent simultaneous conduction of the main and synchronous rectifier or active clamp MOSFETs. The delay is also used to optimize the turn-off transition of the active clamp switch to achieve zero-volt switching of the main switch in an active clamp topology. Figure 61 shows the timing relationship between OUTA and OUTB.

# Figure 61. Timing relationship between OUTA and OUTB.

The dead time between OUTA and OUTB is adjusted by connecting a resistor,  $R_D$ , from the  $R_D$  pin to ground. The overlap delay is proportional to  $R_D$ . The delay time can be set between 80 ns and 1.8  $\mu$ s using the formula:

$$\begin{split} t_{delay}(\text{in ns}) \ = \ 8.0 \ \times \ R_{delay}(\text{in } k\Omega) \ \text{with} \\ R_{delay} \ \text{varying between } 10 \ k\Omega \ \text{and} \ 230 \ k\Omega \end{split}$$

#### AC Error Amplifier and Buffer

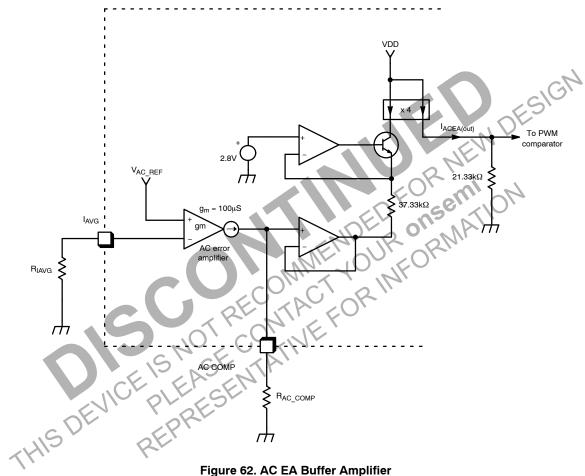

The AC error amplifier (EA) shapes the input current into a high quality sine wave by forcing the filtered input current to follow the output of the reference generator. The output of the reference generator is a full wave rectified ac signal and it is applied to the non inverting input of the EA. The filtered input current,  $I_{in}$ , is the current sense signal at the ISpos pin multiplied by the current sense amplifier gain. It is applied to the inverting input of the AC EA.

The AC EA is a transconductance amplifier. A transconductance amplifier generates an output current proportional to its differential input voltage. This amplifier has a nominal gain of 100 µS (or 0.0001 A/V). That is, an input voltage difference of 10 mV causes the output current to change by 1.0 µA. The AC EA has typical source and sink currents of 70 µA.

The filtered input current is a high frequency signal. A low frequency pole forces the average input current to follow the reference generator output. A pole-zero pair is created by placing a (R<sub>COMP</sub>) and capacitor (C<sub>COMP</sub>) series combination at the output of the AC EA. The AC COMP pin provides access to the AC EA output.

The output of the AC EA is inverted and converted into a current using a second transconductance amplifier. The output of the inverting transconductance amplifier is VACEA(buffer). Figure 62 shows the circuit schematic of the AC EA buffer. The AC EA buffer output current, IACEA(out), is given by Equation 1.

Figure 62. AC EA Buffer Amplifier

$$I_{ACEA(out)} = \left(\frac{2.8 - V_{ACEA}}{37.33k}\right) \cdot 4 \qquad (eq. 1)$$

The voltage at the PWN non-inverting input is determined by IACEA(out), the instantaneous switch current along and the ramp compensation current. OUTA is terminated once the voltage at the PWM non-inverting input reaches 4 V.

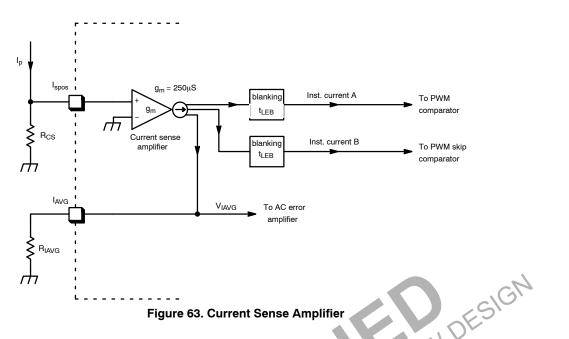

#### **Current Sense Amplifier**

A voltage proportional to the main switch current is applied to the current sense input, IS<sub>POS</sub>. The current sense

amplifier is a wide bandwidth amplifier with a differential input. The current sense amplifier has two outputs, PWM Output and IAVG Output. The PWM Output is the instantaneous switch current which is filtered by the internal leading edge blanking (LEB) circuitry prior to applying it to the PWM Comparator non inverting input. The second output is a filtered current signal resembling the average value of the input current. Figure 63 shows the internal architecture of the current sense amplifier.

Caution should be exercised when designing a filter between the current sense resistor and the  $IS_{POS}$  input, due to the low impedance of this amplifier. Any series resistance due to a filter creates a voltage offset (V<sub>OS</sub>) due to its input bias current, CA<sub>Ibias</sub>. The input bias current is typically 60  $\mu$ A. The voltage offset is given by Equation 2.

$$V_{OS} = CA_{lbias} \cdot R_{external}$$

(eq. 2)

The offset adds a positive offset to the current sense signal. The ac error amplifier will then try to compensate for the average output current which appears never to go to zero and cause additional zero crossing distortion.

A voltage proportional to the main switch current is applied to the IS<sub>POS</sub> pin. The IS<sub>POS</sub> pin voltage is converted into a current,  $i_1$ , and internally mirrored. Two internal currents are generated, I<sub>CS</sub> and I<sub>AVG</sub>. I<sub>CS</sub> is a high frequency signal which is a replica of the instantaneous switch current. I<sub>AVG</sub> is a low frequency signal. The relationship between V<sub>ISPOS</sub> and I<sub>CS</sub> and I<sub>AVG</sub> is given by Equation 3.

The PWM Output delivers current to the positive input of the PWM input where it is added to the AC EA and ramp compensation signal.

Ics

SPOS

(eq. 3)

The  $I_{AVG}$  Output generates a voltage signal to a buffer amplifier. This voltage signal is the product of  $I_{AVG}$  and an external  $R_{IAVG}$  resistor filtered by the capacitor on the  $I_{AVG}$ pin,  $C_{IAVG}$ . The pole frequency,  $f_B$  set by  $C_{IAVG}$  should be significantly below the switching frequency to remove the high frequency content. But, high enough to not to cause significant distortion to the input full wave rectified sinewave waveform. A properly filtered average current signal has twice the line frequency. Equation 4 shows the relationship between  $C_{IAVG}$  (in nF) and  $f_P$  (in kHz).

$$C_{IAVG} = \frac{1}{2 \cdot \pi \cdot R_{IAVG} \cdot f_{P}}$$

(eq. 4)

The gain of the low frequency current buffer is set by the resistor at the  $I_{AVG}$  pin,  $R_{IAVG}$ .  $R_{IAVG}$  sets the scaling factor between the primary peak and primary average currents. The gain of the current sense amplifier,  $A_{CA}$ , is given by Equation 5.

$$A_{CA} = \frac{RI_{AVG}}{4k}$$

(eq. 5)

The current sense signal is prone to leading edge spikes during the main switch turn on due to parasitic capacitance and inductance. This spike may cause incorrect operation of the PWM Comparator. Filtering the current sense signal will inevitably change the shape of the current pulse. The NCP1652 incorporates LEB circuitry to block the first 200 ns (typical) of each current pulse. This removes the leading edge spikes without altering the current signal waveform.

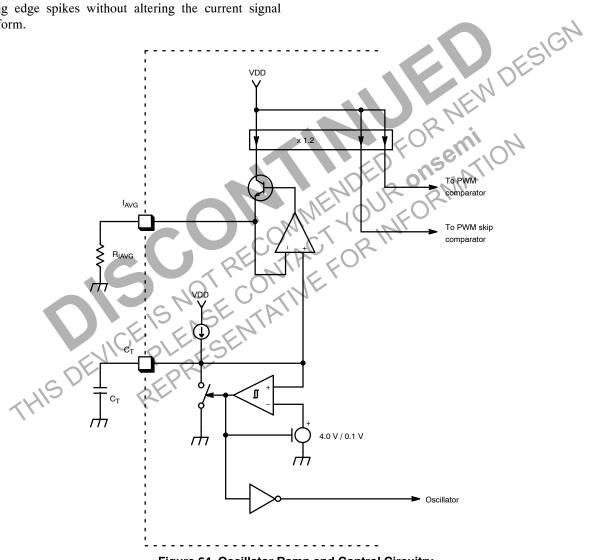

#### Oscillator

The oscillator controls the switching frequency, f, the jitter frequency and the gain of the multiplier. The oscillator ramp is generated by charging the timing capacitor on the CT Pin, C<sub>T</sub>, with a 200 µA current source. This current source is tightly controlled during manufacturing to achieve a controlled and repeatable oscillator frequency. The current source turns off and C<sub>T</sub> is immediately discharged with a pull down transistor once the oscillator ramp reaches its peak voltage, V<sub>CT(peak)</sub>, typically 4.0 V. The pull down transistor turns off and the charging current source turns on once the oscillator ramp reaches its valley voltage, V<sub>CT(valley)</sub>. Figure 64 shows the resulting oscillator ramp and control circuitry.

Figure 64. Oscillator Ramp and Control Circuitry

The relationship between the oscillator frequency in kHz and timing capacitor in pF is given by Equation 6.

$$C_{\mathsf{T}} = \frac{47000}{f} \tag{eq. 6}$$

A low frequency oscillator modulates the switching frequency, reducing the controller EMI signature and allowing the use of a smaller EMI filter. The frequency modulation or jitter is typically  $\pm 5\%$  of the oscillator frequency.

#### **Output Overload**

The Feedback Voltage,  $V_{FB}$ , is directly proportional to the output power of the converter. An internal 6.7 k $\Omega$  resistor pulls–up the FB voltage to the internal 6.5 V reference. An external optocoupler pulls down the FB voltage to regulate the output voltage of the system. The optocoupler is off during power up and output overload conditions allowing the FB voltage to reach its maximum level.

The NCP1652 monitors the FB voltage to detect an overload condition. A typical startup time of a single PFC stage converter is around 100 ms. If the converter is out of regulation (FB voltage exceeds 5.0 V) for more that 150 ms (typical) the drivers are disabled and the controller enters the double hiccup mode to reduce the average power dissipation. A new startup sequence is initiated after the double hiccup is complete. This protection feature is critical to reduce power during an output short condition.

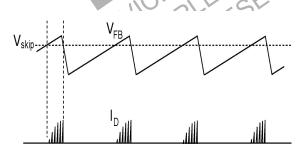

#### Soft-Skip<sup>™</sup> Cycle Mode

The FB voltage reduces as the output power demand of the converter reduces. Once  $V_{FB}$  drops below the skip threshold,  $V_{SSKIP}$  1.30 V (typical) the drivers are disabled. The skip comparator hysteresis is typically 180 mV.

The converter output voltage starts to decay because no additional output power is delivered. As the output voltage decreases the feedback voltage increases to maintain the output voltage in regulation. This mode of operation is known as skip mode. The skip mode frequency is dependent of load loop gain and output capacitance and can create audible noise due to mechanical resonance in the transformer and snubber capacitor. A proprietary Soft–Skip<sup>™</sup> mode reduces audible noise by slowly increasing the primary peak current until it reaches its maximum value. The minimum skip ramp period,  $t_{SSKIP}$  is 2.5 ms. Figure 65 shows the relationship between  $V_{FB}$ ,  $V_{SSKIP}$  and the primary current.

Figure 65. Soft–Skip<sup>™</sup> operation.

Skip mode operation is synchronous of the ac line voltage. The NCP1652 disables Soft-Skip<sup>™</sup> when the rectified ac line voltage drops to its valley level. This ensures the primary current always ramp up reducing audible noise. A skip event occurring as the ac line voltage is decreasing, causes the primary peak current to ramp down instead of ramp up. Once the skip period is over the primary current is only determined by the ac line voltage. A Soft-Skip<sup>™</sup> event terminates once the AC-IN pin voltage decreases below 260 mV. A new Soft-Skip<sup>™</sup> period starts once the voltage on the AC-IN pin increases to 260 mV.

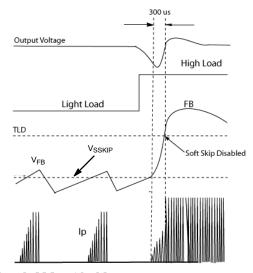

An increase in output load current terminates a Soft–Skip<sup>TM</sup> event. A transient load detector terminates a Soft–Skip<sup>TM</sup> period once  $V_{FB}$  voltage exceeds  $V_{SSKIP}$  by more than 550 mV. This ensures the required output power is delivered during a load transient and the output voltage does not fall out of regulation. Figure 66 shows the relationship between Soft–Skip<sup>TM</sup> and the transient load detector.

Figure 66. Load transient during Soft-Skip™

The output of the Soft–Skip<sup>TM</sup> Comparator is or–ed with the PWM Comparator output to control the duty ratio. The Soft–Skip<sup>TM</sup> Comparator controls the duty ratio in skip mode and the PWM Comparator controls the duty cycle during normal operation. In skip mode, the non–inverting input of the Soft–Skip<sup>TM</sup> Comparator exceeds 4 V, disabling the drivers. As the FB voltage increases, the voltage at the non–inverting input is ramp down from 4 V to 0.2 V to enable the drivers.

#### Multiplier and Reference Generator

The NCP1652 uses a multiplier to regulate the average output power of the converter. This controller uses a proprietary concept for the multiplier used within the reference generator. This innovative design allows greatly improved accuracy compared to a conventional linear analog multiplier. The multiplier uses a PWM switching circuit to create a scalable output signal, with a very well defined gain.

The output of the multiplier is the ac-reference signal. The ac-reference signal is used to shape the input current. The multiplier has three inputs, the error signal from an external error amplifier ( $V_{FB}$ ), the full wave rectified ac input (AC IN) and the feedforward input ( $V_{FF}$ ).

The FB signal from an external error amplifier circuit is applied to the  $V_{FB}$  pin via an optocoupler or other isolation circuit. The FB voltage is converted to a current with a V-I

converter. There is no error in the output signal due to the series rectifier as shown in Figure 67.

The scaled version of the full wave rectified input ac wave is applied to the AC\_IN pin by means of a resistive voltage divider. The multiplier ramp is generated by comparing the scaled line voltage to the oscillator ramp with the AC\_IN Comparator. The current signal from the V-I converter is factored by the AC\_IN comparator output. The resulting signal is filtered by the low pass R-C filter on the CM pin. The low pass filter removes the high frequency content. The gain of the multiplier is determined by the V-I converter, the resistor on the CM pin, and the peak and valley voltages of the oscillator sawtooth ramp.

The third input to the reference generator is the  $V_{FF}$  signal. The  $V_{FF}$  signal is a dc voltage proportional to the ac line voltage. A resistive voltage divider attenuates the full wave rectified line voltage between 0.7 and 5.0 V. The full wave rectified line is then averaged with a capacitor. The ac average voltage must be constant over each half cycle of the line. Line voltage ripple (120 Hz or 100 Hz) ripple on the  $V_{FF}$  signal adds ripple to the output of the multiplier. This will distort the ac reference signal and reduce the power factor and increase the line current distortion. Excessive filtering delays the feedforward signal reducing the line transient response. A good starting point is to set the filter time constant to one cycle of the line voltage. The user can then optimize the filter for line transient response versus power factor. The average voltage on the  $V_{FF}$  pin is:

$$V_{FF} = \frac{2}{\pi} Vac \sqrt{2\alpha}$$

(eq. 7)

Where,  $\alpha$  is the voltage divider ratio, normally 0.01.

$$V_{AC\_REF} = \frac{V_{FB} \cdot V_{AC\_IN}}{V_{FF}^{2}} \cdot k$$

(eq. 8)

The multiplier transfer function is given by Equation 8. The output of the multiplier is the AC\_REF. It connects to the AC Error Amplifier.

where, k is the reference generator gain, typically 0.55. The output of the reference generator is clamped at 4.5 V to limit the maximum output power.

Feedforward maintains a constant input power independent of the line voltage. That is, for a given FB voltage, if the line voltage doubles (AC\_IN), the feedforward term quadruples and reduces the output of the error amplifier in half to maintain the same input power.

#### **AC Error Amplifier Compensation**

A pole-zero pair is created by placing a series combination of  $R_{COMP}$  and  $C_{COMP}$  at the output of the AC error amplifier (EA). The value of the compensation components is

dependent of the average input current and the instantaneous switch current. The gain of the average input current or slow loop is given by Equation 9.

$$A_{LF} = \left(\frac{\mathsf{R}_{\mathsf{IAVG}}}{4\mathsf{k}}\right) \cdot \left(\mathsf{gm} \cdot \mathsf{R}_{\mathsf{AC\_COMP}}\right) \cdot \text{ (2.286) } \quad \text{ (eq. 9)}$$

The low frequency gain is the product of the current sense averaging circuit, the transconductance amplifier and the gain of the AC error amplifier.

A current proportional to the instantaneous current is generated using a  $4 k\Omega$  resistor in the current sense amplifier input. This proportional current is applied to a 21.33 k $\Omega$  at the PWM comparator input to generate a current sense voltage signal. The high frequency or fast loop gain, A<sub>HF</sub>, is calculated using Equation 10.

$$A_{HF} = \frac{21.33k}{4k} = 5.333$$

(eq. 10)

Equation 11 shows system stability requirements. That is, the low frequency gain has to be less than one half of the high frequency gain.

$$\left(\frac{\mathsf{R}_{\mathsf{IAVG}}}{4\mathsf{k}}\right) \cdot \left(\mathsf{gm} \cdot \mathsf{R}_{\mathsf{AC\_COMP}}\right) \cdot (2.286) < \frac{5.333}{2} \ (\mathsf{eq. 11})$$

Equation 12 is obtained by re-arranging Equation 11 for  $R_{AC\_COMP}$ . This equation provides the maximum value for  $R_{AC\_COMP}$ .

$$R_{AC\_COMP} < \frac{4666}{R_{IAVG} \cdot gm}$$

(eq. 12)

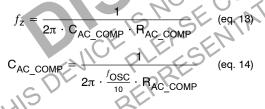

The control loop zero,  $f_Z$ , is calculated using Equation 13. The control loop zero should be set at approximately at  $1/10^{\text{th}}$  of the oscillator frequency,  $f_{\text{OSC}}$ . The compensation capacitor is calculated using Equation 14.

#### **Current Sense Resistor**

The PFC stage has two control loops. The first loop controls the average input current and the second loop controls the instantaneous current across the main switch. The current sense signal affects both loops. The current sense signal is fed into the positive input of the error amplifier to control the average input current. In addition, the current sense information together with the ramp compensation and error amplifier signal control the instantaneous primary peak current.

The primary peak current,  $I_{PK}$ , is calculated using Equation 15,

$$I_{PK} = \frac{\sqrt{2} \cdot P_{out}}{\eta \cdot V_{in(LL)} \cdot D} + \frac{V_{in(LL)} \cdot t_{on}}{0.88 \cdot 2 \cdot L_{P}} \quad (eq. 15)$$

where,  $V_{in(LL)}$  is the low line ac input voltage, D is the duty ratio,  $P_{out}$  is the output power,  $P_{in}$  is the input power,  $\eta$  is the efficiency,  $L_P$  is the primary inductance and  $t_{on}$  is the on time. Typical efficiency for this topology is around 88%.

The current sense resistor is selected to achieve maximum signal resolution at the input of the ac reference amplifier. The maximum voltage input of the ac reference amplifier to prevent saturation is 4.5 V. This together with the instantaneous peak current is used to calculate the current sense resistor,  $R_{CS}$ , using Equation 16.

$$\mathsf{R}_{\mathsf{CS}} = 4.5 \frac{4\mathsf{k} \cdot \left(\mathsf{V}_{\mathsf{in}(\mathsf{LL})} \cdot \mathsf{D}\right)}{\mathsf{R}_{\mathsf{IAVG}} \cdot \mathsf{P}_{\mathsf{in}} \cdot \sqrt{2}} \qquad (\mathsf{eq. 16})$$

#### **Ramp Compensation**

Subharmonic oscillations are observed in peak current-mode controllers operating in continuous conduction mode with a duty ratio greater than 50%. Injecting a compensation ramp on the current sense signal eliminates the subharmonic oscillations. The amount of compensation is system dependent and it is determined by the inductor falling di/dt.

The NCP1652 has built in ramp compensation to facilitate system design. The amount of ramp compensation is set by the user with a resistor,  $R_{RCOMP}$ , between the Ramp Comp pin and ground. The Ramp Comp pin buffers the oscillator ramp generated on the  $C_T$  pin. The current across  $R_{RCOMP}$  is internally mirrored with a 1:1.2 ratio. The inverted ac error amplifier and the instantaneous switch current signals are added to the ramp compensation mirrored current. The resulting current signal is applied to an internal 21.33 k $\Omega$  between the PWM Comparator non inverting input and ground as shown in Figure 64.

The maximum voltage contribution of the ramp compensation signal to the error signal,  $V_{\text{RCOMP}}$ , is given by Equation 17.

$$V_{\text{RCOMP}} = \frac{(1.2) \cdot \left(V_{\text{CT(peak)}}\right) \cdot (21.33k)}{R_{\text{RCOMP}}} = \frac{102.38k}{R_{\text{RCOMP}}}$$

where,  $V_{CT(peak)}$  is the oscillator ramp peak voltage, typically 4.0 V.

For proper ramp compensation, the ramp signal should match the falling di/dt (which has been converted to a dv/dt) of the inductor at 50% duty cycle. Both the falling di/dt and output voltage need to be reflected by the transformer turns ratio to the primary side. Equations 18 through 23 assist in the derivation of equations for  $R_{CS}$  and  $R_{COMP}$

$$\frac{\text{di}}{\text{dt}_{\text{secondary}}} = \frac{\text{V}_{\text{out}}}{\text{L}_{\text{S}}} = \frac{\text{V}_{\text{out}}}{\text{L}_{\text{P}}} \cdot \left(\frac{\text{N}_{\text{P}}}{\text{N}_{\text{S}}}\right)^2 \qquad (\text{eq. 18})$$

$$\frac{di}{dt_{primary}} = \frac{di}{dt_{secondary}} \cdot \frac{N_S}{N_P} = \frac{V_{out}}{L_P} \frac{N_P}{N_S}$$

(eq. 19)

$$V_{\text{RCOMP}} = \frac{\text{di}}{\text{dt}_{\text{primary}}} \cdot \mathbf{T} \cdot \mathbf{R}_{\text{CS}} \cdot \mathbf{A}_{\text{HF}} \quad (\text{eq. 20})$$

$$R_{CS} = \frac{N_S}{N_P} \cdot \frac{L_P \cdot 102.38k}{T \cdot A_{HF} \cdot V_{out} \cdot R_{RCOMP}} \quad (eq. 21)$$

At low line and full load, the output of the ac error amplifier output is nearly saturated in a low state. While the ac error amplifier output is saturated,  $I_{ACEA}$  is zero and does not contribute to the voltage across the internal 21.33 k $\Omega$ resistor on the PWM comparator non-inverting input. In this operation mode, the voltage across the 21.33 k $\Omega$  resistor is determined solely by the ramp compensation and the instantaneous switch current as given by Equation 22.

$$V_{ref(PWM)} = \left(V_{RCOMP} \cdot \frac{t_{on}}{T}\right) + V_{INST}$$

(eq. 22)

The voltage reference of the PWM Comparator,  $V_{REF(PWM)}$ , is 4 V. For these calculations, 3.8 V is used to provide some margin. The maximum instantaneous switch current voltage contribution,  $V_{INST}$ , is given by Equation 23.

$$V_{\rm INST} = I_{\rm PK} \cdot R_{\rm CS} \cdot A_{\rm HF} \qquad (eq. 23)$$