# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# FSUSB63 — 3:1 High-Speed USB 2.0 Switch / Multiplexer

### **Features**

| Constants Times        | 0.4 LICD C:4-k              |

|------------------------|-----------------------------|

| Sw itch Type           | 3:1 USB Switch              |

| LIOD                   | USB 2.0 High-Speed &        |

| USB                    | Full-Speed Compliant        |

| Break-Before-Make Time | 126µs                       |

| Ron                    | 6Ω Typical                  |

| Con                    | 6pF Typical                 |

| Bandw idth             | 830MHz                      |

| Vcc                    | 2.7 to 4.4V                 |

| V <sub>CNTRL</sub>     | 0 to V <sub>CC</sub>        |

| Operating Temperature  | -40°C to 85°C               |

| ICCSLP                 | <1µA                        |

| ССАСТ                  | 7.5µA Typical               |

| Package                | 12- Lead UMLP 1.80 x 1.80 x |

| rackaye                | 0.55mm, 0.40mm pitch        |

| Top Mark               | KG                          |

| Ordering Information   | FSUSB63UMX                  |

## **Applications**

- Cell Phone, Digital Camera, Notebook

- LCD Monitor, TV, and Set-Top Box

- Netbook, Mobile Internet Device (MID)

### **Description**

The FSUSB63 is a bi-directional, low-power, High-Speed (HS) USB 2.0 3:1 Multiplexer (MUX). It is optimized for switching among three high-speed (480Mbps) sources or any combination of high-speed and full-speed (12Mbps) USB sources, such as an application processor, to one USB 2.0 connector.

The FSUSB63 has a break-before-make time to force reenumeration by the host when switching between different HS USB 2.0 controllers and thus requires minimal software changes.

The FSUSB63 is compliant with the requirements of USB 2.0 and features extremely low on capacitance  $(C_{ON})$ . The wide bandwidth exceeds the requirement to pass the third harmonic, resulting in signals with minimum edge and phase distortion. Superior channel-to-channel crosstalk also minimizes interference.

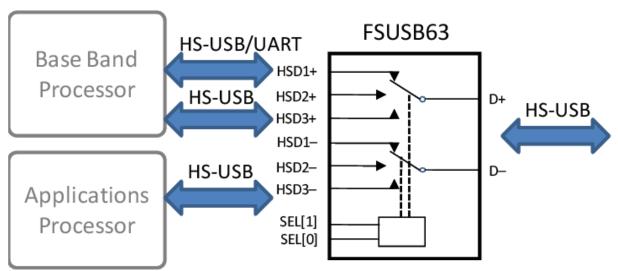

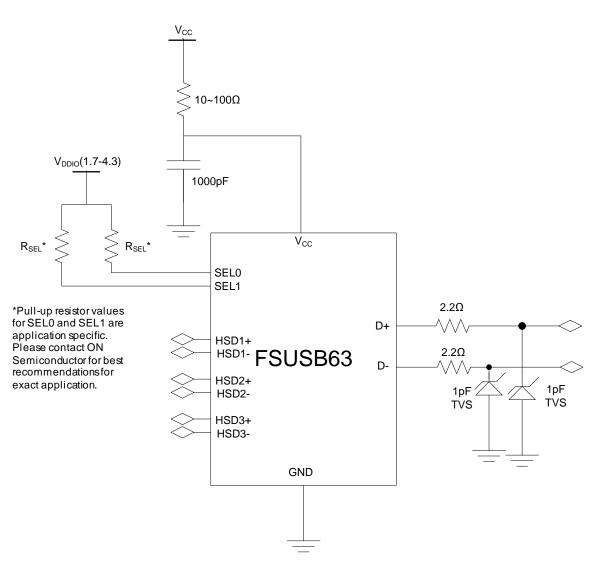

## **Typical Application**

Figure 1. Analog Symbol

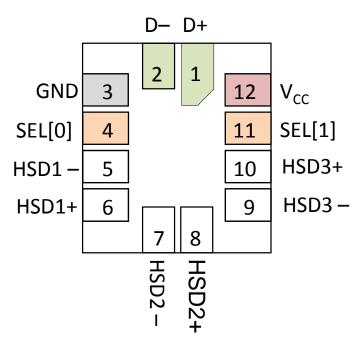

# **Pin Configuration**

Figure 2. Pin Assignments (Top Through View)

# **Pin Descriptions**

| Pin # | Name   | Description                                                |

|-------|--------|------------------------------------------------------------|

| 1     | D+     | USB 2.0 High Speed or Full Speed Data Bus D+               |

| 2     | D-     | USB 2.0 High Speed or Full Speed Data Bus D-               |

| 3     | GND    | Ground                                                     |

| 4     | SEL[0] | Path Selection Control Inputs (see functional table below) |

| 5     | HSD1-  | Multiplexed First Source Path for D-                       |

| 6     | HSD1+  | Multiplexed First Source Path for D+                       |

| 7     | HSD2-  | Multiplexed Second Source Pathfor D-                       |

| 8     | HSD2+  | Multiplexed Second Source Pathfor D+                       |

| 9     | HSD3-  | Multiplexed Third Source Path for D-                       |

| 10    | HSD3+  | Multiplexed Third Source Path for D+                       |

| 11    | SEL[1] | Path Selection Control Inputs (see functional table below) |

| 12    | Vcc    | Supply Voltage                                             |

# **Functional Table**

| Mode       | SEL[1] | SEL[0] | Function                |

|------------|--------|--------|-------------------------|

| Sleep Mode | 0      | 0      | D+, D- Switch PathsOpen |

| USB Port 1 | 0      | 1      | D+=HSD1+, D-=HSD1-      |

| USB Port 2 | 1      | 0      | D+=HSD2+, D-=HSD2-      |

| USB Port 3 | 1      | 1      | D+=HSD3+, D-=HSD3-      |

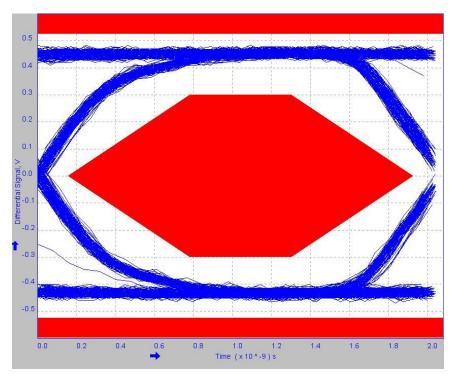

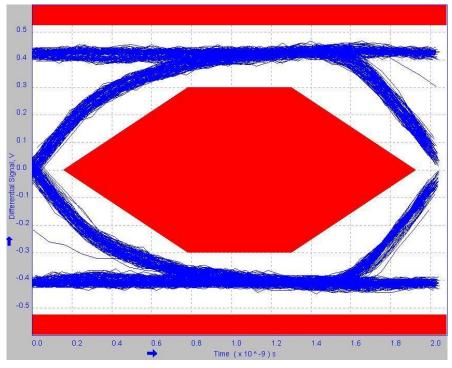

# **Eye Compliance**

Figure 3. USB 2.0 HS-USB Eye Compliance Pass Through (without Switch)

Figure 4. USB 2.0 HS-USB Eye Compliance with Switch

### Notes:

- 1. Figure 3 indicates the HS-USB eye compliance of the source across a characterization board proir to the implementation of the sw tich.

- 2. Figure 4 shows the total impact the swich has on HS-USB eye compliance when compared to Figure 3

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             | Parameter                                     | Min.                                          | Max.  | Unit |       |

|--------------------|-----------------------------------------------|-----------------------------------------------|-------|------|-------|

| Vcc                | Supply Voltage                                |                                               | -0.50 | 5.25 | V     |

| V <sub>CNTRL</sub> | DC Input Voltage (SEL[1:0]) <sup>(3)</sup>    |                                               | -0.5  | Vcc  | V     |

| Vsw                | DC Sw itch I/O Voltage <sup>(3)</sup>         |                                               | -0.50 | 5.25 | V     |

| l <sub>IK</sub>    | DC Input Diode Current                        |                                               | -50   |      | mA    |

| Юит                | DC Switch Current                             |                                               |       | 50   | mA    |

| T <sub>STG</sub>   | Storage Temperature                           | -65                                           | +150  | °C   |       |

| MSL                | Moisture Sensitivity Level (JEDEC J-STD-020A) | Moisture Sensitivity Level (JEDEC J-STD-020A) |       | 1    | Level |

|                    | IEC61000-4-2 System on USB Connector Pins     | Air Gap                                       | 15.0  |      |       |

|                    | D+ & D-                                       | Contact                                       | 8.0   |      | 1     |

| ESD                |                                               | Power to GND                                  | 16.0  |      | kV    |

| ESD                | Human Body Model, JEDEC: JESD22-A114          |                                               | 5.0   |      | NV    |

|                    |                                               | All Pins                                      | 5.0   |      |       |

|                    | Charged Device Model, JEDEC: JESD22-C101      |                                               | 1.5   |      | 1     |

#### Note:

3. The input and output negative ratings may be exceeded if the input and output diode current ratings are observed.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                            | Parameter                        | Min. | Max. | Unit |

|-----------------------------------|----------------------------------|------|------|------|

| V <sub>CC</sub>                   | Supply Voltage                   | 2.7  | 4.4  | V    |

| V <sub>CNTRL</sub> <sup>(4)</sup> | Control Input Voltage (SEL[1:0]) | 0    | Vcc  | V    |

| V <sub>SW</sub>                   | Sw itch I/O Voltage              | -0.5 | 4.3  | V    |

| T <sub>A</sub>                    | Operating Temperature            | -40  | +85  | °C   |

### Note:

4. The control input must be held HIGH or LOW and it must not float.

### **DC Electrical Characteristics**

All typical values are for  $V_{CC}$ =3.3V at  $T_A$ =25°C unless otherwise specified.

| Symbol                         | Parameter                                             | Conditions                                                                        | V (V)               | T <sub>A</sub> =- 40°C to +85°C |      |      | Units  |

|--------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|---------------------------------|------|------|--------|

| Symbol                         |                                                       | Conditions                                                                        | V <sub>CC</sub> (V) | Min.                            | Тур. | Max. | Joints |

| $V_{IK}$                       | Clamp Diode Voltage                                   | I <sub>IN</sub> =-18mA                                                            | 2.7                 |                                 |      | -1.2 | V      |

| $V_{IH}$                       | Input Voltage High                                    | SEL[1], SEL[0] Inputs                                                             | 2.7 to 4.3          | 1.0                             |      |      | V      |

| $V_{IL}$                       | Input Voltage Low                                     | SEL[1], SEL[0] Inputs                                                             | 2.7 to 4.3          |                                 |      | 0.35 | V      |

| I <sub>IN</sub>                | Control Input Leakage                                 | All Combinations of SEL[1] & SEL[0] in the Truth Table (LOW=0V & HIGH= $V_{CC}$ ) | 4.3                 |                                 |      | 1    | μΑ     |

| l <sub>oz</sub>                | Off-State Leakage                                     | $0 \le \square D_n$ , $HSD1_n$ , $HSD2_n$ , $HSD3_n \le \square 3.6V$             | 4.3                 | -2                              |      | 2    | μΑ     |

| I <sub>OFF</sub>               | Power-Off Leakage Current (All I/O Ports)             | $V_{SW}$ =0V to 4.3V, $V_{CC}$ =0V, Figure 7                                      | 0                   | -2                              |      | 2    | μΑ     |

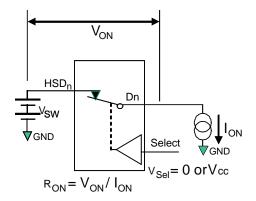

| R <sub>ON</sub> <sup>(5)</sup> | HS Switch On Resistance                               | V <sub>SW</sub> =0.4V, I <sub>ON</sub> =-8mA, Figure 6                            | 3.0                 |                                 | 6.0  | 7.8  | Ω      |

| $\Delta R_{\text{ON}}$         | HS Delta R <sub>ON</sub> <sup>(6)</sup>               | V <sub>SW</sub> =0.4V, I <sub>ON</sub> =-8mA                                      | 3.0                 |                                 | 0.50 |      | Ω      |

| I <sub>CCSLP</sub>             | Sleep Mode Supply Current                             | SEL[1]=SEL[0]=0                                                                   | 3.6                 |                                 |      | 1    | μΑ     |

|                                | Active Made Cupply Current                            | V <sub>CNTRL</sub> =0 or V <sub>CC</sub> ,                                        | 2.7                 |                                 | 7.5  | 15.0 | μΑ     |

| ICCACT                         | Active Mode Supply Current                            | I <sub>OUT</sub> =0                                                               | 3.6                 |                                 | 8.5  | 16.0 | μΑ     |

| 1                              | Increase in I <sub>CC</sub> Current per Control Input | V <sub>CNTRL</sub> =1.8V                                                          | 3.6                 |                                 | 1.5  | 4.0  | μΑ     |

| I <sub>CCT</sub>               | and V <sub>CC</sub>                                   | V <sub>CNTRL</sub> =1.2V                                                          | 3.6                 |                                 | 3.0  | 5.0  | μΑ     |

#### Notes

- 5. Measured by the voltage drop between HSD<sub>n</sub> and D<sub>n</sub> pins at the indicated current through the switch. On resistance is determined by the lower of the voltage on the two (HSD<sub>n</sub> or D<sub>n</sub> ports).

- 6. Guaranteed by characterization.

### **AC Electrical Characteristics**

All typical values are for V<sub>CC</sub>=3.3V at T<sub>A</sub>=25°C unless otherwise specified.

| Symbol           | Parameter                                                                                   | Conditions                                                                     | V == (\/\           | T <sub>A</sub> =- 40°C to +85°C |      |      | Units |

|------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------|---------------------------------|------|------|-------|

| Symbol           |                                                                                             |                                                                                | V <sub>CC</sub> (V) | Min.                            | Тур. | Max. | Units |

| t <sub>ON</sub>  | Turn-On Time when Switching from One USB Path (or Disabled i.e. SEL=00) to Another USB Path | $R_L$ =50 $\Omega$ , $C_L$ =35pF<br>$V_{sw}$ =0.8V<br>Figure 8, Figure 9       | 3.0 to 3.6          | 126                             |      | 400  | μs    |

| t <sub>OFF</sub> | Tum-Off Time<br>SEL≠00 (Any of the Three USB Paths<br>Active) to SEL=00 (Disabled)          | $R_L$ =50 $\Omega$ , $C_L$ =35pF<br>$V_{sw}$ = 0.8 $V$<br>Figure 8, Figure 9   | 3.0 to 3.6          |                                 |      | 45   | ns    |

| t <sub>PD</sub>  | Propagation Delay <sup>(7)</sup>                                                            | $C_L$ =5pF, $R_L$ =50 $\Omega$<br>Figure 8, Figure 10                          | 3.3                 |                                 | 0.25 |      | ns    |

| t <sub>BBM</sub> | Break-Before-Make Time                                                                      | $R_L$ =50 $\Omega$ , $C_L$ =35pF<br>$V_{SW1}$ = $V_{SW2}$ = 0.8V,<br>Figure 12 | 3.0 to 3.6          | 126                             |      | 400  | μs    |

| O <sub>IRR</sub> | Off Isolation <sup>(7)</sup>                                                                | R <sub>L</sub> =50Ω, f=240MHz<br>Figure 14                                     | 3.0 to 3.6          |                                 | -42  |      | dB    |

| Xtalk            | Non-Adjacent Channel Crosstalk <sup>(7)</sup>                                               | R <sub>L</sub> =50Ω, f=240MHz<br>Figure 15                                     | 3.0 to 3.6          |                                 | -33  |      | dB    |

| BW               | -3db Bandwidth <sup>(7)</sup>                                                               | $R_L$ =50 $\Omega$ , $C_L$ =0pF<br>Figure 13                                   | 3.0 to 3.6          |                                 | 830  |      | MHz   |

| D11              | Sub Bandwidth                                                                               | $R_L$ =50 $\Omega$ , $C_L$ =5pF<br>Figure 13                                   | 3.0 to 3.6          |                                 | 510  |      | MHz   |

### Note:

7. Guaranteed by characterization.

# **USB High-Speed Related AC Electrical Characteristics**

| Symbol             | Parameter                                           | Conditions Vcc (V)                                                          |            | TA=- | 40°C to | +85°C | Units |

|--------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|------------|------|---------|-------|-------|

| Syllibol           | Farameter                                           | Conditions                                                                  | VCC (V)    | Min. | Тур.    | Max.  | Uiils |

| t <sub>SK(P)</sub> | Pulse Skew (8)                                      | $V_{SW}$ =0.2 $V$ diff <sub>PP</sub> , Figure 11, $C_L$ =5 $pF$             | 3.0 to 3.6 |      | 10      |       | ps    |

| t <sub>SK(I)</sub> | Skew Between Differential Signals within a Pair (8) | V <sub>SW</sub> =0.2Vdiff <sub>PP</sub> ,<br>Figure 11, C <sub>L</sub> =5pF | 3.0 to 3.6 |      | 10      |       | ps    |

# Capacitance

| Symbol          | Parameter                                                                                   | Conditions                                                                                | T <sub>A</sub> =- 40°C to +85°C |      |      | Units |

|-----------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------|------|------|-------|

| Symbol          | Parameter                                                                                   | Conditions                                                                                | Min.                            | Тур. | Max. | Units |

| C <sub>iN</sub> | SEL[1:0] Input Capacitance <sup>(8)</sup>                                                   | Vcc=0V                                                                                    |                                 | 3    |      |       |

| Con             | Con D+/D- On Capacitance <sup>(8)</sup>                                                     | V <sub>CC</sub> =3.3V, Any of the Three Switch<br>Paths Enabled, f=1MHz, Figure 17        |                                 | 6    |      | , F   |

| JON             | On Supasitance                                                                              | V <sub>CC</sub> =3.3V, Any of the Three Sw itch<br>Paths Enabled, f=240MHz <sup>(9)</sup> |                                 | 5    |      | pF    |

| Coff            | HSD1 <sub>n</sub> , HSD2 <sub>n</sub> , HSD3 <sub>n</sub> Off<br>Capacitance <sup>(8)</sup> | V <sub>CC</sub> =0V or (V <sub>CC</sub> =3.3V and SEL[1]=SEL[0]=0V) Figure 16             |                                 | 2    |      |       |

### Notes:

- 8. Guaranteed by characterization.

- 9. Effective capacitance measured on a network analyzer.

# **Reference Schematic**

Figure 5. Reference Schematic

# **Test Diagrams**

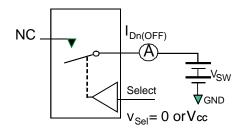

Figure 6. On Resistance

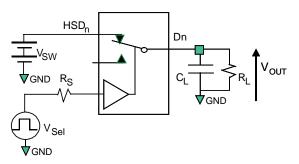

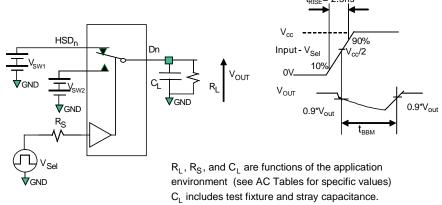

$R_L$ ,  $R_S$ , and  $C_L$  are functions of the application environment (see AC Tables for specific values)  $C_L$  includes test fixture and stray capacitance.

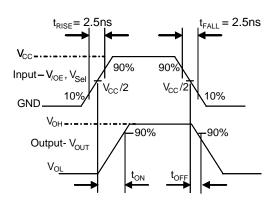

Figure 8. AC Test Circuit Load

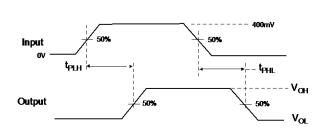

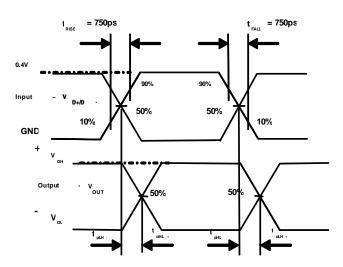

Figure 10. Propagation Delay (t<sub>R</sub>t<sub>F</sub> - 500ps)

\*\*Each switch port is tested separately

Figure 7. Off Leakage

Figure 9. Turn-On / Turn-Off Waveforms

Figure 11. Skew Test Waveforms tsk(P)=| tpLH- - tpHL- | or | tpLH+ - tpHL+ | tsk(I)=| tpLH- - tpHL+ | or | tpLH+ - tpHL- |

## Test Diagrams (Continued)

Figure 12. Break-Before-Make Interval Timing

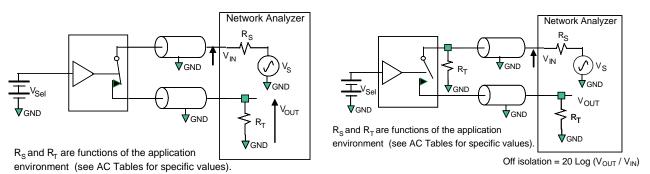

Figure 13. Bandwidth

Figure 14. Channel Off Isolation

Figure 15. Non-Adjacent Channel-to-Channel Crosstalk

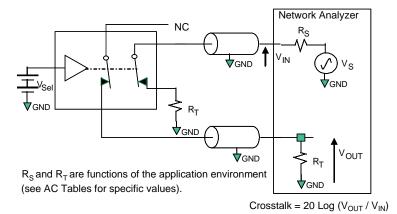

Figure 16. Channel Off Capacitance

Figure 17. Channel On Capacitance

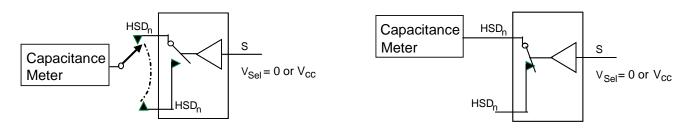

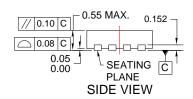

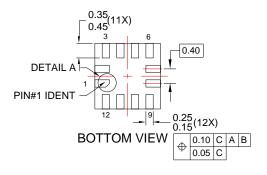

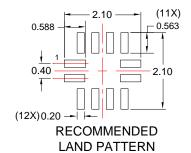

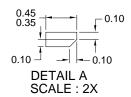

## **Physical Dimensions**

### NOTES:

- A. PACKAGE DOES NOT FULLY CONFORM TO JEDEC STANDARD.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M. 1994.

- D. LAND PATTERN RECOMMENDATION IS BASED ON FSC DESIGN ONLY.

- E. DRAWING FILENAME: MKT-UMLP12Arev4.

Figure 18. 12-Lead, Ultrathin Molded Leadless Package (UMLP)

### Ordering Information

| Part Number | Top Mark | Operating Temperature Range | Package                                                                                      |

|-------------|----------|-----------------------------|----------------------------------------------------------------------------------------------|

| FSUSB63UMX  | KG       |                             | 12-Lead, Quad, Ultrathin Molded Leadless Package (UMLP), 1.8mm x 1.8mm x 0.55mm, 0.4mm pitch |

Package drawings are provided as a service to customers considering ON Semiconductor components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a ON Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of ON Semiconductor's worldwide terms and conditions, specifically the warranty therein, which covers ON Semiconductor products.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and requirements standards, regardless of any support or applications information ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada.

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semic on ductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative