# Motion SPM<sup>®</sup> 5 Series

# Description

The FSB50250B / FSB50250BS is an advanced Motion SPM 5 module providing a fully-featured, high-performance inverter output stage for AC Induction, BLDC and PMSM motors such as refrigerators, fans and pumps. These modules integrate optimized gate drive of the built-in MOSFETs (FRFET technology) to minimize EMI and losses, while also providing multiple on-module protection features including under-voltage lockouts and thermal monitoring. The built-in high-speed HVIC requires only a single supply voltage and translates the incoming logic-level gate inputs to the high-voltage, high-current drive signals required to properly drive the module's internal MOSFETs. Separate open-source MOSFET terminals are available for each phase to support the widest variety of control algorithms.

## Features

- UL Certified No. E209204 (UL1557)

- Optimized for over 10 kHz Switching Frequency

- 500 V FRFET MOSFET 3-Phase Inverter with Gate Drivers and Protection

- Built-In Bootstrap Diodes Simplify PCB Layout

- Separate Open-Source Pins from Low-Side MOSFETs for Three-Phase Current-Sensing

- Active-HIGH Interface, Works with 3.3 / 5 V Logic, Schmitt-trigger Input

- Optimized for Low Electromagnetic Interference

- HVIC Temperature-Sensing Built-In for Temperature Monitoring

- HVIC for Gate Driving and Under-Voltage Protection

- Isolation Rating: 1500 V<sub>rms</sub>/min.

- Moisture Sensitive Level (MSL)3 for SMD

- These Devices are Pb-Free and are RoHS Compliant

# Applications

• 3-Phase Inverter Driver for Small Power AC Motor Drives

## **Related Source**

- AN-9080 FSB50450AS User's Guide for Motion SPM 5 Series

- AN-9082 Motion SPM5 Series Thermal Performance by Contact **Pressure**

# **ON Semiconductor®**

www.onsemi.com

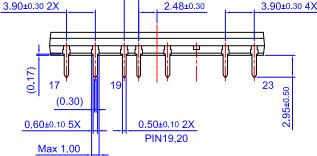

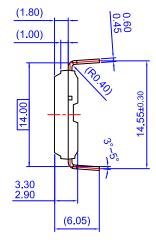

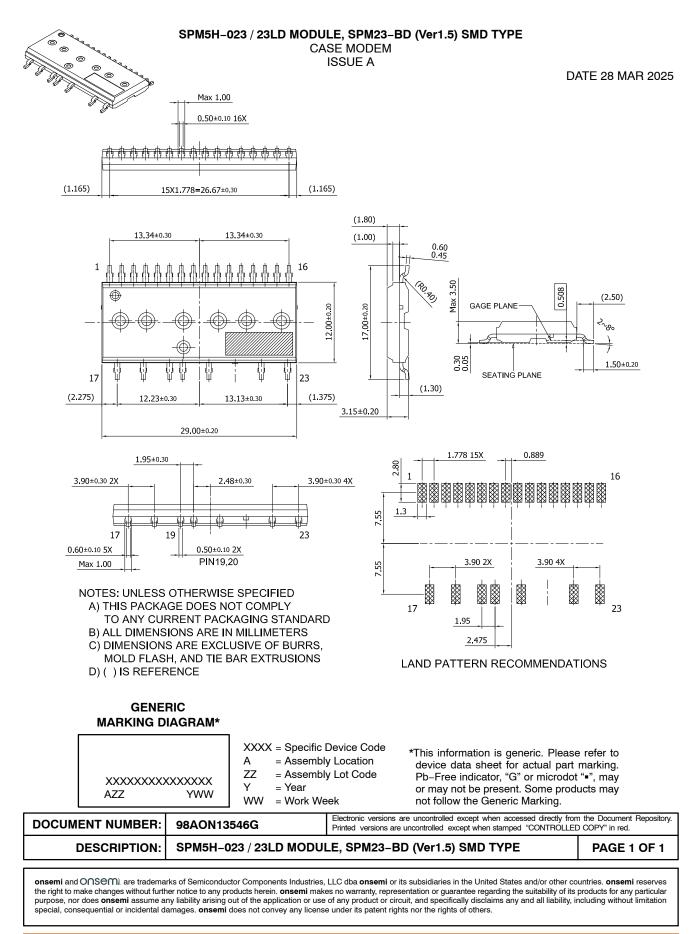

SPM5H-023 / 23LD, PDD S SPM23-BD CASE MODEM

DFOR I SPM5E-023 / 23LD, PDD STD **CASE MODEJ**

## MARKING DIAGRAM

|                                   | 0 | \$Y<br>FSB50250X<br>&Z&K&E&E&E&3                                                                                         |                 |

|-----------------------------------|---|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| \$Y<br>&Z<br>&3<br>&K<br>FSB50250 | x | = ON Semiconduct<br>= Assembly Plant C<br>= Data Code (Year<br>= Lot<br>= Specific Device C<br>$\Rightarrow$ X = B or BS | Code<br>& Week) |

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet

# PACKAGE MARKING AND ORDERING INFORMATION

| Device     | Device Marking | Package   | Packing Type | Reel Size | Quantity |

|------------|----------------|-----------|--------------|-----------|----------|

| FSB50250B  | FSB50250B      | SPM5P-023 | Rail         | NA        | 15       |

| FSB50250BS | FSB50250BS     | SPM5Q-023 | Tape & Reel  | 330 mm    | 450      |

# ABSOLUTE MAXIMUM PATINGS (Ta = 25°C Liplace otherwise poted)

| Symbol             | Parameter                                       | Conditions                                                  | Rating                      | Unit             |

|--------------------|-------------------------------------------------|-------------------------------------------------------------|-----------------------------|------------------|

|                    | ART (Each MOSFET Unless Otherwise Specifi       | ed)                                                         |                             |                  |

| V <sub>DSS</sub>   | Drain-Source Voltage of Each MOSFET             |                                                             | 500                         | V                |

| *I <sub>D 25</sub> | Each MOSFET Drain Current, Continuous           | $T_{C} = 25^{\circ}C$                                       | 1.9                         | А                |

| *I <sub>D 80</sub> | Each MOSFET Drain Current, Continuous           | $T_{C} = 80^{\circ}C$                                       | 1.2                         | А                |

| *I <sub>DP</sub>   | Each MOSFET Drain Current, Peak                 | T <sub>C</sub> = 25°C, PW < 100 μs                          | 5.0                         | A                |

| *I <sub>DRMS</sub> | Each MOSFET Drain Current, Rms                  | T <sub>C</sub> = 80°C, F <sub>PWM</sub> < 20 kHz            | 0.9                         | A <sub>rms</sub> |

| CONTROL PA         | ART (Each HVIC Unless Otherwise Specified)      |                                                             | 25                          |                  |

| V <sub>DD</sub>    | Control Supply Voltage                          | Applied Between V <sub>DD</sub> and COM                     | 20                          | V                |

| $V_{BS}$           | High-side Bias Voltage                          | Applied Between $V_B$ and $V_S$                             | 20                          | V                |

| V <sub>IN</sub>    | Input Signal Voltage                            | Applied Between IN and COM                                  | –0.3 ~ V <sub>DD</sub> +0.3 | V                |

| BOOTSTRAP          | DIODE PART (Each Bootstrap Diode Unless         | Otherwise Specified.)                                       | h h                         |                  |

| V <sub>RRMB</sub>  | Maximum Repetitive Reverse Voltage              | and the set                                                 | 500                         | V                |

| * I <sub>FB</sub>  | Forward Current                                 | $T_{C} = 25^{\circ}C$                                       | 0.5                         | А                |

| * I <sub>FPB</sub> | Forward Current (Peak)                          | T <sub>C</sub> = 25°C, Under 1 ms Pulse Width               | 1.5                         | А                |

| THERMAL RE         | ESISTANCE                                       | MART YOUNFOUND                                              |                             |                  |

| $R_{th(j-c)Q}$     | Junction to Case Thermal Resistance<br>(Note 1) | Inverter MOSFET part, (Per Module)                          | 2.6                         | °C/W             |

| TOTAL SYST         | EM                                              | NIFF                                                        |                             |                  |

| Τ <sub>J</sub>     | Operating Junction Temperature                  | TN                                                          | -40 ~ 150                   | °C               |

| T <sub>STG</sub>   | Storage Temperature                             |                                                             | -40 ~ 125                   | °C               |

| V <sub>ISO</sub>   | Isolation Voltage                               | 60 Hz, Sinusoidal, 1 minute,<br>Connection Pins to Heatsink | 1500                        | V <sub>rms</sub> |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

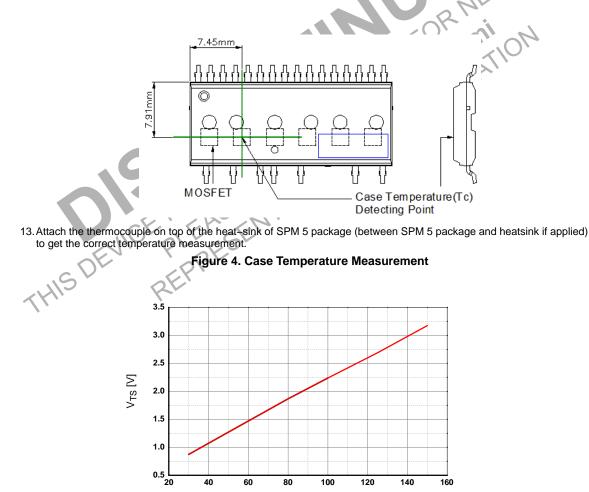

For the Measurement Point of Case Temperature T<sub>C</sub>, Please refer to Figure 4.

Marking "\*" Is Calculation Value or Design Factor.

Using continuously under heavy loads or excessive assembly conditions (e.g. the application of high temperature/ current/ voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/ current/ voltage, etc.) are within the absolute maximum ratings and the operating ranges.

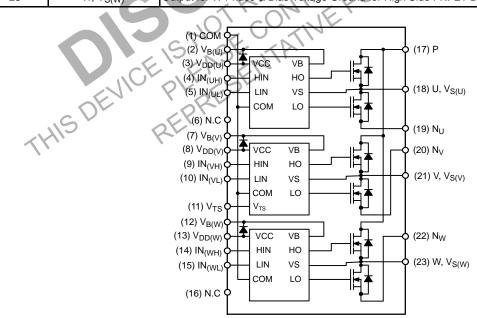

## PIN DESCRIPTION

| Pin No. | Pin Name             | Pin Description                                                      |

|---------|----------------------|----------------------------------------------------------------------|

| 1       | COM                  | IC Common Supply Ground                                              |

| 2       | V <sub>B(U)</sub>    | Bias Voltage for U Phase High Side FRFET Driving                     |

| 3       | V <sub>DD(U)</sub>   | Bias Voltage for U Phase IC and Low Side FRFET Driving               |

| 4       | IN <sub>(UH)</sub>   | Signal Input for U Phase High-side                                   |

| 5       | IN <sub>(UL)</sub>   | Signal Input for U Phase Low-side                                    |

| 6       | N.C                  | N.C                                                                  |

| 7       | V <sub>B(V)</sub>    | Bias Voltage for V Phase High Side FRFET Driving                     |

| 8       | V <sub>DD(V)</sub>   | Bias Voltage for V Phase IC and Low Side FRFET Driving               |

| 9       | IN <sub>(VH)</sub>   | Signal Input for V Phase High-side                                   |

| 10      | IN <sub>(VL)</sub>   | Signal Input for V Phase Low-side                                    |

| 11      | V <sub>TS</sub>      | Output for HVIC Temperature Sensing                                  |

| 12      | V <sub>B(W)</sub>    | Bias Voltage for W Phase High Side FRFET Driving                     |

| 13      | V <sub>DD(W)</sub>   | Bias Voltage for W Phase IC and Low Side FRFET Driving               |

| 14      | IN <sub>(WH)</sub>   | Signal Input for W Phase High-side                                   |

| 15      | IN <sub>(WL)</sub>   | Signal Input for W Phase Low-side                                    |

| 16      | N.C                  | N.C                                                                  |

| 17      | Р                    | Positive DC-Link Input                                               |

| 18      | U, V <sub>S(U)</sub> | Output for U Phase & Bias Voltage Ground for High Side FRFET Driving |

| 19      | NU                   | Negative DC-Link Input for U Phase                                   |

| 20      | N <sub>V</sub>       | Negative DC-Link Input for V Phase                                   |

| 21      | V, V <sub>S(V)</sub> | Output for V Phase & Bias Voltage Ground for High Side FRFET Driving |

| 22      | N <sub>W</sub>       | Negative DC-Link Input for W Phase                                   |

| 23      | W, V <sub>S(W)</sub> | Output for W Phase & Bias Voltage Ground for High Side FRFET Driving |

4. Source Terminal of Each Low–Side MOSFET is Not Connected to Supply Ground or Bias Voltage Ground Inside Motion SPM 5 product. External Connections Should be Made as Indicated in Figure 3.

# Figure 1. Pin Configuration and Internal Block Diagram (Bottom View)

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C, $V_{DD}$ = $V_{BS}$ = 15 V Unless Otherwise Specified)

| Symbol              | Parameter                                             | Test Conditions                                                                                     | Min. | Тур.   | Max.  | Unit |  |  |

|---------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|--------|-------|------|--|--|

| INVERTER I          | NVERTER PART (Each MOSFET Unless Otherwise Specified) |                                                                                                     |      |        |       |      |  |  |

| BV <sub>DSS</sub>   | Drain-Source Breakdown Voltage                        | $V_{IN} = 0 V, I_D = 1 mA (Note 5)$                                                                 | 500  | -      | -     | V    |  |  |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current                       | $V_{IN} = 0 V, V_{DS} = 500 V$                                                                      | -    | -      | 1     | mA   |  |  |

| R <sub>DS(on)</sub> | Static Drain–Source On–Resistance                     | $V_{DD} = V_{BS} = 15$ V, $V_{IN} = 5$ V, $I_D = 0.5$ A                                             | -    | 5.5    | 6.4   | Ω    |  |  |

| V <sub>SD</sub>     | Drain–Source Diode Forward Voltage                    | $V_{DD} = V_{BS} = 15$ V, $V_{IN} = 0$ V, $I_{D} = -0.5$ A                                          | -    | -      | 1.1   | V    |  |  |

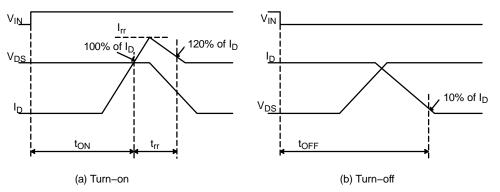

| t <sub>ON</sub>     | Switching Times                                       | $V_{PN} = 300 \text{ V}, V_{DD} = V_{BS} = 15 \text{ V}, I_{D} = 0.5 \text{ A}$                     | -    | 580    | -     | ns   |  |  |

| t <sub>OFF</sub>    |                                                       | $V_{IN} = 0 V \leftrightarrow 5 V$ , Inductive Load L = 3 mH High-<br>and Low-Side MOSFET Switching | -    | 450    | -     | ns   |  |  |

| t <sub>rr</sub>     |                                                       | (Note 6)                                                                                            | -    | 150    | _     | ns   |  |  |

| E <sub>ON</sub>     |                                                       |                                                                                                     | -    | 30     | _     | μJ   |  |  |

| E <sub>OFF</sub>    |                                                       |                                                                                                     | -    | 3      | -     | μJ   |  |  |

| RBSOA               | Reverse–Bias Safe Operating Area                      |                                                                                                     |      | Full S | quare |      |  |  |

| I <sub>QDD</sub>  | Quiescent V <sub>DD</sub> Current          | V <sub>DD</sub> = 15 V, V <sub>IN</sub> = 0 V                                                                          | Applied Between V <sub>DD</sub> and COM                                                                                                                                    |     | -   | 200 | μΑ |

|-------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| I <sub>QBS</sub>  | Quiescent V <sub>BS</sub> Current          | V <sub>BS</sub> = 15 V, V <sub>IN</sub> = 0 V                                                                          | Applied Between<br>V <sub>B(U)</sub> –U, V <sub>B(V)</sub> –V,<br>V <sub>B(W)</sub> –W                                                                                     |     | 1   | 100 | μΑ |

| I <sub>PDD</sub>  | Operating V <sub>DD</sub> Supply           | V <sub>DD</sub> - COM                                                                                                  | $\begin{array}{l} V_{DD}=15 \text{ V,} \\ f_{PWM}=20 \text{ kHz}, \\ Duty=50\%, \text{ Applied to} \\ \text{One PWM Signal Input} \\ \text{for Low-Side} \end{array}$      | -   | _   | 900 | μΑ |

| I <sub>PBS</sub>  | Operating V <sub>BS</sub> Supply Current   | V <sub>B(U)</sub> _V <sub>S(U)</sub> , V <sub>B(V)</sub><br>V <sub>S(V)</sub> , V <sub>B(W)</sub><br>V <sub>S(W)</sub> | $\begin{array}{l} V_{DD}=V_{BS}=15 \text{ V},\\ f_{PWM}=20 \text{ kHz},\\ Duty=50\%, \text{ Applied to}\\ One \text{ PWM Signal Input}\\ \text{for High-Side} \end{array}$ | -   | _   | 800 | μΑ |

| UV <sub>DDD</sub> | Low-Side Undervoltage Protection           | V <sub>DD</sub> Undervoltage Protection Detection Level                                                                |                                                                                                                                                                            | 7.4 | 8.0 | 9.4 | V  |

| UV <sub>DDR</sub> | (Figure 8)                                 | V <sub>DD</sub> Undervoltage Protection Reset Level                                                                    |                                                                                                                                                                            | 8.0 | 8.9 | 9.8 | V  |

| UV <sub>BSD</sub> | High-Side Undervoltage Protection          | V <sub>BS</sub> Undervoltage Prote                                                                                     | ection Detection Level                                                                                                                                                     | 7.4 | 8.0 | 9.4 | V  |

| UV <sub>BSR</sub> | (Figure 9)                                 | V <sub>BS</sub> Undervoltage Protection Reset Level                                                                    |                                                                                                                                                                            | 8.0 | 8.9 | 9.8 | V  |

| V <sub>TS</sub>   | HVIC Temperature sensing voltage<br>output | V <sub>DD</sub> = 15 V, T <sub>HVIC</sub> = 25°                                                                        | °C (Note 8)                                                                                                                                                                | 600 | 790 | 980 | ۳۱ |

| VIH               | ON Threshold Voltage                       | Logic High Level                                                                                                       | Applied between IN and                                                                                                                                                     | -   | -   | 2.9 | V  |

| VIL               | OFF Threshold Voltage                      | Logic Low Level                                                                                                        | СОМ                                                                                                                                                                        | 0.8 | _   | _   | V  |

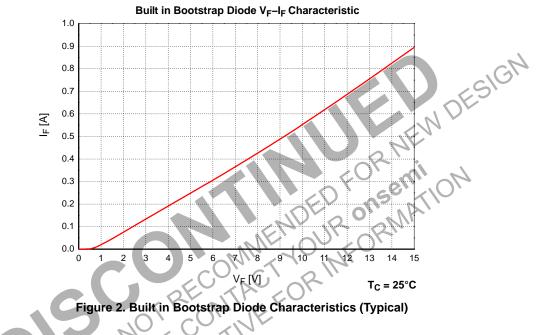

| V <sub>FB</sub>  | Forward Voltage       | I <sub>F</sub> = 0.1 A, T <sub>C</sub> = 25°C (Note 9) | - | 2.5 | - | V  |

|------------------|-----------------------|--------------------------------------------------------|---|-----|---|----|

| t <sub>rrB</sub> | Reverse Recovery Time | $I_{F} = 0.1 \text{ A}, T_{C} = 25^{\circ}\text{C}$    | _ | 80  | - | ns |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### Symbol Parameter Conditions Min. Unit Тур Max. Supply Voltage V VPN Applied between P and N \_ 300 400 $V_{DD}$ 13.5 15.0 16.5 V Control Supply Voltage Applied between V<sub>DD</sub> and COM V High-Side Bias Voltage 13.5 15.0 16.5 VBS Applied between V<sub>B</sub> and V<sub>S</sub> Input ON Threshold Voltage Applied between VIN and COM 3.0 V VIN(ON) VDD \_ VIN(OFF) Input OFF Threshold Voltage 0 0.6 V $V_{DD} = V_{BS} = 13.5 \sim 16.5 \text{ V}, \text{ T}_{J} \le 150^{\circ}\text{C}$ 1.0 t<sub>dead</sub> Blanking Time for Preventing Arm-Short \_ μS 15 PWM Switching Frequency $T_J \le 150^{\circ}C$ kHz fpwm \_ \_

#### **RECOMMENDED OPERATING CONDITION**

#### NOTES:

- BV<sub>DSS</sub> is the Absolute Maximum Voltage Rating Between Drain and Source Terminal of Each MOSFET Inside Motion SPM 5 product. V<sub>PN</sub> Should be Sufficiently Less Than This Value Considering the Effect of the Stray Inductance so that V<sub>DS</sub> Should Not Exceed BV<sub>DSS</sub> in Any Case.

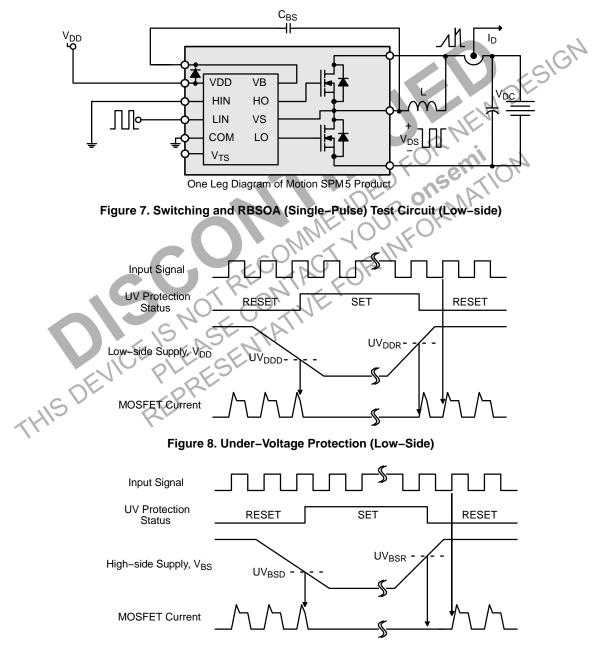

- 6. t<sub>ON</sub> and t<sub>OFF</sub> Include the Propagation Delay Time of the Internal Drive IC. Listed Values are Measured at the Laboratory Test Condition, and They Can be Different According to the Field Applications Due to the Effect of Different Printed Circuit Boards and Wirings. Please see Figure 6 for the Switching Time Definition with the Switching Test Circuit of Figure 7.

- 7. The peak current and voltage of each MOSFET during the switching operation should be included in the Safe Operating Area (SOA). Please see Figure 8 for the RBSOA test circuit that is same as the switching test circuit.

- 8. V<sub>TS</sub> is only for sensing temperature of module and cannot shutdown MOSFETs automatically.

- 9. Built in bootstrap diode includes around 15  $\Omega$  resistance characteristic. Please refer to Figure 1.

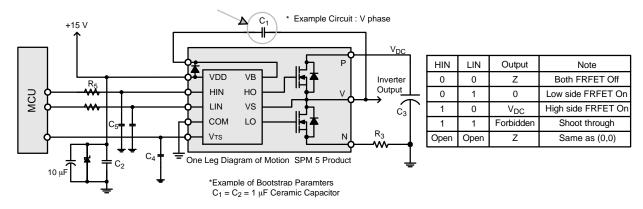

#### These values depend on PWM control algorithm

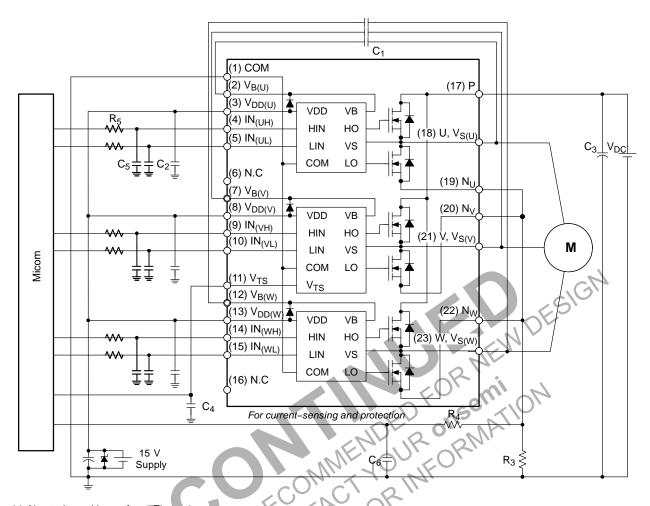

- 10. Parameters for bootstrap circuit elements are dependent on PWM algorithm. For 15 kHz of switching frequency, typical example of parameters is shown above.

- 11. RC-coupling (R<sub>5</sub> and C<sub>5</sub>) and C<sub>4</sub> at each input of Motion SPM 5 product and MCU (Indicated as Dotted Lines) may be used to prevent improper signal due to surge-noise.

- 12. Bold lines should be short and thick in PCB pattern to have small stray inductance of circuit, which results in the reduction of surge-voltage. Bypass capacitors such as C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> should have good high-frequency characteristics to absorb high-frequency ripple-current.

# Figure 3. Recommended MCU Interface and Bootstrap Circuit with Parameters

Figure 5. Temperature Profile of V<sub>TS</sub> (Typical)

T<sub>HVIC</sub> [°C]

Figure 6. Switching Time Definitions

14. About pin position, refer to Figure 1.

- 15. RC-coupling (R5 and C5, R4 and C6) and C4 at each input of Motion SPM 5 product and MCU are useful to prevent improper input signal caused by surge-noise.

- 16. The voltage-drop across R<sub>3</sub> affects the low-side switching performance and the bootstrap characteristics since it is placed between COM and the source terminal of the low-side MOSFET. For this reason, the voltage-drop across R3 should be less than 1 V in the steady-state.

- 17. Ground-wires and output terminals, should be thick and short in order to avoid surge-voltage and malfunction of HVIC.

- 18. All the filter capacitors should be connected close to Motion SPM 5 product, and they should have good characteristics for rejecting high-frequency ripple current. THISDE

#### Figure 10. Example of Application Circuit

SPM is a registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

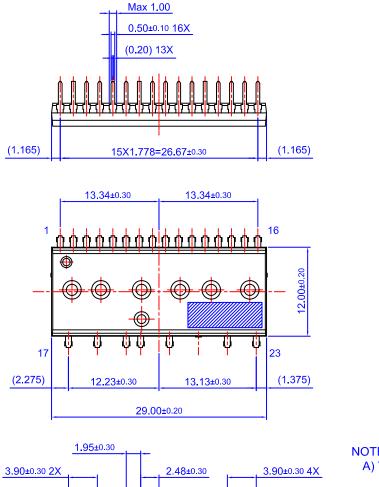

#### SPM5E-023 / 23LD, PDD STD, FULL PACK, DIP TYPE CASE MODEJ ISSUE O

DATE 31 JAN 2017

NOTES: UNLESS OTHERWISE SPECIFIED A) THIS PACKAGE DOES NOT COMPLY TO ANY CURRENT PACKAGING STANDARD B) ALL DIMENSIONS ARE IN MILLIMETERS C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS D) ( ) IS REFERENCE

| DOCUMENT NUMBER:                                                                     | 98AON13543G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DESCRIPTION: SPM5E-023 / 23LD, PDD STD, FULL PACK, DIP TYPE PAGE 1                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                  |  |  |  |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume as | onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or the rights of others. |                                                                                                                                                                                  |  |  |  |  |  |

# onsemi

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>