# onsemi

## Buck Regulator 3 A, Constant On Time (COT)

## FAN53730

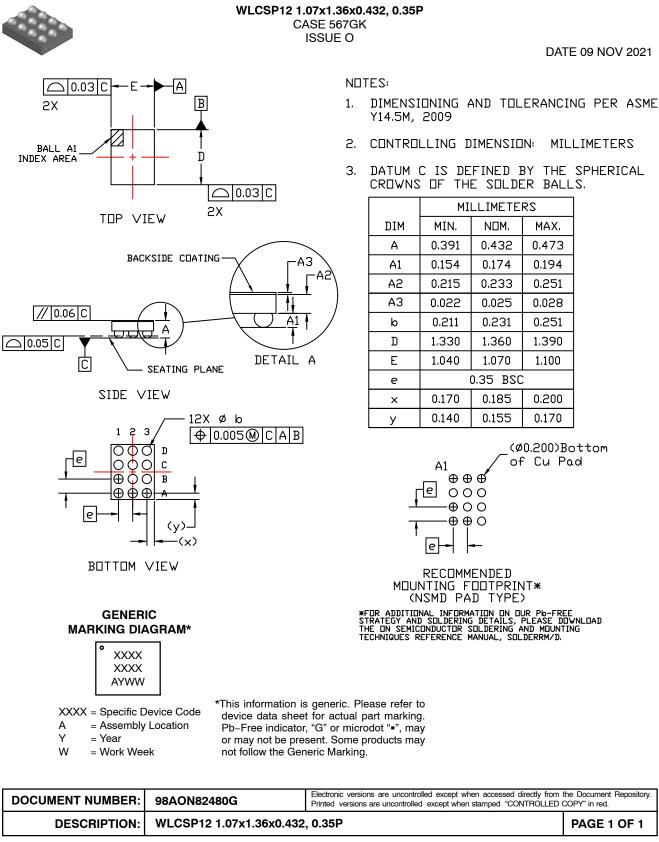

WLCSP12 1.07 x 1.36 x 0.432, 0.35P CASE 567GK

#### Description

The FAN53730 is a constant on time (COT) buck converter that supports a minimum of 3 A load current. The device's COT topology provides the fastest transient recovery and optimal efficiency vs load due to its variable frequency operation.

Two device options are available (see Ordering Information):

- ♦ I<sup>2</sup>C Controlled

- Logic Controlled (pin selectable V<sub>OUT</sub>)

Both options have automatic DCM/CCM mode operation with Forced CCM control.

#### Features

- Input Voltage Range: 2.3 V to 5.5 V

- Output Voltage:

- Programmable from 0.3 V to 2 V

- Pin Selectable Defaults

- Low Quiescent Current: 12 μA

- Internal Soft-Start Limits Input Current During Turn-On

- 2.5 MHz Switching Frequency in Continuous Conduction Operation

- 1.2 V and 1.8 V Logic Compatible

- Fault Protection (Input Under Voltage, Short Circuit, Over Current, and Thermal)

- Power Good Output (PG)

- Forced Continuous Conduction Mode (FCCM)

- Audio Reduction Mode Eliminates Audible Tones Due to Switching

- -40°C to +85°C Ambient Temperature Range

- This is a Pb–Free Device

#### Applications

- LPDDR Memory

- Mobile and Smart Devices

- RF Modules

#### MARKING DIAGRAM

- ZZ = Assembly Lot A = Site Code

- = Site Code = Year

- Y = Year WW = 2 Digit Work Week

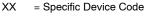

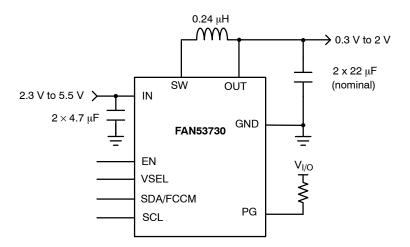

Figure 1. Typical Application Circuit

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

#### **ORDERING INFORMATION**

| Part Number   | Device<br>Option               | Default VSEL                     | l <sup>2</sup> C Address | Ambient<br>Temperature<br>Range | Package                                               | Shipping <sup>†</sup> | Specific<br>Device<br>Code |

|---------------|--------------------------------|----------------------------------|--------------------------|---------------------------------|-------------------------------------------------------|-----------------------|----------------------------|

| FAN53730UCX   | l <sup>2</sup> C<br>Controlled | VSET1 = 1.00 V<br>VSET2 = 1.05 V | 7 h'20                   | –40°C to 85°C                   | 1.07 mm × 1.36 mm,<br>0.35 mm pitch,<br>12–bump WLCSP | n pitch, Tape & Reel  | MH                         |

| FAN53730UC01X | I <sup>2</sup> C<br>Controlled | VSET1 = 1.00 V<br>VSET2 = 1.05 V | 7 h'22                   |                                 |                                                       | 3000 /<br>Tape & Reel | WE                         |

| FAN53730UC02X | I <sup>2</sup> C<br>Controlled | VSET1 = 1.00 V<br>VSET2 = 1.05 V | 7 h'30                   |                                 |                                                       | 3000 /<br>Tape & Reel | WF                         |

| TBD           | Logic<br>Controlled            | VSET1 = TBD<br>VSET2 = TBD       | Not Applicable           |                                 |                                                       | TBD /<br>Tape & Reel  | TBD                        |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

NOTE: Additional options available upon request.

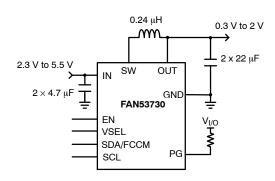

#### **PIN CONFIGURATION**

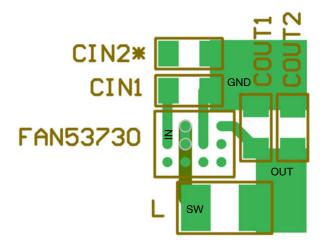

Figure 2. Bumps Facing Down

#### **PIN DEFINITIONS**

| Pin #  | Name     | Description                                                                                                                                                                                                                   |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | SDA/FCCM | SDA I/O in I <sup>2</sup> C controlled device. In the logic controlled device this pin is the FCCM control. Connect to $V_{IN}$ to force continuous conduction at all loads. Connect to GND for variable frequency operation. |

| A2, A3 | IN       | Input voltage connection. Connect to a 2.3 V to 5.5 V input supply.                                                                                                                                                           |

| B1     | SCL      | SCL input in I <sup>2</sup> C controlled device. In the logic controlled device this pin is unused and should connect to GND.                                                                                                 |

| B2, B3 | SW       | Device switching node. Connect to inductor.                                                                                                                                                                                   |

| C1     | VSEL     | Voltage select input. Drive VSEL low to select VSET1. Drive VSEL high to select VSET2.                                                                                                                                        |

| C2, C3 | GND      | Ground connection                                                                                                                                                                                                             |

| D1     | PG       | Power good output. PG goes open drain when V <sub>OUT</sub> is in regulation (I <sup>2</sup> C device can change polarity of PG).                                                                                             |

| D2     | EN       | Device logic high enable input. Drive EN high to enable the device. I <sup>2</sup> C bus remains active when EN is low.                                                                                                       |

| D3     | OUT      | Output voltage sense input. Connect to positive terminal of output capacitor.                                                                                                                                                 |

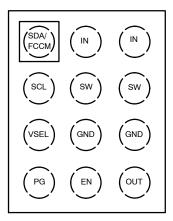

#### **BLOCK DIAGRAM**

Figure 3. Simplified Block Diagram

#### MAXIMUM RATINGS

| Symbol                     | Parameter                             | Condition            | Min  | Тур  | Max                                                                                                                                         | Unit |

|----------------------------|---------------------------------------|----------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>IN</sub>            | Input Voltage                         |                      | -0.3 | -    | 6.0                                                                                                                                         | V    |

| V <sub>SW</sub>            | Voltage on SW Pin                     |                      | -0.3 | -    | V <sub>IN</sub> + 0.3                                                                                                                       | V    |

| V <sub>OUT</sub>           | Output Voltage                        |                      | -0.3 | -    | V <sub>IN</sub> + 0.3                                                                                                                       | V    |

| V <sub>EN</sub>            | Enable Input Voltage                  |                      | -0.3 | -    | V <sub>IN</sub> + 0.3                                                                                                                       | V    |

| $V_{SCL}$ , $V_{SDA/FCCM}$ | SCL, SDA/FCCM Voltage                 |                      | -0.3 | -    | V <sub>IN</sub> + 0.3                                                                                                                       | V    |

| V <sub>SEL</sub>           | Voltage Select Input voltage          |                      | -0.3 | -    | V <sub>IN</sub> + 0.3                                                                                                                       | V    |

| V <sub>PG</sub>            | Power Good Output Voltage             |                      | -0.3 | -    | V <sub>IN</sub> + 0.3                                                                                                                       | V    |

| ESD                        | Electrostatic Discharge               | Human Body Model     | _    | 2.0  | -                                                                                                                                           | kV   |

|                            | Protection Level                      | Charged Device Model | -    | 1000 | $\begin{array}{c} V_{IN} + 0.3 \\ V_{IN} + 0.3 \end{array}$ | V    |

| TJ                         | Junction Temperature                  |                      | -40  | -    | +150                                                                                                                                        | °C   |

| T <sub>STG</sub>           | Storage Temperature                   |                      | -65  | -    | +150                                                                                                                                        | °C   |

| ΤL                         | Soldering Temperature<br>(10 Seconds) |                      | -    | -    | +260                                                                                                                                        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### THERMAL PROPERTIES

Thermal resistance is a function of application and board layout. Theta JA is based on a 2s2p with and without via–in–pad center bump vias in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature TJ(max) at a given ambient temperature  $T_A$ .

| Symbol        | Parameter                                 | Conditions                                      | Min | Тур | Max | Unit |

|---------------|-------------------------------------------|-------------------------------------------------|-----|-----|-----|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal<br>Resistance | 2S2P w/o via-in-pad<br>PCB @ 0.5 W Dissipation  | -   | 130 | -   | °C/W |

| $\theta_{JA}$ | Junction-to-Board Thermal<br>Resistance   | 2S2P with via-in-pad<br>PCB @ 0.5 W Dissipation | -   | 50  | -   | °C/W |

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                                   | Conditions                                                                                                                                      | Min  | Тур  | Max  | Unit |

|------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>  | Input Voltage Range                         |                                                                                                                                                 | 2.3  | -    | 5.5  | V    |

| V <sub>OUT</sub> | Output Voltage Range                        |                                                                                                                                                 | 0.3  | -    | 2    | V    |

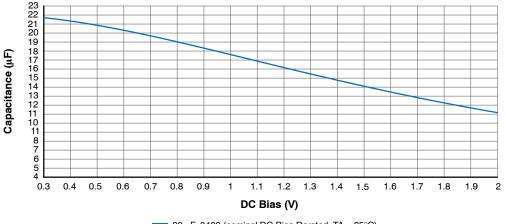

| L                | Inductor (Nominal Value)                    |                                                                                                                                                 | -20% | 0.24 | +20% | μH   |

| C <sub>IN</sub>  | Input Capacitor                             |                                                                                                                                                 | -    | 4.7  | -    | μF   |

| C <sub>OUT</sub> | Output Capacitor<br>(Typical Derated Value) | $\begin{array}{l} C_{OUT} = 2 \times 22 \; \mu \text{F} \; (0402), \\ V_{OUT} = 1 \; \text{V}, \; \text{DC} \; \text{bias derated} \end{array}$ | -20% | 36   | -    | μF   |

| T <sub>A</sub>   | Ambient Temperature Range                   |                                                                                                                                                 | -40  | -    | +85  | °C   |

| Т <sub>Ј</sub>   | Junction Temperature                        |                                                                                                                                                 | -40  | -    | +125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

Minimum and maximum values are at 2.3 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, 0.3 V  $\leq$  V<sub>OUT</sub>  $\leq$  2 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, V<sub>IN</sub> = 3.8 V, V<sub>OUT</sub> = 1.0 V (Note 1, Note 2)

| Symbol                 | Parameter                                                                | Test Condition             | Min   | Тур  | Max | Unit |

|------------------------|--------------------------------------------------------------------------|----------------------------|-------|------|-----|------|

| GENERAL                |                                                                          |                            |       | -    |     | -    |

| R <sub>PD</sub>        | Output Discharge Resistance                                              | EN = Low                   | 72    | 93   | 131 | Ω    |

| I <sub>OUT_SENSE</sub> | OUT Sense Input Leakage Current                                          | V <sub>OUT</sub> = 1 V     | -     | -    | 1   | μA   |

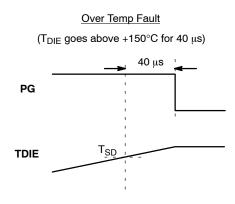

| T <sub>SD</sub>        | Thermal Shutdown                                                         | Die Temperature Rising     | -     | 150  | -   | °C   |

| T <sub>SD_HYST</sub>   | Thermal Shutdown Hysteresis                                              |                            | -     | 30   | -   | °C   |

| f <sub>CLK</sub>       | Fault Clock Frequency                                                    |                            | 450   | 500  | 550 | kHz  |

| R <sub>PG</sub>        | PG Output Pull-down                                                      |                            | -     | -    | 133 | Ω    |

| V <sub>PG_TH</sub>     | V <sub>OUT</sub> Rising Threshold for PG Going<br>Open Drain, PG_POL = 1 | V <sub>OUT</sub> = 0.3 V   | -     | 93   | -   | %    |

| I <sub>PG_POL</sub>    | PG Leakage Current                                                       | EN = Low, $V_{PG}$ = 5.5 V | -     | 0.01 | -   | μA   |

| I <sub>EN_L</sub>      | EN Input Leakage Current                                                 | EN = 5.5 V                 | -     | 0.01 | -   | μΑ   |

| V <sub>IH</sub>        | Logic High Voltage (VSEL, EN, FCCM)                                      |                            | 0.825 | -    | -   | V    |

| V <sub>IL</sub>        | Logic Low Voltage (VSEL, EN, FCCM)                                       |                            | -     | -    | 0.4 | V    |

#### V<sub>OUT</sub> ACCURACY

| V <sub>OUT_ACC</sub> | ACC Output Voltage Accuracy | $V_{OUT}$ < 1 V, No Load, $V_{IN} \geq V_{OUT}$ + 1.5 V          | -20 | - | 9   | mV |

|----------------------|-----------------------------|------------------------------------------------------------------|-----|---|-----|----|

|                      |                             | $V_{OUT} \geq$ 1 V, No Load, $V_{IN} \geq V_{OUT}$ + 1.5 V       | -16 | - | 12  | mV |

|                      |                             | $V_{OUT}$ < 1 V, FCCM, No Load, $V_{IN} \geq V_{OUT}$ + 1.5 V    | -14 | - | 13  | mV |

|                      |                             | $V_{OUT} \geq 1$ V, FCCM, No Load, $V_{IN} \geq V_{OUT}$ + 1.5 V | -1  | - | 1.1 | %  |

#### **OPERATING CURRENT**

| I <sub>SHDN</sub>     | Shutdown Supply Current | I <sup>2</sup> C Controlled device, EN = Low,<br>SDA = SCL = 1.2 V | - | 1.5  | 3.5  | μΑ |

|-----------------------|-------------------------|--------------------------------------------------------------------|---|------|------|----|

| I <sub>SHDN</sub>     | Shutdown Supply Current | Logic Controlled device, EN = Low                                  | - | 1.5  | 3.5  | μA |

| I <sub>Q_ACTIVE</sub> | Active Supply Current   | V <sub>OUT</sub> = 1 V, EN = High, No Load,<br>No Switching        | - | 12.8 | 19.3 | μΑ |

#### CURRENT LIMIT

| IVALLEY              | Valley Current Limit   | V <sub>OUT</sub> = 1 V, [VAL_ILIM] = 1 | 3.5 | 4.2 | 4.8 | А  |

|----------------------|------------------------|----------------------------------------|-----|-----|-----|----|

| IVALLEY              | Valley Current Limit   | V <sub>OUT</sub> = 1 V, [VAL_ILIM] = 0 | 1.9 | 2.3 | 2.6 | А  |

| I <sub>LIM_NEG</sub> | Negative Current limit |                                        | -   | 1.5 | -   | А  |

| t <sub>SHORT</sub>   | Short-Circuit Timeout  | V <sub>OUT</sub> < 0.1 V (Note 3)      | -   | 40  | -   | μs |

#### ELECTRICAL CHARACTERISTICS (continued)

Minimum and maximum values are at 2.3 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, 0.3 V  $\leq$  V<sub>OUT</sub>  $\leq$  2 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, V<sub>IN</sub> = 3.8 V, V<sub>OUT</sub> = 1.0 V (Note 1, Note 2)

| Symbol                     | Parameter                                          | Test Condition                                  | Min   | Тур | Max  | Unit |

|----------------------------|----------------------------------------------------|-------------------------------------------------|-------|-----|------|------|

| CURRENT LIN                | IIT                                                | ·                                               | •     |     | -    | •    |

| V <sub>SHORT</sub>         | Output Short Circuit Threshold                     | t < t <sub>SHORT</sub>                          | 68    | 140 | 212  | mV   |

| SWITCH ON T                | IME                                                | •                                               |       |     | •    |      |

| t <sub>ON</sub>            | High side switch on-time                           | V <sub>IN</sub> = 2.3 V, V <sub>OUT</sub> = 1 V | 181   | 196 | 202  | ns   |

| t <sub>ON</sub>            | High side switch on-time                           | V <sub>IN</sub> = 3.8 V, V <sub>OUT</sub> = 1 V | 104   | 113 | 116  | ns   |

| t <sub>ON</sub>            | High side switch on-time                           | V <sub>IN</sub> = 5.5 V, V <sub>OUT</sub> = 1 V | 70    | 78  | 80   | ns   |

| UVLO DETEC                 | TION                                               | -                                               |       |     |      | -    |

| V <sub>UVLO_R</sub>        | Under-Voltage Lockout Threshold                    | Rising V <sub>IN</sub>                          | -     | -   | 2.3  | V    |

| V <sub>UVLO F</sub>        | Under-Voltage Lockout Threshold                    | Falling V <sub>IN</sub>                         | 2.1   | -   | -    | V    |

| V <sub>UVLO H</sub>        | UVLO Hysteresis                                    |                                                 | -     | 100 | -    | mV   |

| POWER MOSE                 | ETS RDSON                                          |                                                 |       |     |      | •    |

| RDS <sub>ON_LOW</sub>      | Low Side NMOS Resistance<br>(Ball-to-Ball)         | $V_{IN} = V_{GS} = 3.8 \text{ V}$               | -     | 23  | -    | mΩ   |

| RDS <sub>ON_HIGH</sub>     | High Side NMOS Resistance<br>(Ball-to-Ball)        | V <sub>IN</sub> = V <sub>GS</sub> = 3.8 V       | _     | 33  | -    | mΩ   |

| AUDIO MODE                 |                                                    |                                                 |       |     |      |      |

| R <sub>AUDIO</sub>         | Pull-down FET for Output Discharge                 | V <sub>IN</sub> = 3.8 V                         | -     | 5   | -    | Ω    |

| t <sub>AUDIO</sub>         | Maximum Dead Time in Audio Mode                    | [ARM_TO] = 0                                    | -     | 25  | -    | μs   |

| t <sub>AUDIO</sub>         | Maximum Dead Time in Audio Mode                    | [ARM_TO] = 1                                    | -     | 40  | _    | μs   |

| I <sup>2</sup> C TIMING AN | ND PERFORMANCE – FOR I <sup>2</sup> C VERSIC       | ON (Note 4)                                     |       |     |      |      |

| V <sub>IL</sub>            | SDA and SCL Logic Low threshold                    |                                                 | -     | _   | 0.4  | V    |

| V <sub>IH</sub>            | SDA and SCL Logic High threshold                   |                                                 | 0.825 | _   | 5.5  | V    |

| V <sub>OL</sub>            | SDA Logic Low Output                               | 3 mA sink                                       | -     | -   | 0.4  | V    |

| f <sub>SCL</sub>           | SCL Clock Frequency                                | Fast Mode Plus                                  | -     | -   | 1000 | kHz  |

| t <sub>BUF</sub>           | Bus-Free Time Between STOP and<br>START Conditions | Fast Mode Plus                                  | 0.5   | _   | -    | μs   |

| t <sub>HD; STA</sub>       | START or Repeated<br>START Hold Time               | Fast Mode Plus                                  | 260   | _   | -    | ns   |

| t <sub>LOW</sub>           | SCL LOW Period                                     | Fast Mode Plus                                  | 0.5   | -   | -    | μs   |

| t <sub>HIGH</sub>          | SCL HIGH Period                                    | Fast Mode Plus                                  | 260   | -   | -    | ns   |

| t <sub>R</sub>             | SDA and SCL Rise Time                              | Fast Mode Plus                                  | -     | _   | 120  | ns   |

| t <sub>F</sub>             | SDA and SCL Fall Time                              | Fast Mode Plus, V <sub>DD</sub> = 1.8 V         | 6.55  | _   | 120  | ns   |

| t <sub>SU; STO</sub>       | Stop Condition Setup Time                          | Fast Mode Plus                                  | 260   | -   | -    | ns   |

| Cl                         | SDA and SCL Input Capacitance                      |                                                 | _     | -   | 10   | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

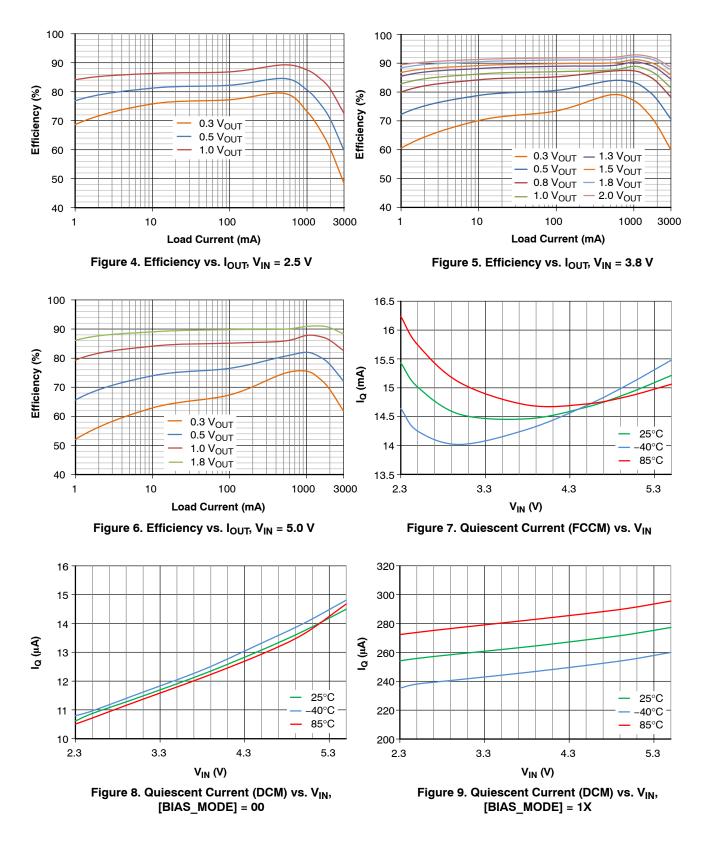

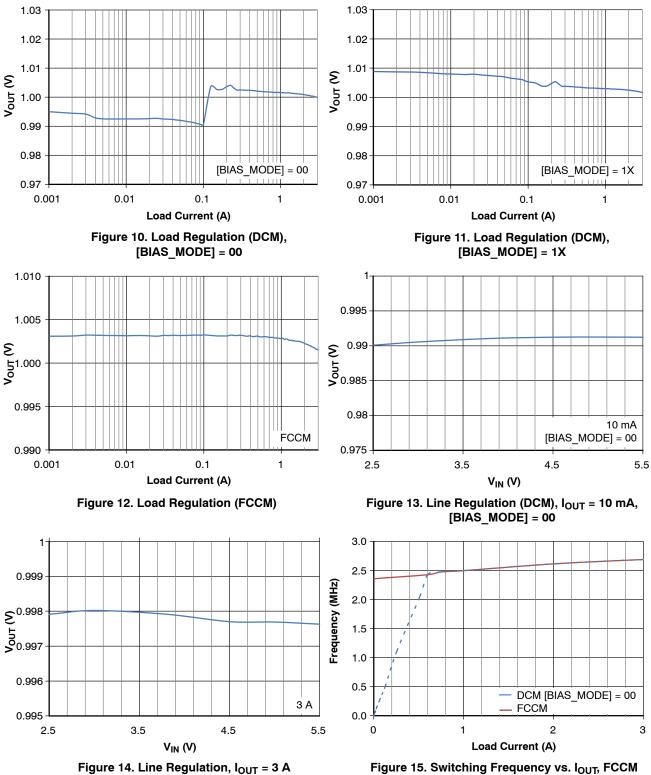

1. Refer to Typical Characteristics waveforms/graphs for closed loop data and variation with input supply and temperature.

2. Electrical Characteristics reflects open loop steady state data. System Characteristics reflects both steady state and dynamic close loop data associated with the recommended external components.

3. Short-Circuit timeout is the time after V<sub>OUT</sub> falls below V<sub>SHORT</sub> to when the FAN53730 is placed into the Fault state.

4. Guaranteed by Design. Characterized on the ATE or Bench.

#### SYSTEM CHARACTERISTICS

System Characteristics reflects both steady state and dynamic closed loop data associated with the recommended external components. They are verified during Application Validation and are not performed in production testing. Recommended operating conditions, unless otherwise noted are 2.3 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, 0.3 V  $\leq$  V<sub>OUT</sub>  $\leq$  2 V, V<sub>IN</sub> = V<sub>OUT</sub> + 1.5 V,  $-40^{\circ}C \leq$  T<sub>A</sub>  $\leq$  85°C. Typical values are based on V<sub>IN</sub> = 3.8 V, V<sub>OUT</sub> = 1.0 V and T<sub>A</sub> = 25°C. System Specifications are based on the Typical Application Circuit, L = 0.24  $\mu$ H, C<sub>IN</sub> = 10  $\mu$ F, C<sub>OUT</sub> = 2 x 22  $\mu$ F (nominal)

| Symbol               | Parameter             | Test Condition                                                                                                              | Min | Тур  | Max  | Unit |

|----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| GENERAL              | •                     | · · ·                                                                                                                       |     |      |      |      |

| IQ <sub>IN_DCM</sub> | DCM Quiescent Current | EN = High, 2.3 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V, V <sub>OUT</sub> = 1 V, [BIAS_MODE] = 00, No Load                     | -   | 12.8 | 19.3 | μΑ   |

|                      |                       | EN = High, [BIAS_MODE] = 1X,<br>No Load                                                                                     | -   | 262  | -    | μΑ   |

| IQ <sub>CCM</sub>    | CCM Quiescent Current | EN = High, FCCM, No Load                                                                                                    | -   | 13.9 | -    | mA   |

| tss                  | Soft-Start            | From EN High to 95% of V <sub>OUT</sub> Target,<br>No Load, [RR_DVS] = 001                                                  | -   | 800  | -    | μs   |

| EFFICIENCY           |                       | -                                                                                                                           | -   |      |      | -    |

| eff                  | Efficiency            | $I_{OUT}$ = 1 mA, $V_{OUT}$ = 1.0 V,<br>$V_{IN}$ = 3.8 V                                                                    | -   | 82.1 | -    | %    |

| eff                  | Efficiency            | $\label{eq:IOUT} \begin{array}{l} I_{OUT} = 10 \text{ mA},  V_{OUT} = 1.0 \text{ V}, \\ V_{IN} = 3.8 \text{ V} \end{array}$ | -   | 86.8 | -    | %    |

| eff                  | Efficiency            | I <sub>OUT</sub> = 100 mA, V <sub>OUT</sub> =1.0 V,<br>V <sub>IN</sub> = 3.8 V                                              | -   | 87.5 | -    | %    |

| eff                  | Efficiency            | I <sub>OUT</sub> = 500 mA, V <sub>OUT</sub> = 1.0 V,<br>V <sub>IN</sub> = 3.8 V                                             | -   | 88.2 | -    | %    |

| eff                  | Efficiency            | I <sub>OUT</sub> = 1000 mA, V <sub>OUT</sub> = 1.0 V,<br>V <sub>IN</sub> = 3.8 V                                            | -   | 89.3 | -    | %    |

| eff                  | Efficiency            | $I_{OUT} = 3000 \text{ mA}, V_{OUT} = 1.0 \text{ V}, V_{IN} = 3.8 \text{ V}$                                                | -   | 83   | -    | %    |

| I <sub>OUT</sub> MAX | ÷                     | ż                                                                                                                           | -   | -    | -    | -    |

| I <sub>OUT_MAX</sub> | Maximum Output Current (Note 6) | $V_{\rm IN}$ from 2.5 V to 5.5 V, $V_{\rm OUT}$ from 0.3 V to 1 V | 3 | - | - | A |

|----------------------|---------------------------------|-------------------------------------------------------------------|---|---|---|---|

|----------------------|---------------------------------|-------------------------------------------------------------------|---|---|---|---|

#### V<sub>OUT</sub> LOAD REGULATION

| V <sub>LO_REG</sub> | Load Regulation       |                                                                                                                   | - | - | 0.6 | %/A |

|---------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|---|---|-----|-----|

| V <sub>LO_REG</sub> | Load Regulation       | I <sub>OUT</sub> = 10 μA to 3 A,<br>V <sub>IN</sub> = 2.5 V to 5.5 V,<br>V <sub>OUT</sub> = 1 V, [BIAS_MODE] = 1X | - | - | 0.4 | %/A |

| V <sub>LO_REG</sub> | Load Regulation (CCM) |                                                                                                                   | - | - | 0.4 | %/A |

#### VOUT LINE REGULATION

| V <sub>LREG_CCM</sub> | Line Regulation 10 µA | $      I_{OUT} = 10 \ \mu A, \ V_{OUT} = 1 \ V, \\ V_{IN} = 2.5 \ V \ to \ 5.5 \ V $ | _ | _ | 0.12 | %/V |

|-----------------------|-----------------------|--------------------------------------------------------------------------------------|---|---|------|-----|

| V <sub>LREG_DCM</sub> | Line Regulation 10 mA | $I_{OUT}$ = 10 mA, $V_{OUT}$ = 1 V,<br>$V_{IN}$ = 2.5 V to 5.5 V                     | - | - | 0.08 | %/V |

| V <sub>LREG_DCM</sub> | Line Regulation 3 A   | $I_{OUT}$ = 3 A, $V_{OUT}$ = 1 V,<br>$V_{IN}$ = 2.5 V to 5.5 V                       | - | - | 0.08 | %/V |

#### SWITCHING

| V <sub>RIPPLE_DCM</sub> | Output Ripple | $V_{IN}$ = 2.3 V to 5.5 V, $I_{OUT}$ = 10 mA, FCCM, $V_{OUT}$ = 1 V              | - | 12 | - | mVpp |

|-------------------------|---------------|----------------------------------------------------------------------------------|---|----|---|------|

| V <sub>RIPPLE_CCM</sub> | Output Ripple | $V_{\text{IN}}$ = 2.3 V to 5.5 V, $I_{\text{OUT}}$ = 3 A, $V_{\text{OUT}}$ = 1 V | - | 6  | - | mVpp |

#### SYSTEM CHARACTERISTICS (continued)

System Characteristics reflects both steady state and dynamic closed loop data associated with the recommended external components. They are verified during Application Validation and are not performed in production testing. Recommended operating conditions, unless otherwise noted are 2.3 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, 0.3 V  $\leq$  V<sub>OUT</sub>  $\leq$  2 V, V<sub>IN</sub> = V<sub>OUT</sub> + 1.5 V,  $-40^{\circ}C \leq$  T<sub>A</sub>  $\leq$  85°C. Typical values are based on V<sub>IN</sub> = 3.8 V, V<sub>OUT</sub> = 1.0 V and T<sub>A</sub> = 25°C. System Specifications are based on the Typical Application Circuit, L = 0.24  $\mu$ H, C<sub>IN</sub> = 10  $\mu$ F, C<sub>OUT</sub> = 2 x 22  $\mu$ F (nominal)

| Symbol           | Parameter                        | Test Condition                                    | Min | Тур | Max | Unit |  |  |  |  |

|------------------|----------------------------------|---------------------------------------------------|-----|-----|-----|------|--|--|--|--|

| f <sub>CCM</sub> | Switching Frequency in CCM Mode  | I <sub>OUT</sub> = 1 A, FCCM                      | -   | 2.5 | -   | MHz  |  |  |  |  |

| CURRENT LIN      | CURRENT LIMIT                    |                                                   |     |     |     |      |  |  |  |  |

| IVALLEY_CL       | Closed Loop Valley Current Limit | $V_{IN} \ge 2.5 \text{ V}, \text{[VAL_ILIM]} = 1$ | -   | 4.6 | -   | А    |  |  |  |  |

|                  | (Note 5)                         | $V_{IN} \ge 2.5 \text{ V}, \text{[VAL_ILIM]} = 0$ | -   | 2.3 | -   | А    |  |  |  |  |

|                  |                                  | V <sub>IN</sub> = 2.3 V, [VAL_ILIM] = 1           | -   | 2.8 | -   | А    |  |  |  |  |

|                  |                                  | V <sub>IN</sub> = 2.3 V, [VAL_ILIM] = 0           | -   | 1.8 | -   | А    |  |  |  |  |

5. Closed loop current limit reflects the maximum control loop error amplifier voltage output, which can mean that the inductor valley current limit has reached its maximum value, or that the control loop has reached a maximum duty cycle.

6. Refer to Fig. 33 Typical Derating Curve for additional  $I_{OUT(MAX)}$  guidance.

#### **TYPICAL CHARACTERISTICS**

#### TYPICAL CHARACTERISTICS (continued)

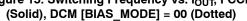

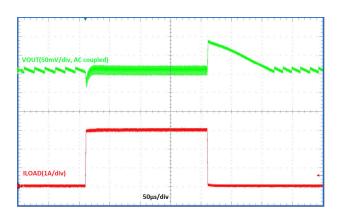

#### TYPICAL CHARACTERISTICS (continued)

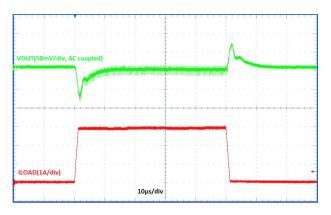

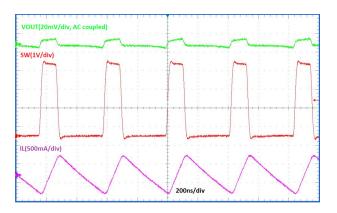

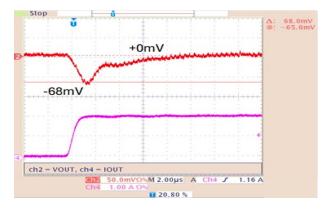

Figure 16. Load Transient (DCM),  $I_{OUT}$  = 10 mA  $\leftrightarrow$  3 A, Trise = Tfall = 1  $\mu s$

Figure 17. Load Transient (FCCM),  $I_{OUT}$  = 10 mA  $\leftrightarrow$  3 A, Trise = Tfall = 1 µs

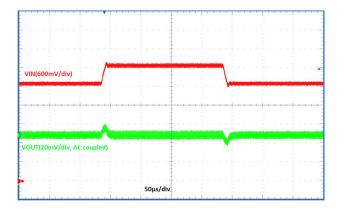

Figure 18. Line Transient,  $V_{IN}$  = 3.3 V  $\leftrightarrow$  3.8 V, Slew Rate = 100 mV/µs,  $I_{OUT}$  = 3 A

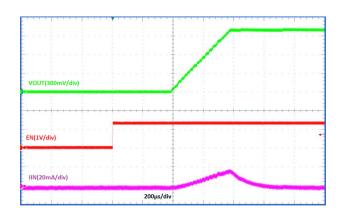

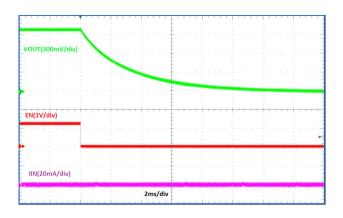

Figure 20. Start-up, No Load

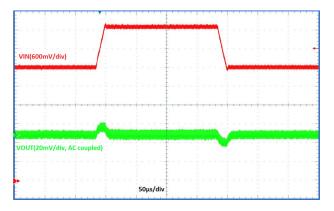

Figure 19. Line Transient, V<sub>IN</sub> = 3.8 V  $\Leftrightarrow$  5 V, Slew Rate = 100 mV/µs, I<sub>OUT</sub> = 3 A

Figure 21. Shut-down, No Load

#### TYPICAL CHARACTERISTICS (continued)

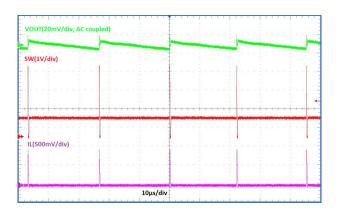

Figure 22. Device Switching (DCM), I<sub>OUT</sub> = 10 mA

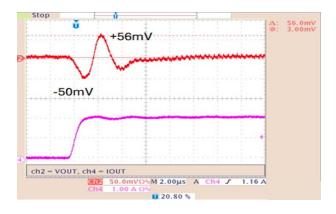

Figure 24. TRANSIENT\_ENHANCEMENT bit enabled, 10 mA  $\leftrightarrow$  2 A, Slew Rate = 2 A/µs

Figure 23. Device Switching (FCCM), I<sub>OUT</sub> = 10 mA

Figure 25. TRANSIENT\_ENHANCEMENT bit disabled, 10 mA  $\Leftrightarrow$  2 A, Slew Rate = 2 A/µs

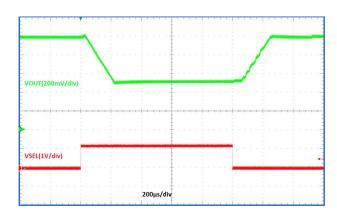

Figure 26. Vsel Toggle, V<sub>OUT</sub> = 1 V to 0.5 V to 1 V, No Load, [DVS\_FCCM] = 1

#### FUNCTIONAL SPECIFICATIONS

#### **Device Options**

**Options and Features**

The FAN53730 has two options:

- 1. A fully programmable I<sup>2</sup>C version.

- 2. A logic controlled fixed output voltage version.

The following table lists the differences between the two:

#### FAN53730 FEATURE BREAKDOWN

| Feature                                | Logic Controlled Device                                             | I <sup>2</sup> C Controlled Device                                        |  |

|----------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Enable (EN)                            | Logic Enable Input Only                                             | Logic Enable Input and Enable Bit                                         |  |

| Thermal Shutdown                       | Yes, 150°C                                                          | Yes, 150°C                                                                |  |

| Under Voltage Lockout (UVLO)           | Yes                                                                 | Yes                                                                       |  |

| Power Good Output (PG)                 | Yes<br>(goes open drain when V <sub>OUT</sub> > 93% of tar-<br>get) | Yes (programmable active high or active low)                              |  |

| Output Pull-Down                       | Yes, In shutdown (100 $\Omega$ )                                    | Yes, In shutdown (100 $\Omega$ ).<br>Can be disabled via I <sup>2</sup> C |  |

| Forced Continuous Conduction (FCCM)    | Yes, via FCCM input                                                 | Yes, via $I^{2}C$ or when VSEL = High and [VSEL_FCCM] = 1                 |  |

| Voltage Select Input (VSEL)            | Yes, VSET1 and VSET2 are fixed by device voltage options            | Yes, VSET1 and VSET2 targets are<br>programmable                          |  |

| Audio Reduction Mode (ARM)             | No (disabled)                                                       | Yes, can be enabled via I <sup>2</sup> C                                  |  |

| Valley Current Limit                   | Fixed at 4.6 A (typ)                                                | Programmable to 4.6 A or 2.3 A to accommodate different sized inductors   |  |

| Dynamic Voltage Scaling                | Yes                                                                 | Yes, 8 programmable slew rates.<br>Can be disabled via I <sup>2</sup> C   |  |

| Low Power Mode (PFM) During Light Load | Yes                                                                 | Yes, can be disabled via I <sup>2</sup> C                                 |  |

| Output Short Fault                     | Yes                                                                 | Yes                                                                       |  |

| Fault Auto-Restart / Shutdown          | Auto-Restart                                                        | Can be programmed to auto-restart after a fault, or go into shutdown      |  |

#### Overview

#### Constant On-Time Operation (COT)

The FAN53730 is a constant on-time (COT) synchronous buck which regulates a 0.3 V to 2 V output voltage from a 2.3 V to 5.5 V input voltage. The COT controller operates as follows:

When the output voltage falls out of regulation the input power switch turns on for the fixed on time ( $t_{ON}$ ) and ramps the inductor current. At the end of  $t_{ON}$  the input switch turns off and the low side synchronous FET turns on and discharges the inductor into the output. If the inductor current reaches 0 before the load pulls the output voltage out of regulation, both the input FET and the synchronous FET will turn off and the device enters an idle state where it will remain until the output falls below the regulation target. Once the output falls below the regulation target the switching action starts again. This results in a variable frequency operation (load dependent) for light currents. At higher load currents (dependent on V<sub>IN</sub>, and V<sub>OUT</sub>) the inductor current will no longer hit 0 before the output voltage falls out of regulation. This results in an approximate constant switching frequency at heavy loads.

#### **On-Time and Maximum Switching Frequency**

The Buck switch on-time ( $t_{ON}$ ) varies with  $V_{IN}$  and  $V_{OUT}$  in order to approximately target a 2.5 MHz switching frequency at  $V_{IN} = 3.8$  V and  $V_{OUT} = 1$  V, when the device is operating in continuous conduction mode. Although this switching frequency will have some variation due to delays and non-linearities in the timing circuit, as well as load dependence effects due to resistive drops that make the effective  $V_{IN}$  lower. Typical CCM frequency variation is shown in the typical operating characteristic graphs.

#### Efficiency

The load dependent switching frequency allows the buck converter to only switch as necessary to keep the load in regulation. This provides for an optimum efficiency response vs load, as the light load switching losses are minimized. When forced CCM (FCCM) is enabled the light load efficiency will be drastically reduced due to increased switching losses.

#### Low Power Mode

During low output current conditions the idle state can be very long compared to the on and off times. During these conditions (typically for  $I_{OUT} < 2$  mA), the FAN53730 will enter a low power state where the device is shutdown during the idle period. This results in low quiescent current.

#### Enable Input

The Enable input (EN) is an active high device enable. When EN is driven low the FAN53730 is in a low power shutdown mode. When driven high the device is in the active state and the output is regulating at its target voltage. For the I<sup>2</sup>C controlled device, the EN input must be high and the ENABLE (REG 06h[0]) bit set to 1 to enable the device.

In the shutdown state, the output pull-down (typically 100  $\Omega$ ) is active and V<sub>OUT</sub> will discharge to GND. The l<sup>2</sup>C version has the ability to disable the active pull-down. The EN input is a high impedance input and should not be left floating.

#### Soft-Start

The FAN53730 incorporates a soft-start which ramps the output from 0 to the target voltage during turn-on. This will limit the high input in-rush current during start-up. The soft-start ramp uses the same ramp as the DVS, but soft-start cannot be disabled using the DVS\_EN (Reg 06h [4]) bit. The default start-up ramp time is set to 4  $\mu$ s per step which results in a soft-start ramp time of typically 400  $\mu$ s with V<sub>OUT</sub> = 1 V and no load. This is in addition to approximately 400  $\mu$ s of initialization time for the bias and reference to wake-up.

Additionally, the device will always start–up in DCM mode until the  $V_{OUT}$  ramp is done, even if the part is set for FCCM.

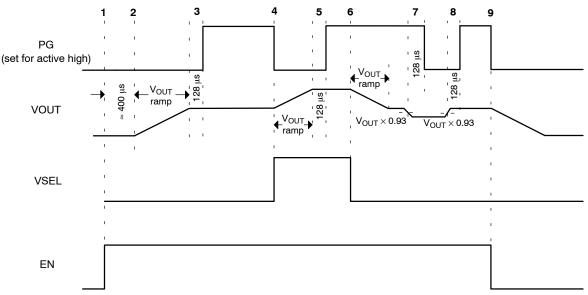

#### **Power Good**

#### Power Good Output

Power Good (PG) is an open drain output which is active when  $V_{OUT}$  rises above 93% of the regulation target and when the  $V_{OUT}$  ramp has completed. PG will remain active as long as: the output is enabled,  $V_{OUT}$  is above 93% of the  $V_{OUT}$  target, and no faults are detected (PG is inactive in the FAULT state). The following figure details the operation of PG when set for active high operation.

- 1. EN goes high and the bias and reference are enabled.

- 2. After the 400  $\mu$ s start-up delay, V<sub>OUT</sub> begins ramping to the target voltage. During this time PG is low.

- 3. When the V<sub>OUT</sub> ramp stops and V<sub>OUT</sub> is higher than 93% of the target, a 128  $\mu$ s de-glitch timer starts If V<sub>OUT</sub> remains above 93% of the target voltage during the de-glitch timer, PG is pulled high.

- 4. When a voltage change occurs which forces V<sub>OUT</sub> to a higher level, PG goes low.

- 5. After the  $V_{OUT}$  ramp completes and the 128 µs de-glitch timer expires, PG goes high.

- 6. When  $V_{OUT}$  is set to a new lower voltage, PG remains high because  $V_{OUT}$  is above 93% of the new target voltage.

- 7. If  $V_{OUT}$  is forced below 93% of the target voltage for  $t > 128 \mu s$  (or if any fault occurs PG will pull-low).

- 8. PG will go high again if the condition which forced  $V_{OUT}$  to drop is removed and  $V_{OUT}$  again rises above 93% of the target output voltage (after 128 µs de–glitch timer expires).

- 9. When enable is brought low, the PG output will pull low immediately.

During a fault condition, PG will pull low after the fault passes the de–glitch time. This can make PG inactive sooner than the 128  $\mu$ s de–glitch time (see below).

#### Figure 27. PG Operation

Figure 30. UVLO Fault

#### Power Good Polarity

# The PG polarity bit, PG\_POL (Reg 03h [0]), sets the active state of the power good output. By default, the PG output will go open drain (externally pulled high) in the active state. When PG\_POL is set to 0, the PG output will pull low in the active state.

#### Power Good Bit

The POWER\_GOOD (Reg 01h [5] bit sets to 1 when the PG output is in it's active state.

#### **Output Pull-Down**

#### Output Pull-Down

During shutdown and fault timeout, the output has a 100  $\Omega$  pull-down. The pull-down resistor can be disabled via OUT\_DISCHARGE (Reg06h[3]).

#### UVLO

#### UVLO Rising

The Under Voltage Lockout (UVLO) holds the device in shutdown until  $V_{IN}$  rises above the UVLO rising threshold.

#### UVLO Falling

If  $V_{IN}$  falls below the UVLO falling threshold, the FAN53730 will trigger a UVLO event and shutdown.

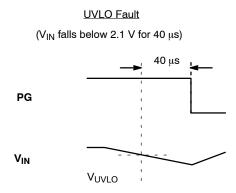

Output Short Fault

(V<sub>OUT</sub> is pulled below 100 mV for 40  $\mu$ s)

Figure 29. Output Short Fault

Figure 31. Over Temperature Fault

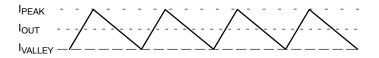

#### Valley Current Limit

#### Valley Current Limit

In CCM operation the FAN53730 will regulate the valley of the inductor current in order to keep  $V_{OUT}$  at its target voltage. However, there is a maximum valley inductor current capability (I<sub>VALLEY</sub>) allowed in the FAN53730's power path. When I<sub>OUT</sub> increases to the point where the inductor valley current reaches I<sub>VALLEY</sub>, the FAN53730's control loop will be clamped at this valley current limit threshold and will no longer be able to regulate V<sub>OUT</sub> at the target voltage. When this happens V<sub>OUT</sub> will tend to drop out. The maximum output current from the FAN53730 is approximately:

$$I_{OUT\_MAX} = I_{VALLEY} + (V_{IN} - V_{OUT})/(2L) \times t_{ON}$$

(eq. 1)

where  $I_{VALLEY}$  is the valley current limit threshold. For the logic controlled device  $I_{VALLEY}$  is fixed at VAL\_ILIM (Reg 03h [0]) = 1. For the I<sup>2</sup>C controlled device VAL\_ILIM is programmable.

For inductor selection, typically the peak inductor current is required. Keep in mind that the peak inductor current will typically be 20% to 30% higher than the valley current.

$I_{OUT MAX} = I_{VALLEY} + (V_{IN} - V_{OUT}) \times t_{ON}/(2 \times L)$  $I_{\text{PEAK}} = I_{\text{OUT}} + (V_{\text{IN}} - V_{\text{OUT}}) \times t_{\text{ON}}/(2 \times L)$

For example:

$V_{OUT}$  = 1 V,  $V_{IN}$  = 3.8 V,  $I_{VALLEY}$  = 4.6 A  $I_{PEAK}$  = 4.6 A + (3.8 V – 1 V)  $\times$  79 ns / 0.24  $\mu H$  = 4.6 A + 0.922 A = 5.52 A

Figure 32. Current Limit Description

#### VOUT= 1.2V VOUT= 1.9V JT=1.1V NT=1.5V NT=1.N

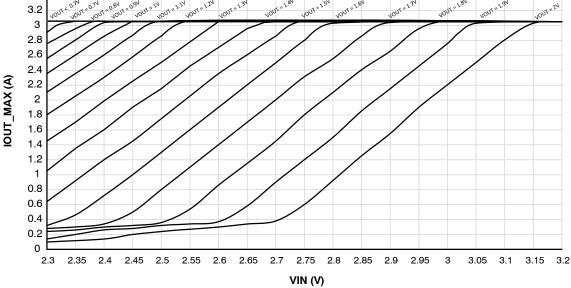

Maximum I<sub>OUT</sub> vs V<sub>IN</sub> and V<sub>OUT</sub> ( $T_A$  = 85°C, Measured on FAN53730 EVM)

Figure 33. Typical Derating Curve vs. VIN, VOUT, ILOAD

#### **Maximum Duty Cycle**

3.4

3.2

For some VIN to VOUT conditions, the maximum output current can be limited by the device minimum off time (toff MIN), which can be up to 100 ns. This places a limitation on the maximum duty cycle the device can attain in CCM. Parameters which effect the required duty cycle are VIN, VOUT, and ILOAD. Typically the FAN53730 can reach a duty cycle of t<sub>ON</sub>/(t<sub>ON</sub> + t<sub>OFF MIN</sub>) at no load. However, as load increases, the effective voltage across the inductor is less, and the required duty cycle increases. This will limit the maximum current below 3 A for some VIN/VOUT configurations. Figure 16 shows a typical derating curve for  $V_{IN}$ ,  $V_{OUT}$ , and Load for  $T_A = 85^{\circ}$ C. This can be used for targeting the maximum load for different  $V_{IN}/V_{OUT}$ configurations.

#### V<sub>OUT</sub> < 0.8 V Operation

If  $V_{OUT} < 0.8V$  (VSET1 or VSET2  $\leq$  code 0x4F), set HIGH BANDWIDTH (Reg 02h [1]) = 0 to avoid low phase margin conditions and possible output voltage oscillations.

#### **Audio Reduction Mode**

#### Audio Reduction Mode

The I<sup>2</sup>C controlled device features an Audio Reduction Mode (ARM). In this mode the switching frequency is kept above a programmed target frequency to eliminate audible noise typically generated in ceramic capacitors with changing electric fields. The ARM is is enabled by setting ARM EN (Reg 06h [5]) = 1. When enabled, the Buck's DCM idle time (dead time between switching events) is monitored. If t<sub>IDLE</sub> reaches the programmed maximum period before the start of a new tON, then the synchronous MOSFET will be forced on long enough to pull VOUT out of regulation and force a new switching cycle. This forced switching period is approximately equal to the ARM time-out period. Programmable timeout periods are 25 µs and 40 µs (see ARM TO (Reg 02h [6])) which result in minimum allowed frequency targets of 1/40 µs = 25 kHz and  $1/25 \ \mu s = 40 \ kHz.$

#### **Dynamic Voltage Scaling**

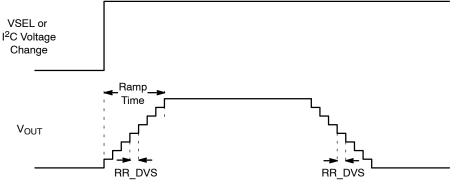

#### Dynamic Voltage Scaling (DVS)

The  $I^2C$  controlled device features a Dynamic Voltage Scaling mode (DVS), which is the controlled slewing of the output voltage (up or down) depending on the direction of the new target output voltage. The slewing of V<sub>OUT</sub> (or ramp

**DVS PROGRAMMABLE TIME PER STEP**

rate) is done by incrementing through each voltage set-point (10 mV/step) between the current target and the new target, until the new target voltage is reached. The time per step is programmable using RR\_DVS (Reg 02h [4:2]). Programmable times per step are shown below:

| DVS_EN | RR_DVS | Time per Step |

|--------|--------|---------------|

| 0      | XXX    | Immediate     |

| 1      | 000    | 2 μs/step     |

| 1      | 001    | 4 μs/step     |

| 1      | 010    | 6 μs/step     |

| 1      | 011    | 8 μs/step     |

| 1      | 100    | 10 μs/step    |

| 1      | 101    | 12 μs/step    |

| 1      | 110    | 14 μs/step    |

| 1      | 111    | 16 μs/step    |

For example: DVS is enabled with RR\_DVS set to 10  $\mu$ s/step. V<sub>OUT</sub> is initially set to 0.5 V and has reached steady state. V<sub>OUT</sub> is then programmed to 1 V. The output will increment from 0.5 V to 1 V through each voltage set-point (10 mV/step) with a pause at each step of 10  $\mu$ s. The total ramp time is given as:

#### $\label{eq:model} \left[ \left( 1000 \ \text{mV} - \ 500 \ \text{mV} \right) / \left( 10 \ \text{mV/step} \right) - 1 \right] \times \ 10 \ \mu\text{s/step} \ = \ 490 \ \mu\text{s}$

During negative transitions (high voltage to lower voltage), if there is a no load condition the output can take a long time to decay to its new target. There is an option to have FCCM turn on during high to low voltage transitions in order to rapidly bring  $V_{OUT}$  down to its new target (see DVS\_FCCM (Reg 02h [5])).

DVS control also applies when the output voltage transitions between VSET1 and VSET2 settings following a VSEL change.

The DVS control can be disabled with the DVS\_EN (Reg 06h [4] bit, in which case any  $V_{OUT}$  transition will immediately change to the new value without a ramp. However, disabling the DVS ramp will not effect the ramp during soft-start. Soft-start will continue to use the programmed DVS setting regardless of the setting of DVS\_EN. Additionally, disabling the DVS ramp with FORCE\_FCCM = 1 will still utilize slew rate control during high to low voltage transitions.

Figure 34. DVS Voltage Ramp

#### **Forced Continuous Conduction Mode**

#### Forced Continuous Conduction Mode (FCCM)

Forced continuous conduction mode will disable the zero cross detection and allow the inductor current to conduct negative during light load conditions. This allows the FAN53730 to switch continuously at all loads. FCCM is beneficial when the DCM switching frequency would cause unwanted noise and interference. During constant frequency operation, the light load efficiency will be much lower compared to variable frequency operation due to higher switching losses in the converter.

The I<sup>2</sup>C controlled device has a dedicated bit for FCCM, FORCE\_CCM (Reg 06h [1]). The logic controlled device has a dedicated pin, called FCCM, for this feature.

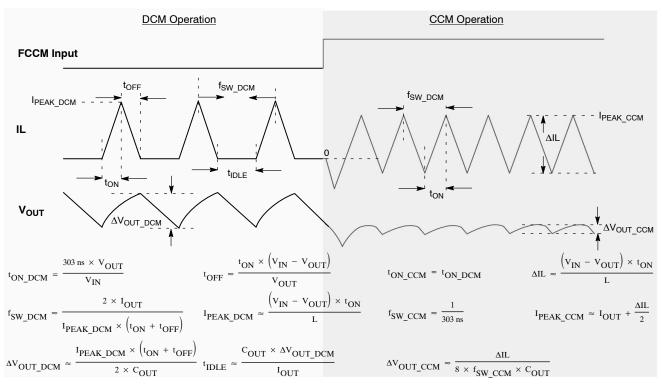

The figure below shows the basic differences between DCM and CCM operation. DCM operation occurs for light

load conditions while CCM operation occurs at heavy load or if the FCCM control is set. In DCM, the device will switch once and then enter the idle state. During the idle state, I<sub>OUT</sub> will continue to discharge the output capacitor. When V<sub>OUT</sub> falls below the regulation target, a new switching cycle is initiated. This causes VOUT to regulate to the bottom of the output voltage ripple, and the average value to be slightly higher at  $V_{OUT} + \Delta V_{OUT} \frac{1}{DCM}/2$ . In CCM operation (either with FCCM high or at heavy loads when V<sub>OUT</sub> falls out of regulation before I<sub>L</sub> reaches zero), the output voltage is regulated via a high gain feedback loop. This causes the average value of V<sub>OUT</sub> to become the regulation target. The parameters listed in the following figure are approximations because they ignore circuit losses and circuit delays, but can give a good idea of the various buck converter operating conditions.

Figure 35. DCM vs. CCM Operation

#### Voltage Select Input

#### Voltage Select (VSEL Input)

VSEL is a logic input which shifts  $V_{OUT}$  between two target voltages. In the logic controlled device, VSEL will shift the target output voltage to the fixed VSET2 level when driven to a logic high. When VSEL is driven to a logic low, the output voltage will shift to the fixed VSET1 target.

In the  $I^2C$  controlled device the VSEL input operates the same except the VSET1 and VSET2 targets are programmable.

#### FCCM Tied to VSEL

Forced continuous conduction mode (FCCM) can be made to follow the VSEL input by enabling the VSEL\_FCCM (Reg 06h [2]) bit. When this bit is set, a logic high at VSEL will change the  $V_{OUT}$  target and will place the buck in FCCM. If this bit is not set, the device remains in auto mode when VSEL is high or low. The FORCE\_CCM bit will always override the VSEL\_FCCM setting. See following table.

#### VSEL AND FCCM

| FORCE_CCM Bit | VSEL_FCCM Bit | VSEL Input | Result                                          |

|---------------|---------------|------------|-------------------------------------------------|

| 0             | Х             | 0          | VOUT = VSET1 target and buck is in Auto DCM/CCM |

| 0             | 0             | 1          | VOUT = VSET2 target and buck is in Auto DCM/CCM |

| 0             | 1             | 1          | VOUT = VSET2 target and buck is in FCCM         |

| 1             | Х             | 0          | VOUT = VSET1 target and buck is in FCCM         |

| 1             | Х             | 1          | VOUT = VSET2 target and buck is in FCCM         |

#### **Bias Modes**

The I<sup>2</sup>C controlled device has three programmable bias mode options for reducing the device's quiescent current. These BIAS\_MODE (Reg 03h [2:1]) bits disable infrequently used internal logic blocks during long SW idle periods, as described below:

#### High Bias Mode

All circuitry active when the part is enabled. Under certain conditions this mode can provide for a faster response to transient disturbances, but at the expense of higher quiescent current.

#### Low Bias Mode

Forces some of the FAN53730's circuitry into shutdown during the DCM idle state. This will greatly reduce no load quiescent current, but under certain conditions can lead to a slower response to a transient event.

#### Ultra Low Bias Mode

This mode is the default selection and will provide the lowest no load quiescent current. The logic version of the device also has the Low Bias Mode option enabled.

#### **Transient Enhancement Bit**

Setting TRANSIENT\_ENHANCEMENT (Reg 03h [4]) bit will force the FAN53730's on-time to double when VOUT drops 30 mV below its regulation target. This allows for a faster recovery of  $V_{OUT}$  during load step events (low to high load). The drawback to using this mode is that during  $V_{OUT}$  recovery, because the on-time and inductor current ripple have doubled, the output can see significant overshoot. Refer to Figures 24 and 25 in Typical Characteristics section.

#### **Protection Features**

#### Fault Protection

The FAN53730 contains four fault modes consisting of:

- V<sub>IN</sub> UVLO Fault

- Current Limit Fault

- Output Short Fault

- Thermal Fault

When any of these faults occur, the FAN53730 is placed in the fault state and is shutdown. By default, the OUT\_DISCHARGE (Reg 06h [3]) bit enables the output discharge resistor during shutdown.

During Current Limit and Output Short faults the converter will auto-restart every 20 ms. This feature can be disabled by setting FAULT\_SHDN (Reg 03h [3]) = 1, and instead the ENABLE bit will be reset to 0 (device remains in shutdown).

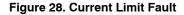

#### Under Voltage Fault

A V<sub>IN</sub> UVLO is detected if V<sub>IN</sub> falls below the UVLO\_F threshold for 40  $\mu$ s. Once this happens, the device stops switching and is placed in the Fault State. In the I<sup>2</sup>C version the UVLO\_FAULT Flag is set. If V<sub>IN</sub> continues to fall past the UVLO threshold and crosses the power on reset threshold, the FAN53730 will immediately shutdown.

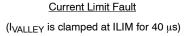

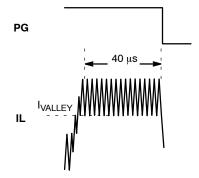

#### Current Limit Timeout

During valley current limit events, when  $I_L$  is clamped at  $I_{VALLEY}$ , the fault clock begins counting. If the fault clock reaches 40 µs of a continuous valley current limit condition, the device is placed into the fault state. During the fault count, if a period occurs without a valley current limit clamp event then the count is reset to 0.

In the I<sup>2</sup>C version, when the part is placed into the fault state, the ILIM\_FAULT flag is set.

#### **Output Short Fault**

If the output voltage falls below 100 mV for 40  $\mu$ s, after the device has reached the active state (power good), the device will detect an output short fault and be forced into the fault state.

In the I<sup>2</sup>C version, when the part is placed into the fault state, the SHORT\_FAULT flag is set.

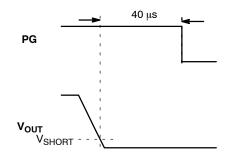

#### Thermal Shutdown

When the die temperature increases due to a high load condition and/or a high ambient temperature, the FAN53730 can reach a thermal fault condition and be placed in the Fault State. In the  $I^2C$  version the OVER\_TEMP\_FAULT flag is set. The device will restart after it cools below the hysteresis level.

#### Operation

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is compatible with Standard, Fast, and Fast Plus I<sup>2</sup>C bus specifications. The SCL line is an input and the SDA line is a bi-directional open-drain output; it can only pull down the bus when active. The SDA line only pulls LOW during data reads and when signaling ACK. All data is shifted in MSB (bit 7) first.

#### I<sup>2</sup>C Slave Address

The equivalent 7 bit slave identification for the FAN53730UCX device version is 7h'20. This is followed by the read/write bit (0 = Write) and (1 = Read).

| 7–Bit | Binary  | Hex   |

|-------|---------|-------|

| 7h'20 | 0100000 | 8h'40 |

#### **REGISTER MAP**

#### **REGISTER MAPPING TABLE**

|         |             |                   |        |            |                                 | Write Only | Read / Write    | Read / Clear | Write/Clear |

|---------|-------------|-------------------|--------|------------|---------------------------------|------------|-----------------|--------------|-------------|

| Address | Name        | Bit[7]            | Bit[6] | Bit[5]     | Bit[4]                          | Bit[3]     | Bit[2]          | Bit[1]       | Bit[0]      |

| 0x01    | FAULT FLAGS | 0 <u>POWER_GO</u> |        | POWER_GOOD | 0                               | UVLO_FAULT | OVER_TEMP_FAULT | SHORT_FAULT  | ILIM_FAULT  |

| 0x02    | CONFIG1     | 0 ARM_TO DVS_FCCM |        | RR_DVS     |                                 |            | HIGH_BANDWIDTH  | VAL_ILIM     |             |

| 0x03    | CONFIG2     | 0                 |        |            | <u>Transient</u><br>Enhancement | FAULT_SHDN | BIAS_MODE       |              | PG_POL      |

| 0x04    | VOUT_SET_1  | VSET1             |        |            |                                 | <u>.</u>   | <u>.</u>        |              |             |

| 0x05    | VOUT_SET_2  | VSET2             |        |            |                                 |            |                 |              |             |

| 0x06    | ENABLE      | 0 <u>ARM_EN</u>   |        | DVS_EN     | OUT_DISCHARGE                   | VSEL_FCCM  | FORCE_CCM       | ENABLE       |             |

| 0x09    | RESET       | SOFT_F            | RESET  |            |                                 |            |                 |              |             |

#### **REGISTER DETAILS**

#### Table 1. REGISTER DETAILS – 0 × 01 FAULT FLAGS

| 0 × 01 FAULT FLAGS |                |         |       | Default = 00000000                                                                                                              |  |  |

|--------------------|----------------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                | Name           | Default | Туре  | Description                                                                                                                     |  |  |

| 7:6                | UNUSED         |         |       |                                                                                                                                 |  |  |

| 5                  | POWER_GOOD     | 0       | Read  | Reset condition: 0                                                                                                              |  |  |

|                    |                |         |       | PG Bit (Tracks the state of PG Output Active state)                                                                             |  |  |

|                    |                |         |       | Code Power Good Status                                                                                                          |  |  |

|                    |                |         |       | 0 Power good output is not active<br>1 Power good output is active                                                              |  |  |

|                    |                |         |       | 1 Power good output is active                                                                                                   |  |  |

| 4                  | UNUSED         |         |       |                                                                                                                                 |  |  |

| 3                  | UVLO_FAULT     | 0       | R/CLR | Reset condition: 0                                                                                                              |  |  |

|                    |                |         |       | Displays UVLO fault status. This flag is set when a UVLO fault occurs.<br>The flag is cleared upon read.                        |  |  |

|                    |                |         |       | Code Input Under Voltage Fault Occurrence                                                                                       |  |  |

|                    |                |         |       | 0 No UVLO fault occurred                                                                                                        |  |  |

|                    |                |         |       | 1 A UVLO fault occured                                                                                                          |  |  |

| 2                  | OVER_TEMP_FAUL | 0       | R/CLR | Reset condition: 0                                                                                                              |  |  |

|                    | ſ              |         |       | Displays over temp fault status. This flag is set when a die over temp fault occurs.<br>The flag is cleared upon read.          |  |  |

|                    |                |         |       | Code Die Over Temperature Fault                                                                                                 |  |  |

|                    |                |         |       | 0 No over temp fault                                                                                                            |  |  |

|                    |                |         |       | 1 An over temp fault occurred                                                                                                   |  |  |

| 1                  | SHORT_FAULT    | 0       | R/CLR | Reset condition: 0                                                                                                              |  |  |

|                    |                |         |       | Displays $V_{OUT}$ short fault status. This flag is latched when a $V_{OUT}$ short fault occurs. The flag is cleared upon read. |  |  |

|                    |                |         |       | Code Vout Short Fault                                                                                                           |  |  |

|                    |                |         |       | 0 The output has not shorted                                                                                                    |  |  |

|                    |                |         |       | 1 $V_{OUT}$ has dropped below 100 mV for > 40 $\mu$ s                                                                           |  |  |

| 0                  | ILIM_FAULT     | 0       | R/CLR | Reset condition: 0                                                                                                              |  |  |

|                    |                |         |       | The ILIM flag is set if the valley current limit is triggered continuously for 40 $\mu s.$ The flag is cleared upon read.       |  |  |

|                    |                |         |       | Code VALLEY Current Limit Fault                                                                                                 |  |  |

|                    |                |         |       | 0 No ILIM fault                                                                                                                 |  |  |

|                    |                |         |       | 1 ILIM triggered event for 40 μs                                                                                                |  |  |

#### Table 2. REGISTER DETAILS – $0 \times 02$ CONFIG1

|     | <u>0 × 02 CONFIG1</u> |         |      | Default = 00000111                                                                                                            |

|-----|-----------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name                  | Default | Туре | Description                                                                                                                   |

| 7   | UNUSED                |         |      |                                                                                                                               |

| 6   | ARM_TO                | 0       | R/W  | Reset condition: 0                                                                                                            |

|     |                       |         |      | Sets the timeout period for Audio Reduction Mode forced switching event                                                       |

|     |                       |         |      | Code Audio Reduction Mode Timeout                                                                                             |

|     |                       |         |      | 0 25 μs                                                                                                                       |

|     |                       |         |      | 1 40 μs                                                                                                                       |

| 5   | DVS_FCCM              | 0       | R/W  | Reset condition: 0                                                                                                            |

|     |                       |         |      | Controls whether the Force CCM functionality is active when DVS is enabled<br>and the voltage is programmed from high to low. |

|     |                       |         |      | Code CCM During high to low DVS Transition                                                                                    |

|     |                       |         |      | 0 Force CCM is not active during negative V <sub>OUT</sub> transitions                                                        |

|     |                       |         |      | 1 Force CCM is active during negative V <sub>OUT</sub> transitions                                                            |

| 4:2 | RR_DVS                | 001     | R/W  | Reset condition: 001                                                                                                          |

|     |                       |         |      | DVS (and also Soft-Start) ramp rate                                                                                           |

|     |                       |         |      | Code DVS Time per step                                                                                                        |

|     |                       |         |      | 000 2 μs/step                                                                                                                 |

|     |                       |         |      | 001 4 μs/step                                                                                                                 |

|     |                       |         |      | 010 6 μs/step                                                                                                                 |

|     |                       |         |      | 011 8 μs/step                                                                                                                 |

|     |                       |         |      | 100 10 μs/step                                                                                                                |

|     |                       |         |      | 101 12 μs/step                                                                                                                |

|     |                       |         |      | 110 14 μs/step                                                                                                                |

|     |                       |         |      | 111 16 μs/step                                                                                                                |

| 1   | HIGH_BANDWIDTH        | 1       | R/W  | Reset condition: 1                                                                                                            |

|     |                       |         |      | Control loop high bandwidth adjust. Set to "0" when $V_{OUT}$ < 0.8 V.                                                        |

|     |                       |         |      | Code Bandwidth Adjust                                                                                                         |

|     |                       |         |      | 0 Low Bandwidth setting                                                                                                       |

|     |                       |         |      | 1 High Bandwidth setting                                                                                                      |

| 0   | VAL_ILIM              | 1       | R/W  | Reset condition: 1                                                                                                            |

|     |                       |         |      | Valley Current Limit threshold. The FAN53730 will limit the valley of the inductor current to the $\rm I_{VALLEY}$ target.    |

|     |                       |         |      | Code I <sub>VALLEY</sub> (Typ)<br>0 2.3 A                                                                                     |

|     |                       |         |      | 1 4.2 A                                                                                                                       |

|     |                       |         |      | · · · · · · · · · · · · · · · · · · ·                                                                                         |

#### Table 3. REGISTER DETAILS – 0 $\times$ 03 CONFIG2

|     | <u>0 × 03 CONFIG2</u> |         |      | Default = 00010001                                                                                                                                                                   |

|-----|-----------------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name                  | Default | Туре | Description                                                                                                                                                                          |

| 7:5 | UNUSED                |         |      |                                                                                                                                                                                      |

| 4   | TRANSIENT_ENHANCEMEN  | 1       | R/W  | Reset condition: 1                                                                                                                                                                   |

|     | Т                     |         |      | Transient Enhancement Mode                                                                                                                                                           |

|     |                       |         |      | Code Transient Enhancement Mode                                                                                                                                                      |

|     |                       |         |      | 0 Disables the extended on-time during V <sub>OUT</sub> dips                                                                                                                         |

|     |                       |         |      | 1 Enables the extended on-time during V <sub>OUT</sub> dips                                                                                                                          |

| 3   | FAULT_SHDN            | 0       | R/W  | Reset condition: 0                                                                                                                                                                   |

|     |                       |         |      | This register enables/disables the shutdown option for faults.<br><u>Note:</u> For proper operation, this bit should only be written to when the device is<br>in the shutdown state. |

|     |                       |         |      | Code Fault Shutdown Control                                                                                                                                                          |

|     |                       |         |      | 0 The converter will auto-restart after 20 ms if a fault occurs                                                                                                                      |

|     |                       |         |      | 1 The converter will be placed into shutdown if a fault occurs                                                                                                                       |

| 2:1 | BIAS_MODE             | 00      | R/W  | Reset condition: 00                                                                                                                                                                  |

|     |                       |         |      | Sets the converters ability to shutdown various blocks to achieve low quies-<br>cent current vs. output accuracy and response time.                                                  |

|     |                       |         |      | Code Low Bias Mode Control                                                                                                                                                           |

|     |                       |         |      | 00 Ultra Low Bias Mode                                                                                                                                                               |

|     |                       |         |      | 01 Low Bias Mode                                                                                                                                                                     |

|     |                       |         |      | 1X High Bias Mode                                                                                                                                                                    |

| 0   | PG_POL                | 1       | R/W  | Reset condition: 1                                                                                                                                                                   |

|     |                       |         |      | Changes the polarity of the Power-Good Output                                                                                                                                        |

|     |                       |         |      | Code Power–Good Polarity                                                                                                                                                             |

|     |                       |         |      | 0 PG output is active low                                                                                                                                                            |

|     |                       |         |      | 1 PG output is active high                                                                                                                                                           |

#### Table 4. REGISTER DETAILS – 0 $\times$ 04 VOUT\_SET\_1