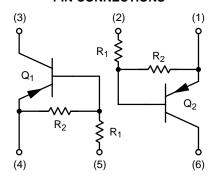

# Dual PNP Bias Resistor Transistors R1 = 100 kΩ, R2 = $\infty$ kΩ

# PNP Transistors with Monolithic Bias Resistor Network

# NSBA115TDP6

This series of digital transistors is designed to replace a single device and its external resistor bias network. The Bias Resistor Transistor (BRT) contains a single transistor with a monolithic bias network consisting of two resistors; a series base resistor and a base-emitter resistor. The BRT eliminates these individual components by integrating them into a single device. The use of a BRT can reduce both system cost and board space.

#### **Features**

- Simplifies Circuit Design

- Reduces Board Space

- Reduces Component Count

- S and NSV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable

- This Device is Pb-Free, Halogen Free/BFR Free and is RoHS Compliant

#### **MAXIMUM RATINGS**

(T<sub>A</sub> = 25 °C, common for Q<sub>1</sub> and Q<sub>2</sub>, unless otherwise noted)

| Rating                         | Symbol               | Max | Unit |

|--------------------------------|----------------------|-----|------|

| Collector-Base Voltage         | V <sub>CBO</sub>     | 50  | Vdc  |

| Collector-Emitter Voltage      | V <sub>CEO</sub>     | 50  | Vdc  |

| Collector Current – Continuous | IC                   | 100 | mAdc |

| Input Forward Voltage          | V <sub>IN(fwd)</sub> | 40  | Vdc  |

| Input Reverse Voltage          | V <sub>IN(rev)</sub> | 5   | Vdc  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **ORDERING INFORMATION**

|   | Device         | Package | Shipping <sup>†</sup> |

|---|----------------|---------|-----------------------|

| I | NSBA115TDP6T5G | SOT-963 | 8,000/Tape & Reel     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **PIN CONNECTIONS**

#### **MARKING DIAGRAM**

SOT-963 CASE 527AD

V = Specific Device Code M = Date Code\*

<sup>\*</sup>Date Code orientation may vary depending upon manufacturing location.

# NSBA115TDP6

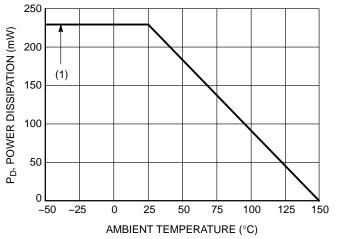

# THERMAL CHARACTERISTICS

| Characteristic                                                                                                                                                 | Symbol                            | Max                      | Unit        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-------------|

| NSBA115TDP6 (SOT-963) ONE JUNCTION HEATED                                                                                                                      | •                                 |                          |             |

| Total Device Dissipation $T_A = 25 ^{\circ}C \qquad \text{(Note 1)}$ $\text{(Note 2)}$ Derate above 25 $^{\circ}C \qquad \text{(Note 1)}$ $\text{(Note 2)}$    | P <sub>D</sub>                    | 231<br>269<br>1.9<br>2.2 | MW<br>mW/°C |

| Thermal Resistance,<br>Junction to Ambient (Note 1)<br>(Note 2)                                                                                                | $R_{	heta JA}$                    | 540<br>464               | °C/W        |

| NSBA115TDP6 (SOT-963) BOTH JUNCTION HEATED (Note 3)                                                                                                            |                                   |                          |             |

| Total Device Dissipation $T_A = 25  ^{\circ}C \qquad \text{(Note 1)} $ $\text{(Note 2)}$ Derate above 25 $^{\circ}C \qquad \text{(Note 1)} $ $\text{(Note 2)}$ | P <sub>D</sub>                    | 339<br>408<br>2.7<br>3.3 | MW<br>mW/°C |

| Thermal Resistance,<br>Junction to Ambient<br>(Note 1)                                                                                                         | $R_{	hetaJA}$                     | 369<br>306               | °C/W        |

| Junction and Storage Temperature Range                                                                                                                         | T <sub>J</sub> , T <sub>stg</sub> | -55 to +150              | °C          |

FR-4 @ 100 mm<sup>2</sup>, 1 oz. copper traces, still air.

FR-4 @ 500 mm<sup>2</sup>, 1 oz. copper traces, still air.

Both junction heated values assume total power is sum of two equally powered channels.

# NSBA115TDP6

# **ELECTRICAL CHARACTERISTICS** ( $T_A = 25$ °C, common for $Q_1$ and $Q_2$ , unless otherwise noted)

| Characteristic                                                                                           | Symbol                         | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------------------------|--------------------------------|-----|------|------|------|

| OFF CHARACTERISTICS                                                                                      |                                |     |      | •    |      |

| Collector-Base Cutoff Current $(V_{CB} = 50 \text{ V}, I_E = 0)$                                         | Ісво                           | -   | -    | 100  | nAdc |

| Collector-Emitter Cutoff Current $(V_{CE} = 50 \text{ V}, I_B = 0)$                                      | I <sub>CEO</sub>               | -   | -    | 500  | nAdc |

| Emitter-Base Cutoff Current $(V_{EB} = 6.0 \text{ V}, I_C = 0)$                                          | I <sub>EBO</sub>               | -   | -    | 0.1  | mAdc |

| Collector-Base Breakdown Voltage $(I_C = 10 \mu A, I_E = 0)$                                             | V <sub>(BR)CBO</sub>           | 50  | -    | _    | Vdc  |

| Collector-Emitter Breakdown Voltage (Note 4) (I <sub>C</sub> = 2.0 mA, I <sub>B</sub> = 0)               | V <sub>(BR)CEO</sub>           | 50  | -    | _    | Vdc  |

| ON CHARACTERISTICS                                                                                       |                                |     |      |      |      |

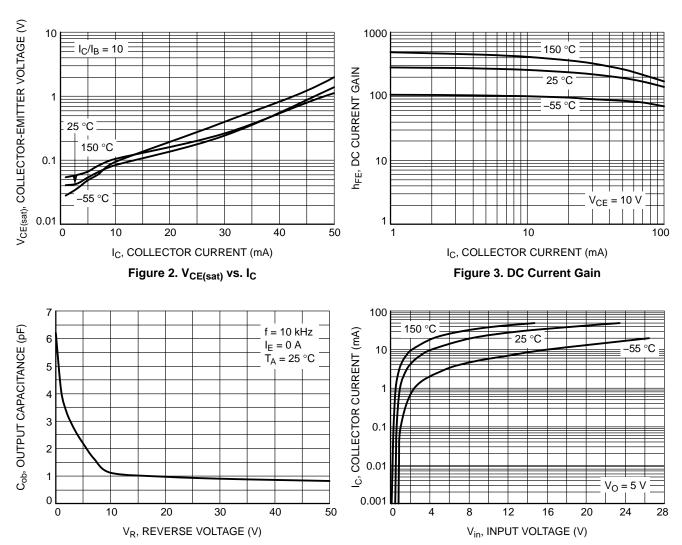

| DC Current Gain (Note 4)<br>(I <sub>C</sub> = 5.0 mA, V <sub>CE</sub> = 10 V)                            | h <sub>FE</sub>                | 160 | 350  | _    |      |

| Collector-Emitter Saturation Voltage (Note 4) $(I_C = 10 \text{ mA}, I_B = 0.3 \text{ mA})$              | V <sub>CE(sat)</sub>           | -   | -    | 0.25 | V    |

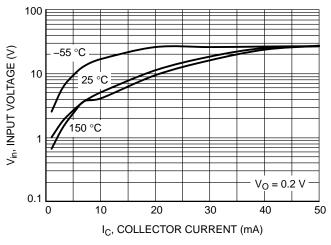

| Input Voltage (Off) (V <sub>CE</sub> = 5.0 V, I <sub>C</sub> = 100 $\mu$ A)                              | V <sub>i(off)</sub>            | -   | 0.62 | -    | Vdc  |

| Input Voltage (On)<br>(V <sub>CE</sub> = 0.2 V, I <sub>C</sub> = 1.0 mA)                                 | V <sub>i(on)</sub>             | -   | 1.0  | _    | Vdc  |

| Output Voltage (On) (V <sub>CC</sub> = 5.0 V, V <sub>B</sub> = 2.5 V, R <sub>L</sub> = 1.0 k $\Omega$ )  | V <sub>OL</sub>                | -   | -    | 0.2  | Vdc  |

| Output Voltage (Off) (V <sub>CC</sub> = 5.0 V, V <sub>B</sub> = 0.5 V, R <sub>L</sub> = 1.0 k $\Omega$ ) | V <sub>OH</sub>                | 4.9 | -    | _    | Vdc  |

| Input Resistor                                                                                           | R1                             | 70  | 100  | 130  | kΩ   |

| Resistor Ratio                                                                                           | R <sub>1</sub> /R <sub>2</sub> | -   | -    | -    |      |

<sup>4.</sup> Pulsed Condition: Pulse Width = 300 ms, Duty Cycle ≤ 2%.

(1) SOT-963; 100 mm<sup>2</sup>, 1 oz. Copper Trace

Figure 1. Derating Curve

### NSBA115TDP6

# TYPICAL CHARACTERISTICS NSBA115TDP6

Figure 4. Output Capacitance

Figure 5. Output Current vs. Input Voltage

Figure 6. Input Voltage vs. Output Current

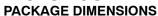

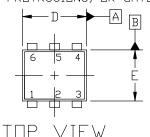

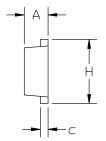

## SOT-963 1.00x1.00x0.37, 0.35P CASE 527AD **ISSUE F**

**DATE 20 FEB 2024**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2018. 1.

- CONTROLLING DIMENSION: MILLIMETERS.

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS, MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH,

- PROTRUSIONS, OR GATE BURRS

VIFW

|     | MILLIMETERS |      |      |

|-----|-------------|------|------|

| DIM | MIN.        | N□M. | MAX. |

| А   | 0.34        | 0.37 | 0.40 |

| b   | 0.10        | 0.15 | 0.20 |

| C   | 0.07        | 0.12 | 0.17 |

| D   | 0.95        | 1.00 | 1.05 |

| E   | 0.75        | 0.80 | 0.85 |

| е   | 0.35 BSC    |      |      |

| Н   | 0.95        | 1.00 | 1.05 |

| L   | 0.19 REF    |      |      |

| L2  | 0.05        | 0.10 | 0.15 |

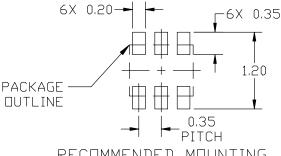

# RECOMMENDED MOUNTING FOOTPRINT

\*For additional information on our Pb-Free strategy and soldering details, please download the  $\ensuremath{\square N}$  Semiconductor Soldering and Mounting Techniques Reference manual, SOLDERRM/D.

# BUTTUM VIEW

| STYLE 1:                      | STYLE 2:                      | STYLE 3:                        |

|-------------------------------|-------------------------------|---------------------------------|

| PIN 1. EMITTER 1              | PIN 1. EMITTER 1              | PIN 1. CATHODE 1                |

| 2. BASE 1                     | <ol><li>EMITTER2</li></ol>    | <ol><li>CATHODE 1</li></ol>     |

| <ol><li>COLLECTOR 2</li></ol> | 3. BASE 2                     | <ol><li>ANODE/ANODE 2</li></ol> |

| 4. EMITTER 2                  | <ol><li>COLLECTOR 2</li></ol> | <ol><li>CATHODE 2</li></ol>     |

| 5. BASE 2                     | 5. BASE 1                     | <ol><li>CATHODE 2</li></ol>     |

| <ol><li>COLLECTOR 1</li></ol> | <ol><li>COLLECTOR 1</li></ol> | 6. ANODE/ANODE 1                |

| STYLE 4:                      | STYLE 5:                      | STYLE 6:                        |

# PIN 1. CATHODE 2. CATHODE 3. ANODE 4. ANODE PIN 1. COLLECTOR 2. COLLECTOR 3. BASE 4. EMITTER

PIN 1. CATHODE 2. ANODE 3. CATHODE 4. CATHODE 5 CATHODE CATHODE 6. CATHODE 6. CATHODE

5. COLLECTOR 6. COLLECTOR STYLE 8: PIN 1. DRAIN 2. DRAIN STYLE 7: PIN 1. CATHODE 2. ANODE 3. CATHODE 4. CATHODE 3. GATE 4. SOURCE 5. ANODE 6. CATHODE 5. DRAIN 6. DRAIN 5. GATE 2 6. DRAIN 1

STYLE 9: PIN 1. SOURCE 1 2. GATE 1 3. DRAIN 2 4. SOURCE 2

## **GENERIC MARKING DIAGRAM\***

XX = Specific Device Code = Month Code

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON26456D                   | Electronic versions are uncontrolled except when accessed directly from the Document Reprinted versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOT-963 1.00x1.00x0.37, 0.35P |                                                                                                                                                                        | PAGE 1 OF 1 |

onsemi and Onsemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries, onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

STYLE 10: PIN 1. CATHODE 1 2. N/C 3. CATHODE 2

4. ANODE 2

5. N/C 6. ANODE 1

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales