**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# High Efficiency Switch Mode Li-Ion Battery Charger

The ADP3808A is a complete Li-Ion battery charging controller for 3– or 4–cell battery packs. The device combines accurate final battery charge voltage control with constant current control to simplify the implementation of constant-current, constant-voltage (CCCV) chargers.

The final battery charge voltage is programmable between 4.0 V to 4.5 V per cell, allowing the charging of various cell types. The charge current is programmable over a wide range from trickle charging to full charging. The system current sense amplifier includes an ac adapter detection output to signal that the adapter is connected. The bootstrapped synchronous driver controls two N-channel MOSFET transistors for high efficiency charging at a low system cost.

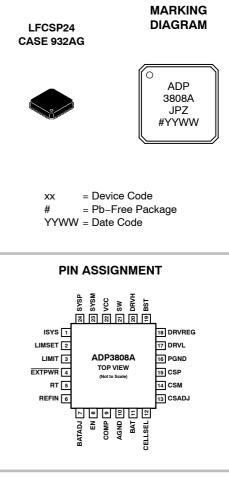

The ADP3808A is specified over the extended commercial temperature range of 0°C to 100°C and is available in a 24–lead LFCSP package.

# Features

- Selectable 3-Cell or 4-Cell Operation

- Adjustable 4.0 V to 4.5 V Per Cell

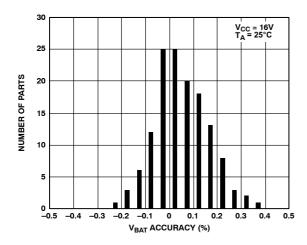

- High End-of-Charge Voltage Accuracy

- ◆ ±0.4% @ 25°C

- ★ ±0.6% @ 5°C to 55°C

- ◆ ±0.8% @ 0°C to 100°C

- Programmable Charge Current, Including Trickle Charge

- Bootstrapped Synchronous Drive for External N-Channel MOSFETs

- Programmable Oscillator Frequency

- This is a Pb–Free Device

# Applications

- Portable Computers

- Portable Equipment

# **ON Semiconductor®**

http://onsemi.com

# **ORDERING INFORMATION**

| Device*         | Package | Shipping <sup>†</sup> |

|-----------------|---------|-----------------------|

| ADP3808AJCPZ-RL | LFCSP24 | 5000/Tape & Reel      |

\*The "Z' suffix indicates Pb-Free package.

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

1

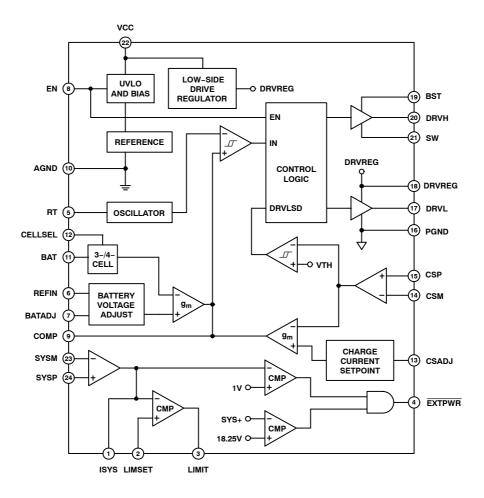

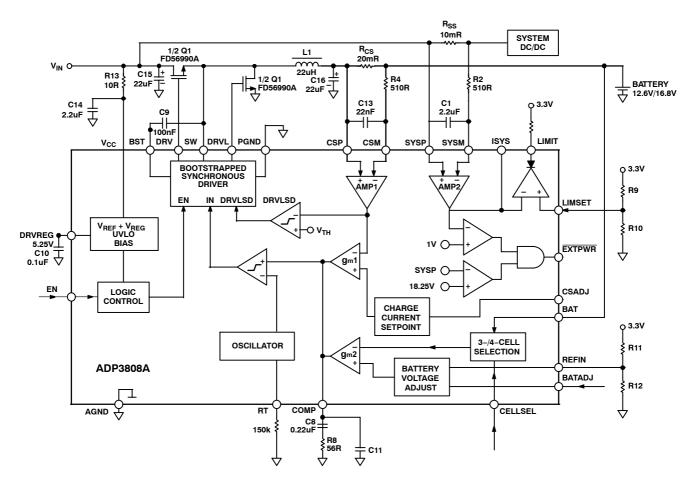

Figure 1. Functional Block Diagram

# **ABSOLUTE MAXIMUM RATINGS**

| Description                                                                        | Symbol                                                                       | Value                         | Unit |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------|------|

| Supply Voltage Input                                                               | VCC                                                                          | –0.3 to +25                   | V    |

| Power Ground                                                                       | PGND                                                                         | –0.3 to +0.3                  | V    |

| Bootstrap Supply Voltage Input                                                     | BST                                                                          | –0.3 to +30                   | V    |

| BST to Switching Node                                                              | BST to SW                                                                    | –0.3 to +6                    | V    |

| Switching Node                                                                     | SW                                                                           | -4 to +25                     | V    |

| High-Side Driver Output                                                            | DRVH                                                                         | SW – 0.3 to BST + 0.3         | V    |

| v-Side Driver Output DRVL PGND - 0.3 to DRVR                                       |                                                                              | PGND – 0.3 to DRVREG + 0.3    | V    |

| System Sense Inputs to Analog Ground     SYSP, SYSM to AGND       DC     < 50 μsec |                                                                              | -25 to +30<br>-25 to +35      | V    |

| Battery Input, Current Sense Inputs to Analog<br>Ground                            | BAT, CSP, CSM to AGND                                                        | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Positive System Sense Input to Negative System Sense Input                         | SYSP to SYSM                                                                 | –5 to +5                      | V    |

| Positive Current Sense Input to Negative Current Sense Input                       | CSP to CSM                                                                   | –5 to +5                      | V    |

| All Other Inputs and Outputs                                                       | DRVREG, CSADJ, EN,<br>CELLSEL, REFIN, BATADJ,<br>LIMSET, LIMIT, ISYS, EXTPWR | -0.3 to +6                    | V    |

| 2-Layer Board<br>4-Layer Board                                                     | θ <sub>JA</sub>                                                              | 125<br>83                     | °C/W |

| Operating Ambient Temperature Range                                                | T <sub>A</sub>                                                               | 0 to 100                      | °C   |

| Junction Temperature Range                                                         | ТJ                                                                           | 0 to 150                      | °C   |

| Storage Temperature Range                                                          | Τ <sub>S</sub>                                                               | –65 to +150                   | °C   |

| Lead Temperature Soldering (10 sec)<br>Vapor Phase (60 sec)<br>Infrared (15 sec)   |                                                                              | 300<br>215<br>220             | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

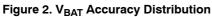

# **PIN DESCRIPTION**

| Pin No. | Symbol  | Description                                                                                                                                                                                            |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ISYS    | Output for System Current Sense Amplifier.                                                                                                                                                             |

| 2       | LIMSET  | System Current Limit Set Point Input.                                                                                                                                                                  |

| 3       | LIMIT   | System Current Limit Output. This is an open-drain pin and requires a pull-up resistor to a maximum of 6.0 V.                                                                                          |

| 4       | EXTPWR  | External Adapter Sense Open-Drain Output. This pin pulls low when the ac adapter voltage is present. A pullup resistor is required to a maximum of 6 V.                                                |

| 5       | RT      | Frequency Setting Resistor Input. An external resistor connected between this pin and AGND sets the oscillator frequency of the device.                                                                |

| 6       | REFIN   | Reference Input for BATADJ and CSADJ.                                                                                                                                                                  |

| 7       | BATADJ  | Battery Voltage Adjust Input. This pin uses an analog voltage referenced to REFIN to program voltage from 4.0 V to 4.5 V per cell.                                                                     |

| 8       | EN      | Charger Enable Input. Pulling this pin to AGND disables the DRVH and DRVL outputs and puts the circuitry powered by $V_{CC}$ into a low power state. The system amplifier and EXTPWR are still active. |

| 9       | COMP    | Output of Error Amplifiers and Compensation Point.                                                                                                                                                     |

| 10      | AGND    | Analog Ground. Reference point for the battery sense and all analog functions.                                                                                                                         |

| 11      | BAT     | Battery Sense Input.                                                                                                                                                                                   |

| 12      | CELLSEL | Battery Cell Selection Input. Pulling this pin high selects 3-cell operation; pulling it low selects 4-cell operation.                                                                                 |

| 13      | CSADJ   | Charge Current Programming Input. This pin uses an analog voltage referenced to REFIN to program the battery charge current. ( $V_{CSP} - V_{CSM}$ ) = 96 mV x CSADJ/REFIN.                            |

| 14      | CSM     | Negative Current Sense Input. This pin connects to the battery side of the battery current sense resistor.                                                                                             |

| 15      | CSP     | Positive Current Sense Input. This pin connects to the inductor side of the battery current sense resistor.                                                                                            |

| 16      | PGND    | Power Ground. This pin should closely connect to the source of the lower MOSFET.                                                                                                                       |

| 17      | DRVL    | Synchronous Rectifier Drive. Output drive for the lower MOSFET.                                                                                                                                        |

| 18      | DRVREG  | Driver Supply Output. A bypass capacitor should be connected from this pin to PGND to provide filtering for the low-side supply.                                                                       |

| 19      | BST     | Upper MOSFET Floating Bootstrap Supply. A capacitor connected between the BST and SW pins holds this bootstrapped voltage for the high-side MOSFET as it is switched.                                  |

| 20      | DRVH    | Main Switch Drive. Output drive for the upper MOSFET.                                                                                                                                                  |

| 21      | SW      | Switch Node Input. This pin is connected to the buck-switching node, close to the source of the upper MOSFET, and is the floating return for the upper MOSFET drive signal.                            |

| 22      | VCC     | Input Supply. This pin does not power the SYS amplifier section.                                                                                                                                       |

| 23      | SYSM    | Negative System Current Sense Input. This pin connects to the battery side of the system current sense resistor.                                                                                       |

| 24      | SYSP    | Positive System Current Sense Input. This pin connects to the adapter side of the system current sense resistor. This pin also provides power to the system amplifier section.                         |

| 25      | Paddle  | This pin should be connected to AGND.                                                                                                                                                                  |

# **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 20 V, EN = 5.0 V, REFIN = 3.0 V,  $T_A$  = 0°C to 100°C; unless otherwise noted. (Note 1)

| Parameter                       | Symbols                 | Symbol                                                                                                                                | Min  | Тур   | Max             | Unit |

|---------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------|------|

| Battery Voltage Sensing         |                         |                                                                                                                                       |      |       |                 |      |

| Accuracy                        | $\Delta V_{BAT}$        | $T_A = 25^{\circ}C, 13 \text{ V} \le \text{V}_{CC} \le 21 \text{ V},$<br>BATADJ = 0 V or BATADJ = REFIN                               | -0.4 |       | +0.4            | %    |

|                                 |                         | $5^{\circ}C \le T_A \le 55^{\circ}C$ , 13 V $\le V_{CC} \le 21$ V,<br>BATADJ = 0 V or BATADJ = REFIN                                  | -0.6 |       | +0.6            | %    |

|                                 |                         | 13 V $\leq$ V <sub>CC</sub> $\leq$ 21 V,<br>BATADJ = 0 V or BATADJ = REFIN                                                            | -0.8 |       | +0.8            | %    |

| Input Resistance                | R <sub>BAT</sub>        |                                                                                                                                       |      | 170   |                 | kΩ   |

| Shutdown Leakage Current        | I <sub>BAT(SD)</sub>    | EN = 0 V                                                                                                                              |      | 0.2   | 1.0             | μA   |

| Overvoltage Threshold           | V <sub>BAT(OV)</sub>    |                                                                                                                                       | 120  | 135   |                 | %    |

| Overvoltage Response Time       | t <sub>BAT(OV)</sub>    | V <sub>BAT(OV)</sub> to COMP < 1 V                                                                                                    |      | 1     |                 | μs   |

| Battery Voltage Adjust          |                         |                                                                                                                                       |      |       |                 |      |

| BATADJ Input Range              | V <sub>BATADJ</sub>     |                                                                                                                                       | 0    |       | REFIN           | V    |

| REFIN Input Range               | V <sub>REFIN</sub>      |                                                                                                                                       | 2.0  |       | 3.5             | V    |

| 3-Cell Voltage Low              | V <sub>BAT</sub>        | BATADJ = 0 V, CELLSEL = 3.3 V                                                                                                         |      | 12.0  |                 | V    |

| 3-Cell Voltage High             | V <sub>BAT</sub>        | BATADJ = REFIN, CELLSEL = 3.3 V                                                                                                       |      | 13.5  | 1               | V    |

| 4-Cell Voltage Low              | V <sub>BAT</sub>        | BATADJ = 0 V, CELLSEL = 0 V                                                                                                           |      | 16.0  |                 | V    |

| 4-Cell Voltage High             | V <sub>BAT</sub>        | BATADJ = REFIN, CELLSEL = 0 V                                                                                                         |      | 18.0  |                 | V    |

| Battery Current Sense Amplifier |                         | •                                                                                                                                     |      |       |                 |      |

| Accuracy (Note 2)               |                         | CSADJ = REFIN, 3 V $\leq$ V <sub>CS(CM)</sub> $\leq$ 21 V                                                                             | -5   |       | +5              | %    |

|                                 |                         | $\begin{array}{l} CSADJ = REFIN \ / \ 5, \ 3 \ V \leq V_{CS(CM)} \leq \\ 21 \ V \end{array}$                                          | -9   |       | +9              | %    |

|                                 |                         | $\begin{array}{l} 0^{\circ}C \leq T_{A} \leq 55^{\circ}C, \ CSADJ = REFIN \ / \ 32, \\ 3 \ V \leq V_{CS(CM)} \leq 12 \ V \end{array}$ | -33  |       | +33             | %    |

|                                 |                         | $\begin{array}{l} 0^{\circ}C \leq T_{A} \leq 55^{\circ}C, \ CSADJ = REFIN \ / \ 32, \\ 12 \ V < V_{CS(CM)} \leq 21 \ V \end{array}$   | -40  |       | +40             | %    |

| Input Common Mode Range         | V <sub>CM(CS)</sub>     |                                                                                                                                       | 0    |       | V <sub>CC</sub> | V    |

| Input Bias Current, Operating   | I <sub>B(CSP)</sub>     |                                                                                                                                       |      | 40    |                 | μA   |

| Input Bias Current, Shutdown    | I <sub>B(CSP,SD)</sub>  | EN = 0 V                                                                                                                              |      | 0.1   | 1               | μA   |

| Input Bias Current, CSM         | I <sub>B(CSM)</sub>     |                                                                                                                                       |      | 0.1   | 2               | μA   |

| Gain                            | A <sub>V(CS)</sub>      |                                                                                                                                       |      | 31.25 |                 | V/V  |

| CSADJ Bias Current              | I <sub>B(CSADJ)</sub>   |                                                                                                                                       |      | 1     | 2               | μA   |

| Overcurrent Threshold (Note 2)  | V <sub>CS(OC)</sub>     |                                                                                                                                       | 90   | 100   | 110             | mV   |

| Overcurrent Response Time       | t <sub>DC</sub>         | V <sub>OC</sub> > 130 mV to COMP < 1 V                                                                                                |      | 1     |                 | μs   |

| DRVL Shutdown Threshold         | V <sub>CS(DRVLSD)</sub> |                                                                                                                                       |      | 28    |                 | mV   |

| System Current Sense Amplifier  |                         |                                                                                                                                       |      |       |                 |      |

| Input Common Mode Range         | V <sub>CM(SYS)</sub>    | SYSP and SYSM to AGND                                                                                                                 | 10   |       | 22              | V    |

| Input Bias Current, SYSP        | I <sub>B(SYSP)</sub>    | V <sub>SYS(CM)</sub> = 19 V                                                                                                           |      | 300   | 400             | μA   |

| Input Bias Current, SYSM        | I <sub>B(SYSM)</sub>    | V <sub>SYS(CM)</sub> = 19 V                                                                                                           |      | 0.1   | 1               | μA   |

| Voltage Gain                    |                         | VISYS/(VSYSP - VSYSM)                                                                                                                 | 49.5 | 50    | 51.5            | V/V  |

| ISYS Output Current             |                         | V <sub>ISYS</sub> = 2.5 V                                                                                                             |      | 5     |                 | μA   |

| LIMIT Threshold                 | V <sub>TH(LIMIT)</sub>  | SYSP to SYSM, LIMSET = 2.5 V                                                                                                          | 48   | 53    | 58              | mV   |

| LIMSET Input Range              | VLIMSET                 |                                                                                                                                       | 0    |       | 3.5             | V    |

| LIMIT Output Voltage Low        | V <sub>OL(LIMIT)</sub>  | I <sub>LIMIT</sub> = -100 μA                                                                                                          | 1    | 30    | 75              | mV   |

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC) methods.

Measured between CSP and CSM. (V<sub>CSP</sub> - V<sub>CSM</sub>) = 96 mV x CSADJ/REFIN.

For propagation delays, t<sub>pdh</sub> refers to the specified signal going high, and t<sub>pdl</sub> refers to it going low.

The turn-on of DRVL is initiated after DRVH turns off by either SW crossing a ~ 1.0 V threshold or by examination of the timeout delay.

# **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 20 V, EN = 5.0 V, REFIN = 3.0 V,  $T_A$  = 0°C to 100°C; unless otherwise noted. (Note 1)

| Parameter                              | Symbols                                 | Symbol                                               | Min        | Тур        | Мах  | Unit |

|----------------------------------------|-----------------------------------------|------------------------------------------------------|------------|------------|------|------|

| LIMIT Propagation Delay Time           | t <sub>pdl(LIMIT)</sub>                 | (SYSP) – (SYSM) rising > 55 mV to<br>LIMIT going low |            | 1          |      | μs   |

| EXTPWR Current Threshold               | V <sub>TH(EXTPWR)</sub>                 | SYSP to SYSM                                         | 17.5       | 22.5       | 27.5 | mV   |

| EXTPWR Voltage Threshold               | V <sub>TH</sub> (EXTPWR)                | SYSP to AGND                                         | 18.0       | 18.25      | 18.5 | V    |

| EXTPWR Output Voltage Low              | V <sub>TH(EXTPWR)</sub>                 | $I_{\overline{EXTPWR}} = -100 \mu A$                 |            | 5          | 50   | mV   |

| EXTPWR Propagation Delay<br>Time       | V <sub>dpl</sub> (EXTPWR)               | SYSP Rising > 18.5 V to EXTPWR going low             |            | 1          |      | μs   |

| Oscillator                             |                                         |                                                      |            |            |      |      |

| Maximum Frequency                      | f <sub>OSC</sub>                        |                                                      |            | 1          |      | MHz  |

| Frequency Variation                    | $\Delta f_{OSC}$                        | RT = 150 kΩ                                          | 250        | 290        | 340  | kHz  |

| RT Output Voltage                      | V <sub>RT</sub>                         |                                                      | 1.9        | 2          | 2.1  | V    |

| Zero Duty Cycle Threshold              |                                         | Measured at COMP                                     |            | 1          |      | V    |

| Maximum Duty Cycle Threshold           |                                         | Measured at COMP                                     |            | 2          |      | V    |

| Logic Inputs (EN, CELLSEL)             |                                         |                                                      |            |            |      |      |

| Input Voltage High                     | VIH                                     |                                                      | 2.0        |            |      | V    |

| Input Voltage Low                      | VIL                                     |                                                      |            |            | 0.8  | V    |

| Input Current                          | I <sub>IN</sub>                         | Inputs = 0 V or 5 V                                  | -1         |            | +1   | μA   |

| High–Side Driver                       |                                         |                                                      |            |            |      |      |

| Output Resistance, Sourcing<br>Current |                                         | BST to SW = 5 V                                      |            | 3          | 8    | Ω    |

| Output Resistance, Sinking<br>Current  |                                         | BST to SW = 5 V                                      |            | 3          | 8    | Ω    |

| Output Resistance, Unbiased            |                                         | BST to SW = 0 V                                      |            | 10         |      | kΩ   |

| Transition Time                        | t <sub>rDRVH</sub> , t <sub>fDRVH</sub> | BST to SW = 5 V, C <sub>LOAD</sub> = 1 nF            |            | 20         | 40   | ns   |

| Propagation Delay Time                 | t <sub>pdhDRVH</sub>                    | BST to SW = 5 V, C <sub>LOAD</sub> = 1 nF            | 25         | 45         | 70   | ns   |

| Low–Side Driver                        |                                         |                                                      |            |            |      |      |

| Output Resistance, Sourcing<br>Current |                                         |                                                      |            | 3.8        | 8    | Ω    |

| Output Resistance, Sinking<br>Current  |                                         |                                                      |            | 1.5        | 8    | Ω    |

| Output Resistance, Unbiased            |                                         | VCC = PGND                                           |            | 10         |      | kΩ   |

| Transition Time                        | t <sub>rDRVL</sub> , t <sub>fDRVL</sub> | C <sub>LOAD</sub> = 1 nF                             |            | 20         | 40   | ns   |

| Propagation Delay Time (Note 3)        | t <sub>pdhDRVL</sub>                    | C <sub>LOAD</sub> = 1 nF                             |            | 15         | 35   | ns   |

| Timeout Delay (Note 4)                 |                                         | SW = 5 V<br>SW = PGND                                | 150<br>150 | 300<br>300 |      | ns   |

| Supply V <sub>CC</sub>                 |                                         |                                                      |            |            |      |      |

| Supply Voltage Range                   | V <sub>CC</sub>                         |                                                      | 10         |            | 22   | V    |

| Supply Current                         |                                         |                                                      |            |            |      | 1    |

| Normal Mode                            | I <sub>VCC</sub>                        | EN = 5 V                                             |            | 9.8        | 14   | mA   |

| Shutdown Mode                          | I <sub>VCC(SD)</sub>                    | EN = 0 V                                             |            | 1          | 10   | μA   |

| Undervoltage Lockout Threshold         | V <sub>UVLO</sub>                       | V <sub>CC</sub> rising                               | 9          | 9.5        | 10   | V    |

| Undervoltage Lockout Hysteresis        |                                         |                                                      |            | 600        |      | mV   |

| DRV Regulator Output Voltage           | V <sub>DRVREG</sub>                     | C <sub>L</sub> = 100 nF                              | 5.0        | 5.25       | 5.5  | V    |

| DRV Regulator Output Current           | IDRVREG                                 |                                                      | 10         |            |      | mA   |

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC) methods.

Measured between CSP and CSM. (V<sub>CSP</sub> - V<sub>CSM</sub>) = 96 mV x CSADJ/REFIN.

For propagation delays, t<sub>pdh</sub> refers to the specified signal going high, and t<sub>pdl</sub> refers to it going low.

The turn-on of DRVL is initiated after DRVH turns off by either SW crossing a ~ 1.0 V threshold or by examination of the timeout delay.

# **TYPICAL CHARACTERISTICS**

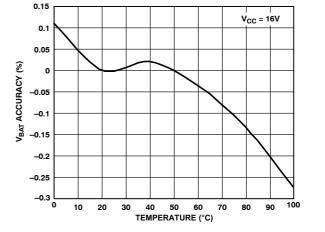

Figure 3. V<sub>BAT</sub> Accuracy vs. Temperature

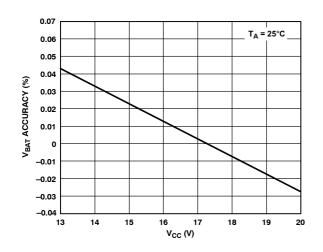

Figure 4. V<sub>BAT</sub> Accuracy vs. V<sub>CC</sub>

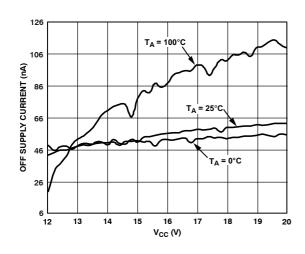

Figure 6. Off Supply Current vs. V<sub>CC</sub>

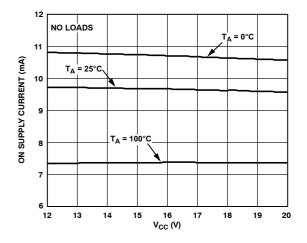

Figure 5. On Supply Current vs.  $V_{CC}$

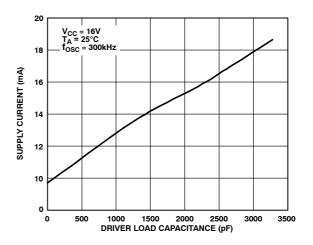

# **TYPICAL CHARACTERISTICS**

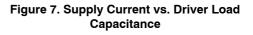

Figure 8. Oscillator Frequency vs. RT

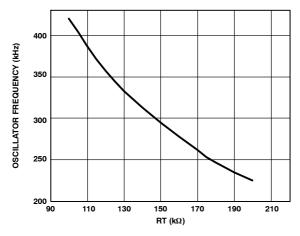

Figure 9. V<sub>LIMIT</sub> vs. V<sub>ISYS</sub>

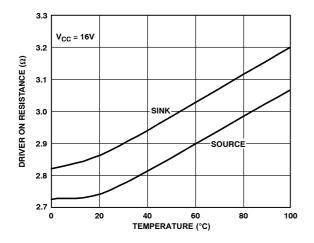

Figure 10. DRVH On Resistance vs. Temperature

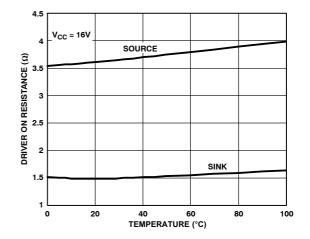

Figure 11. DRVL On Resistance vs. Temperature

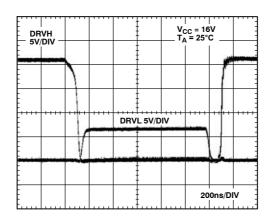

Figure 12. Driver Waveforms

# **TYPICAL CHARACTERISTICS**

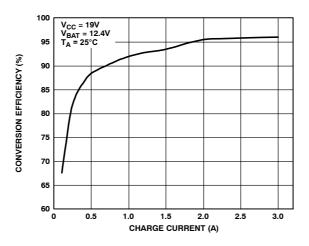

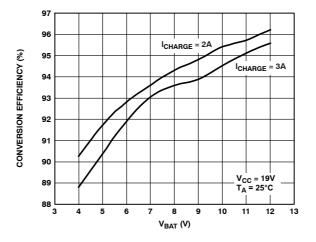

Figure 13. Conversion Efficiency vs. Charge Current

Figure 14. Conversion Efficiency vs. Battery Voltage

# Theory of Operation

The ADP3808A combines a bootstrapped synchronous switching driver with programmable current control and accurate final battery voltage control in a constant-current, constant-voltage (CCCV) Li-Ion battery charger. High accuracy voltage control is needed to safely charge Li-Ion batteries, which are typically specified at  $4.2 \text{ V} \pm 1\%$  per cell. For a typical notebook computer battery pack, three or four cells are in series, giving a total voltage of 12.6 V or 16.8 V. The ADP3808A allows the final battery voltage to be programmed. The programmable range is 4.0 V to 4.5 V per cell. The total number of cells to be charged can be set to either 3 or 4 via a control pin.

Another requirement for safely charging Li-Ion batteries is accurate control of the charge current. The actual charge current depends on the number of cells in parallel within the battery pack. Typically, this is in the range of 2.0 A to 3.0A. The ADP3808A provides flexibility in programming the charge current over a wide range. An external resistor is used to sense the charge current. The charge current can be set by programming the sense resistor voltage drop. The voltage drop can be set to a maximum of 96 mV. This programmability allows the current to be changed during charging. For example, the charge current can be reduced for trickle charging.

The synchronous driver provides high efficiency when charging at high currents. Efficiency is important mainly to reduce the amount of heat generated in the charger, but also to stay within the power limits of the ac adapter. With the addition of a bootstrapped high-side driver, the ADP3808A drives two external power NMOS transistors for a simple, lower cost power stage.

The ADP3808A also provides an uncommitted current sense amplifier. This amplifier provides an analog output pin for monitoring the current through an external sense resistor. The amplifier can be used anywhere in the system that high-side current sensing is needed. The sense amplifier output is compared to a programmable voltage limit. If the limit is exceeded, the LIMIT pin is asserted. The system sense amplifier is also used to detect the presence of an ac adaptor. If the adaptor is detected, the ADP3808A asserts a logic pin to signal the detection.

# Setting the Charge Current

The charge current is measured across an external sense resistor,  $R_{CS}$ , between the CSP and CSM pins. The input common-mode range is from ground to  $V_{CC}$ , allowing current control in short-circuit and low dropout conditions. The voltage between CSP and CSM is programmed by a ratio of the voltages at CSADJ and REFIN according to Equation 1.

$$V_{\rm CSP} - V_{\rm CSM} = 96 \, {\rm mV} \frac{{\rm CSADJ}}{{\rm REFIN}}$$

(eq. 1)

For example, using a 20 m $\Omega$  sense resistor gives a range from 150 mA with CSADJ = REFIN/32 to 4.8 A maximum when CSADJ = REFIN.

The power dissipation in  $R_{CS}$  should be kept below 500 mW. Components R4 and C13 in Figure 15 provide high frequency filtering for the current sense signal.

Figure 15. Typical Application Circuit

### **Final Battery Voltage Control**

As the battery approaches its final voltage, the ADP3808A switches from CC mode to CV mode. The change is achieved by the common output node of  $g_m1$  and  $g_m2$ . Only one of the two outputs controls the voltage at the COMP pin. Both amplifiers can only pulldown on COMP, such that when either amplifier has a positive differential input voltage, its output is not active. For example, when the battery voltage,  $V_{BAT}$ , is low,  $g_m2$  does not control VCOMP. When the battery voltage reaches the desired final voltage,  $g_m2$  takes control of the loop, and the charge current is reduced.

Amplifier  $g_m 2$  compares the battery voltage to a programmable level set by pins BATADJ and REFIN. The target battery voltage is dependent on the state of the CELLSEL pin as CELLSEL sets the number of cells to be charged. Pulling CELLSEL high sets the ADP3808A to charge three cells. When CELLSEL is tied to ground, four cells are selected. CELLSEL has a 2  $\mu$ A pullup current as a fail-safe to select three cells when it is left open.

The final battery voltage is programmable from 4.0 V to 4.5 V per cell. The programming voltage is applied to the

BATADJ pin and is ratioed to the REFIN pin. The battery voltage  $V_{BAT}$  is set according to Equation 2 and Equation 3. For CELLSEL > 2 V:

$$V_{BAT} = 12 V + 1.5 V \frac{BATADJ}{REFIN}$$

(eq. 2)

For CELLSEL < 0.8 V:

$$V_{BAT} = 16 V + 2.0 V \frac{BATADJ}{REFIN}$$

(eq. 3)

### **Oscillator and PWM**

The oscillator generates a triangle waveform between 1.0 V and 2.0 V, which is compared to the voltage at the COMP pin, setting the duty cycle of the driver stage. When  $V_{COMP}$  is below 1.0 V, the duty cycle is zero. Above 2.0 V, the duty cycle reaches its maximum. The oscillator frequency is set by the external resistor at the RT pin,  $R_{OSC}$ , and is given by Equation 4.

$$f_{OSC} = \frac{41 \times 10^9}{R_{OSC}}$$

(eq. 4)

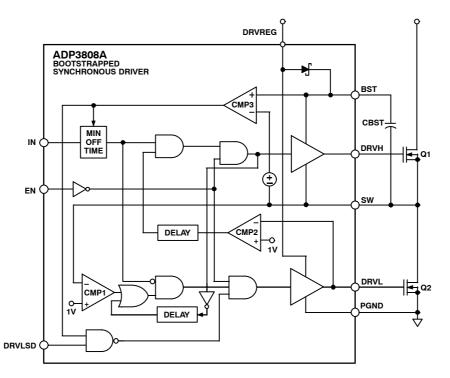

Figure 16. Bootstrapped Synchronous Driver

# 5.25 V Bootstrap Regulator

The driver stage is powered by the internal 5.25 V bootstrap regulator, which is available at the DRVREG pin. Because the switching currents are supplied by this regulator, decoupling must be added. A 0.1  $\mu$ F capacitor should be placed close to the ADP3808A, with the ground side connected close to the power ground pin, PGND. This supply is not recommended for use externally due to high switching noise.

### **Bootstrapped Synchronous Driver**

The PWM comparator controls the state of the synchronous driver shown in Figure 16. A high output from the PWM comparator forces DRVH on and DRVL off. The drivers have an on resistance of less than 4.0  $\Omega$  for fast rise and fall times when driving external MOSFETs. Furthermore, the bootstrapped drive allows an external NMOS transistor for the main switch instead of a PMOS. A boost capacitor of 0.1  $\mu$ F must be added externally between BST and SW.

The DRVL pin switches between DRVREG and PGND. The 5.25 V output of DRVREG drives the external NMOS with high  $V_{GS}$  to lower the on resistance. PGND should be connected close to the source pin of the external synchronous NMOS. When DRVL is high, this turns on the lower NMOS and pulls the SW node to ground. At this point, the boost capacitor is charged up through the internal boost diode. When the PWM switches high, DRVL is turned off and DRVH turns on. DRVH switches between BST and SW. When DRVH is on, the SW pin is pulled up to the input supply (typically 16 V), and BST rises above this voltage by approximately 4.75 V. Overlap protection is included in the driver to ensure that both external MOSFETs are not on at the same time. When DRVH turns off the upper MOSFET, the SW node goes low due to the inductor current. The ADP3808A monitors the SW voltage, and DRVL goes high to turn on the lower MOSFET when SW goes below 1.0 V. When DRVL turns off, an internal timer adds a delay of 50 ns before turning DRVH on. When the charge current is low, the DRVLSD comparator signals the driver to turn off the low-side MOSFET and DRVL is held low. The DRVLSD threshold is set to 0.8 V corresponding to a 32 mV differential between the CS pins.

The driver stage monitors the voltage across the BST capacitor with CMP3. When this voltage is less than 4.0 V, CMP3 forces a minimum off time of 200 ns. This ensures that the BST capacitor is charged even during DRVLSD. However, because a minimum off time is only forced when needed, the maximum duty cycle is greater than 99%.

### System Current Sense

An uncommitted differential amplifier is provided for additional high-side current sensing. This amplifier, AMP2, has a fixed gain of 50 V/V from the SYSP and SYSM pins to the analog output at ISYS. The common-mode range of the input pins is from 10 V to 22 V. This amplifier is the only part of the ADP3808A that remains active during shutdown. The power to this block is derived from the bias current on the SYSP and SYSM pins.

### LIMIT

The LIMIT pin is an open-drain output that signals when the voltage at ISYS exceeds the voltage at LIMSET. The internal comparator produces the function shown in Figure 9. This is a graph of V<sub>LIMIT</sub> vs. V<sub>ISYS</sub> where LIMSET is set to 1.5 V. The LIMIT pin should be pulled up to a maximum of 6.0 V through a resistor. When ISYS is below LIMSET, the LIMIT pin has high output impedance. The open-drain output is capable of sinking 100  $\mu$ A when the threshold is exceeded. This comparator is turned off during shutdown to conserve power.

# **AC Adaptor Detection**

The  $\overline{\text{EXTPWR}}$  pin on the ADP3808A is an open-drain active low output used to signal that an ac adaptor is connected. If the ISYS voltage level is greater than 1.0 V or the SYSP sense pin voltage is greater then 18.25 V, the  $\overline{\text{EXTPWR}}$  pin is driven low. A pullup resistor must be connected when this function is required. The maximum pullup voltage is 6.0 V.

# EN

A high impedance CMOS logic input is provided to turn off the ADP3808A. When the voltage on EN is less than 0.8 V, the ADP3808A is placed in low power shutdown. With the exception of the system current sense amplifier, AMP2, all other circuitry is turned off. The reference and regulators are pulled to ground during shutdown and all switching is stopped. During this state, the supply current is less than 5.0  $\mu$ A. In addition, the BAT, CSP, CSM, and SW pins go to high impedance to minimize current drain from the battery.

# UVLO

Undervoltage lock-out, UVLO, is included in the ADP3808A to ensure proper startup. As  $V_{CC}$  rises above 1.0 V, the regulator tracks  $V_{CC}$  until it reaches its final voltage. However, the rest of the circuitry is held off by the UVLO comparator. The UVLO comparator monitors the regulator to ensure that it is above 5.0 V before turning on the main charger circuitry. This occurs when  $V_{CC}$  reaches 9.5 V. Monitoring the regulator outputs makes sure that the charger circuitry and driver stage have sufficient voltage to operate normally. The UVLO comparator includes 600 mV of hysteresis to prevent oscillations near the threshold.

### Loop Feed Forward

As the startup sequence discussion shows, the response time at COMP is slowed by the large compensation capacitor. To speed up the response, two comparators can quickly feed forward around the normal control loop and pull the COMP node down to limit any overshoot in either short-circuit or overvoltage conditions. The overvoltage comparator has a trip point set to 35% higher than the final battery voltage. The overcurrent comparator threshold is set to 100 mV across the CS pins. When these comparators are tripped, a normal soft–start sequence is initiated. The overvoltage comparator is valuable when the battery is removed during charging. In this case, the current in the inductor causes the output voltage to spike up, and the comparator limits the maximum voltage. Neither of these comparators affects the loop under normal charging conditions.

# **Application Information**

# **Design Procedure**

Refer to Figure 15, the typical application circuit, for the following description. The design follows that of a buck converter. With Li-Ion cells it is important to have a regulator with accurate output voltage control.

# **Battery Voltage Settings**

# Inductor Selection

Usually the inductor is chosen based on the assumption that the inductor ripple current is  $\pm 15\%$  of the maximum output dc current at maximum input voltage. As long as the inductor used has a value close to this, the system should work fine. The final choice affects the trade–offs between cost, size, and efficiency. For example, the lower the inductance, the size is smaller but ripple current is higher. This situation, if taken too far, leads to higher ac losses in the core and the windings. Conversely, a higher inductance results in lower ripple current and smaller output filter capacitors, but the transient response will be slower. With these considerations, the required inductance can be calculated using Equation 5.

$$L1 = \frac{V_{\text{IN, MAX}} - V_{\text{BAT}}}{\Delta I} \times D_{\text{MIN}} \times T_{\text{S}} \qquad (\text{eq. 5})$$

where the maximum input voltage  $V_{IN, MAX}$  is used with the minimum duty ratio  $D_{MIN}$ . The duty ratio is defined as the ratio of the output voltage to the input voltage,  $V_{BAT}/V_{IN}$ . The ripple current is calculated using Equation 6.

$$\Delta I = 0.3 \times I_{BAT, MAX}$$

(eq. 6)

The maximum peak-to-peak ripple is 30%, that is 0.3, and maximum battery current,  $I_{BAT, MAX}$ , is used.

For example, with  $V_{IN, MAX} = 19$  V,  $V_{BAT} = 12.6$  V,  $I_{BAT}$ ,  $_{MAX} = 3.0$  A, and  $T_S = 4 \mu s$ , the value of L1 is calculated as 18.9  $\mu$ H. Choosing the closest standard value gives L1 = 22  $\mu$ H.

# **Output Capacitor Selection**

An output capacitor is needed in the charger circuit to absorb the switching frequency ripple current and smooth the output voltage. The rms value of the output ripple current is given by:

$$I_{rms} = \frac{V_{IN, MAX}}{f L 1 \sqrt{12}} D(1 - D)$$

(eq. 7)

The maximum value occurs when the duty cycle is 0.5. Thus,

$$V_{\rm rms\_MAX} = 0.072 \frac{V_{\rm IN, MAX}}{f \, L1} \qquad (eq. 8)$$

For an input voltage of 19 V and a 22 uH inductance, the maximum rms current is 0.26 A. A typical 10  $\mu$ F or 22  $\mu$ F ceramic capacitor is a good choice to absorb this current.

# Input Capacitor Ripple

As is the case with a normal buck converter, the pulse current at the input has a high rms component. Therefore, because the input capacitor has to absorb this current ripple, it must have an appropriate rms current rating. The maximum input rms current is given by

$$I_{rms} = \frac{P_{BAT}}{\eta \times DV_{IN}} \times \frac{\sqrt{D(1-D)}}{D}$$

(eq. 9)

where  $\eta$  is the estimated converter efficiency (approximately 90%, 0.9) and P<sub>BAT</sub> is the maximum battery power consumed.

This is a worst-case calculation and, depending on total charge time, the calculated number could be relaxed. Consult the capacitor manufacturer for further technical information.

# Decoupling the $V_{CC}\ensuremath{\mathsf{Pin}}$

It is a good idea to use an RC filter (R13 and C14) from the input voltage to the IC both to filter out switching noise and to supply bypass to the chip. During layout, this capacitor should be placed as close to the IC as possible. Values between 0.1  $\mu$ F and 2.2  $\mu$ F are recommended.

# **Current Sense Filtering**

During normal circuit operation, the current sense signals can have high frequency transients that need filtering to ensure proper operation. In the case of the CSP and CSM inputs, Resistor R4 is set to 510  $\Omega$  and the filter capacitor C13 is 22 nF. For the system current sense filter on SYSP, SYSM, R2 is set to 510  $\Omega$ , C1 is 2.2  $\mu$ F.

# **MOSFET Selection**

One of the features of the ADP3808A is that it allows use of a high-side NMOS switch instead of a more costly PMOS device. The converter also uses synchronous rectification for optimal efficiency. To use a high-side NMOS, an internal bootstrap regulator automatically generates a 5.25 V supply across C10.

Maximum output current determines the  $R_{DS(ON)}$  requirement for the two power MOSFETs. When the ADP3808A is operating in continuous mode, the simplifying assumption can be made that one of the two MOSFETs is always conducting the load current. The power dissipation for each MOSFET is given by:

Upper MOSFET:

$$P_{\text{DISS}} = R_{\text{DS(ON)}} \times \left(I_{\text{BAT}} \times \sqrt{D}\right)^2 + V_{\text{IN}} \times I_{\text{BAT}} \times \sqrt{D} \times T_{\text{SW}} \times f \qquad (\text{eq. 10})$$

Lower MOSFET:

$$\begin{split} \mathsf{P}_{\mathsf{DISS}} &= \mathsf{R}_{\mathsf{DS}(\mathsf{ON})} \times \left(\mathsf{I}_{\mathsf{BAT}} \times \sqrt{\mathsf{D}}\right)^2 + \mathsf{V}_{\mathsf{IN}} \times \\ \left(\mathsf{I}_{\mathsf{BAT}} \times \sqrt{\mathsf{1}} - \mathsf{D}\right)^2 \times \mathsf{T}_{\mathsf{SW}} \times f \end{split} \tag{eq. 11}$$

where f is the switching frequency and  $t_{SW}$  is the switch transition time, usually 10 ns.

The first term accounts for conduction losses while the second term estimates switching losses. Using these equations and the manufacturer's data sheets, the proper device can be selected.

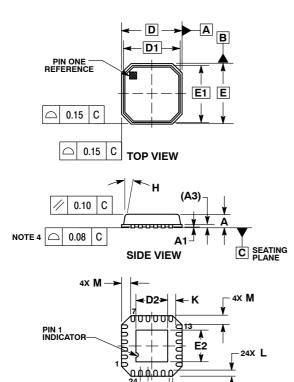

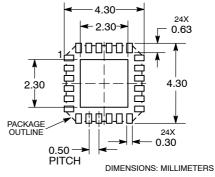

# **PACKAGE DIMENSIONS**

LFCSP24 4x4, 0.5P CASE 932AG-01 **ISSUE O**

e

**BOTTOM VIEW**

h 24X

> ¢ 0.05 С NOTE 3

0.10

С AB 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSIONS: MILLIMETERS. 2

NOTES:

- DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN З.

- 0.15 AND 0.30mm FROM THE TERMINAL TIP. COPLANARITY APPLIES TO THE EXPOSED 4 PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| A3  | 0.20        | REF  |  |

| b   | 0.18        | 0.30 |  |

| D   | 4.00 BSC    |      |  |

| D1  | 3.75 BSC    |      |  |

| D2  | 1.95        | 2.25 |  |

| Е   | 4.00 BSC    |      |  |

| E1  | 3.75        | BSC  |  |

| E2  | 1.95        | 2.25 |  |

| е   | 0.50 BSC    |      |  |

| н   | 12°         |      |  |

| к   | 0.20        |      |  |

| L   | 0.30        | 0.50 |  |

| М   |             | 0.60 |  |

### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILIC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILIC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILIC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILIC obsent or any liability nor the rights of others. SCILIC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications are specified to the SCILIC of the S intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

ADP3808A/D