# High-Side SmartFETs with Analog Current Sense

# AND9733/D

# INTRODUCTION AND SCOPE

This application note describes the structure and design philosophy of onsemi High Side SmartFETs, and serves as a guide to understand the operation of the device in specific applications. The scope of this document is limited to SmartFETs with analog current sense output. The following section covers the application details and behavior of specific application loads. This is followed by Section Power FET and Protection that provides details on the physical structure of the power element- the vertical power FET and different technologies employed to realize the power FET. This section also includes the protection features incorporated within the device that enable it to protect itself in case a system failure condition exists. Section Application interface and control describes the application interface to the SmartFET and provides recommendations for the peripheral circuit for the desired operation. The switching characteristics of the device while driving typical automotive loads are explained in Section Switching Characteristics

The subsequent section elaborates the operation of the analog current sense and fault reporting through the diagnostic output multiplexed with the current sense output. Since the fault flagging conditions could be different for different devices in the family, it is always recommended to refer to individual product datasheets for the specific diagnostic truth table. This document encompasses the typically observed fault conditions and describes the behavior of device and expected the current sense operation for those faults. Finally, the last section provides an understanding of the thermal response of the device and also outlines the interpretation of thermal data and curves published in the product datasheets. This would help in designing the correct application heat sinking and PCB layout to obtain the optimal thermal performance from the device.

The document also provides specific examples and numerical calculations while explaining certain concepts. It should be noted that unless otherwise mentioned, the values mentioned in these examples should be considered only typical and not defining any bounds on the performance of the device. For all maximum ratings, the respective product datasheets should be referred. In addition, any layouts or circuit blocks depicted in this document are exemplary and do not necessarily represent an actual die or a real circuit schematic drawing of a specific device. Lastly, the waveforms have been idealized to explain the behavior of device inputs/outputs under certain scenarios.

# **APPLICATION SYSTEM OVERVIEW**

The design flow for any device initiates with a holistic understanding of the target application environment followed by specification creation around the required performance in application. The close interaction with application and an intricate dependence (of a device's performance) on external conditions necessitate adopting a system level approach for a design guide. Therefore, before discussing the device specifics, it is imperative to understand the application environment, behavior of typical loads and their interaction with the high side switches.

# Smart High Side Switches – Motivation

The "end requirement" from a high side SmartFET is to switch loads, and there are different alternatives, available in market, towards that end. Relays, for instance, have been used for long in the industry to switch various automotive loads, especially those requiring high current activation. With a continual reduction in the weight and size of automotive components and assemblies, there has been an evident transition from relays to semiconductor switches that take up less area and also offer improved noise immunity and lower electromagnetic interference as compared to relays.

A p-n junction diode is an easy to use semiconductor switch that solves the basic requirement of switching. However, the power dissipations and high conduction losses do not render them as a viable alternative in the modern automotive environment with aggressive target specs on improving efficiency and cutting down system losses. Further, the bipolar nature of the conduction element involves minority carrier injection and extraction during switching that limits the speed in application. Devices like SCR's (Silicon controlled rectifiers) and triacs also face similar challenges. Bipolar transistors have high output current drive capabilities and lower conduction losses (than diodes) but require an input current drive that makes them undesirable as a switching element. They are widely used in semiconductor industry, however, for bandgap generation and voltage regulation purposes. Applications requiring high voltage breakdown with a reasonably high output current drive, such as fuel ignition, typically employ IGBTs as the switching element. Since the output stage in an IGBT is bipolar, the minority carrier extraction, as for any p-n junction, limits the turn-on/turn-off rates. With a focus on all the performance metrics discussed above, a FET is the most likely and widely used candidate for switching automotive loads. Ease of input drive, high input

impedance, fast switching and a wide SOA (Safe Operating Area) help in achieving the optimal switching performance.

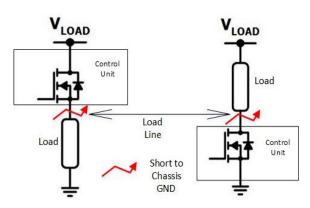

Figure 1 depicts two of many topologies used for switching loads in an application. With a high side switch, the load is always connected to the ground and the connection to the supply is switched; with a low side switch, the load is always connected to the power supply and the connection to GND is switched. The switch is typically housed inside a control unit or, ECU. The load line is the cable length that connects the load to the pin connector on the ECU. Depending on the load type and its location in the vehicle, this load line could be fairly long, thereby, increasing the likelihood of a short to chassis ground which could be a severely stressful condition for the load in a low-side configuration. This makes the high side switches a preferred choice for load switching. In addition, in cases where a parasitic impedance path to GND exists in the system (as would be described in later sections that temperature and humidity can create leakage resistances over time), the leakage levels are higher in a low side configuration where power supply is always connected to the load. With the advancement in charge pump design and technology, it is relatively convenient to integrate charge pump with the power element, enabling N-channel FETs to be used in high side configuration in a small chip size.

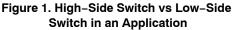

Some applications also use an H–Bridge switching configuration to drive bi–directional loads– for example, a door lock/unlock motor. An H–bridge utilizes two pairs of high side and low side switches as shown below:

Figure 2. H–Bridge Switching Configuration

With the increasing complexity in application (to render more features available to the user), the probability of a system failure condition also increases. This requires the switch to protect itself in case of operation outside the intended regime, most likely due to a system failure condition (such as output short circuit to GND) existing. From a cost point of view, adding smarts to a switch eliminates the cost of replacement (in certain safety critical applications, the whole module needs to be replaced in case a device fails) and reduces the system cost over an extended period. While adding control and logic features to the power FET, due care has to be exercised in the device design stage to ensure the required module reliability.

## **Hide Side SmartFET Solutions**

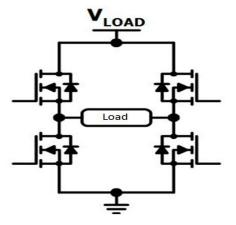

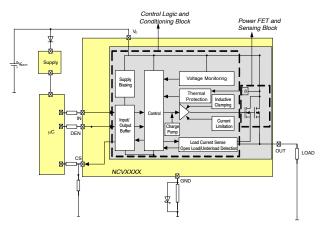

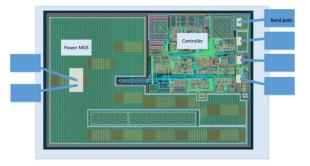

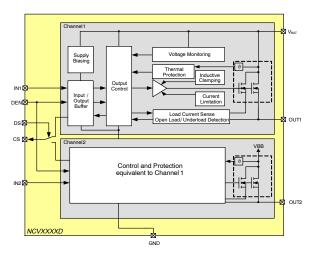

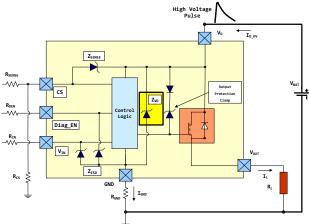

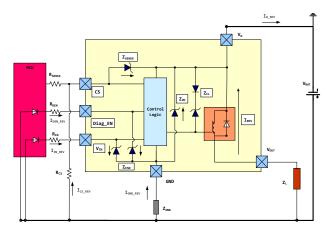

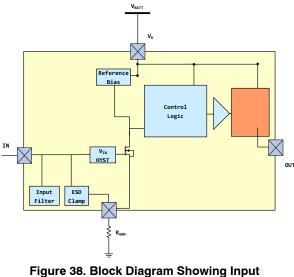

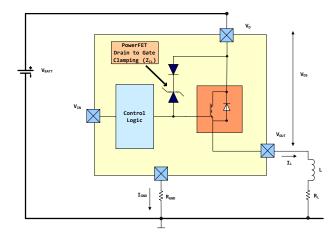

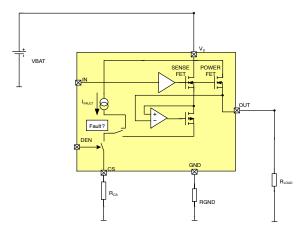

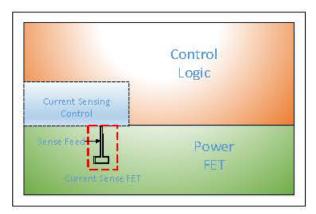

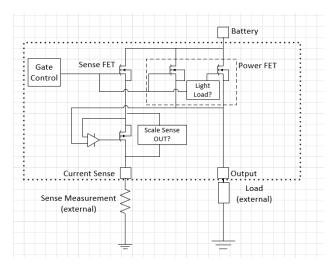

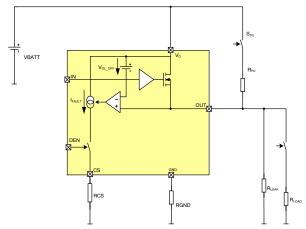

**onsemi** High Side SmartFETs are offered in monolithic or dual die solutions. Figure 3 highlights, in dashed rectangles, the two sections of a SmartFET– the control circuit (consisting both analog, digital controls and the charge pump) and a power section (consisting the power DMOS and sense elements for temperature and current sensing). In a monolithic solution, as the name suggests, both these sections are integrated on the same substrate while in a dual die solution, these two sections are realized on two different substrates and connected with inter–die bonds. The relative orientation and integration of the two dies depends on required package dimensions and device's long term reliability. Section Monolithic vs Dual Die Technology provides a detailed description of these solutions along with their benefits and drawbacks.

# AND9733/D

Figure 3. Block Diagram Highlighting the Power FET And The Control Section

Within the power FET section, the technology can vary between a planar and a trench gate stack for the vertical DMOS (Refer Section Planar vs Trench FET). The choice of solution for a particular device is primarily governed by the normalized on state resistance targeted in a given package (a trench FET, in general, will have a lower on-state resistance than a planar FET for a given silicon area) while considering other factors including, but not limited to, required output current drive and sense capability, and the thermal response of the die (Refer Section Understanding the Thermal Network for details on the thermal behavior). In addition, manufacturability and process costs are also considered before determining the technology for a given device. onsemi High Side SmartFETs are designed considering that the performance parameters, protection and diagnostic feature set, and the desired operation in application are not affected by the underlying technology.

It should be highlighted here that some high-side SmartFETs are equipped with one-time programmable trims (OTP) in the form of an array of fuses that are programmed at the end of production line. The "trimming" process starts by evaluating the performance of "untrimmed" devices first. Based on any deviation from the desired spec, these trims (or fuses), then serve as inputs to the control logic, which subsequently alters the performance on silicon to closely align it with the spec. Implementing such a sequence allows for an improved tolerance on timing and protection parameters such as the short circuit current limit, switching times etc.; reduces device-to-device variability; and provides an enhanced design flexibility. The trim structures realized on the die undergo the required reliability stress and are ensured to adhere to lifetime operation standards. The devices with trim capability can only be programmed at the end of the production line and are not offered to be programmed in field by the customers for safety concerns. Effect of trims on the product performance will be discussed individually for specific blocks and parameters through this document.

## Application Environment and Loads

The automotive application environment is vastly different and typically more aggressive in requirements than other applications like industrial, consumer etc. Standards including AEC–Q100 require automotive switches to adhere to a minimum standard of quality, reliability and robustness under extremes of ambient variations (temperature, pressure humidity etc.).

Consider, for example, a scenario of switching a bulb load. As will be described later in this section, incandescent lamps require an inrush current at turn-on, which is higher than the nominal drive current. The bulb load in this example is an H4 type headlamp rated for a nominal power of 55 W at 12.8 V. The inrush current required at an ambient temperature of ~300 K (27 °C) is ~75 Amp. The cable lengths in automotive environments can be long, and consequently the cable resistance can be significant. For a cable impedance of 20 m $\Omega$ , the inrush results in a ~1.5 V drop across the cable for a few milliseconds, (until the bulb is sufficiently turned on). Further, a typical connection to the supply in an automotive environment is switched through protection relays and fuses (housed inside the junction box). These may also present impedance to the inrush and limit the voltage swing available for the operation of high side switch. It is assumed (in this hypothetical case) that this drop is  $\sim$  1V. In addition to losses in the supply line, there are losses in the GND line as well. Modules, in automotive environment, are connected to chassis GND through a resistive network for protection purposes. This network adds to the losses, averaged to ~1V for this example. This implies that losses in the automotive application could easily lead to a 20~25% drop in the supply voltage at a nominal  $V_{BATT} = 14$  V for a readily observed situation of a headlamp turn-on. The high side switch should be able to operate under reduced battery voltages. It should be noted that "operation" in this regard encompasses a fully turned on charge pump, available protection for current limitation (if required) during inrush and a complete diagnosis feature set. Now, consider a bulb turn-on at cold ambient temperatures. At low temperatures, the battery voltage will further droop and the inrush required for the lamp turn on will increase- both these factors create a stringent environment for switch operation. All onsemi high-side SmartFETs typically operate well down to 8 V and certain devices also spec an extended battery voltage down to 4.5 V (Refer to specific product datasheets for low voltage operation). Section Under-Voltage Operation describes the LV124 spec and under-voltage behavior.

While the above discussion is focused more on droops in the battery voltage, transient overshoots in the supply voltage are also seldom observed in automotive applications- especially in cases like a jump start, or an alternator load dump (Refer to Section Over-Voltage Protection for details). The high-side switch should be able to protect itself against such events. In case the load is

# AND9733/D

switched repetitively in a PWM operation, for instance considering the bulb load again where the intensity of light is controlled with a PWM drive, the controller should modulate the RMS voltage across the bulb (by modulating the PWM duty cycle) to minimize fluctuations in the intensity. Another key consideration with the automotive environment is the EMI performance in the system. With increasing electronics content in the modern day automotive applications, every component should be designed while guaranteeing conformance to the required EMI/EMC standards and minimizing the cross-coupled noise both internal and external to an application.

The switching characteristics of a high side SmartFET, therefore, should account for EMI implications as well, in addition to losses. In multi–channel devices, there should be no interference between channels, especially when one channel is reading fault state.

As discussed before, that chassis in an automotive application is considered as system GND, the high side switch should be robust enough to handle and protect itself in case of an output shorted to GND (a highly likely system fault condition in high-side applications). This is usually achieved by limiting the load current and incorporating thermal shutdown (Refer section Short Circuit OUT to GND-Current Limitation and Temperature/Power Limitation for details) in the device. AEC-Q100-012 (Refer [4]) describes the typical automotive short circuit condition set and also quantifies the performance of a device (in terms of number of cycles) against a short circuit event.

The calculations and estimated losses presented in this section above are exemplary and should not be extended as a representative of generic automotive condition set. In general, cable dimensions (and associated losses), power supply distribution fuse/relay specs, ground connections etc. are all OEM dependent, and OEM specifications should be referred to while making a selection for a high–side switch in an application.

#### Resistive Loads

Typical resistive loads in automotive applications comprise (but are not limited to) LEDs, heating elements in seats, transmission and engine management systems, airbag squibs, air flow sensors etc. LEDs, or Light Emitting Diodes are current controlled loads, –in other words the light output is directly proportional to the drive current, or the input electrical energy. The operation of an LED is very similar to that of any diode; except for the semiconductor material employed for fabrication that emits photons on electronic excitation (quantum of light) instead of phonons (quantum of mechanical vibration) – as in a Si diode. The color output depends primarily on the energy band–gap of the starting material (Refer [1]).

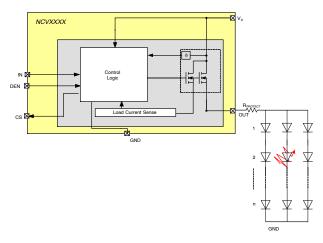

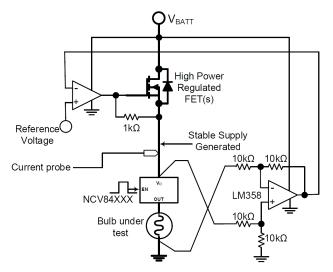

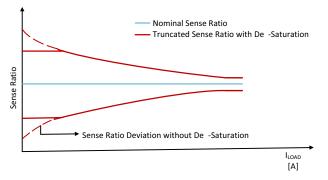

The input drive circuit is controlled through either current regulation or voltage regulation across the LED load. A current is usually limited by stacking multiple arrays of LEDs (within a module) in parallel and adding a limiting resistor in series with the array. A voltage regulation, on the other hand, is typically achieved with DC-DC conversion stages that bring down the voltage required for turning on an array. Figure 4 depicts a parallel cluster of LEDs driven by a high side SmartFET. Each array has n number of LEDs in series. RPROTECT limits the current through the cluster. In case one LED goes faulty and reads open circuit (as highlighted in red in Figure 4), the other arrays will still operate and conduct. The current through the load module, however, will change and the high side SmartFET should be able to indicate this change through analog current sense read-out. Since typical automotive LED loads are driven at low current levels of the order of a few mill- amperes (Refer Figure 5), it is challenging to precisely reflect the small change in current and thereby diagnose an open circuit of a particular LED string. As will be discussed in Current Sense and Diagnostic, the current sense accuracy reduces at small load currents; different design schemes have been implemented in onsemi High Side SmartFETs to improve sense accuracy (Refer section Current Sense De-Saturation at Light Loads).

## Figure 4. High Side Switch Driving a Parallel Cluster LED Array

Most automotive applications employ a PWM drive scheme to modulate the intensity of output light; the switching characteristics of the high–side switch should be compatible with the application's PWM requirements. Resistive Switching provides the details on LED switching.

LEDs have been gradually replacing the traditional incandescent sources of light for both vehicles' interior and exterior lighting applications. High energy efficiency (proportional conversion of electrical energy into light), better light output (output light is more directional/anisotropic as compared to bulbs that have a diffused output spectrum), ease of drivability (LEDs typically require a low input power and a drive circuit with minimum complexity) and a longer operating life (LEDs do not comprise of a filament, or any internal component that may fatigue over time) are the primary motivations driving OEMs towards LED loads as a viable alternative for automotive lighting. A few shortcomings, for instance, the

high initial cost and challenges in achieving an efficient thermal management (especially for applications like headlight) still need to be addressed. Figure 5 summarizes the typical automotive LED applications and their drive requirements.

| Location | a Application Drive Current (Low/M |                 |  |

|----------|------------------------------------|-----------------|--|

|          | Center High Mount Stop Lamp        | Low (<100mA)    |  |

|          | Side View Mirror                   | Low (<100mA)    |  |

|          | Side Markers                       | Low (<100mA)    |  |

|          | License Plate Lamp                 | Low (<100mA)    |  |

| Exterior | Rear Combination Lamps             | Med (200~500mA) |  |

|          | Turn Signal                        | Med (200~500mA) |  |

|          | DRL                                | Med (200~500mA) |  |

|          | Head Lights                        | High(>500mA)    |  |

|          | Fog Lights                         | High(>500mA)    |  |

|          | Colored RGB Lighting               |                 |  |

| Interior | (Including ambient lighting,       |                 |  |

|          | instrument cluster lighting, LCD   | Low (<100mA)    |  |

|          | Backlighting, Switches, Front      |                 |  |

|          | Panel (Clock etc.) )               |                 |  |

|          | Map/Dome Lights                    | Med (200~500mA) |  |

## Figure 5. Typical Automotive Applications Utilizing LEDs

# Inductive Loads

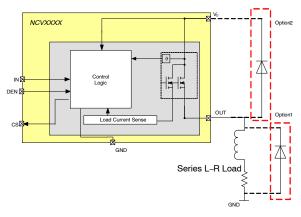

Inductive loads mostly include different motors in applications such as wipers, starters, door modules, HVAC, fuel injectors, electric power steering, throttle control etc. In addition, there are relays used in engine and body control applications. While driving inductive loads, the primary concern is to limit the magnitude of the output voltage when the inductor begins to discharge. All onsemi High Side SmartFETs have an integrated protection clamp for this purpose. The mechanism of active clamping is explained in section Inductive Switching. Another concern with the inductive loads is the inductive discharge energy capability of the high side SmartFET. The product datasheets specify the single pulse and repetitive pulse energy capability across a range of inductors at defined starting ambient temperatures (Refer section Inductive Switching for equations describing the energy dissipation in the high side switch). Exceeding the energy rating may irreversibly damage the device. The protection features will not be active once the input command is turned to trigger inductive flyback.

To protect the device from high energy dumps during inductive discharge, some applications employ a free-wheeling diode and external clamping. Figure 6 shows two such options marked inside the dashed red rectangles. A series L-R load is depicted because all inductive loads have an associated parasitic resistance. While paralleling across the load, the available voltage to discharge the inductor is just a diode drop, which may lead to a prolonged discharge. The clamp voltage in the second option will depend on the breakdown of the external diode (the breakdown should be lower than that of the integrated clamps within the device). In both cases, the diode should be capable of handling the power dumped in the inductive discharge. While implementing these designs, extra components may be required to protect against reverse battery conduction, overvoltage scenarios etc.

It should be noted that the clamping schemes described above are only indicative. Other circuit configurations with external clamping may also be used. However, detailed calculations of power handling capabilities of the external components, analysis of protection during reverse battery and overvoltage situations as well as estimation of the associated leakage levels should be done before employing these topologies.

# Bulb Loads

An incandescent bulb is very different in operation than the LED light sources discussed in section Resistive Loads. The bulb comprises of a tungsten filament in a glass enclosure filled with inert gases such as argon or xenon, for instance. The contact wires carry current in and out of the filament supported by mounts and caps for mechanical support and casing. When an electric current is forced through the tungsten filament, the temperature of the filament increases and eventually it starts to glow thus emitting light. Most of the input electrical energy is converted into heat and rest is converted into light. The light conversion efficiency of incandescent lamps is inferior to that in other light sources like LEDs, CFLs etc. However, a low cost of manufacturing and availability across different power ratings make it the most widely used light source in the present day automotive applications.

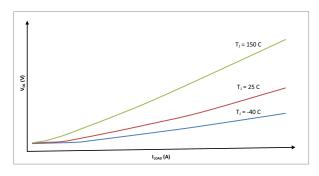

The electrical behavior of a bulb is capacitive, with the high current required in the beginning for heating the filament gradually decaying to a nominal current required for operation. This initial high current is called the bulb inrush. The resistance presented by a "cold" bulb (the term cold describes the initial turn on, or the inrush) is lower than that in a steady state operation. The steady state resistance depends on the desired final filament temperature (For most bulbs, the desired filament temperature is 2900~3200 K). Describing the closed loop electro–thermal operation of a bulb: On the application of an electrical voltage source, the current across the bulb depends on the dynamic resistivity of

the filament (which is a function of temperature). The instantaneous temperature of the filament depends on its thermal resistance (and the thermal resistance of the contacts) and the input power (which in-turn depends on instantaneous current), thereby making it an iterative model. There are various models that predict this closed loop resistivity profiles using look-up tables or empirical equations (Refer [2]).

Typically, automotive lamps specify a rated power at a nominal voltage. The nominal resistance of the filament can be calculated as:

$$R_{NOM} = \frac{V_{NOM}^2}{P_{NOM}}$$

(eq. 1)

where  $V_{NOM}$  and  $P_{NOM}$  are the rated voltage and power.

Based on empirical data, the dynamic resistance can be estimated as a function of instantaneous temperature using an "inrush factor":

$$R(T) = R_{NOM} \cdot \left(\frac{T_{REF}}{T}\right)^{const}$$

(eq. 2)

T is the instantaneous filament temperature,  $T_{REF}$  is the desired filament temperature and "*const*" is an empirical constant (Refer [3]). The latter part of the multiplier in Eq. 2 is the inverse inrush factor. The inrush current profile can be simulated using the dynamic resistance profile assuming a known stable voltage across the bulb.

Figure 7 below lists the applications widely using incandescent bulbs along with the rated power of the bulbs.

| S.No | Application                          | Rated Wattage                                                                                                                                                         |  |

|------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | Front Light (High Beam and Low Beam) | 51W; 55W;60W;65W;60/55W*                                                                                                                                              |  |

| 2    | Parking Light                        | Front: 4W; 5W; 6W<br>Rear: 10W; 21/5W*, 21/4W*<br>Door Integrated: 4W; 5W<br>Front and Rear: 21W<br>16W; 21W<br>21W<br>CHM: 5W;16W<br>Rear: 21W; 21/4W*; 21/5W*<br>5W |  |

| 3    | Turn Signal Lights                   |                                                                                                                                                                       |  |

| 4    | Reverse Lights                       |                                                                                                                                                                       |  |

| 5    | Warning Lights                       |                                                                                                                                                                       |  |

| 6    | Brake Lights                         |                                                                                                                                                                       |  |

| 7    | Trunk Light                          |                                                                                                                                                                       |  |

| 8    | Fog Lights                           | Front: 55W; 35W<br>Rear: 21W                                                                                                                                          |  |

| 9    | Interior Lights                      | 3W; 5W; 10W; 15W; 18W                                                                                                                                                 |  |

| 10   | License Plate Lights                 | 4W; 5W                                                                                                                                                                |  |

| 11   | Daytime Running Light                | 35W; 55W                                                                                                                                                              |  |

Figure 7. Typical Automotive Applications Utilizing Incandescent Bulbs

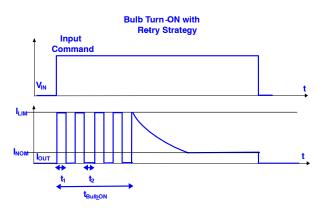

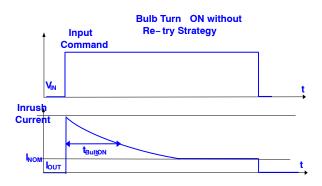

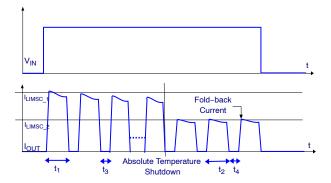

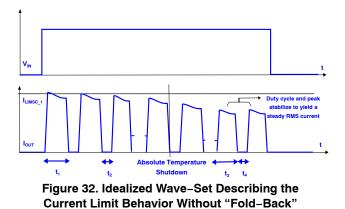

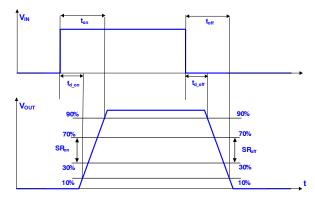

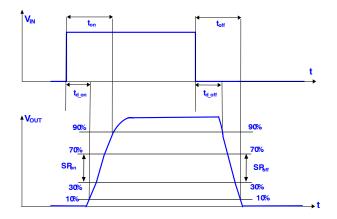

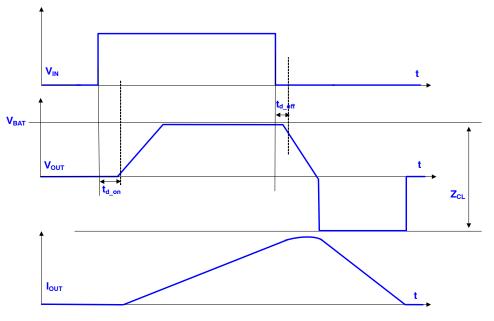

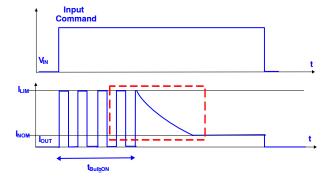

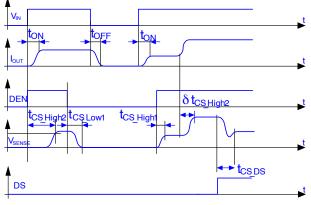

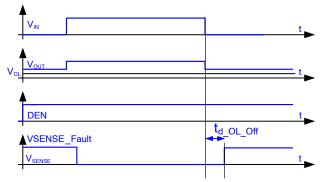

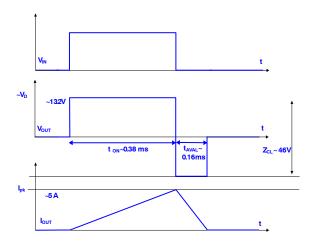

It is critical to understand the output current drive capability of the high side switch with respect to the inrush profile required for the application bulb. **onsemi** High Side SmartFETs are equipped with the current limitation feature to protect themselves in case of overload situations (Refer section Short Circuit OUT to GND-Current Limitation). Extended operation at the current limit forces the device to repeatedly turn off and on because of the thermal shutdown mechanisms (Refer section Temperature/Power Limitation). While such protection is desirable to limit the transient thermal stresses in case of system failure conditions such as output short circuit to GND, the bulb turn-on characteristics are impacted if the inrush required for the bulb turn-on is greater than the internal current limit. In such case, the device attempts to turn on the bulb with a re-try strategy (refer section Re-try Strategy). The idealized wave-set in Figure 8 and Figure 9 depicts the bulb turn-on scenario with and without the re-try strategy.

Figure 8. Bulb Turn-On With Retry Strategy

Figure 9. Bulb Turn-On Without Retry Strategy

Referring to the waveforms above, t<sub>Bulb ON</sub> is the time required to turn on the bulb- in most cases, it is the time interval in which the instantaneous current drops to  $\sim 0.5^*$ peak inrush current. The specifications for this parameter are OEM dependent. With internal current limitation, t<sub>Bulb ON</sub> increases as the device toggles in and out of differential thermal shutdown. The root mean squared current over the ILIM cycles and the consequential power at the beginning of the last re-try should result in an equivalent electro-thermal resistance profile (of the bulb) as in the case with no re-try after a period of t<sub>Bulb</sub> ON. While selecting a device for an application, it should be considered that t<sub>Bulb</sub> ON in the worst case condition (typically in case of low ambient temperatures when a high inrush is required at low available battery voltages) should be within the limits defined by the OEM. Measured maximum inrush currents for certain standard automotive bulb loads have been tabulated in Figure 10. Measurements were performed by forcing a stable differential voltage of ~12.8 V across the

bulb (For an accurate inrush profile, the voltage across the bulb should be stable, any parasitic resistive drops in the measurement system may yield a low inrush current because of a reduction in the voltage available to turn the bulb on). The maximum inrush depends on the electrical specifications (primarily, electrical wattage) and the physical construction of the bulb. The injected power in the bulb is dissipated as conducted power across the filament and the radiated power. The physical structure of the bulb determines the distribution of power and thereby also impacts the instantaneous temperature and inrush profiles.

| Bulb | Spec<br>Voltage (V) | Spec<br>Power (W) | Max Inrush @<br>25C (Amp) | Max Inrush @<br>-40C (Amp) |

|------|---------------------|-------------------|---------------------------|----------------------------|

| W3W  | 12                  | 3                 | 2.24                      | 2.95                       |

| T4W  | 12                  | 4                 | 3.69                      | 4.77                       |

| R5W  | 12                  | 5                 | 4.51                      | 5.79                       |

| H6W  | 12                  | 6                 | 7.46                      | 9.83                       |

| R10W | 12                  | 10                | 9.81                      | 12.77                      |

| P21W | 12                  | 21                | 23.64                     | 31.67                      |

| P27W | 12.8                | 26.9              | 22.01                     | 28.75                      |

| H1   | 12.8                | 55                | 63.67                     | 82.73                      |

| H4   | 12.8                | 55                | 71.77                     | 89.80                      |

| H7   | 12.8                | 55                | 62.99                     | 81.68                      |

| HB2  | 12                  | 60/55             | 78.30/70.07               | 98.75/90.19                |

| HB3  | 12                  | 60                | 72.00                     | 92.41                      |

| H9   | 12                  | 65                | 70.50                     | 91.03                      |

## Figure 10. Measured Maximum Inrush For Typical Automotive Bulbs @ V ~ 12.8 V

It should be noted that measured bulb inrush are only typical and do not represent the extremes of variations in the bulb performance. In addition, the inrush profiles may vary across bulb manufacturers. Devices recommendations (against specific bulbs) can be provided on customer requests.

# Relay and Fuse Replacements

There has been evident focus on component weight and size reduction in all automotive applications in order to achieve higher system efficiency. Also, with extensive electrification in vehicles, there has been a growing requirement to replace existing switching and protection components with solid state solutions. Towards this objective, various onsemi High Side SmartFETs are targeted at replacing application relays (relays are usually heavier and consume a significant area on the PCB). It is recommended to refer to the product datasheets for specific suitable applications. In addition, the ultra-low ohmic devices (with typical R<sub>DS(ON)</sub>, for instance, between 0.5~3 m $\Omega$ ) are targeted to replace protection fuses and offer an E-fuse solution. The smart high side switch creates a closed loop protection scheme with fault reporting and the integrated protection features protect the E-fuse from getting damaged- thereby reducing the replacement cost (over vehicle's lifetime) associated with the fuses.

While the relay and fuse replacing SmartFET solutions utilize the standard set of features available across the portfolio, there are some key application requirements that differentiates the design approach for these SmartFETs from those switching other conventional loads such as lighting, or resistive elements. A few instances of these differentiating requirements include the difference in retry strategy in case of a short circuit to ground, current sense ratio specs, operating temperature range, number of output channels, reverse battery protection, slew rates etc. Most of these requirements would be discussed individually in the respective sections to highlight the required adaptability in design as the market impetus shifts progressively towards power distribution using smart switches.

# **Functional Safety Overview:**

With the advent of smart switches in more safety critical applications such as SRS (Secondary Restraint Systems, including airbags, pre-tensioners and braking), power distribution and transmission, among others, due consideration and adherence to functional safety standards has been more important than ever. Standards such as ISO26262 elucidate a designer's approach to incorporate features while conforming to safety functions described in the standard. It should be noted that the emergence and application of these standards is recent which makes it difficult for the semiconductor manufacturers across industry to re-design their products in hindsight. To address this predicament, onsemi provides product specific (on customer request) Failure Mode Distribution Analysis, design and package specific FIT rates, and block wise impact on safety functions in the form of an open FMEDA. Further, these FIT rates are provided based on multiple standards-such as IEC 62380, SN29500 etc. understanding that different standards may be employed across customers for analysis. This information helps the customers design the system with the necessary failsafe mechanisms built in for safety critical applications per the desired mission profile over the intended lifetime. For specific functional safety requests, it is recommended to contact the respective field representatives.

# **POWER FET AND PROTECTION**

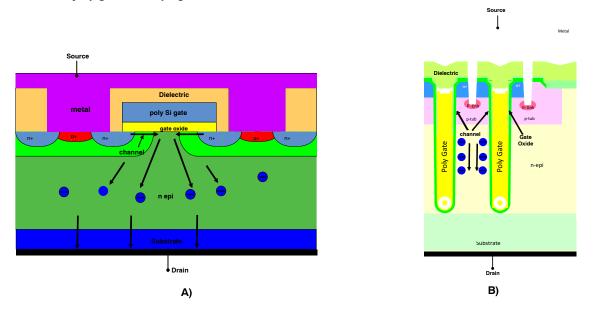

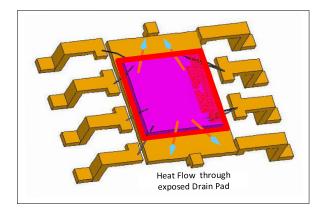

# Power MOSFET

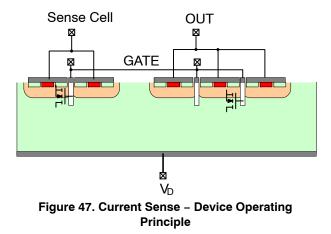

This section describes the structure and different topologies of the power element, or the DMOS. The power element in a high side device is comprised of a large number of vertical N-channel FET cells laid out in parallel with the drain as the substrate for an improved heat spreading and reduced thermal density over the drain area. Optimal design and area considerations of the power FET are critical in determining the key electrical performance metrics including, but not limited to, R<sub>DS(ON)</sub>, max current capability, breakdown voltage, current sensing, temperature sensing etc. Based on technology, parametric requirements and geometrical constraints, a "planar", or a "trench" configuration could be employed in **onsemi**'s high-side SmartFETs. Following is the depiction of the two structural designs.

# Planar vs Trench FET

As discussed above, the vertical power element may be planar, or a trench structure. The terms "planar", and "trench" here, refer to the Gate Stack Structure which consists of the poly gate, underlying oxide and the channel. The former design has a planar, or a lateral gate and channel with near surface channel conduction, while the latter design has a vertical Gate and channel going into the depth of the body (See figures 11 a) and 11 b) for details).

Figure 11. Exemplary Layout Depicting the Gate, Channel and Carrier Flow in a) Planar FET and b) Trench FET

The conventional, or the planar FET is thermally efficient and easy to manufacture with low "mask steps", while the trench counterpart offers a tighter cell pitch (resulting in better specific  $R_{DS(ON)}$ ) yielding the ability to pack more cells within the given chip "real–estate". The following table summarizes the key differences in the two designs, differentiating the performance as Hi (Good), or Lo (Moderate) against a specific characteristic.

| Parameter/Characteristic                       | Planar<br>FET | Trench<br>FET |

|------------------------------------------------|---------------|---------------|

| Specific RDS(on) – m $\Omega$ *mm <sup>2</sup> | Lo            | Hi            |

| Thermal Stability                              | Hi            | Lo            |

| Energy Capability for Similar FET area         | Hi            | Lo            |

| Ease of Manufacturability                      | Hi            | Lo            |

| Cell Pitch                                     |               | Hi            |

| Table 1. PERFORMANCE COMPARISON IN PLANAR |

|-------------------------------------------|

| AND TRENCH VERTICAL POWER FETS            |

# Monolithic vs Dual Die Technology

A monolithic high side device has the power element (vertical N–FET) and the control circuit fabricated on the same substrate/starting Si. The term "dual die", on the other hand, refers to having two separate die for power FET and controller within the same package. A monolithic design renders least mismatch and offsets between the FET and the controller; however, at sufficiently low specific  $R_{DS(ON)}$  levels with a complex control circuitry comprising of analog

and digital sections, it is challenging to monolithically integrate the two elements (FET and controller) within a given package size. This is where technologies like chip-on-chip are utilized to optimize the "package real-estate". Further, the control circuit needs to be fully isolated from the FET using isolation structures. Following (Figure 12) is an exemplary representation of a monolithic high-side device. Bond pads to the controller and power FET, and various sense elements (Temp Sense, Current Sense) are also shown in the die image below.

Figure 12. Representation Of a Monolithic High–Side Smart FET Design

It should also be considered that while most of the high–end SmartFET control circuitry is based on CMOS logic, it is always challenging to incorporate a back side drain technology in a monolithic configuration with isolation between CMOS substrate and back side drain.

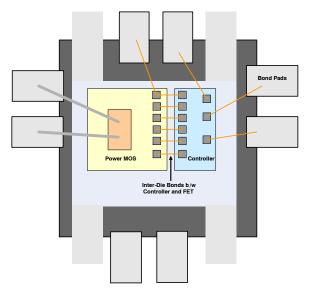

# AND9733/D

A dual-die technology manages the interaction between the FET and control circuit through inter-die bonds which require additional front-end masking, sacrificial die area for bonding, and back-end assembly and processing steps. Because of different starting silicon for the two elements, there are some inherent process mismatches associated with dual-die technology devices. Figure 13 depicts a high level block diagram representation for such technologies.

Figure 13. Representation of a Dual–Die High–Side SmartFET Design

The advantage with this technology is the ease in substitution of FETs with different sizes and  $R_{DS(ON)}$  levels while maintaining the compatibility with the controller across a specific product family.

Depending on the application requirements, and product family segment, **onsemi** High Side SmartFETs could be fabricated on either of these technologies.

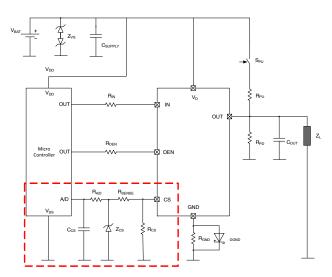

#### Multi-Channel Devices

Some applications require multi-channel devices for operating parallel loads (Refer section Application System Overview). Such devices are required to have independent power N-FETs with identical parametric and behavioral performance. Each power FET, or "channel", has its independent sensing elements, and the diagnostics are typically multiplexed. A challenge with these devices is to isolate the operation of the two channels, especially in case where one of the channels is in a fault condition. Figure 14 below presents a circuit schematic detailing different blocks in a dual channel High-side device, for instance.

Figure 14. Example Circuit Block Diagram for a Dual Channel High–Side SmartFET

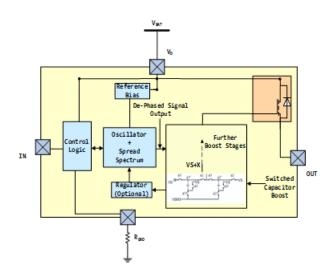

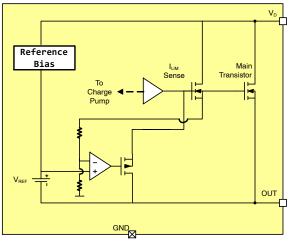

#### **Charge Pump-Principle of Operation**

An efficient charge pump design is extremely critical to achieve the desired performance from a High–Side FET. To make sure the FET is fully turned on in the  $R_{DS(ON)}$  region (of the output characteristic curve), the gate potential needs to be boosted over and above the battery (drain potential) to provide sufficient overdrive to the N–FET. A charge pump, as the name suggests, essentially acts as this boost circuit and ensures maximum  $R_{DS(ON)}$  for a given die area. Though, in a strict definition, a charge pump is integral to the control circuit, however, since its characteristics are directly tied to the performance of the power FET, it is being discussed in this section.

In addition to generating sufficient gate charge, an efficient charge pump must provide a stable gate drive with smooth turn on and turn-off characteristics, and should be realized on a minimum die area. Typical charge pump networks employ stages of switched capacitor boost networks, though; this is not the only method to generate high voltages.

Figure 15 is a block diagram representation of a charge pump operation. Based on the command from the input control circuit, an oscillator produces a set of "de-phased" output signals which then are fed into the boost network as shown in the figure on the right. These signals control the switches and charge the capacitive ladder. The difference in the phases results in accumulation of charge/generation of high voltage at the output of this network.

Figure 15. Charge Pump–Operational Block Diagram

A charge pump output may be regulated to make sure there are no gate voltage overshoots by pulling back on the booster, once the device is closing into complete turn–on. This may increase the time to achieve the full–scale gate overdrive required for the  $R_{DS(On)}$ , but improves the gate control stability and reduces overshoots.

In some devices, oscillator frequency is trimmed in production. This ensures tight tolerance across population around the nominal switching times specified in the datasheet. Different technologies (within the **onsemi** High Side SmartFET product portfolio) may or may not have an internal regulator. Depending on the gate potential required, the boost stages can be cascaded to multiply the charge at each stage.

The internal spread spectrum is used along with the oscillator to suppress any spectral energy spikes produced by the oscillator, and ensures good EMI performance. It should be noted that switching speed of the device is also contingent on the rate at which the charge pump can boost the gate voltage and how fast can the gate be "unloaded". While it is desirable to have a fast charge pump response, it should be designed in a way not to infringe with the EMI requirements.

## **Supply Voltage**

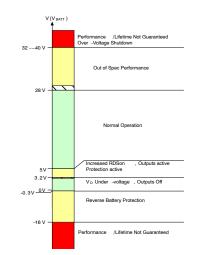

## Typical Supply Voltage Specs

**onsemi** High–Side SmartFETs have been designed to operate across typical battery voltage range for an automotive environment accounting for application variations around the nominal value as described later in this section. The operating voltage range is typically specified as 5 V - 28 V, however, some specific datasheet parameters may be characterized and guaranteed across a narrower range, for instance 8 V to 18 V. The range and the corresponding electrical specs guaranteed will differ across

devices and technologies within the **onsemi** High Side SmartFET portfolio. Following is a depiction of a typical supply voltage spec.

## Figure 16. Device Operation Across Typical Supply Voltage Specification

As described in the chart above, the normal operation is guaranteed (unless otherwise specified in the product datasheet) across a range of 5 V - 28 V. The electrical performance (in terms of typical R<sub>DS(ON)</sub>, switching speeds, current sense etc.) and expected behavior (in terms of protection and diagnostics) may deviate out of spec outside this range. Below the under-voltage threshold, the device turns off and turns back on with a hysteresis. Reverse Battery protection for controller and FET, as described later in this section, is achieved through internal clamping structures and the body diode respectively. Reverse battery threshold for typical devices is -16 V (sustained for a defined time interval), below which, the expected lifetime, reliability and performance may be irreversibly affected. Some devices may employ an over-voltage shutdown feature to prevent the FET and controller from high voltage transients observed during events like a Load Dump; other devices offer over-voltage protection through internal clamp structures, and lifetime/performance of the device may be compromised if operated in this high voltage region. The over-voltage shutdown threshold may be different across devices.

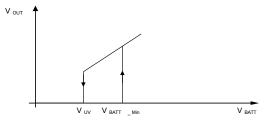

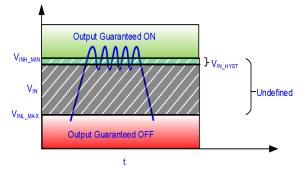

## Under-Voltage Operation

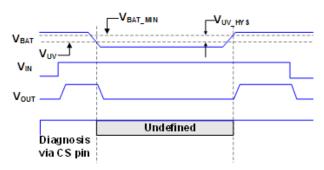

**onsemi** High Side SmartFETs have an under-voltage shutdown mechanism when the supply voltage droops too low to support device operation. This feature also prevents the device from flagging any false/out of spec outputs or diagnostic signals. The under-voltage threshold differs across devices with typical spec in the range of 3 V~ 4 V. An under-voltage shutdown event has an associated hysteresis to prevent aberrant turn on and turn off because of a potential noisy power source in the vicinity of threshold.

Figure 17. Under-Voltage Turn Off With Hysteresis

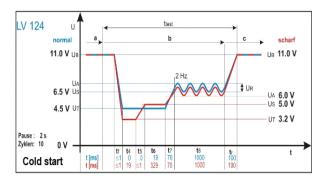

Such low voltage events are most likely observed in an automotive environment in case of cranking (vehicle starting) conditions when the battery voltage can fall to a low value for a brief event before rising eventually. The difficulty is compounded in case of "cold cranking" when the battery voltage further droops at low ambient temperatures. As per the LV 124 automotive spec for electrical and electronic components in motor vehicles up to 3.5 tons, the supply voltage trajectory while cold cranking is described in the following wave–set.

Figure 18. LV124 Spec-Battery Voltage Trajectory During a Cold Start Event

The worst case low voltage per this spec 3.2 V. Certain **onsemi** High–Side devices like NCV84012A comply with this standard, while devices such as NCV84160 have under–voltage shutdown triggered at 3.5 V slightly above the minimum voltage spec of 3.2 V. The output and diagnostic behavior in an under–voltage event is described in Figure 19.

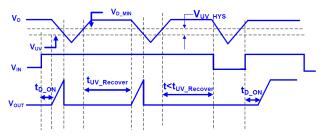

Some of the low RDS(ON) higher power SmartFETs have an under-voltage recovery delay timer designed in. This feature helps protect the device when an under-voltage condition is triggered consequential to the battery voltage pulled down (by its output impedance) in a high current conduction scenario such as short circuit current limit. Once the device safely shuts down and the current decays, the battery voltage rises again. In the absence of the alluded feature, the device will turn back on again into the short circuit as VBATT > VBATT MIN, overriding the built-in cool down time (Refer section Short Circuit OUT to GND -Current Limitation). The repetitive retries can be stressful for the die especially in case of high current devices observing a persistent short circuit. Incorporating a delay timer, spaces out such retries and allows the die to "cool down" sufficiently before the next retry. Figure 20 explains this phenomenon. Refer to product datasheets for details on UV delay specification.

Figure 19. Idealized Wave-Set Depicting The Device Behavior During Under-Voltage

Figure 20. Under-voltage Recovery Delay

## **Over-Voltage Protection**

Over-voltage scenarios, in an automotive environment, primarily occur because of high voltage transients conducted/coupled across the supply line (including alternator load dump), electro-static discharge (ESD) and jump start events. In a load dump event, the battery connection to the alternator (which provides the charging current to the battery) is lost, and the output current becomes unregulated, and thereby the loads connected to the alternator observe a significant increase in the supply voltage until the alternator regulator responds and cuts back on the drive current. A vehicle manufacturer specifies the characteristics of the load dump pulse by defining the voltage and time period for this pulse. In addition, standards like ISO 7637-2: Electrical Transient Conduction Along Supply Line Only (Refer [5]), also define specific ISO pulse profiles and load dump test cases. Over the recent years, the use of transient voltage suppressors at the alternator have led to the relaxation of load dump requirements in the form of a "suppressed load dump" spec (typically around 35 V for 12 V applications). This has allowed for scaling down the feature size on the die facilitating low R<sub>DS(ON)</sub> devices in shrunk packages such as NCV84012A. In case of a jump start, the vehicle battery is being charged by a high voltage source to start the engine, for instance, the battery of a truck, or a double car battery (usually to compensate for the line losses in the long charging cables). For a jump start, again, the pulse characteristics are defined by the OEM. A jump start event is less stressful than a load dump condition. Most automotive loads are required to sustain these high voltage events as specified by the OEM. onsemi High-Side SmartFETs have internal clamp structures designed to protect the FET and the controller against high voltage spikes.

Figure 21. Schematic Representation of Over–Voltage Protection Clamp Structures in a High Side SmartFET

Referring Figure 21, there is a protection clamp for the power FET from Drain–Gate that limits the voltage swing at the output. In case the FET was initially off, this protection clamp conducts if the voltage at the drain terminal exceeds

the zener breakdown, and turns the FET on by developing a potential across the Gate-Source impedance. The load impedance at the output limits the current through the FET. If the FET was initially on, it will stay on unless the device incorporates an over-voltage shutdown, as mentioned in section Typical Supply Voltage Specs. A separate clamp structure limits the voltage drop across the control section to Z<sub>VD</sub>, and the ground impedance network limits the current through these clamps. The protection diodes at the logic inputs clamp these inputs to a diode below the GND potential. The protection clamp for current sense, Z<sub>Sense</sub> in High-Side SmartFETs is referenced to the supply rail. As a standard practice, onsemi recommends external clamps at the current sense output to limit the voltage observed at the input A/D stage of the microcontroller. Also, it is recommended to have external protection resistors at the I/O pins interfacing with the microcontroller to prevent the microcontroller clamp structures from excessive current. An extended operation in the high voltage regime may impact the lifetime, robustness and performance of the device.

Device layout, terminations and metal routings are also carefully designed for superior transient high voltage robustness. The devices are subjected to standard ISO pulses and rated on the max ESD transient capability per the human body model and machine model (Charge Device Model Ratings are also provided for certain devices). Refer to product datasheets for specifications.

## Inductive Flyback

While switching an inductive load, the voltage at the output terminal may observe a considerable negative swing dependent on the rate of current decay at device turn off and the effective inductance being discharged. The Drain-Gate protection clamps limit the magnitude of this swing and provide an "active clamping" of the output potential to VBATT - VCLAMP, where VBATT is the drain potential and V<sub>CLAMP</sub> is the breakdown voltage of the protection clamps. Active clamping reduces the stress inflicted on the clamp diodes and improves the heat dissipation during inductive discharge by distributing the current density though the entire FET area. Such an approach is preferred over a scenario where the back-side body diode avalanches (i.e. breaks down) and discharges the inductor. For further details on the output behavior, clamp functionality and inductive energy capability, refer section Inductive Switching.

#### Loss of Power Supply

If the supply connection to the drain terminal is lost, a High–Side Smart FET protects itself by disabling the power device and the control section. Both OUT and Current Sense read "Lo" during a loss of supply event. In a case where the connection to the supply is lost during inductive switching (or if the wiring harness is sufficiently inductive), there has to be a flyback path for the current to be discharged. This path would include the protection diode for the control section ( $Z_{VD}$ , see Figure 19 ) limited by the external ground

resistor. Since the protection diodes are not as capable as the power FET to handle the inductive flyback energy, this may damage the High–Side Device in cases of high energy dissipations. In such cases, due considerations in system design should be given, for instance, by including freewheeling diodes to provide a path for the current flow during inductive discharge.

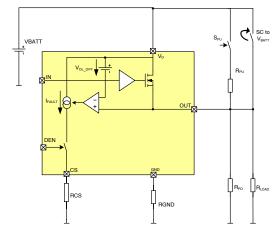

## Short Circuit to Power Supply

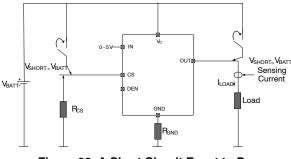

A short circuit to power supply event is depicted below.

Figure 22. A Short Circuit Event to Power Supply

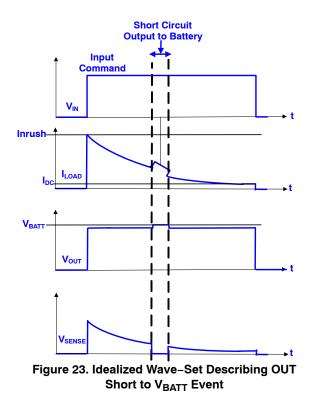

The above figure describes the short circuit of  $V_{BATT}$  line to the two output terminals– OUT or CS. In the former case, the load will conduct irrespective of the input command. Assuming that the drain terminal is strictly tied to the battery (i.e. no potential drops between battery and drain connections), there is no power dissipated across the device, but the event could be severely stressful for the load. The idealized set of waveforms in Figure 23 describes a transient OUT short to  $V_{BATT}$  event occurring in case of a typical bulb inrush. Load current and voltage increases transiently;  $V_{SENSE}$  drops to zero because the FET will be off during this time. In Figure 22, it is to be noted that the current is being measured close to the load and does not represent the output current coming out of the OUT terminal (which would be zero in a SHORT to  $V_{BATT}$  event).

If there is an impedance path between battery and drain connections, it may be possible that the source potential (in a short circuit to  $V_{BATT}$  event) is higher than drain's, resulting in an inverse current through the body diode. Such a situation, though unlikely in an automotive environment, can be very stressful for the device.

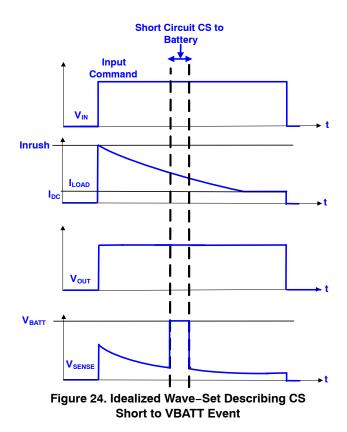

In case of  $V_{BATT}$  short to Current Sense, the OUT terminal and the load will operate normally, however a voltage equal to  $V_{BATT}$  will be observed at the CS pin which could potentially stress the I/O interface of the microcontroller's A/D. As described in section Operational Methodology, it is always recommended to put in external clamps at the CS pin to prevent high voltages at this node. Figure 24 shows the behavior of OUT and Sense nodes in case of CS short to  $V_{BATT}$ .

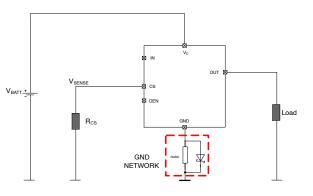

## Ground (GND) Operation

# Recommended GND Circuit

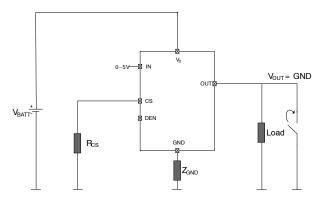

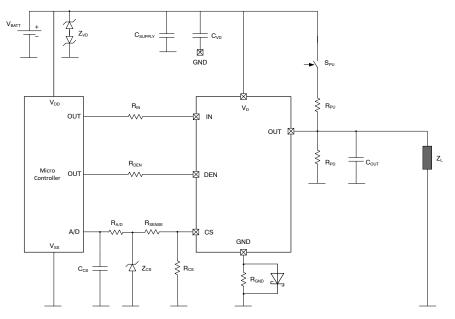

Understanding and employing an optimal ground network is imperative in an application involving High–Side FETs. As a standard practice, it is not recommended to tie the device GND pin directly to the vehicle, or chassis GND. As explained later in this section, this protects the High–Side FET under some specific system failure conditions. A typical ground network has been highlighted (in red) in Figure 25 – a resistance connected in parallel with (optional) diode. The resistor a) limits the current through the protection clamps,  $Z_{VD}$  (see Figure 21) in case of an overvoltage event, b) prevents the power dissipation in the device in case of a reverse battery connection (the protection clamps are forward biased in a reverse battery connection, see Figure 26), or in case of loss of battery during an inductive flyback.

#### Figure 25. Schematic Representation of Ground Network in an Application

While the resistance does offer device protection, it also raises the GND potential depending on the device's operating GND current. This potential, if high enough, can alter the threshold of the power FET and also limit the headroom rail available for the operation of the analog circuitry within the control section. There is, therefore, a tradeoff in the selection of this resistance. A high value for this resistance implies a low limiting current during over-voltage/reverse battery connections, but would also raise the ground potential significantly.

The diode helps in reducing the GND potential by shunting the resistance during normal operation, and also blocks the reverse voltage (upto its breakdown). It, however, does not help during an over-voltage situation. Unless otherwise suggested, as a typical value, a 1 k $\Omega$  resistor is recommended to be used in parallel with a diode, or a standalone resistance of ~150  $\Omega$  can be used as the GND impedance. For device specific recommendations, refer to the corresponding product datasheets.

# **Reverse Battery Protection**

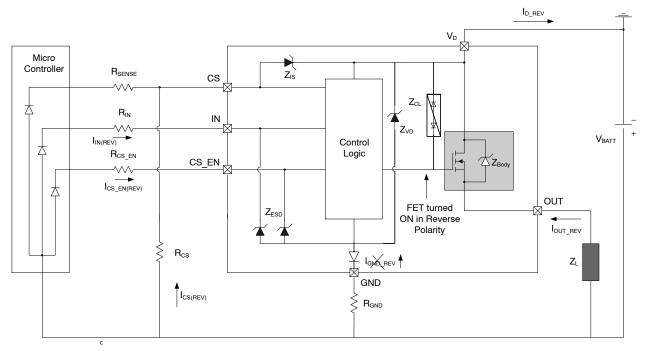

When the polarity/connection to the battery terminals is flipped, a reverse current would flow through the device as depicted in Figure 26. The protection diodes and resistors along with the direction of reverse current have also been shown in this block level schematic. The intrinsic body diode of the power FET would conduct a current  $I_{REV}$  and the power through this diode is limited by the load itself. In the control section, a ground current,  $I_{GND_REV}$  is conducted by the forward biased overvoltage protection clamps,  $Z_{VD}$ ;  $I_{IN\_REV}$  and  $I_{DEN\_REV}$  conduct through the internal microcontroller network into the protection resistors  $R_{IN}$  and  $R_{DEN}$  respectively. These currents flow through the ESD zener clamps for the digital inputs and eventually add to the current across  $Z_{VD}$ . The resistors at the logic inputs,  $R_{IN}$  and  $R_{DEN}$ , limit the current through the ESD structures; and the ground resistor represented by  $Z_{GND}$ , limits the current, and hence, the power dissipation across  $Z_{VD}$ . A reverse current,  $I_{CS\_REV}$  flows into the CS pin through the sense resistance  $R_{CS}$  and is fed back into the negative terminal of the battery through the forward biased overvoltage protection diode  $Z_{SENSE}$ .

Figure 26. Current Flow and Protection During Reverse Battery Operation

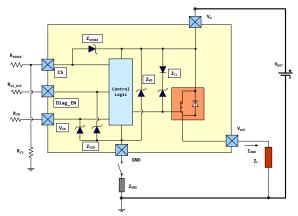

Low-ohmic devices intended primarily for relay and fuse replacement applications, such as NCV84008A, NCV84004A etc., are equipped with a ReverseON feature that turns on the output FET in an upside down configuration when a reverse battery voltage is observed. Such an operation helps reduce the power dissipation in the device by shunting the body diode and limiting the conduction losses in reverse mode. Fig. 27 highlights the conduction path through the FET instead of the body diode. Further, a reverse battery blocking mechanism in the ground path ensures a low GND current (Refer to specific product datasheets for max allowed reverse battery spec) and allows to undersize the external GND resistor.

In addition to ReverseON, the certain devices also offer an InverseON feature in which the body diode conduction is once again shunted and over-riden by FET turn on if the source potential exceeds that at the drain. Such a condition could be prompted when the output of the FET observes a hard short circuit to battery in the application as explained in the section Short Circuit to Power Supply. The  $R_{DS(ON)}$  offered by the FET in case of reverse battery, or inverse current conduction is specified in the respective product datasheets.

Figure 27. Reverse Battery Protection with ReverseON

It is to be noted that the reverse current in the output stage is not "blocked" in either of the cases described above; rather, the power dissipation is limited by employing FET conduction along with external protection resistors. Certain applications such as fuse and/or relay replacements require an external reverse battery blocking mechanism in the power path to prevent any current conduction in case of reverse battery connection to protect the loads downstream. For the maximum capability of a device (in terms of maximum time and reverse voltage withstood) in reverse polarity mode, refer to specific product datasheets. For loads requiring a reverse current blocking, special care must be exercised (for instance, incorporating reverse battery blocking circuit elements) while working with these High-Side devices. None of the protection features are available in the reverse battery mode.

## Loss of Ground

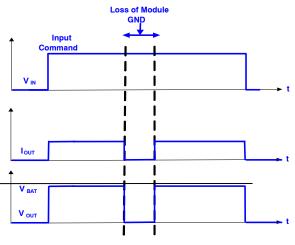

When the GND (Ground) connection to the device is lost, it will turn OFF the output FET and the control section. A loss of GND could occur at the module level (where the connection of the module GND to ECU GND is lost), or at the ECU level– where the entire ECU, including the microcontroller, loses the connection to the chassis GND. In both the cases, there is no return path/reference available for the control circuitry in the device. Any parasitic GND connections to the module should be avoided in the ECU design.

The block diagram below depicts such a situation.

Figure 28. Block Diagram Depicting a Loss of GND Situation. The Load Remains Connected to the Chassis GND, However, the Module GND is Lost.

Figure 29. Idealized Wave–Set Showing the Output Current and Voltage Behavior in a Loss of GND Event.

The idealized wave-set in Figure 29 shows the output behavior in a loss of GND event.

# Short Circuit OUT to GND - Current Limitation

In case of an unprotected FET, if the load gets shorted out to GND, there is nothing to limit the current and the power dissipation in the FET (the current eventually be limited by the device trans-conductance, or the current capacity of the supply, or the max capability of the bond wires) which could damage the device. To prevent such a situation of uncontrolled conduction, onsemi High-Side devices are equipped with a current limiter logic that limits the maximum current in a device during a short circuit event. The maximum allowed current differs across devices and technologies and can be looked up in the product datasheet. Figure 30 describes the scenario of OUT short circuit to ground- when the switch on the right is closed, the OUT node gets shorted to ground. The device observes a potential difference of VBATT across Drain-Source (ignoring any parasitic line resistance, and the resistance of the short).

Figure 30. A Short Circuit Event to Ground

Typically, this maximum current,  $I_{LIM}$ , is decided based on device's thermal capacity (taking inputs such as size, active silicon area, package etc.), and its intended application. For instance, if the intended application is to drive a bulb load with a high inrush current, the  $I_{LIM}$  would have to be set accordingly to ensure the bulb turn-on within the required time. Refer section Bulb Loads for more details on driving bulb loads.

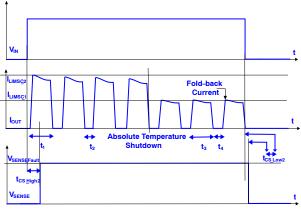

If the short to GND persists, the die temperature would eventually rise even though the current is limited. To preclude high temperature gradients, **onsemi** High–Side FETs incorporate a restart strategy based on differential and absolute temperature sensing (Refer section Temperature/Power Limitation for more information on temperature sensing). The idealized set of waveforms below depicts the exemplary output current behavior in a short circuit event:

Figure 31. Idealized Wave–Set Describing the Current Limit Behavior with "Fold–Back"

As the device turns on into a short circuit, the current is limited to  $I_{LIMSC_1}$  (also referred to as  $I_{LIM_Hi}$ ). When the differential temperature swing reaches its threshold (Refer Temperature/Power Limitation), the power FET is turned off and turns back on with a hysteresis. The device keeps on toggling on and off with a maximum saturation current of  $I_{LIMSC_1}$  until the absolute temperature of the die reaches the maximum limit and thereafter the output current "folds back" to a lower value,  $I_{LIMSC_2}$ , to limit the power dissipation, and thereby the temperature rise at high junction temperatures. The turn on times  $t_1$  and  $t_2$  depend on the thresholds for differential and absolute thermal shutdowns respectively (thresholds in terms of absolute and differential temperature limits are defined and specified in the product datasheets); and turn off times  $t_3$  and  $t_4$  depend on their corresponding hysteresis. In addition, the heat sinking and the thermal environment would also impact these time scales. As the device heats up, the circuit controlling the thermal shutdown also observes an increase in temperature which could potentially result in a time lag before these time intervals reach their steady state value.

The current fold-back feature is not universally present across all **onsemi** High Side devices (Refer to specific product datasheets for details). For some devices, a stable RMS current is defined post the absolute thermal shutdown threshold with no fold-back. Such a behavior is presented in Figure 32.

The current limit circuitry has, in most onsemi High-Side FETs, a slightly negative coefficient of variation with temperature to avoid any regenerative increase in current for device safety. Once, the junction temperature reaches the absolute thermal shutdown limit, the peak and the duty cycle of the ILIM pulses stabilizes eventually to yield a steady state RMS current, which is defined in the product datasheet. It should be noted that I<sub>LIM</sub> is also dependent on the battery voltage, (i.e. the Drain-Source voltage in this case), and is usually specified against a typical battery voltage, or a voltage range. Some devices, like NCV84012A, may also have an ILIM roll off at high Drain-Source voltages to reduce the power dissipation at these high voltages. In case of a "Soft Short" when the resistance in the output conduction path (including the resistance of the short) is high enough such that the output current does not reach the max limit-ILIM SC1, the thermal protection in the form of Differential and Absolute thermal shutdown and toggling would still be available.

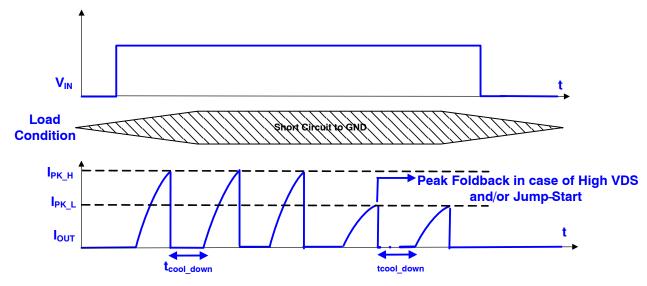

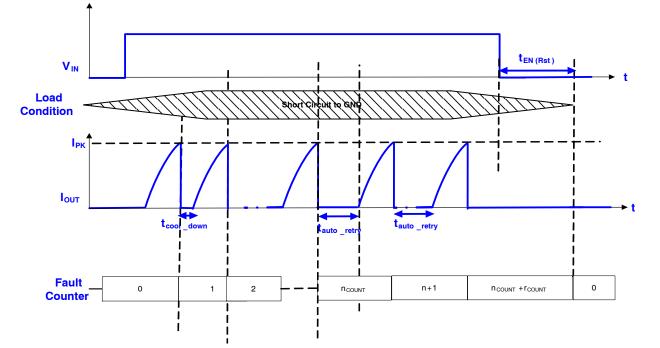

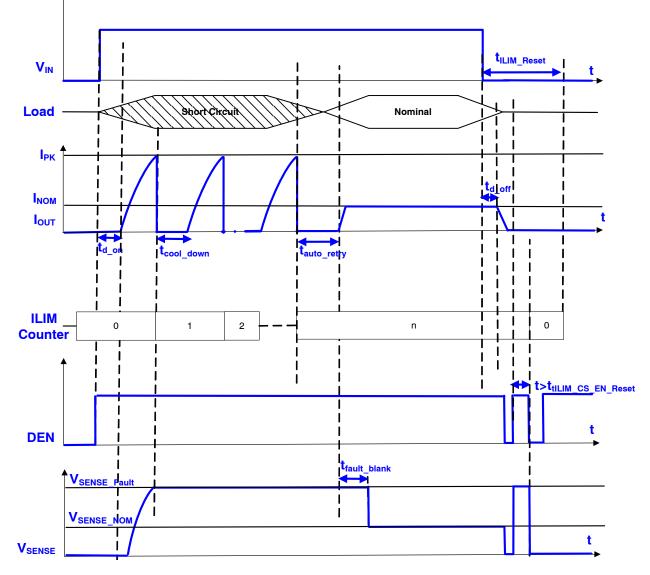

Other than the two current limitation philosophies depicted in Figure 31 and Figure 32, some devices, such as NCV84012A, may incorporate a peak current detect based turn-off in case of a short circuit to GND. The design approach is explained in Figure 33, where the device shuts

# AND9733/D

off the output stage when the drain current exceeds the internal threshold for current limit, thereby avoiding the higher power dissipation as in case of a linear current limit controlled by thermal shut–down.

Figure 33. Idealized Wave-Set Describing Peak Detect Based Current Limit

Such a design scheme becomes imperative for devices with high current limits realized on dense technologies where the high power dissipation (in a linear current limit) can be detrimental for the die, and needs to be controlled by a precise peak based turn-off and timer based re-start instead of regulating the current. The "cool-down" timer t<sub>cool down</sub> is defined in the control logic based on the safe operating area measurements performed on the technology. Most of these devices also employ a high V<sub>DS</sub> (as in case of a "hard" short circuit), and/or high VD (as in case of jump-start) based current limit fold-back. Further, if the absolute or the differential temperature on the die rises over repetitive retries, the longer cool down time enforced by thermal sensors (as explained in the following section) prevails. The majority of devices equipped with this feature also have the capability for trimming the current thresholds and associated timers, offering more design flexibility and a lower device-to-device variability. Refer to product datasheets for specifications on these timer specs, peak detect thresholds and tolerances in the measured peaks.

With reference to relay and fuse replacement solutions, the peak detect based current limit is the preferred choice of design that provides a controlled response in case of a short circuit event and avoids dissipating high power in the loads. On the other hand, applications such as lighting or switching capacitive loads require a steady current over a duration for inrush management. This trade–off is often handled by dialing in peak current thresholds and cool down timers (using trims) pertinent to the load that the device is expected to drive.

#### **Temperature/Power Limitation**

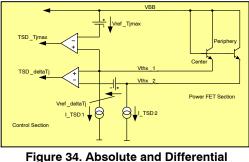

## Absolute and Differential Temperature Sensing

Fast and accurate temperature sensing serves to protect onsemi-High Side FETs in cases of overload and/or high power dissipation events such as Short Circuit OUT to GND. Exceeding device's thermal capacity is one of the most plausible failure modes in the application, which necessitates employing control elements that could sense and turn off the device when the junction temperature reaches a given threshold. Such a mechanism is termed as Absolute Thermal Shutdown, or simply referred to as TSD (Thermal Shutdown). The typical thermal Shutdown threshold in onsemi High-Side FETs is ~175°C, unless otherwise specified in the product datasheet. The device turns back on after the die has "cooled down" to a lower temperature. Thermal shutdowns have a hysteresis associated with the turn on to avoid continual thermal toggling around the threshold. There are often many challenges associated with an efficient TSD design-where should the temperature be sensed on the die considering the layout constraints; what should be the optimum tripping point and hysteresis for device shutdown, generating a reference circuitry with minimal variations across temperature etc.

While an absolute thermal shutdown precludes the detrimental damage in case of high power dissipation events, it does not prevent the device from observing temperature gradient during these events, which can severely affect the lifetime, performance and robustness of the device. For instance, considering a case of a cold bulb inrush, where the ambient temperatures are low and bulb filament needs to be warmed up sufficiently (Refer section Bulb Loads), a high inrush current is conducted through the device which raises the die temperature. In a hypothetical example, where the device ambient temperature is  $-40^{\circ}$ C and absolute thermal shutdown would occur at ~ 175°C, the device would observe a thermal gradient of more than 200°C which may stress the device and significantly reduce the lifetime in case of multiple such events. In some cases these thermal transients result in a thermo-mechanical overstrain which may potentially induce mechanical damages such as die cracks, or delamination. To prevent such a situation, a Differential, or Delta Temperature Sensing and Shutdown (DTSD) mechanism is employed that senses the differential between the max and min die temperatures as shown in Figure 34.

Temperature Sensing

Two sense elements are placed– one close to the center of the power FET (that typically observes the max temperature), and the other close to the periphery of the power FET. Since there is a time lag associated with the thermal wave propagation, there is always some difference in the temperature sensed by the two sensors– with the sensor is the centered sensor reading a higher temperature. If the temperature difference exceeds as set threshold, the device is turned off and turns on with a hysteresis. Figure 31 depicts the exemplary electrical equivalent that emulates the thermal behavior described above. The sensed voltages are compared with (thermally) stable references  $V_{ref_Tjmax}$  and  $V_{ref_deltaTj}$ , and the output is sent to the block that eventually makes the decision to/not to turn off the FET.

Another advantage with this Differential Thermal Toggling is the potential improvement in the Repetitive Short Circuit Performance (RSC). The standard from Automotive Electronics Council– AEC–Q100–012, details the short circuit reliability characterization of smart power devices. In the worst case, device switches an impedance network representative of a short circuit in an automotive environment, and the performance is quantified in grades from A through O (For test setup details and performance classification, refer to AEC–Q100–012). Better performance implies a greater number of pulses survived under the given test and external stimuli conditions. With

DTSD, the extent of thermal transient observed in each retry is attenuated and the device can withstand more such short circuit pulses, i.e. an improvement in device lifetime and robustness is observed. The re-try strategy is further explained in the next section. Certain **onsemi** High-side Smart FETs are also equipped with a "back-up" temperature sensor laid out within the control section to protect the device from catastrophic failures.

In the context of SmartFETs with shrunk die sizes, a fast thermal response is indispensable for ensuring the survival off the die in case of transient high power dissipation. The peak current detect is generally designed to meet inrush requirements but may not be sufficient to protect the device under certain conditions. In situations where the short impedance is very small, and a high Drain-Source voltage could occur, the peak current detect may not respond fast enough to the extreme thermal transient experienced by the die. In that case DTSD will take over and ensure that the thermal transient does not exceed the capability of the device. Additionally, a fast absolute thermal shutdown protection can occur when short circuit events happen at elevated temperatures. In this event, thermal sensors are required to safely turn-off the device before the defined peak is attained. This necessitates the sensing and propagation delay to be optimized for a response time on the order of a few tens of microseconds. Applications such as power distribution often operate at higher junction temperatures requiring a higher thermal shutdown threshold in addition to a fast thermal response.

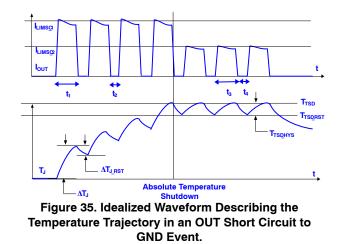

## *Re-try Strategy*

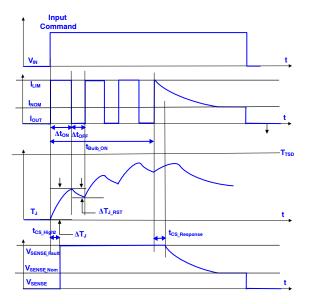

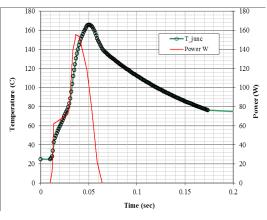

Idealized wave-set in Figure 35 describes the trajectory of the thermal response in a High Side device mapped against the output current in case of Short Circuit OUT to GND. This wave-set essentially adds the temperature curve to the example elucidated in the last section.

At the beginning of the first pulse, with no power dissipation, the peak junction temperature is equal to the peripheral, or the ambient temperature. As the current rises to the max limit  $I_{LIM SC1}$ , the temperature rises with a more

pronounced increase at the center of the die. When the difference in the two temperatures,  $\Delta T_J$ , exceeds the defined limit (usually 60°C in **onsemi** High–Side Devices, unless otherwise specified), the power FET is turned off until the device cools down by  $\Delta T_{J_RST}$ , and thereafter restarts with another I<sub>LIM\_SC1</sub> pulse. The temperature at the edge of the die increases with each retry cycle as shown in the waveform. Once the peak junction temperature reaches the absolute thermal shutdown limit, T<sub>TSD</sub>, the device turns on and off with the hysteresis– T<sub>TSD\_HYS</sub>. As explained in section Short Circuit to OUT to GND–Current Limitation, not all **onsemi** High Side FETs have a current fold–back, and the waveforms shown here are just for instance.

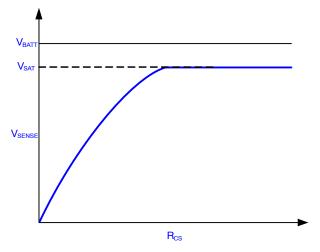

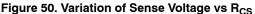

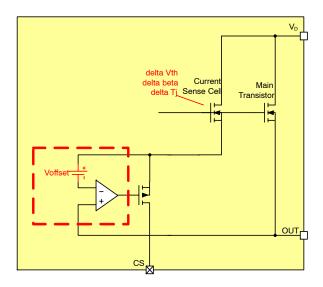

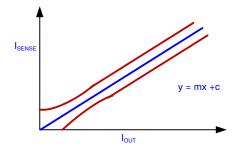

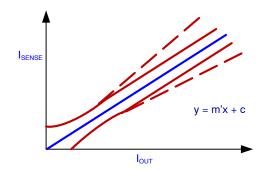

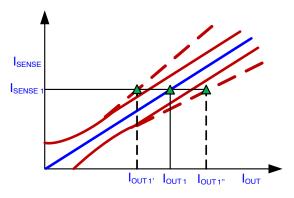

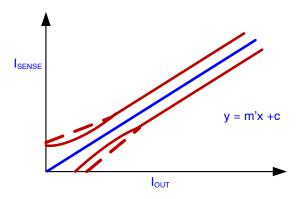

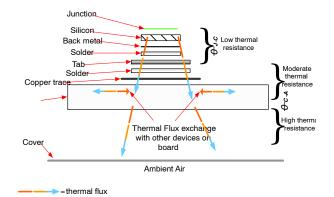

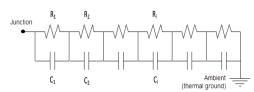

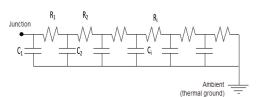

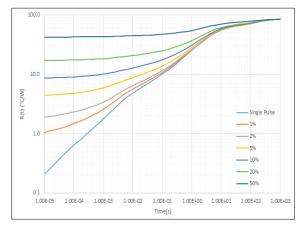

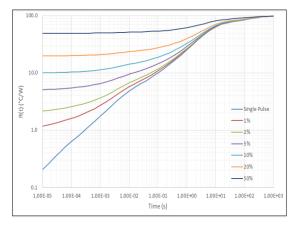

The turn on times and hysteresis are chosen with a trade-off between the max temperature transient observed by the die (it is desirable to have a short retry period to avoid large temperature swings), and the ability of a device to turn on a bulb within the given time (long retry periods are desirable to deliver the required bulb inrush with least number of retries).