**ON Semiconductor**

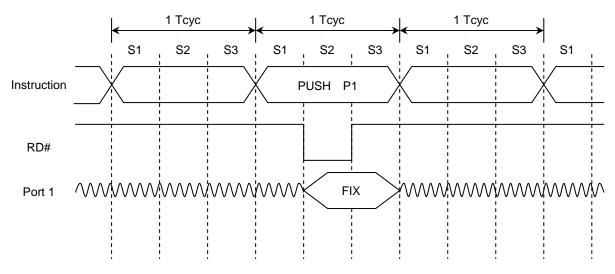

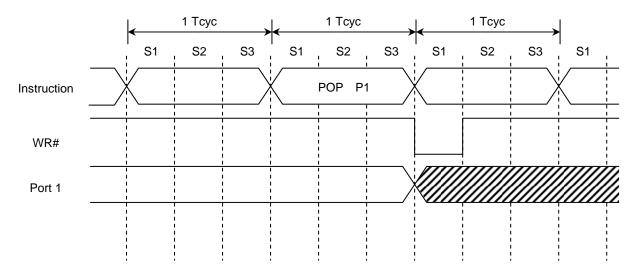

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

**CMOS 8-BIT MICROCONTROLLER**

# LC871K00 SERIES USER'S MANUAL

REV : 1.00

ON Semiconductor Digital Solution Division Microcontroller & Flash Business Unit

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

| Chapte          | er 1  | Overview ······1-1                                                |

|-----------------|-------|-------------------------------------------------------------------|

| 1.1             | Ove   | rview 1-1                                                         |

| 1.2             | Feat  | ures1-1                                                           |

| 1.3             | Pino  | ut1-6                                                             |

| 1.4             | Syst  | em Block Diagram ······1-8                                        |

| 1.5             | Pin F | Functions ······1-9                                               |

| 1.6             | On-c  | chip Debugger Pin Connection Requirements                         |

| 1.7             | Reco  | ommended Unused Pin Connections1-11                               |

| 1.8             |       | Output Types ······ 1-11                                          |

| 1.9             |       | Option Table ······ 1-12                                          |

| 1.10            | US    | B Reference Power Supply Option 1-13                              |

| Chapte          | er 2  | Internal Configuration2-1                                         |

| <b>.</b><br>2.1 |       | ory Space2-1                                                      |

| 2.2             |       | ram Counter (PC) ······2-1                                        |

| 2.3             |       | ram Memory (ROM)2-2                                               |

| 2.4             |       | nal Data Memory (RAM) ······2-2                                   |

| 2.5             |       | umulator/A Register (ACC/A) ······2-3                             |

| 2.6             |       | egister (B)2-3                                                    |

| 2.7             | C Re  | egister (C)2-4                                                    |

| 2.8             | Prog  | ram Status Word (PSW) ······2-4                                   |

| 2.9             |       | k Pointer (SP)······2-5                                           |

| 2.10            | Ind   | irect Addressing Registers······2-5                               |

| 2.11            | Ade   | dressing Modes······2-6                                           |

| 2.1             | 11.1  | Immediate Addressing (#)······ 2-6                                |

| 2.1             | 11.2  | Indirect Register Indirect Addressing ([Rn]) 2-7                  |

| 2.1             | 11.3  | Indirect Register + C Register Indirect Addressing ([Rn, C]) 2-7  |

| 2.1             | 11.4  | Indirect Register (R0) + Offset Value Indirect Addressing ([off]) |

|                 |       |                                                                   |

| 2.1             | 11.5  | Direct Addressing (dst) 2-8                                       |

| 2.1             | 11.6  | ROM Table Look-up Addressing 2-9                                  |

| 2.1             | 11.7  | External Data Memory Addressing 2-9                               |

| 2.12            | Wa    | it Sequence ······2-10                                            |

| 2.1             | 12.1  | Wait Sequence Occurrence2-10                                      |

| 2.1             | 12.2  | What is a Wait Sequence?2-10                                      |

| Chapte          | er 3  | Peripheral System Configuration3-1                                |

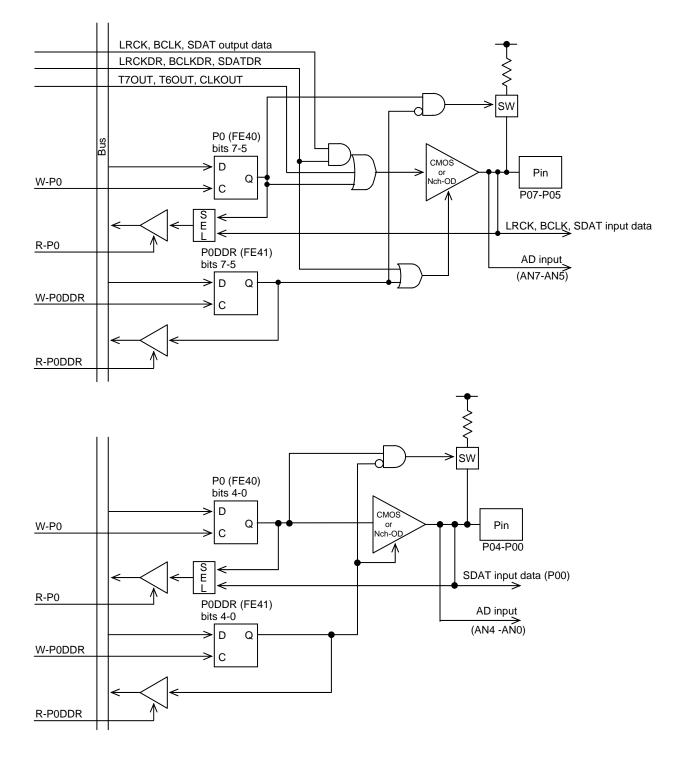

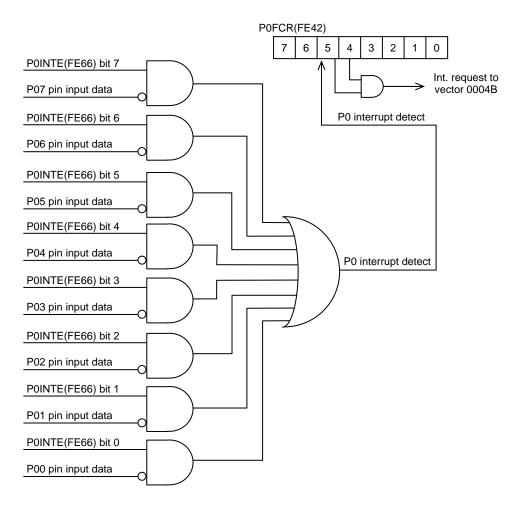

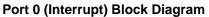

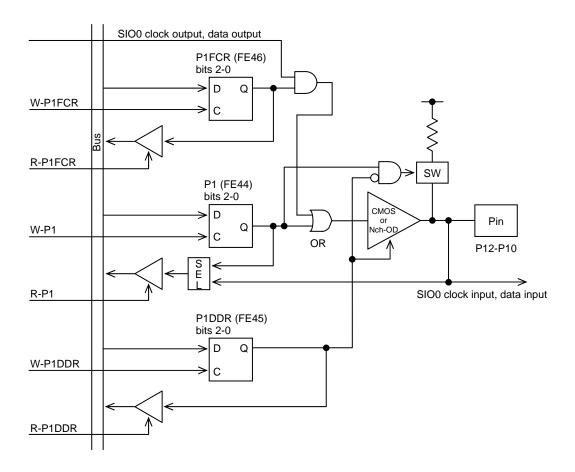

| 3.1             | Port  | 03-1                                                              |

|                 |       | Overview                                                          |

| 3.1.2   | Functions                        |

|---------|----------------------------------|

| 3.1.3   | Related Registers 3-2            |

| 3.1.4   | Options 3-5                      |

| 3.1.5   | HALT and HOLD Mode Operation     |

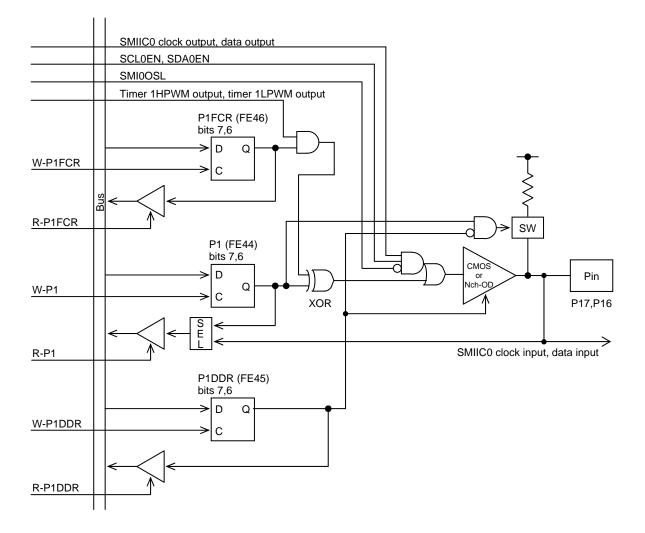

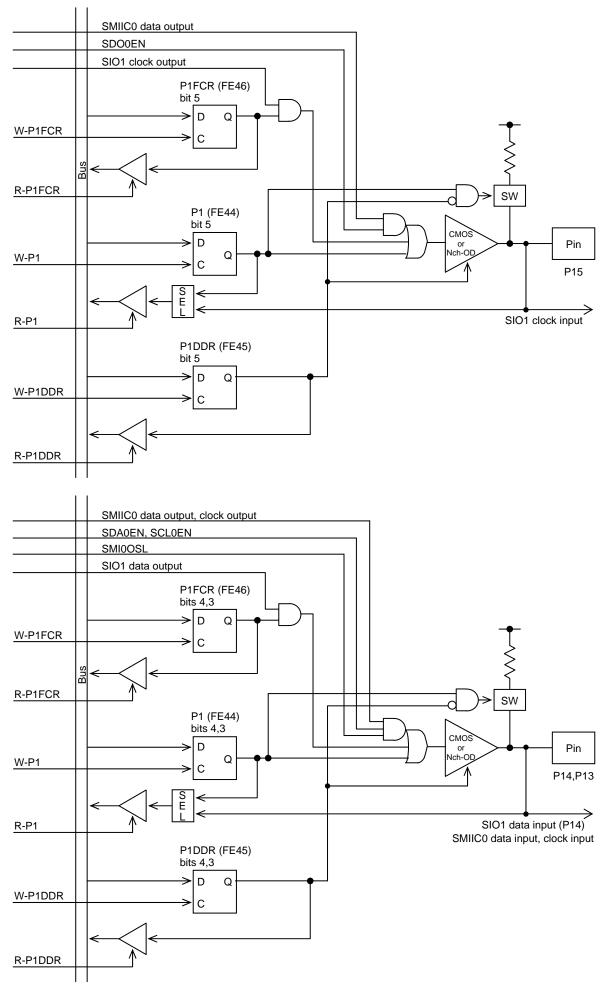

| 3.2 Po  | rt 13-6                          |

| 3.2.1   | Overview 3-6                     |

| 3.2.2   | Functions                        |

| 3.2.3   | Related Registers 3-6            |

| 3.2.4   | Options 3-9                      |

| 3.2.5   | HALT and HOLD Mode Operation     |

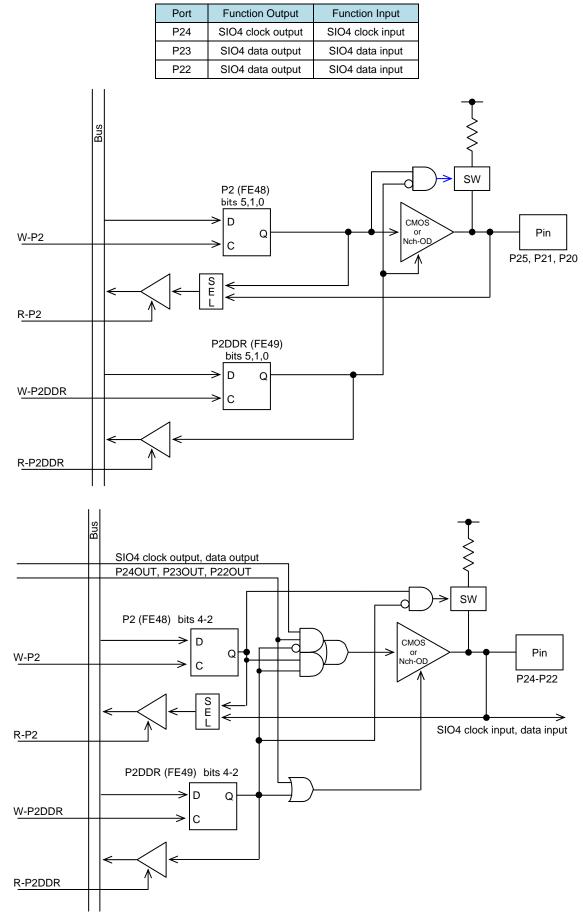

| 3.3 Po  | rt 2 ····· 3-10                  |

| 3.3.1   | Overview                         |

| 3.3.2   | Functions3-10                    |

| 3.3.3   | Related Registers                |

| 3.3.4   | Options                          |

| 3.3.5   | HALT and HOLD Mode Operation     |

| 3.4 Po  | rt 3 3-16                        |

| 3.4.1   | Overview                         |

| 3.4.2   | Functions                        |

| 3.4.3   | Related Registers                |

| 3.4.4   | Options                          |

| 3.4.5   | HALT and HOLD Mode Operation     |

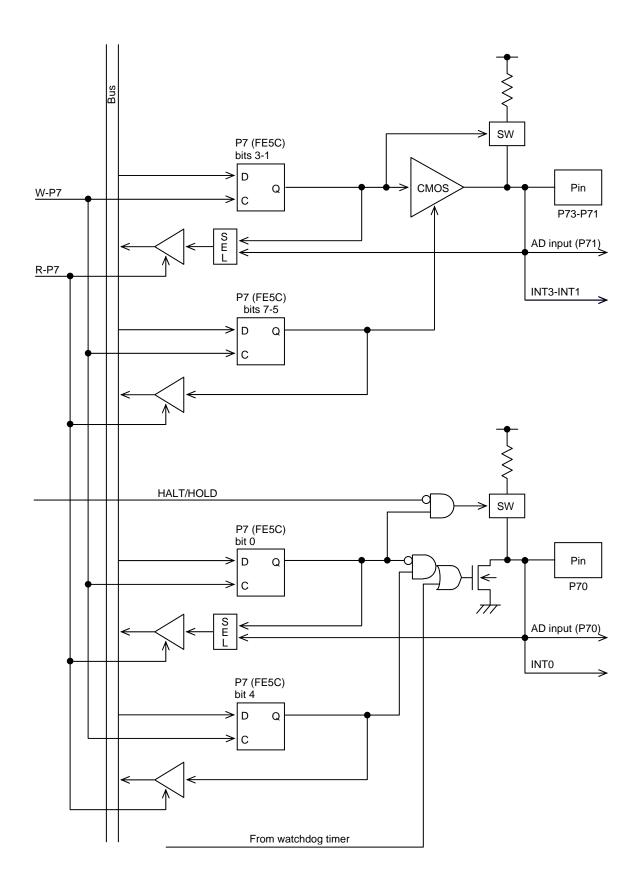

| 3.5 Po  | rt 7 3-18                        |

| 3.5.1   | Overview                         |

| 3.5.2   | Functions                        |

| 3.5.3   | Related Registers                |

| 3.5.4   | Options                          |

| 3.5.5   | HALT and HOLD Mode Operation     |

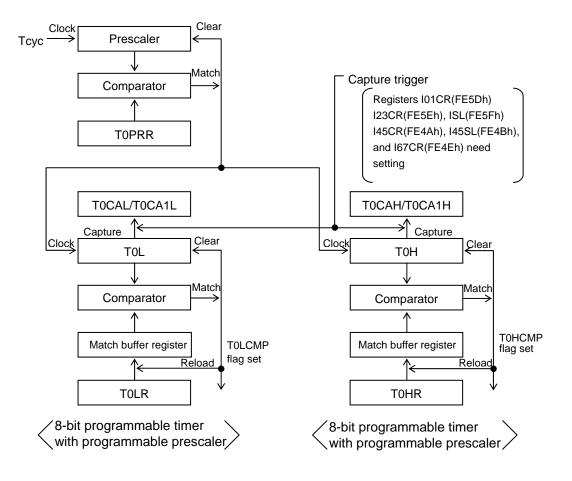

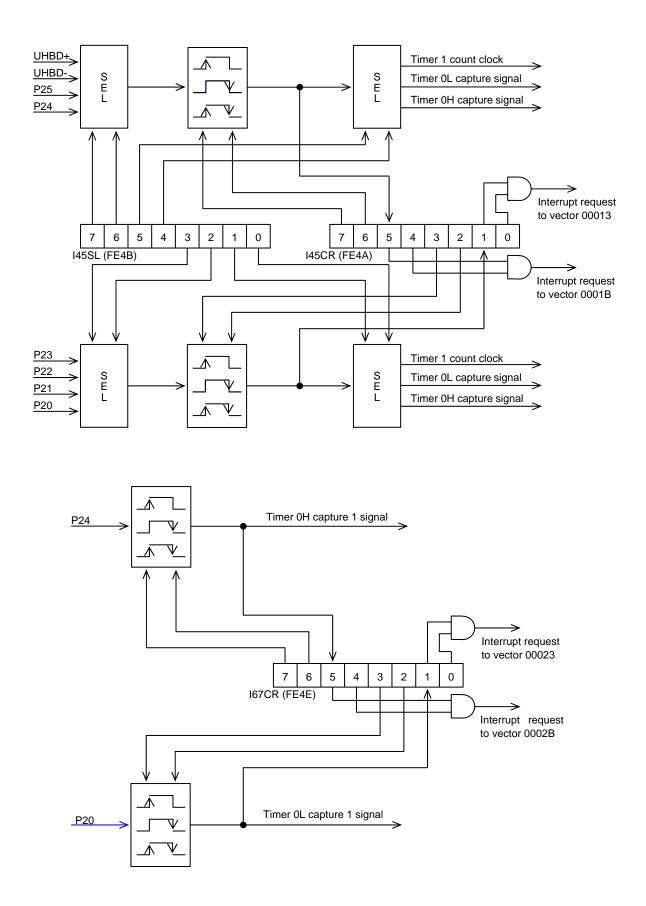

| 3.6 Tin | ner/Counter 0 (T0)               |

| 3.6.1   | Overview                         |

| 3.6.2   | Functions                        |

| 3.6.3   | Circuit Configuration            |

| 3.6.4   | Related Registers                |

| 3.7 Hig | h-speed Clock Counter ······3-34 |

| 3.7.1   | Overview                         |

| 3.7.2   | Functions                        |

| 3.7.3   | Circuit Configuration            |

| 3.7.4   | Related Register                 |

| 3.8 Tin | ner/Counter 1 (T1) 3-38          |

| 3.8.1   | Overview                         |

| 3.8.2 Functions                     |

|-------------------------------------|

| 3.8.3 Circuit Configuration         |

| 3.8.4 Related Registers ······ 3-4  |

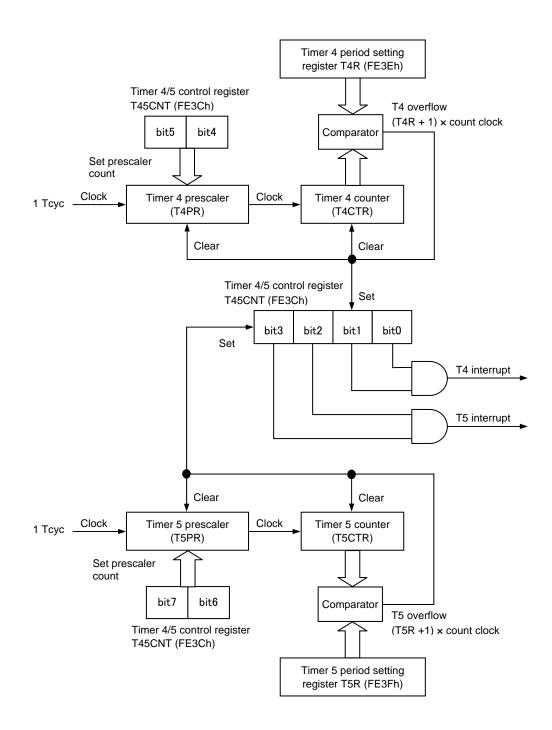

| 3.9 Timers 4 and 5 (T4, T5) 3-50    |

| 3.9.1 Overview                      |

| 3.9.2 Functions                     |

| 3.9.3 Circuit Configuration         |

| 3.9.4 Related Registers ······ 3-55 |

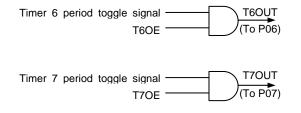

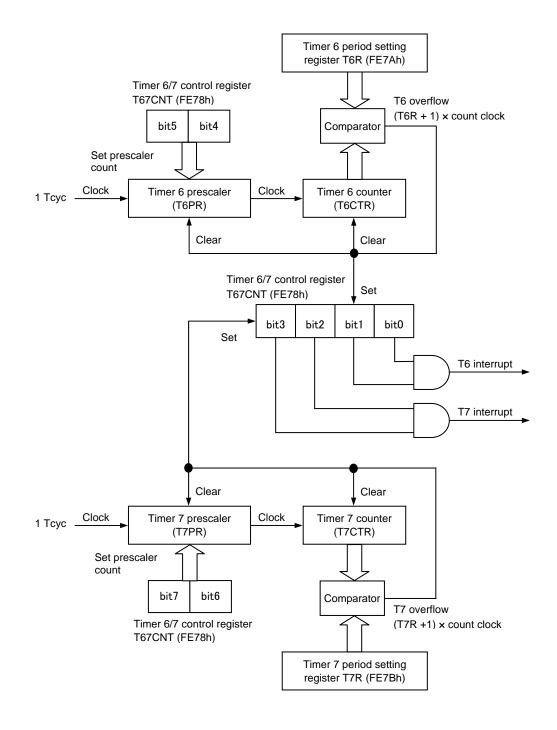

| 3.10 Timers 6 and 7 (T6, T7)        |

| 3.10.1 Overview                     |

| 3.10.2 Functions                    |

| 3.10.3 Circuit Configuration        |

| 3.10.4 Related Registers            |

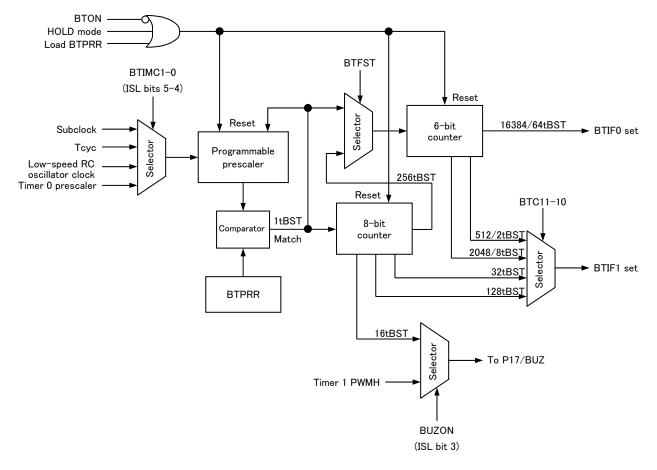

| 3.11 Base Timer (BT)                |

| 3.11.1 Overview                     |

| 3.11.2 Functions                    |

| 3.11.3 Circuit Configuration        |

| 3.11.4 Related Registers            |

| 3.12 Serial Interface 0 (SIO0)      |

| 3.12.1 Overview                     |

| 3.12.2 Functions                    |

| 3.12.3 Circuit Configuration        |

| 3.12.4 Related Registers            |

| 3.12.5 SIO0 Communication Examples  |

| 3.12.6 SIO0 HALT Mode Operation     |

| 3.13 Serial Interface 1 (SIO1) 3-75 |

| 3.13.1 Overview                     |

| 3.13.2 Functions                    |

| 3.13.3 Circuit Configuration        |

| 3.13.4 SIO1 Communication Examples  |

| 3.13.5 Related Registers ······3-84 |

| 3.14 Serial Interface 4 (SIO4)      |

| 3.14.1 Overview                     |

| 3.14.2 Functions                    |

| 3.14.3 Circuit Configuration        |

| 3.14.4 Related Registers            |

| 3.14.5 SIO4 Communication Examples  |

| 3.14.6 SIO4 HALT Mode Operation3-98 |

| 3.15 Parallel Interface 3-99        |

| 3.15.1 Overview                     |

| 3.15.2  | Functions                                                |

|---------|----------------------------------------------------------|

| 3.15.3  | Related Registers                                        |

| 3.15.4  | Parallel Interface Programming Example                   |

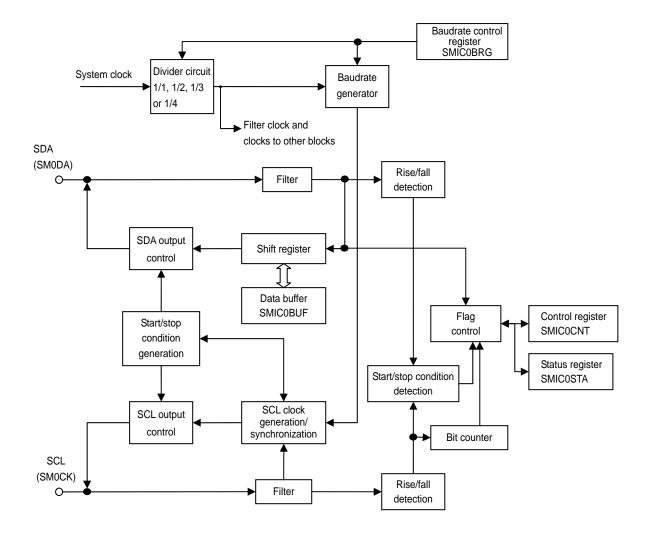

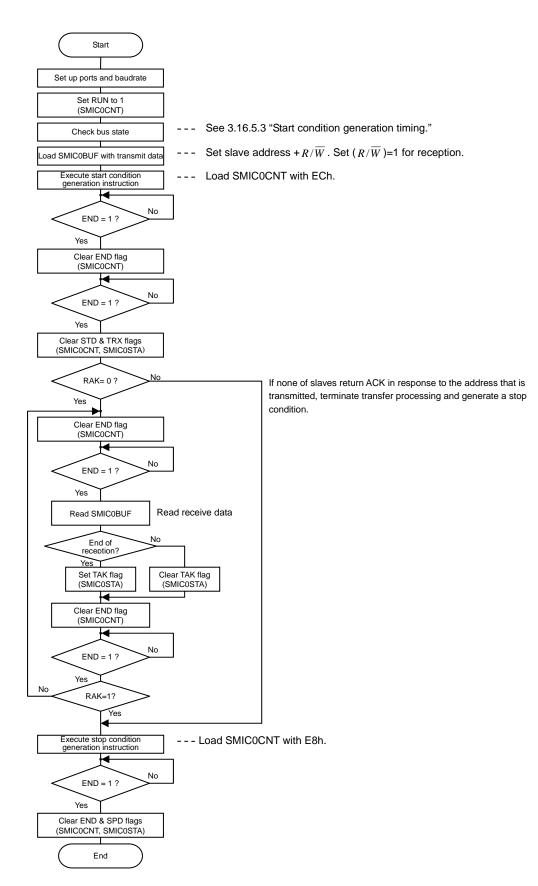

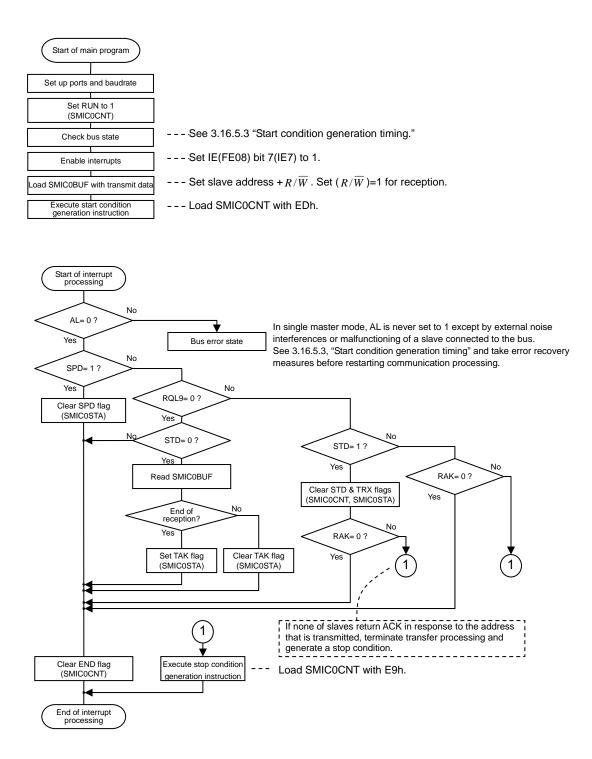

| 3.16 SN | /IIC0 (Single Master I <sup>2</sup> C)······ 3-102       |

| 3.16.1  | Overview                                                 |

| 3.16.2  | Circuit Configuration                                    |

| 3.16.3  | Related Registers ······ 3-104                           |

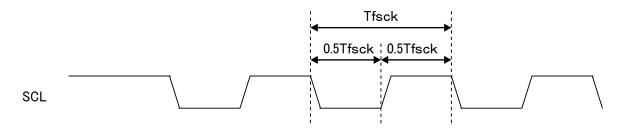

| 3.16.4  | Waveform of Generated Clocks and SCL Rise Times          |

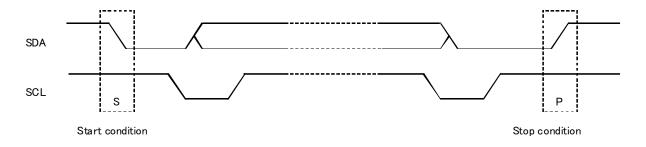

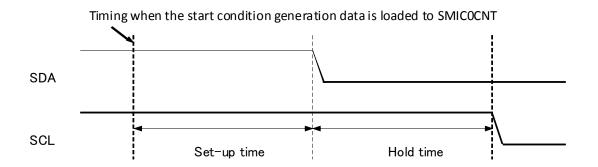

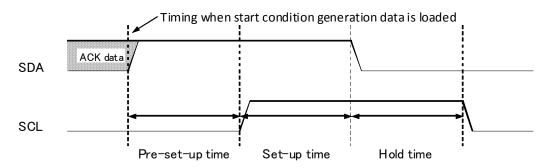

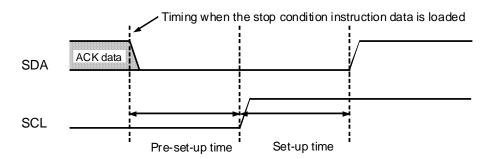

| 3.16.5  | Start Condition and Stop Condition 3-117                 |

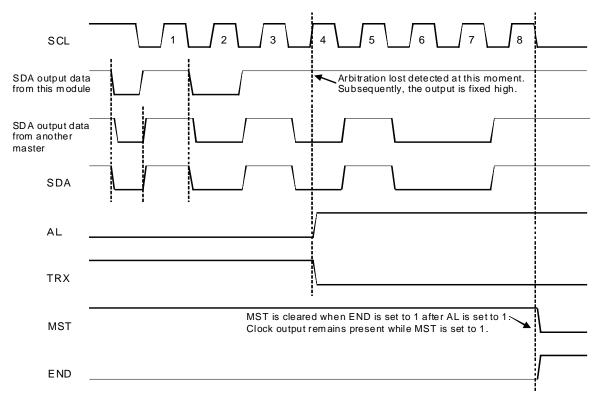

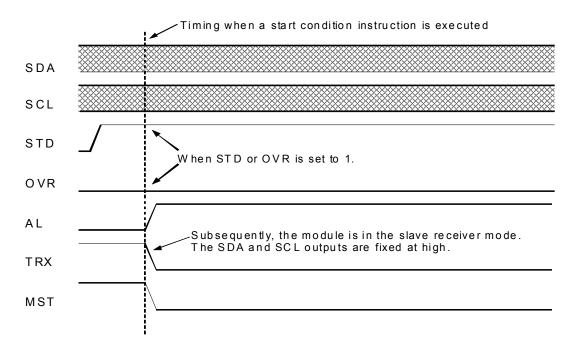

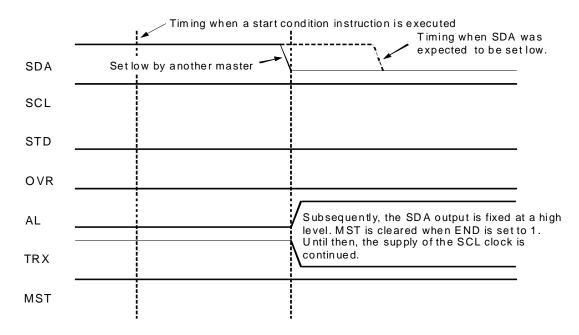

| 3.16.6  | Arbitration Lost ······ 3-121                            |

| 3.16.7  | Examples of Simple SIO Mode Communication 3-124          |

| 3.16.8  | Examples of Single Master I <sup>2</sup> C Communication |

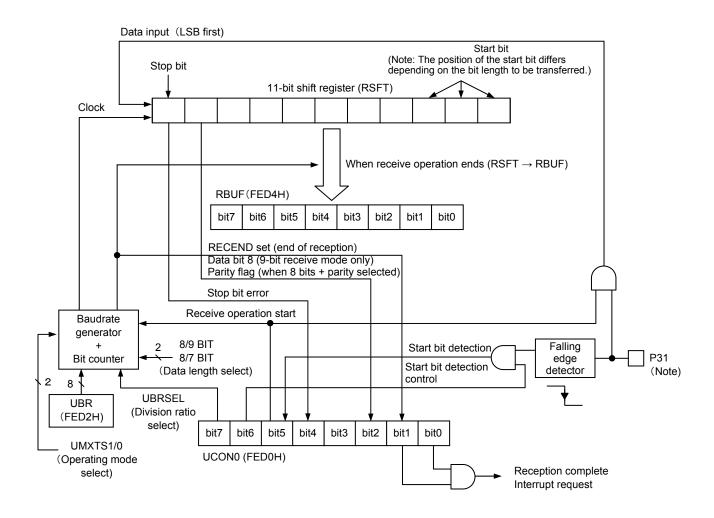

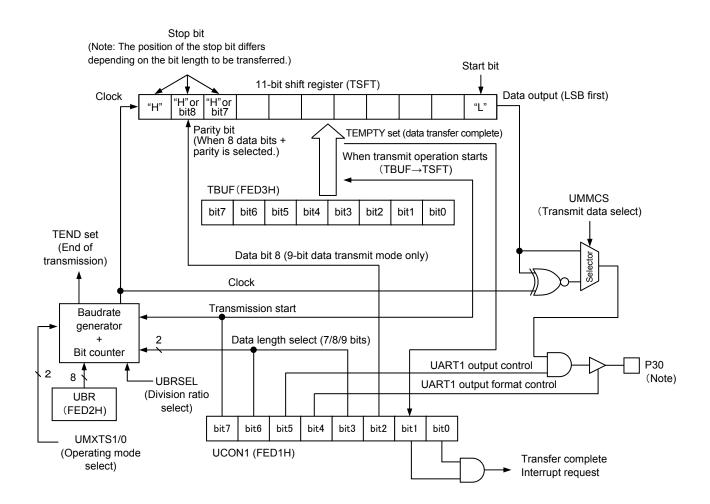

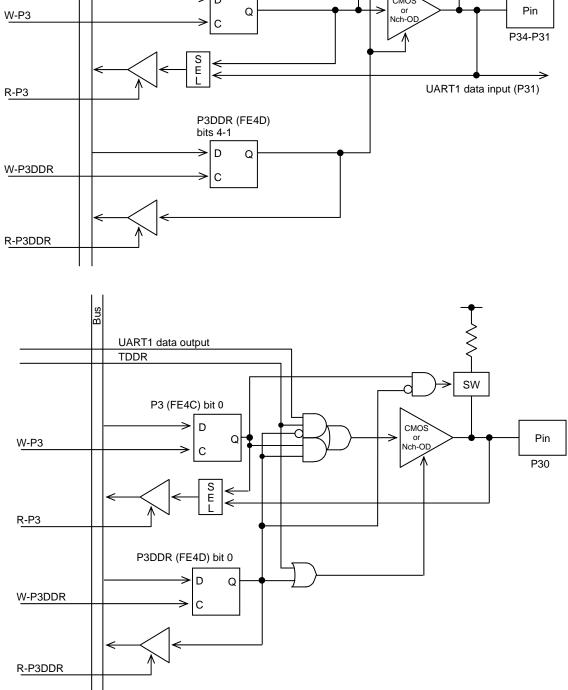

| 3.17 As | ynchronous Serial Interface 1 (UART1)······ 3-129        |

| 3.17.1  | Overview                                                 |

| 3.17.2  | Functions                                                |

| 3.17.3  | Circuit Configuration 3-130                              |

| 3.17.4  | Related Registers ······ 3-132                           |

| 3.17.5  | UART1 Continuous Communication Operation Examples        |

| 3.17.6  | Supplementary Notes on UART1 3-140                       |

| 3.17.7  | UART1 HALT Mode Operation ······ 3-141                   |

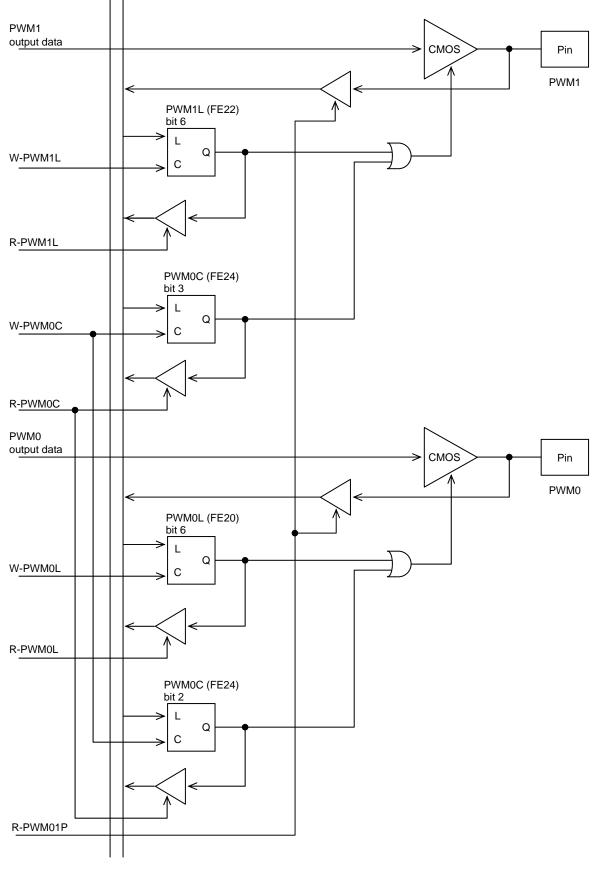

| 3.18 PN | /IW0 and PWM1 3-142                                      |

| 3.18.1  | Overview                                                 |

| 3.18.2  | Functions                                                |

| 3.18.3  | Circuit Configuration                                    |

| 3.18.4  | Related Registers ······ 3-144                           |

| 3.19 AD | O Converter (ADC12)                                      |

| 3.19.1  | Overview                                                 |

| 3.19.2  | Functions 3-149                                          |

| 3.19.3  | Circuit Configuration 3-149                              |

| 3.19.4  | Related Registers ······ 3-150                           |

| 3.19.5  | AD Conversion Example                                    |

| 3.19.6  | Hints on the Use of the ADC                              |

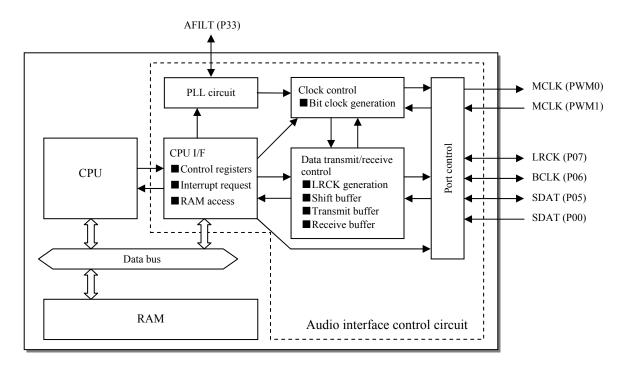

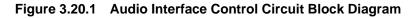

| 3.20 Au | dio Interface                                            |

| 3.20.1  | Overview                                                 |

| 3.20.2  | Functions 3-157                                          |

| 3.20.3  | Circuit Configuration 3-158                              |

| 3.20.4  | Related Registers ······ 3-159                           |

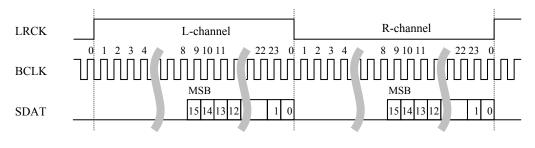

| 3.20.5  | Audio Interface Communication Example                    |

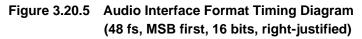

| 3.20.6  | Synchronous Serial Interface Communication Example       |

| 3.20.7  | Audio Interface HALT Mode Operation 3-178                |

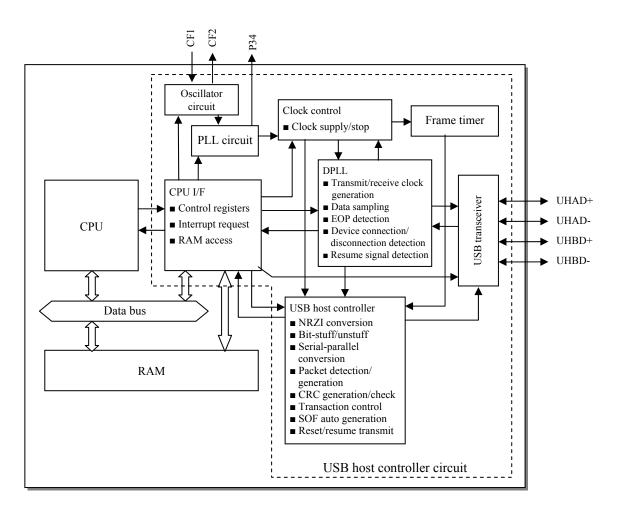

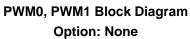

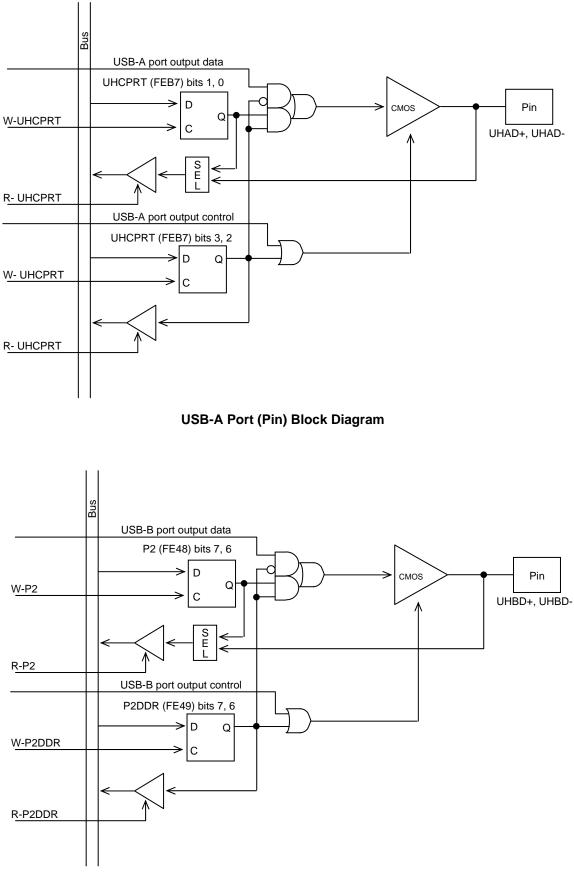

| 3.21 U   | SB Host                                                   |

|----------|-----------------------------------------------------------|

| 3.21.1   | Overview                                                  |

| 3.21.2   | Punctions                                                 |

| 3.21.3   | Circuit Configuration 3-180                               |

| 3.21.4   | Related Registers                                         |

| 3.21.5   | USB Host Communication Example                            |

| 3.21.6   | USB Host HALT Mode Operation 3-197                        |

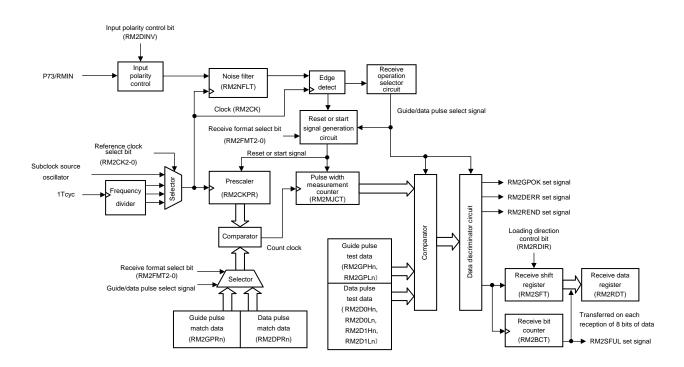

| 3.22 In  | frared Remote Control Receiver Circuit 2 (REMOREC2) 3-198 |

| 3.22.1   | Overview                                                  |

| 3.22.2   | Punctions                                                 |

| 3.22.3   | Circuit Configuration 3-199                               |

| 3.22.4   | Related Registers 3-203                                   |

| 3.22.5   | Remote Control Receiver Circuit Operation 3-209           |

|          |                                                           |

|          | r 4 Control Functions4-1                                  |

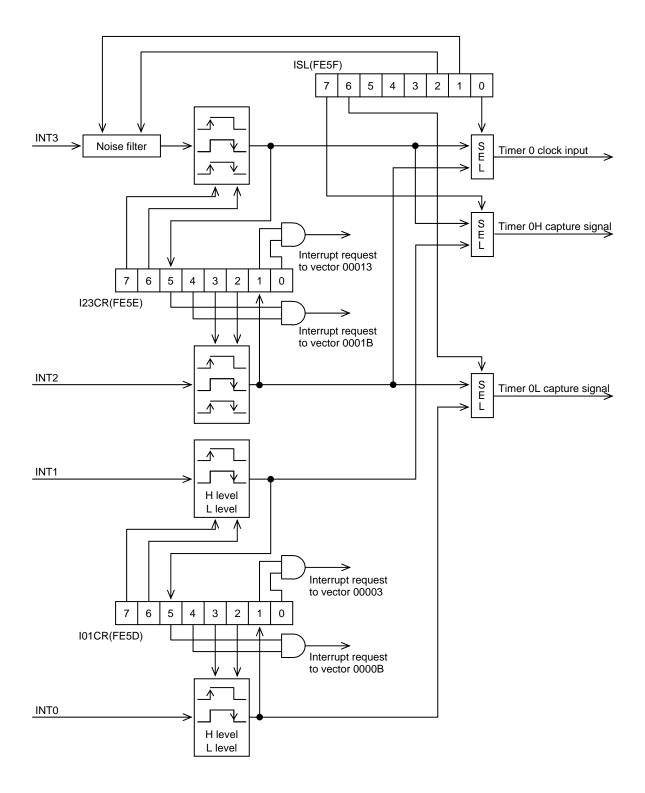

| 4.1 Inte | errupt Function ······4-1                                 |

| 4.1.1    | Overview 4-1                                              |

| 4.1.2    | Functions 4-1                                             |

| 4.1.3    | Circuit Configuration 4-2                                 |

| 4.1.4    | Related Registers 4-3                                     |

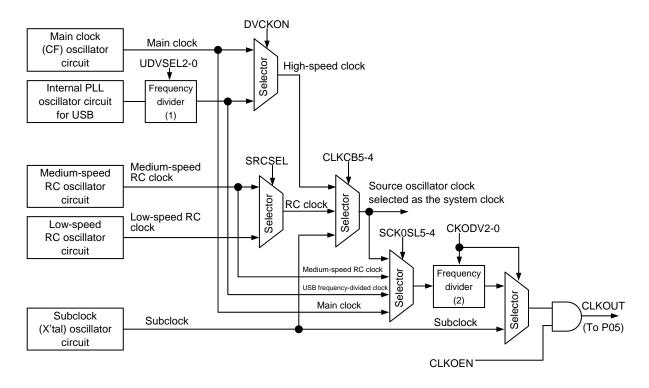

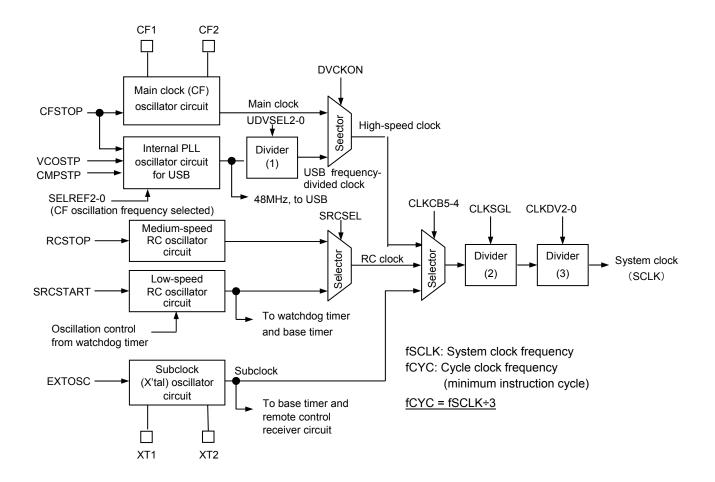

| 4.2 Sys  | stem Clock Generator Function4-5                          |

| 4.2.1    | Overview 4-5                                              |

| 4.2.2    | Functions 4-5                                             |

| 4.2.3    | Circuit Configuration 4-6                                 |

| 4.2.4    | Related Registers 4-9                                     |

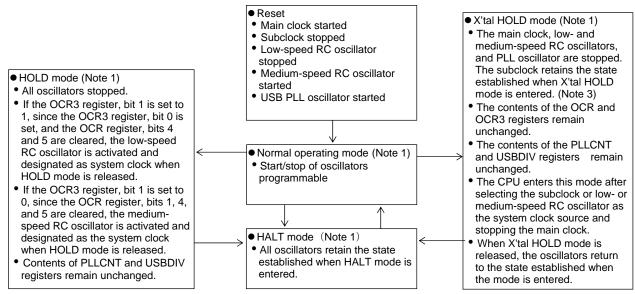

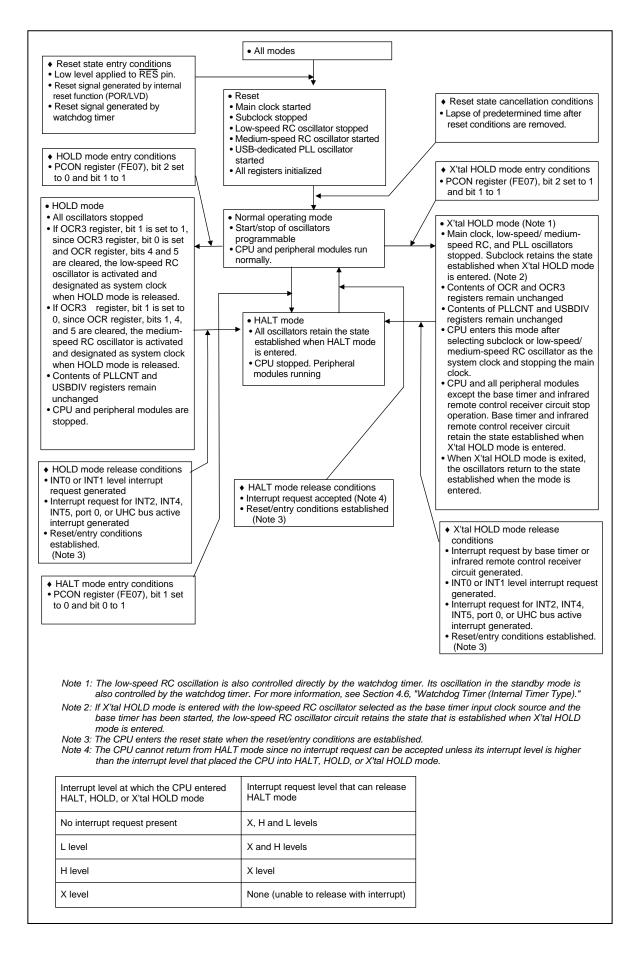

| 4.3 Sta  | andby Function 4-15                                       |

| 4.3.1    | Overview                                                  |

| 4.3.2    | Functions4-15                                             |

| 4.3.3    | Related Register4-16                                      |

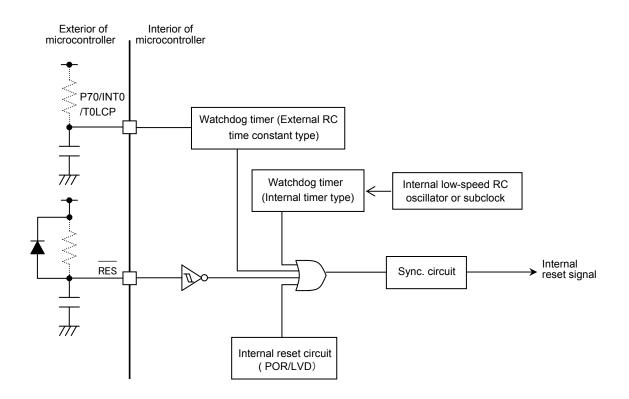

| 4.4 Re   | set Function 4-21                                         |

| 4.4.1    | Overview4-21                                              |

| 4.4.2    | Functions4-21                                             |

| 4.4.3    | Reset State                                               |

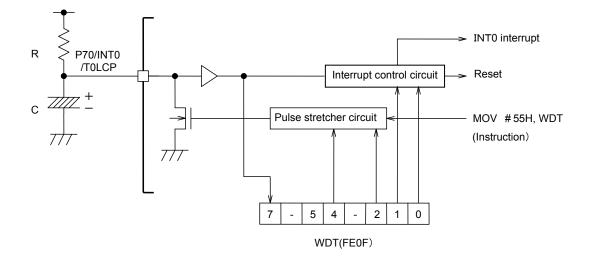

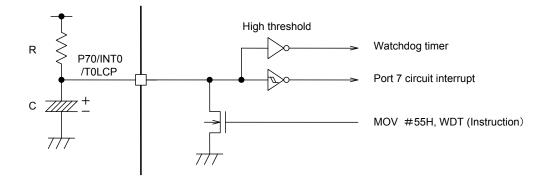

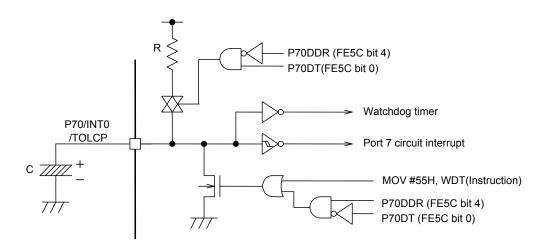

| 4.5 Wa   | atchdog Timer (External RC Time Constant Type) 4-23       |

| 4.5.1    | Overview                                                  |

| 4.5.2    | Functions4-23                                             |

| 4.5.3    | Circuit Configuration4-23                                 |

| 4.5.4    | Related Registers                                         |

| 4.5.5    | Using the Watchdog Timer4-26                              |

|          |                                                           |

|          | Contonto                                                        |

|----------|-----------------------------------------------------------------|

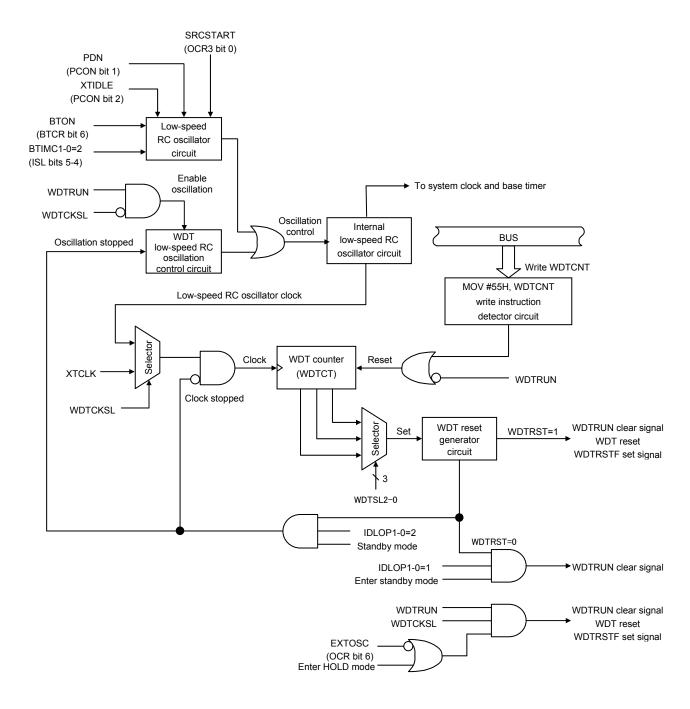

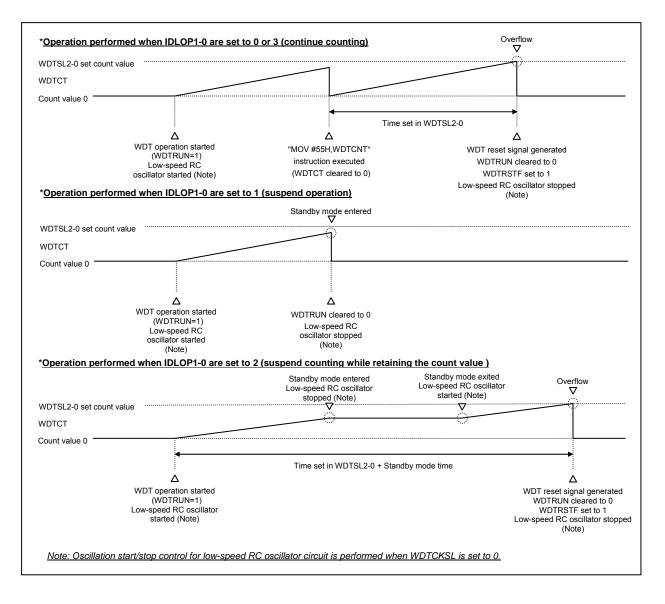

| 4.6 Wa   | atchdog Timer (Internal Timer Type)4-29                         |

| 4.6.1    | Overview4-29                                                    |

| 4.6.2    | Functions4-29                                                   |

| 4.6.3    | Circuit Configuration4-30                                       |

| 4.6.4    | Related Register4-32                                            |

| 4.6.5    | Using the Watchdog Timer4-34                                    |

| 4.6.6    | Notes on the Use of the Watchdog Timer4-35                      |

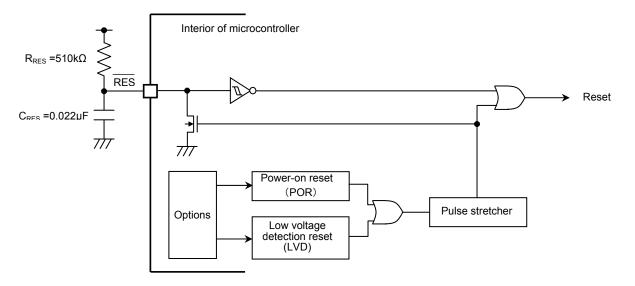

| 4.7 Inte | ernal Reset Function 4-36                                       |

| 4.7.1    | Overview4-36                                                    |

| 4.7.2    | Functions4-36                                                   |

| 4.7.3    | Circuit Configuration4-36                                       |

| 4.7.4    | Options 4-37                                                    |

| 4.7.5    | Sample Operating Waveforms of the Internal Reset Circuit4-39    |

| 4.7.6    | Notes on the Use of the Internal Reset Circuit4-40              |

| 4.7.7    | Notes to be Taken When Not Using the Internal Reset Circuit4-42 |

|          |                                                                 |

# Appendixes

| Appendix-I  | Special Function Register (SFR) MapAl-(1-9) |

|-------------|---------------------------------------------|

| Appendix-II | Port Block Diagrams All-(1-10)              |

# 1. Overview

## 1.1 Overview

The LC871K00 series is an 8-bit microcontroller that, centered around a CPU running at a minimum bus cycle time of 83.3 ns, integrates on a single chip a number of hardware features such as 64K-byte flash ROM (onboard programmable), 8192-byte RAM, an on-chip debugger, a sophisticated 16-bit timer/ counter (may be divided into 8-bit timers), 16-bit timer (may be divided into 8-bit timers or 8-bit PWMs), four 8-bit timers with a prescaler, a base timer serving as a time-of-day clock, two synchronous SIO interfaces (with an automatic transfer function), an asynchronous/synchronous SIO interface, a single master I<sup>2</sup>C/synchronous SIO interface, a UART interface (full duplex), two full-/low-speed USB interfaces (with host control function), a 12-bit 12-channel AD converter, two 12-bit PWM channels, a system clock frequency divider, an infrared remote control receive function, an internal reset circuit, and 44-source 10-vector interrupt function.

## 1.2 Features

- Flash ROM

- Capable of onboard programming with a wide supply voltage range of 3.0 to 5.5V

- 128-byte block erase

- Writing in two-byte units

- 65536 × 8 bits

- RAM

- $8192 \times 9$  bits

- Bus cycle time

- 83.3 ns (at CF=12 MHz)

Note: The bus cycle time here refers to the ROM read speed.

- Minimum instruction cycle time (Tcyc)

- 250 ns (at CF=12 MHz)

- Ports

- I/O ports

Ports whose input/output can be specified in 1-bit units:

- USB ports

- Dedicated oscillator ports

- Input-only port (also used for oscillation)

- Reset pin:

- Power pins:

34 (P00 to P07, P10 to P17, P20 to P25, P30 to P34, P70 to P73, PWM0, PWM1, XT2)

4 (UHAD+, UHAD-, UHBD+, UHBD-)

2 (CF1, CF2)

1 (XT1)

1 (RES)

6 (VSS1 to VSS3, VDD1 to VDD3)

#### • Timers

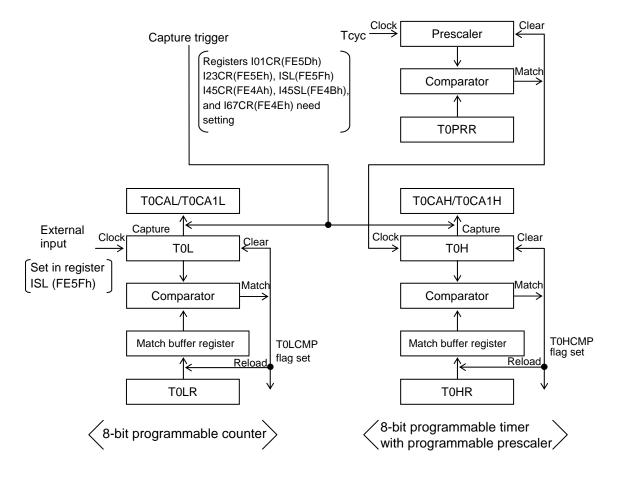

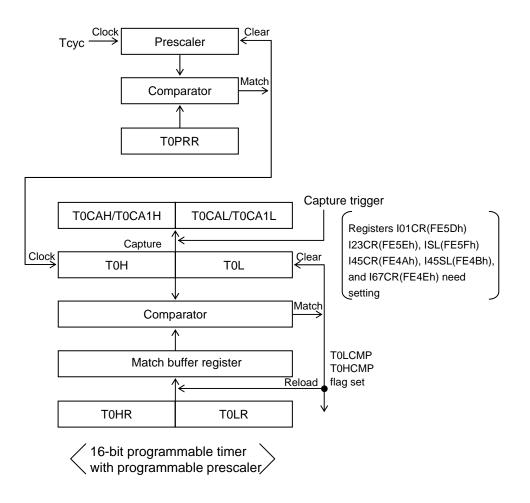

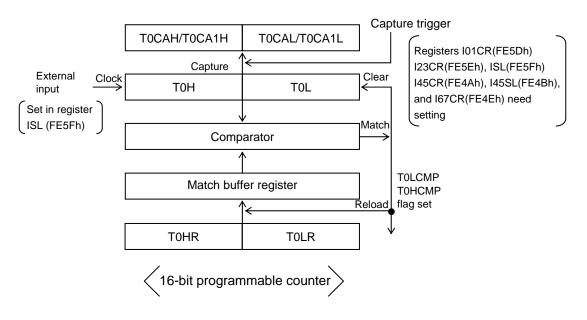

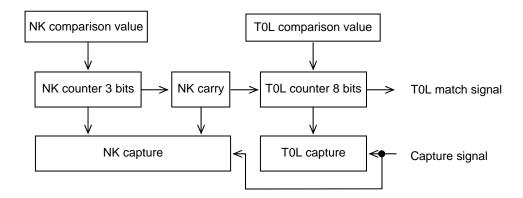

- Timer 0: 16-bit timer/counter with two capture registers

- Mode 0: 8-bit timer with an 8-bit programmable prescaler (with two 8-bit capture registers)  $\times$  2 channels

- Mode 1: 8-bit timer with an 8-bit programmable prescaler (with two 8-bit capture registers) + 8-bit counter (with two 8-bit capture registers)

- Mode 2: 16-bit timer with an 8-bit programmable prescaler (with two 16-bit capture registers)

- Mode 3: 16-bit counter (with two 16-bit capture registers)

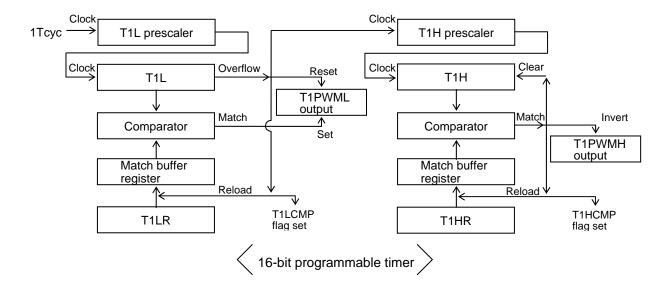

- Timer 1: 16-bit timer/counter that supports PWM/toggle output

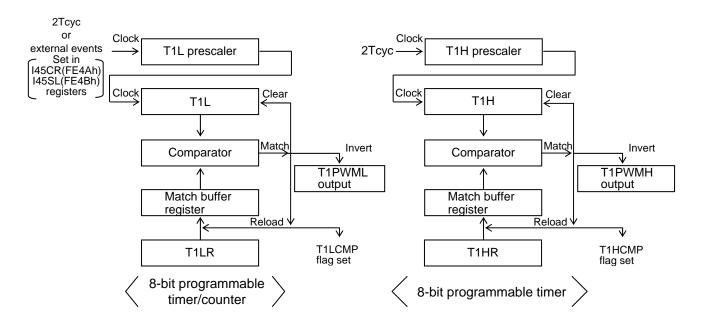

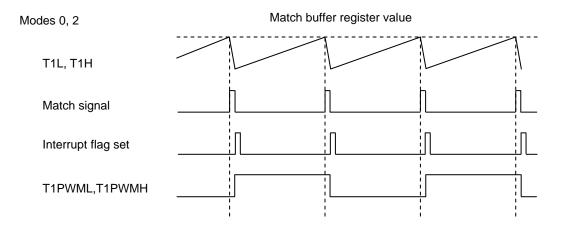

- Mode 0: 8-bit timer with an 8-bit prescaler (with toggle output) + 8-bit timer/counter with an 8-bit prescaler (with toggle output)

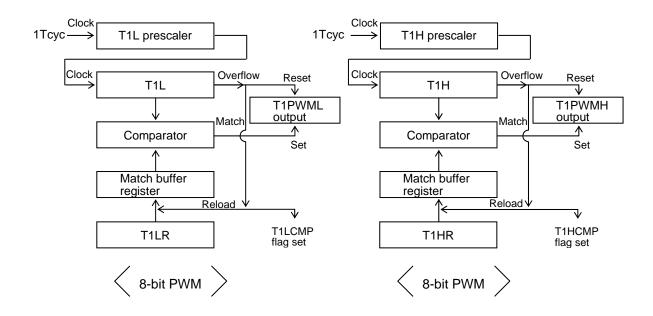

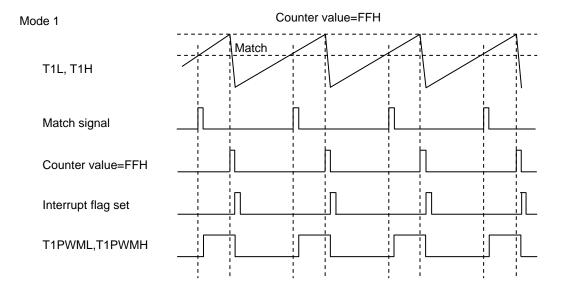

- Mode 1: 8-bit PWM with an 8-bit prescaler  $\times$  2 channels

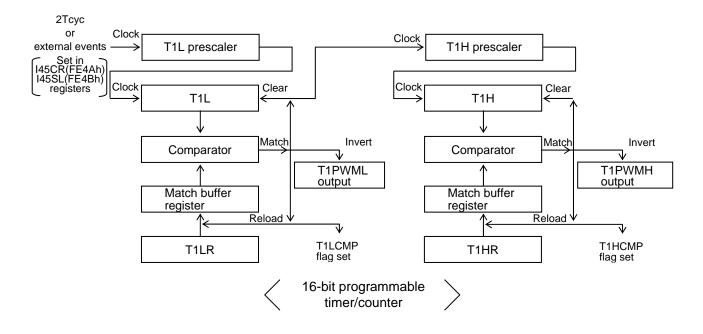

- Mode 2: 16-bit timer/counter with an 8-bit prescaler (with toggle output) (toggle output also possible from the low-order 8 bits)

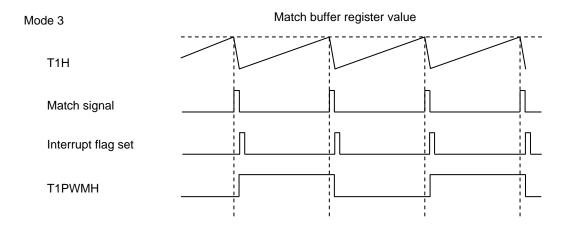

- Mode 3: 16-bit timer with an 8-bit prescaler (with toggle output) (lower-order 8 bits can be used as PWM.)

- Timer 4: 8-bit timer with a 6-bit prescaler

- Timer 5: 8-bit timer with a 6-bit prescaler

- Timer 6: 8-bit timer with a 6-bit prescaler (with toggle output)

- Timer 7: 8-bit timer with a 6-bit prescaler (with toggle output)

- Base timer

- The clock can be selected from among the subclock (32.768 kHz crystal oscillation), low-speed RC oscillator, system clock, and timer 0 prescaler output.

- 2) Interrupts can be generated at five specified time intervals.

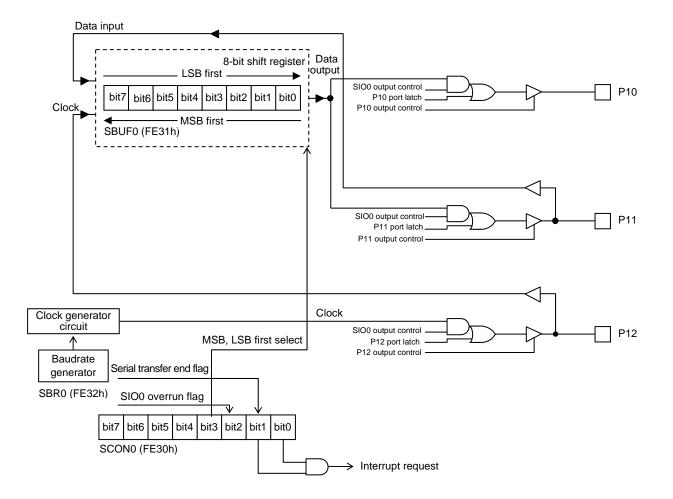

- Serial interface

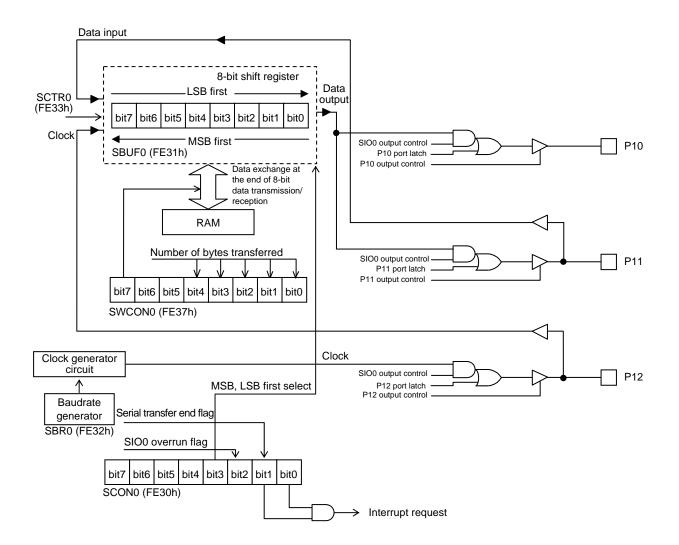

- SIO0: Synchronous serial interface

- 1) LSB first/MSB first selectable

- 2) Transfer clock cycle: 4/3 to 512/3 Tcyc

- Automatic continuous data communication (1 to 256 bits can be specified in 1-bit units) (Suspension and resumption of data transfer possible in 1-byte units)

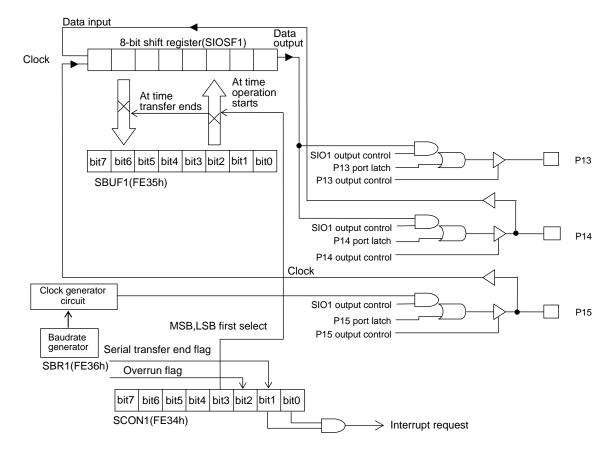

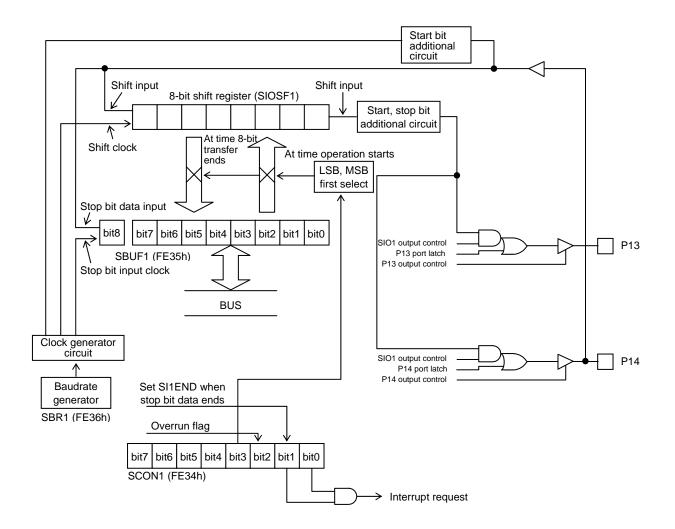

- SIO1: 8-bit asynchronous/synchronous serial interface

- Mode 0: Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 Tcyc transfer clock) Mode 1: Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 Tcyc baudrate)

- Mode 2: Bus mode 1 (start bit, 8 data bits, 2 to 512 Tcyc transfer clock)

- Mode 3: Bus mode 2 (start detection, 8 data bits, stop detection)

- SIO4: Synchronous serial interface

- 1) LSB first/MSB first selectable

- 2) Transfer clock cycle: 4/3 to 1020/3 Tcyc

- Automatic continuous data communication (1 to 8192 bytes can be specified in 1-byte units) (Suspension and resumption of data transfer possible in 1-byte or word units)

- 4) Clock polarity can be selected.

- 5) Built-in CRC16 computation circuit

- SMIIC0: Single master I<sup>2</sup>C/synchronous 8-bit serial I/O

- Mode 0: Single-master master mode communication

Mode 1: Synchronous 8-bit serial I/O (data MSB first)

- Full duplex UART

- 1) Data length: 7/8/9 bits

- 2) Stop bits: 1 bit (2 bits in continuous transmission mode)

- 3) Parity bit: None/even parity/odd parity (data length 8 bits only)

- 4) Baudrate: 16/3 to 8192/3Tcyc

- AD converter:  $12 \text{ bits} \times 12 \text{ channels}$

- PWM: Multifrequency 12-bit PWM × 2 channels

- Infrared remote control receiver circuit

- 1) Noise rejection function

- (Noise rejection filter time constant: approx. 120  $\mu$ s when selecting a 32.768 kHz crystal oscillator as a reference clock.)

- 2) Supports data encoding formats, including PPM (Pulse Position Modulation), Manchester encoding, and so on.

- 3) X'tal HOLD mode release function

- USB interface (with host control function)  $\times$  2 ports

- Supports full-speed (12 Mbps) and low-speed (1.5 Mbps).

- Supports four types of transfer (control transfer, bulk transfer, interrupt transfer, and isochronous transfer)

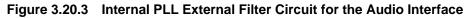

- Audio interface

- Sampling frequencies (fs): 8 kHz/11.025 kHz/12 kHz/16 kHz/22.05 kHz/24 kHz/32 kHz/44.1 kHz/48 kHz

- 2) Master clock: 256 fs/384 fs

- 3) Bit clock: 48 fs/64 fs

- 4) Data bit length: 16/18/20/24 bits

- 5) LSB first/MSB first selectable

- 6) Left-justified/right-justified/I<sup>2</sup>S format selectable

- Watchdog timer

- External RC time constant type

- 1) Interrupt generation/reset generation can be selected

- 2) WDT operation on entry into HALT or HOLD mode can be selected from operation continue mode or operation stop mode.

- Internal timer type

- 1) Capable of generating an internal reset on an overflow of a timer running on the low-speed RC oscillator clock or the subclock.

- 2) WDT operation on entry into HALT or HOLD mode can be selected from three modes (operation continue, operation stop, and operation stop while retaining the count value).

- Clock output function

- 1) Capable of generating a clock with a frequency of 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, or 1/64 of the source oscillator clock selected as the system clock.

- 2) Capable of generating the source oscillator clock for the subclock.

- Interrupts

- 44 sources, 10 vector addresses

- 1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt request of the level equal to or lower than the current interrupt is not accepted.

2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt with the lowest vector address has priority.

| No. | Vector | Level  | Interrupt Source                                                                                     |

|-----|--------|--------|------------------------------------------------------------------------------------------------------|

| 1   | 00003H | X or L | INT0                                                                                                 |

| 2   | 0000BH | X or L | INT1                                                                                                 |

| 3   | 00013H | H or L | INT2/T0L/INT4/UHC-A bus active/UHC-B bus active/remote control receive                               |

| 4   | 0001BH | H or L | INT3/INT5/base timer                                                                                 |

| 5   | 00023H | H or L | T0H/ INT6/UHC-A device connection/UHC-<br>A device disconnection/UHC-A resume                        |

| 6   | 0002BH | H or L | T1L/T1H/INT7/AIF start/SMIIC0/UHC-B<br>device connection/UHC-B device<br>disconnection/ UHC-B resume |

| 7   | 00033H | H or L | SIO0/UART1 receive end                                                                               |

| 8   | 0003BH | H or L | SIO1/SIO4/UART1 buffer empty/UART1<br>transmit end/AIF end                                           |

| 9   | 00043H | H or L | ADC/T6/T7/UHC-ACK/UHC-NAK/UHC<br>error/UHC-STALL                                                     |

| 10  | 0004BH | H or L | Port 0/PWM0/PWM1/T4/T5/UHC-SOF                                                                       |

- Priority levels: X > H > L

- When interrupts of the same level occur at the same time, the interrupt with the lowest vector address is processed first.

- Subroutine stack levels: Up to 4096 levels (The stack is allocated in RAM.)

- High-speed multiplication/division instructions

- 16 bits  $\times$  8 bits (5 Tcyc execution time)

- 24 bits  $\times$  16 bits (12 Tcyc execution time)

- 16 bits ÷ 8 bits (8 Tcyc execution time)

- 24 bits ÷ 16 bits (12 Tcyc execution time)

- Oscillator circuits and PLL

| • Medium-speed RC oscillator circuit (internal): | For system clock (approx. 1 MHz)                              |

|--------------------------------------------------|---------------------------------------------------------------|

| • Low-speed RC oscillator circuit (internal):    | For system clock, timers, and watchdog timer (approx. 30 kHz) |

| CF oscillator circuit:                           | For system clock                                              |

| Crystal oscillator circuit:                      | For system clock and time-of-day clock                        |

| • PLL circuit (internal):                        | For USB interface and audio interface                         |

|                                                  |                                                               |

- Internal reset circuit

- Power-on reset (POR) function

- 1) POR is generated only when power is turned on.

- 2) The POR release level can be selected from 8 levels (1.67, 1.97, 2.07, 2.37, 2.57V, 2.87V, 3.86V, and 4.35V) by setting options.

- Low-voltage detection reset (LVD) function

- 1) LVD and POR functions are combined to generate resets when power is turned on and when the power voltage falls below a certain level.

- 2) The use/non-use of the LVD function and the low voltage detection level can be selected from 7 levels (1.91, 2.01, 2.31, 2.51, 2.81V, 3.79V, and 4.28V) by setting options.

- Standby function

- HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation.

- 1) Oscillators do not stop automatically.

- 2) There are three ways of releasing HALT mode.

- <1> Low level input to the reset pin

- <2> Generating a reset by the watchdog timer or low-voltage detection

- <3> Generating an interrupt

- HOLD mode: Suspends instruction execution and the operation of the peripheral circuits.

1) The PLL, CF, RC, and crystal oscillators automatically stop operation.

- *Note:* The low-speed RC oscillation is also controlled directly by the watchdog timer. Its oscillation in the standby mode is also controlled by the watchdog timer.

- 2) There are five ways of releasing HOLD mode.

- <1> Low level input to the reset pin

- <2> Generating a reset by the watchdog timer or low-voltage detection

- <3> Establishing an interrupt source at either of INT0, INT1, INT2, INT4, and INT5 pins.

- \* INT0 and INT1 HOLD mode release is available only when level detection is set.

- <4> Establishing an interrupt source at port 0.

- <5> Establishing a bus active interrupt source in the USB host controller circuit.

- X'tal HOLD mode: Suspends instruction execution and the operation of the peripheral circuits except the base timer and infrared remote control receiver circuit.

- 1) The PLL, CF and RC oscillators automatically stop operation.

- *Note: The low-speed RC oscillation is also controlled directly by the watchdog timer. Its oscillation in the standby mode is also controlled by the watchdog timer.*

- Note: In an environment in which the base timer is run with its input clock source set to the lowspeed RC oscillator and X'tal HOLD mode is entered, the low-speed RC oscillator retains the state that is established when this mode is entered.

- 2) The state of crystal oscillation established when X'tal HOLD mode is entered is retained.

- 3) There are seven ways of releasing X'tal HOLD mode.

- <1> Low level input to the reset pin

- <2> Generating a reset by the watchdog timer or low-voltage detection.

- <3> Establishing an interrupt source at either of INT0, INT1, INT2, INT4, and INT5 pins

- \* INT0 and INT1 X'tal HOLD mode release is available only when level detection is set.

- <4> Establishing an interrupt source at port 0

- <5> Establishing an interrupt source in the base timer circuit

- <6> Establishing a bus active interrupt source in the USB host controller circuit

- <7> Establishing an interrupt source in the infrared remote control receiver circuit

- Package form

- SQFP48 (7×7) (Lead-free and halogen-free product)

- Development tools

- On-chip debugger: TCB87-Type B + LC87F1K64A or

TCB87-Type C (3-wire communication cable) + LC87F1K64A

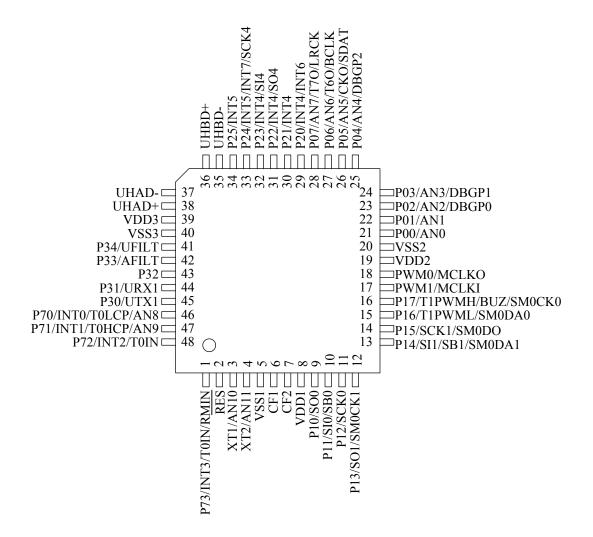

## 1.3 Pinout

SQFP48 (7×7)

| SQFP48 | NAME                  |

|--------|-----------------------|

| 1      | P73/INT3/T0IN/RMIN    |

| 2      | RES                   |

| 3      | XT1/AN10              |

| 4      | XT2/AN11              |

| 5      | VSS1                  |

| 6      | CF1                   |

| 7      | CF2                   |

| 8      | VDD1                  |

| 9      | P10/SO0               |

| 10     | P11/SI0/SB0           |

| 11     | P12/SCK0              |

| 12     | P13/SO1/SM0CK1        |

| 13     | P14/SI1/SB1/SM0DA1    |

| 14     | P15/SCK1/SM0DO        |

| 15     | P16/T1PWML/SM0DA0     |

| 16     | P17/T1PWMH/BUZ/SM0CK0 |

| 17     | PWM1/MCLKI            |

| 18     | PWM0/MCLKO            |

| 19     | VDD2                  |

| 20     | VSS2                  |

| 21     | P00/AN0               |

| 22     | P01/AN1               |

| 23     | P02/AN2/DBGP0         |

| 24     | P03/AN3/DBGP1         |

| SQFP48 | NAME               |

|--------|--------------------|

| 25     | P04/AN4/DBGP2      |

| 26     | P05/AN5/CKO/SDAT   |

| 27     | P06/AN6/T6O/BCLK   |

| 28     | P07/AN7/T7O/LRCK   |

| 29     | P20/INT4/INT6      |

| 30     | P21/INT4           |

| 31     | P22/INT4/SO4       |

| 32     | P23/INT4/SI4       |

| 33     | P24/INT5/INT7/SCK4 |

| 34     | P25/INT5           |

| 35     | UHBD-              |

| 36     | UHBD+              |

| 37     | UHAD-              |

| 38     | UHAD+              |

| 39     | VDD3               |

| 40     | VSS3               |

| 41     | P34/UFILT          |

| 42     | P33/AFILT          |

| 43     | P32                |

| 44     | P31/URX1           |

| 45     | P30/UTX1           |

| 46     | P70/INT0/T0LCP/AN8 |

| 47     | P71/INT1/T0HCP/AN9 |

| 48     | P72/INT2/T0IN      |

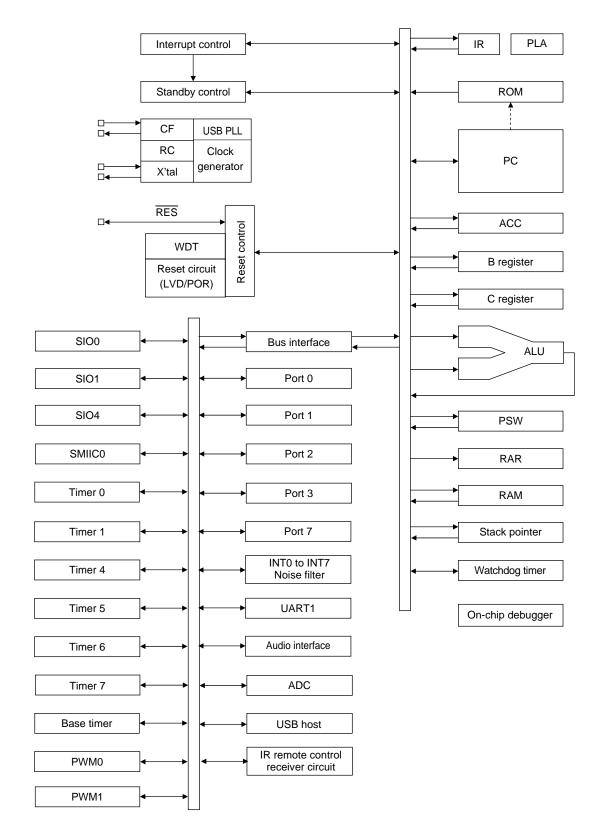

# 1.4 System Block Diagram

# 1.5 Pin Functions

| Name        | I/O |               |                                                           | Des           | cription                          |             |               | Option |  |  |  |  |

|-------------|-----|---------------|-----------------------------------------------------------|---------------|-----------------------------------|-------------|---------------|--------|--|--|--|--|

| VSS1, VSS2, | _   | Power supp    | oly pin (-)                                               |               |                                   |             |               | No     |  |  |  |  |

| VSS3        |     |               | • • • •                                                   |               |                                   |             |               |        |  |  |  |  |

| VDD1,VDD2   | _   | Power supp    | oly pin (+)                                               |               |                                   |             |               | No     |  |  |  |  |

| VDD3        | _   | USB refere    |                                                           | supply pin    |                                   |             |               | Yes    |  |  |  |  |

| Port 0      | I/O |               | 8-bit I/O port                                            |               |                                   |             |               |        |  |  |  |  |

| P00 to P07  |     | -             |                                                           | in 1-bit unit | s                                 |             |               | Yes    |  |  |  |  |

| F00 t0 F07  |     |               | -                                                         |               | n and off in 1-                   | bit units   |               |        |  |  |  |  |

|             |     | • HOLD re     | lease input                                               |               |                                   |             |               |        |  |  |  |  |

|             |     | • Port 0 inte | errupt input                                              | t             |                                   |             |               |        |  |  |  |  |

|             |     | • Pin functi  | ons                                                       |               |                                   |             |               |        |  |  |  |  |

|             |     | AD conv       | verter input                                              | port: AN0     | to AN7 (P00 t                     | o P07)      |               |        |  |  |  |  |

|             |     | On-chip       | debugger p                                                | oin: DBGP0    | to DBGP2 (P                       | 02 to P04)  |               |        |  |  |  |  |

|             |     |               |                                                           |               | o interface SD                    |             |               |        |  |  |  |  |

|             |     |               |                                                           |               | io interface B                    |             |               |        |  |  |  |  |

|             |     |               |                                                           | e output/aud  | io interface L                    | RCK I/O     |               |        |  |  |  |  |

| Port 1      | I/O | • 8-bit I/O   | -                                                         |               |                                   |             |               | Yes    |  |  |  |  |

| P10 to P17  |     |               | I/O can be specified in 1-bit units                       |               |                                   |             |               |        |  |  |  |  |

|             |     | 1             | Pull-up resistors can be turned on and off in 1-bit units |               |                                   |             |               |        |  |  |  |  |

|             |     |               | • Pin functions                                           |               |                                   |             |               |        |  |  |  |  |

|             |     |               | P10: SIO0 data output                                     |               |                                   |             |               |        |  |  |  |  |

|             |     |               | 00 data inp                                               |               |                                   |             |               |        |  |  |  |  |

|             |     |               | 00 clock I/C                                              |               | 1 1 1/0                           |             |               |        |  |  |  |  |

|             |     |               |                                                           | put/SMIIC0    |                                   |             | 4             |        |  |  |  |  |

|             |     |               | -                                                         |               | SMIIC0 bus I                      |             | -             |        |  |  |  |  |

|             |     |               |                                                           |               | lata output (3-<br>⁄IIIC0 bus I/O |             |               |        |  |  |  |  |

|             |     |               |                                                           |               | izzer output/S                    |             |               |        |  |  |  |  |

| Deut 2      | I/O | • 6-bit I/O   |                                                           | In output/ot  | izzei output/s                    |             | CK 1/O        | 3.7    |  |  |  |  |

| Port 2      | 1/0 | -             | -                                                         | in 1-bit unit | e.                                |             |               | Yes    |  |  |  |  |

| P20 to P25  |     |               | -                                                         |               | s<br>n and off in 1-              | hit units   |               |        |  |  |  |  |

|             |     | • Pin functi  |                                                           |               |                                   | on units    |               |        |  |  |  |  |

|             |     |               |                                                           | /O /HOLD 1    | elease input/ti                   | imer 1 ever | nt innut/     |        |  |  |  |  |

|             |     | 120 10 1      |                                                           |               | put/timer 0H                      |             |               |        |  |  |  |  |

|             |     | P24 to P      |                                                           |               | release input/ti                  |             |               |        |  |  |  |  |

|             |     | 121001        |                                                           | -             | mer 0H captur                     |             | t input timer |        |  |  |  |  |

|             |     | P20: IN       |                                                           | mer 0L capt   |                                   | • mp av     |               |        |  |  |  |  |

|             |     |               | 04 data I/O                                               |               |                                   |             |               |        |  |  |  |  |

|             |     |               | P23: SIO4 data I/O                                        |               |                                   |             |               |        |  |  |  |  |

|             |     |               | P24: INT7 input/timer 0H capture 1 input/SIO4 clock I/O   |               |                                   |             |               |        |  |  |  |  |

|             |     |               |                                                           | -             | 1                                 |             |               |        |  |  |  |  |

|             |     | Interrupt de  | election mo                                               | de            |                                   | r           |               |        |  |  |  |  |

|             |     |               | Rising                                                    | Falling       | Rising &<br>Falling               | H level     | L level       |        |  |  |  |  |

|             |     | INT4          | 0                                                         | 0             | 0                                 | ×           | ×             |        |  |  |  |  |

|             |     | INT5          | 0                                                         | 0             | 0                                 | ×           | ×             |        |  |  |  |  |

|             |     | INT5<br>INT6  | 0                                                         | 0             | 0                                 | ×           | ×             |        |  |  |  |  |

|             |     |               |                                                           | 1             |                                   | 1           |               | 1      |  |  |  |  |

Continued on next page

Continued from preceding page

| Name       | I/O |              | Description         C           5-bit I/O port         6                                                       |                        |                                  |           |           |     |  |  |  |  |  |  |

|------------|-----|--------------|----------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------|-----------|-----------|-----|--|--|--|--|--|--|

| Port 3     | I/O | • 5-bit I/O  |                                                                                                                |                        |                                  |           |           | Yes |  |  |  |  |  |  |

| P30 to P34 |     |              |                                                                                                                | in 1-bit unit          |                                  |           |           |     |  |  |  |  |  |  |

| 150 10 151 |     |              |                                                                                                                | be turned o            | n and off in 1-                  | bit units |           |     |  |  |  |  |  |  |

|            |     | • Pin functi | ions                                                                                                           |                        |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              | ART1 transi                                                                                                    | nit                    |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              | rt1 receive                                                                                                    |                        |                                  |           |           |     |  |  |  |  |  |  |

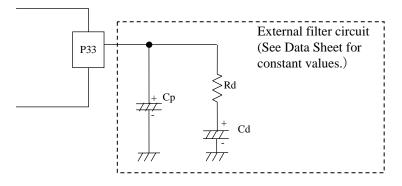

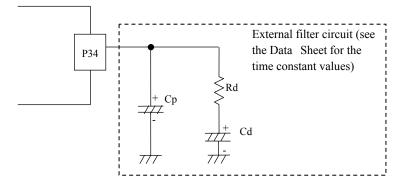

|            |     |              | P33: Audio interface PLL filter circuit connection pin<br>P34: USB interface PLL filter circuit connection pin |                        |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                | PLL filter             | circuit connect                  | tion pin  |           |     |  |  |  |  |  |  |

| Port 7     | I/O | • 4-bit I/O  |                                                                                                                |                        |                                  |           |           | No  |  |  |  |  |  |  |

| P70 to P73 |     |              |                                                                                                                | in 1-bit unit          |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                | be turned o            | n and off in 1-                  | bit units |           |     |  |  |  |  |  |  |

|            |     | • Pin funct  |                                                                                                                |                        |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | e input/timer 0                  | L capture |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                | og timer out           |                                  | TT /      | . ,       |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | e input/timer 0                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | e input/timer 0<br>clock counter |           | u/umer oL |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | ter)/timer 0 ev                  |           | mer 0H    |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | note control re                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | (P70), AN9 (P                    |           |           |     |  |  |  |  |  |  |

|            |     | Interrupt de | etection mo                                                                                                    | ode                    |                                  | ,         |           |     |  |  |  |  |  |  |

|            |     |              | Rising                                                                                                         | Falling                | Rising &<br>Falling              | H level   | L level   |     |  |  |  |  |  |  |

|            |     | INT0         | 0                                                                                                              | 0                      | ×                                | 0         | 0         |     |  |  |  |  |  |  |

|            |     | INT0<br>INT1 | 0                                                                                                              | 0                      | ×                                | 0         | 0         |     |  |  |  |  |  |  |

|            |     | INT1<br>INT2 | 0                                                                                                              | 0                      | Ô                                | ×         | ×         |     |  |  |  |  |  |  |

|            |     | INT2<br>INT3 | 0                                                                                                              | Õ                      | 0                                | ×         | ×         |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | Ű                                | ~         | ~         |     |  |  |  |  |  |  |

| PWM0       | I/O |              | nd PWM1 o                                                                                                      |                        |                                  |           |           | No  |  |  |  |  |  |  |

| PWM1       |     |              | purpose inp                                                                                                    | ut port                |                                  |           |           |     |  |  |  |  |  |  |

|            |     | • Pin functi |                                                                                                                | <b>C</b>               |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | r clock output                   |           |           |     |  |  |  |  |  |  |

|            | 1/0 |              |                                                                                                                |                        | r clock input                    |           |           |     |  |  |  |  |  |  |

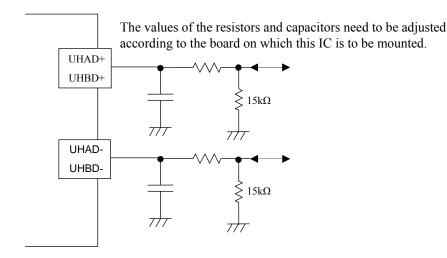

| UHAD-      | I/O | USB-A pol    | ri dala 1/0 p                                                                                                  | oin /general-          | -purpose I/O p                   | ort       |           | No  |  |  |  |  |  |  |

| UHAD+      |     |              |                                                                                                                |                        |                                  |           |           |     |  |  |  |  |  |  |

| UHBD-      | I/O | USB-B por    | rt data I/O p                                                                                                  | oin /general-          | purpose I/O p                    | ort       |           | No  |  |  |  |  |  |  |

| UHBD+      |     |              |                                                                                                                |                        |                                  |           |           |     |  |  |  |  |  |  |

|            | I/O | External re  | set input/in                                                                                                   | ternal reset           | output nin                       |           |           | No  |  |  |  |  |  |  |

| RES        |     |              | -                                                                                                              |                        |                                  |           |           | -   |  |  |  |  |  |  |

| XT1        | Ι   |              |                                                                                                                | esonator inp           | but pin                          |           |           | No  |  |  |  |  |  |  |

|            |     | • Pin functi | ons<br>-purpose in                                                                                             | nut nort               |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              | -purpose in                                                                                                    | put port<br>port: AN1( | )                                |           |           |     |  |  |  |  |  |  |

| VT2        | I/O |              |                                                                                                                | esonator ou            |                                  |           |           | ٦T  |  |  |  |  |  |  |

| XT2        | 1/0 | • Pin functi |                                                                                                                |                        | ւթութու                          |           |           | No  |  |  |  |  |  |  |

|            |     |              |                                                                                                                | O port                 |                                  |           |           |     |  |  |  |  |  |  |

|            |     |              |                                                                                                                |                        | l                                |           |           |     |  |  |  |  |  |  |

| CF1        | Ι   |              | General-purpose I/O port<br>AD converter input port: AN11                                                      |                        |                                  |           |           |     |  |  |  |  |  |  |

| CFI        |     | Ceramic/ci   | ystal resona                                                                                                   | ator input pi          | n                                |           |           | No  |  |  |  |  |  |  |

# 1.6 On-chip Debugger Pin Connection Requirements

For the treatment of the on-chip debugger pins, refer to the separately available document entitled "On-chip Debugger Installation Manual".

| Pin                       | Recommended Unused I                                | Pin Connections |

|---------------------------|-----------------------------------------------------|-----------------|

| PIN                       | Board                                               | Software        |

| P00 to P03,<br>P05 to P07 | Open                                                | Output low      |

| P04                       | Pulled down with a resistor of $100k\Omega$         | -               |

| P10 to P17                | Open                                                | Output low      |

| P20 to P25                | Open                                                | Output low      |

| P30 to P34                | Open                                                | Output low      |

| P70 to P73                | Open                                                | Output low      |

| PWM0, PWM1                | Open                                                | Output low      |

| UHAD+, UHAD-              | Open                                                | Output low      |

| UHBD+, UHBD-              | Open                                                | Output low      |

| XT1                       | Pulled down with a resistor of $100k\Omega$ or less | -               |

| XT2                       | Open                                                | Output low      |

# 1.7 Recommended Unused Pin Connections

Note: Since P34 is multiplexed with UFILT, it must be configured for input when using the USB function. Since P33 is multiplexed with AFILT, it must be configured for input when using the PLL circuit for the audio interface.

# **1.8 Port Output Types**

The table below lists the types of port outputs and the presence/absence of a pull-up resistor. Data can be read into any input port even if it is in output mode.

| Port         | Option<br>Selected in<br>Units of | Option<br>Type | Output Type                  | Pull-up Resistor |

|--------------|-----------------------------------|----------------|------------------------------|------------------|

| P00 to P07   | 1 bit                             | 1              | CMOS                         | Programmable     |

| P10 to P17   |                                   |                |                              |                  |

| P20 to P25   |                                   | 2              | N-channel open drain         | Programmable     |

| P30 to P34   |                                   |                |                              |                  |

| P70          | —                                 | No             | N-channel open drain         | Programmable     |

| P71 to P73   | —                                 | No             | CMOS                         | Programmable     |

| PWM0, PWM1   | —                                 | No             | CMOS                         | No               |

| UHAD+, UHAD- | —                                 | No             | CMOS                         | No               |

| UHBD+, OHBD- |                                   |                |                              |                  |

| XT1          | —                                 | No             | Input only                   | No               |

| XT2          | —                                 | No             | 32.768 kHz crystal resonator | No               |

|              |                                   |                | output                       |                  |

|              |                                   |                | (N-channel open drain when   |                  |

|              |                                   |                | selected as general-purpose  |                  |

|              |                                   |                | output port)                 |                  |

# 1.9 User Option Table

| Option                  | Option to be<br>Applied on | Flash-ROM<br>Version | Option Selected<br>in Units of | Option Selection     |

|-------------------------|----------------------------|----------------------|--------------------------------|----------------------|

|                         | D00 4- D07                 | 0                    | 11.4                           | CMOS                 |

|                         | P00 to P07                 | -                    | 1 bit                          | N-channel open drain |

|                         | D10 4- D17                 | 0                    | 11.4                           | CMOS                 |

| D ( ) ()                | P10 to P17                 | 0                    | 1 bit                          | N-channel open drain |

| Port output type        | D20 4- D25                 | 0                    | 11.4                           | CMOS                 |

|                         | P20 to P25                 | 0                    | 1 bit                          | N-channel open drain |

|                         | D20 / D24                  | 0                    | 1.1.1                          | CMOS                 |

|                         | P30 to P34                 | 0                    | 1 bit                          | N-channel open drain |

| Program start           |                            | 0                    |                                | 00000h               |

| address                 | -                          | 0                    | -                              | 0FE00h               |

|                         |                            | 0                    |                                | Use                  |

|                         | USB regulator              | 0                    | _                              | Non-use              |

|                         | USB regulator              | 0                    |                                | Use                  |

| USB regulator           | (HOLD mode)                | 0                    | _                              | Non-use              |

|                         | USB regulator              | 0                    |                                | Use                  |

|                         | (HALT mode)                | 0                    | _                              | Non-use              |

| Main clock              |                            | 0                    |                                | Enable               |

| 8 MHz select            | -                          | 0                    | -                              | Disable              |

| Low-voltage             |                            | 0                    |                                | Enable: Use          |

| detection reset         | Detection function         | 0                    | -                              | Disable: Non-use     |

| function                | Detection level            | 0                    | -                              | 7 levels             |

| Power-on reset function | Power-on reset level       | 0                    | -                              | 8 levels             |

# 1.10 USB Reference Power Supply Option

When a voltage 4.5 to 5.5V is supplied to VDD1 and the internal USB reference voltage circuit is activated, the reference voltage for USB port output is generated. The active/inactive state of reference voltage circuit can be switched by the option selection.

The option selection must be made according to the voltage supplied to VDD1 as described below.

| VD              | D1 Voltage (V)             |        | 4.5 to 5.5 |          | 3.0 to 3.6 |

|-----------------|----------------------------|--------|------------|----------|------------|

|                 | USB regulator              | Use    | Use        | Use      | Non-use    |

| Option setting  | USB regulator in HOLD mode | Use    | Non-use    | Non-use  | Non-use    |

|                 | USB regulator in HALT mode | Use    | Non-use    | Use      | Non-use    |

| Reference       | Normal operating mode      | Active | Active     | Active   | Inactive   |

| voltage circuit | HOLD mode                  | Active | Inactive   | Inactive | Inactive   |

| operation       | HALT mode                  | Active | Inactive   | Active   | Inactive   |

|                 |                            | (1)    | (2)        | (3)      | (4)        |

When the USB reference voltage circuit is made inactive, the level of the reference voltage for USB port output is equal to VDD1 level.

Selection (2) or (3) can be used to set the reference voltage circuit inactive in HALT or HOLD mode.

When the reference voltage circuit is activated, the current drain increases by approximately  $100\mu A$  compared with that when the reference voltage circuit is inactive.

Do not apply a voltage of 3.6V or more to UHAD+, UHAD-, UHBD+, and UHBD- pins when the reference voltage generator circuit is active.

# 2. Internal Configuration

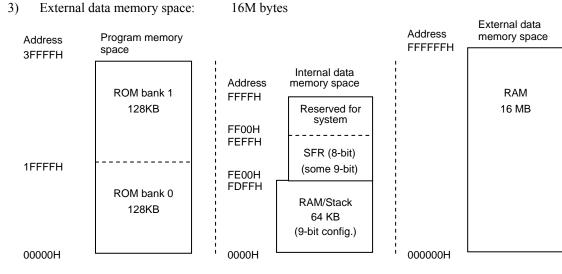

#### 2.1 Memory Space

LC870000 series microcontrollers have the following three types of memory space:

- 1) Program memory space:

- 2) Internal data memory space:

- 256K bytes (128K bytes  $\times$  2 banks)

- 64K bytes (0000H to FDFFH out of 0000H to FFFFH is shared with the stack area.)

Note: SFR is the area in which special function registers such as the accumulator are allocated (see Appendix A-I).

Figure 2.1.1 Types of Memory Space

#### 2.2 **Program Counter (PC)**

The program counter (PC) is made up of 17 bits and a bank flag BNK. The value of BNK determines the bank. The low-order 17 bits of the PC allows linear access to the 128K ROM space in the current bank.

Normally, the PC advances automatically in the current bank on each execution of an instruction. Bank switching is accomplished by executing a Return instruction after pushing necessary addresses onto the stack. When executing a branch or subroutine instruction, when accepting an interrupt, or when a reset is generated, the value corresponding to each operation is loaded into the PC.

Table 2.2.1 lists the values that are loaded into the PC when the respective operations are performed.

|         |                    | Operation                          | PC Value                                                     | <b>BNK Value</b> |

|---------|--------------------|------------------------------------|--------------------------------------------------------------|------------------|

| Inter-  | Reset (Note)       |                                    | 00000Н                                                       | 0                |

| rupt    |                    |                                    | 0FE00H                                                       | 0                |

|         | INT0               |                                    | 00003H                                                       | 0                |

|         | INT1               |                                    | 0000BH                                                       | 0                |

|         | INT2/T0L/INT4/U    | JHC-A bus active/UHC-B bus active/ | 00013H                                                       | 0                |

|         | remote control rec | eive                               |                                                              |                  |

|         | INT3/INT5/base ti  | mer                                | 0001BH                                                       | 0                |

|         | T0H/INT6/UHC-A     | A device connect/UHC-A device      | 00023H                                                       | 0                |

|         | disconnect/UHC-A   | A resume                           |                                                              |                  |

|         |                    | IF start/SMIIC0/UHC-B device       | 0002BH                                                       | 0                |

|         |                    | evice disconnect/UHC-B resume      |                                                              |                  |

|         | SIO0/UART1 rece    |                                    | 00033H                                                       | 0                |

|         |                    | 1 buffer empty/UART1 transmit end/ | 0003BH                                                       | 0                |

|         | AIF end            |                                    |                                                              |                  |

|         |                    | -ACK/UHC-NAK/UHC error/UHC-        | 00043H                                                       | 0                |

|         | STALL              |                                    | 0004011                                                      | 0                |

|         |                    | /M1/T4/T5/UHC-SOF                  | 0004BH                                                       | 0                |

| Uncon   | ditional branch    | JUMP a17                           | PC=a17                                                       | Unchanged        |

|         |                    | BR r12                             | PC=PC+2+r12[-2048 to +2047]                                  | Unchanged        |

|         | tional branch      | BE, BNE, DBNZ, DBZ, BZ, BNZ,       | PC=PC+nb+r8[-128 to +127]                                    | Unchanged        |

| instruc |                    | BZW, BNZW, BP, BN, BPC             | nb: Number of instruction bytes                              | T                |

| Call in | structions         | CALL a17                           | PC=a17                                                       | Unchanged        |

|         |                    | RCALL r12                          | PC=PC+2+r12[-2048 to +2047]                                  | Unchanged        |

|         |                    | RCALLA                             | PC=PC+1+Areg[0 to +255]                                      | Unchanged        |

| Returr  | n instructions     | RET, RETI                          | PC16 to 08=(SP)                                              | BNK is set to    |

|         |                    |                                    | PC07 to 00=(SP-1)                                            | bit 8 of         |

|         |                    |                                    | (SP) denotes the contents of                                 | (SP-1).          |

|         |                    |                                    | RAM address designated by the value of the stack pointer SP. |                  |

| Stande  | ard instructions   | NOP, MOV, ADD,                     | PC=PC+nb                                                     | Unchanged        |

| Standa  |                    | $1001, 1000, ADD, \dots$           | nb: Number of instruction bytes                              | Unchanged        |

Table 2.2.1 Values Loaded in the PC

Note: For the flash version, the program start addresson on reset can be selected by setting options.

# 2.3 Program Memory (ROM)

This series of microcontrollers has a program memory space of 256K bytes, but the size of the ROM that is actually incorporated in the microcontroller varies with the type of microcontroller. The ROM table look-up instruction (LDC) can be used to reference all ROM data within the bank. Of the ROM space, the 256 bytes in ROM bank 0 (1FF00H to 1FFFFH for ROM size of 64K and above, and 0FF00H to 0FFFFH for ROM size of 64K and below) is reserved as the option area. Consequently, this area is not available as a program area.

# 2.4 Internal Data Memory (RAM)

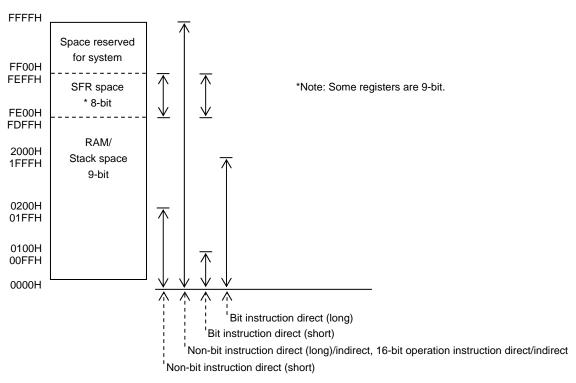

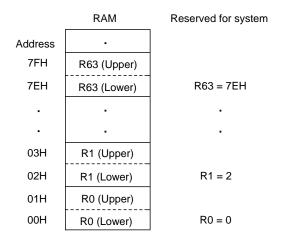

LC870000 series microcontrollers have an internal data memory space of 64K bytes, but the size of the RAM that is actually incorporated in the microcontroller varies with the type of the microcontroller. Nine bits are used to access addresses 0000H to FDFFH of the 128K ROM space and 8 or 9 bits are used to access addresses FE00H to FFFFH. The 9th bit of RAM is implemented by bit 1 of the PSW and can be read and written.

The 128 bytes of RAM from 0000H to 007FH are paired to form 64 2-byte indirect address registers. The bit length of these indirect registers is normally 16 bits (8 bits  $\times$  2). When they are used by the ROM table look-up instruction (LDC), however, their bit length is set to 17 bits (9 high-order bits + 8 low-order bits).

As shown in Figure 2.4.1, the available instructions vary depending on the RAM address.

The efficiency of the ROM used and a higher execution speed can be attempted using these instructions properly.

Figure 2.4.1 RAM Addressing Map

When the value of the PC is stored in RAM during the execution of a subroutine call instruction or interrupt, assuming that SP represents the current value of the stack pointer, the value of BNK and the low-order 8 bits of the (17-bit) PC are stored in RAM address SP+1 and the high-order 9 bits in SP+2, after which SP is set to SP+2.

# 2.5 Accumulator/A Register (ACC/A)

The accumulator (ACC), also called the A register, is an 8-bit register that is used for data computation, transfer, and I/O processing. It is allocated to address FE00H in the internal data memory space and initialized to 00H when a reset is performed.

| Address | Initial Value | R/W | Name | BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|---------|---------------|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

| FE00    | 0000 0000     | R/W | AREG | AREG7 | AREG6 | AREG5 | AREG4 | AREG3 | AREG2 | AREG1 | AREG0 |

# 2.6 B Register (B)

The B register is combined with the ACC to form a 16-bit arithmetic register during the execution of a 16bit arithmetic instruction. During a multiplication or division instruction, the B register is used with the ACC and C register to store the results of computation. In addition, during an external memory access instruction (LDX or STX), the B register designates the high-order 8 bits of the 24-bit address.

The B register is allocated to address FE01H of the internal data memory space and initialized to 00H when a reset is performed.

| Address | Initial Value | R/W | Name | BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|---------|---------------|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

| FE01    | 0000 0000     | R/W | BREG | BREG7 | BREG6 | BREG5 | BREG4 | BREG3 | BREG2 | BREG1 | BREG0 |

# 2.7 C Register (C)

The C register is used with the ACC and B register to store the results of computation during the execution of a multiplication or division instruction. In addition, during a C register offset indirect instruction, the C register stores the offset data (-128 to +127) to the contents of an indirect register.

The C register is allocated to address FE02H of the internal data memory space and initialized to 00H when a reset is performed.

| Address | Initial Value | R/W | Name | BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|---------|---------------|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

| FE02    | 0000 0000     | R/W | CREG | CREG7 | CREG6 | CREG5 | CREG4 | CREG3 | CREG2 | CREG1 | CREG0 |

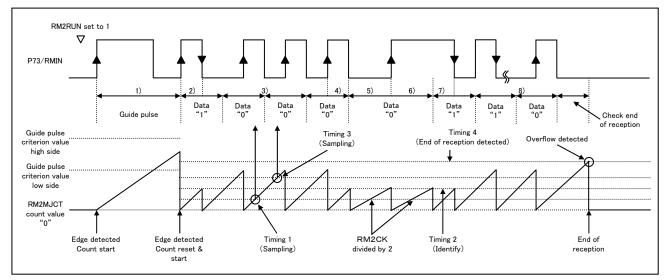

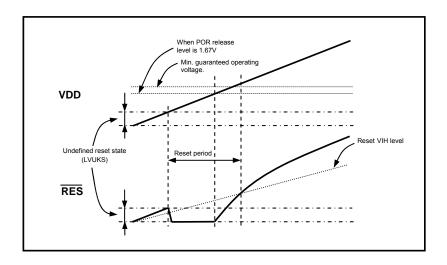

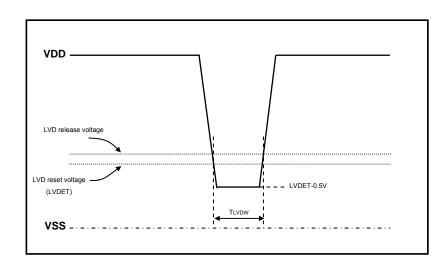

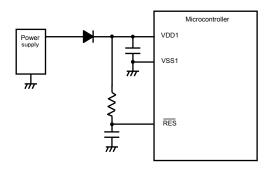

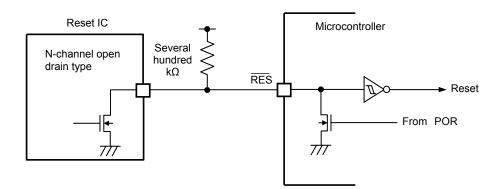

## 2.8 Program Status Word (PSW)