**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# AND8459/D

## **Basics of Clock Jitter**

Prepared by Baljit Chandhoke ON Semiconductor

### **ON Semiconductor®**

http://onsemi.com

## **APPLICATION NOTE**

#### Introduction

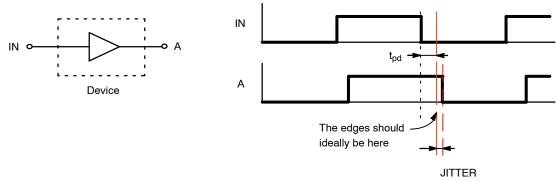

This application note focuses on the different types of clock jitter. Clock jitter is deviation of a clock edge from its ideal location. Understanding clock jitter is very important in applications as it plays a key role in the timing budget in a system.

With the increasing system data rates, timing jitter has become critical in system design, as in some instances the system performance limit is determined by the system timing margin. So a good understanding of the timing jitter becomes very important in system design. Total jitter can be separated into random jitter and deterministic jitter components. We will not discuss the components of jitter in this application note. We will focus on different types of clock jitter.

Clock timing jitter can be measured in time domain and in frequency domain. Cycle-to-cycle jitter, period jitter and time interval error (TIE) jitter are measured in time domain, where as phase noise and phase jitter are measured in frequency domain. Some of the sources of jitter are thermal noise, power supply noise, ground bounce, PLL circuitry, crosstalk and reflections.

Figure 1. Examples of Clock Jitter

#### **Different types of Clock Jitter**

• *Cycle-to-cycle Jitter* – The cycle-to-cycle jitter measures the change in clock period between any two adjacent clock cycles over 1,000 clock cycles.

- The cycle-to-cycle jitter RMS measures the standard deviation of the change in clock period measurement between any two adjacent clock cycles over 1,000 clock cycles.

- The cycle-to-cycle jitter peak-to-peak measures the difference between minimum clock period change and maximum clock period change between any two adjacent clock cycles over 1,000 clock cycles.

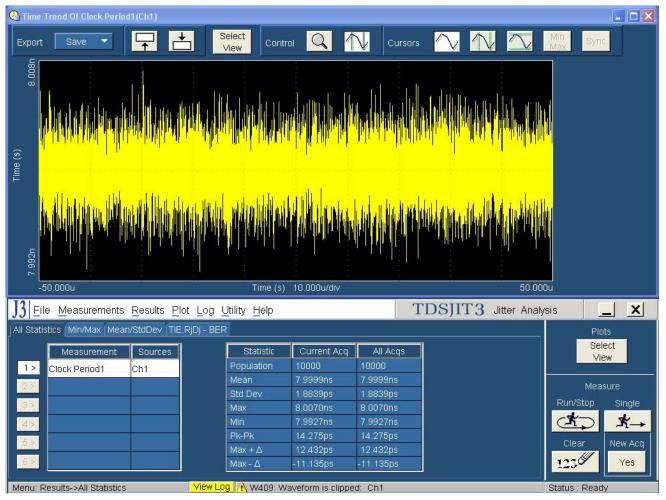

The cycle-to-cycle jitter measurement is used to determine high frequency jitter in applications as it measures the jitter between two adjacent clock cycles. It is very important to have a small value of cycle to cycle jitter as it impacts the system timing margin. • *Period Jitter* – The period jitter measures the maximum deviation of clock period of a clock cycle in the waveform over 10,000 clock cycles.

- The period jitter RMS measures the standard deviation of the clock period measurements over 10,000 clock cycles.

- The period jitter peak-to-peak measures the difference between minimum clock period and

maximum clock period measurement over 10,000 clock cycles.

The period jitter measurement is used to determine low frequency jitter in applications as it measures the jitter by measuring the clock period deviations over 10,000 clock cycles. Period jitter is used to calculate the system timing margin. Figure 2 shows Example of Clock Period Jitter Measurement of ON Semiconductor's Programmable Clock – NB3N3020.

Figure 2.

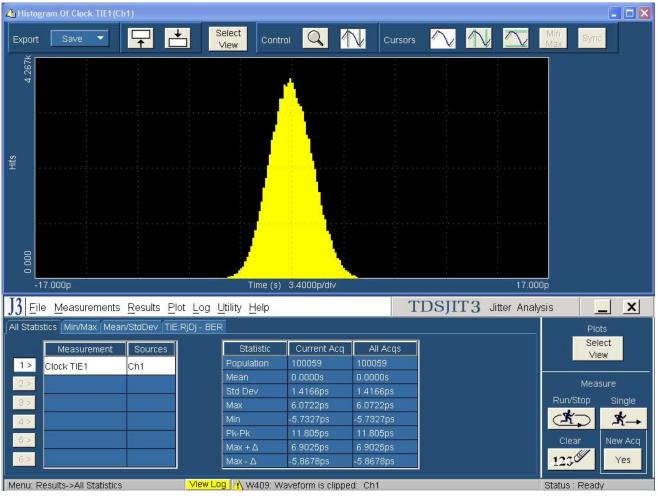

• *Time Interval Error (TIE) Jitter* – The TIE jitter measures how far each active edge of the clock varies from corresponding edge of an ideal clock.

- The TIE jitter RMS measures the standard deviation of the timing error.

- The TIE peak-to-peak measures the difference of the minimum and maximum timing error.

The TIE jitter is important in clock and data recovery (CDR) PLLs to show if the PLL in the CDR is able to track to the incoming data stream. A large TIE jitter shows that the CDR PLL is not able to properly track the variation in the incoming data stream. Figure 3 shows Example of Time Interval Error (TIE) Jitter measurement of ON Semiconductor's Clock Synthesizer – NB3N3002.

Figure 3.

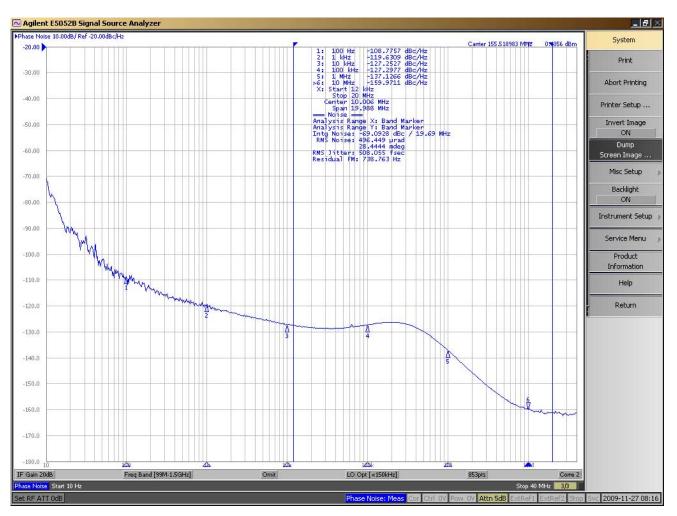

• *Phase Noise* – Phase noise is measured in the frequency domain, and is a ratio of signal power to noise power normalized to a 1 Hz bandwidth at a given offset from the carrier signal.

Phase jitter is measured by integrating the phase noise across specified frequency offsets from the carrier signal. Phase jitter measures the amount of energy present in the specified frequency offsets from the carrier signal compared to the energy of the carrier signal by integrating the area under the phase noise plot. As an example, SONET uses a frequency offset of 12 kHz to 20 MHz from the carrier signal to integrate the area under the phase noise plot to measure phase jitter. Fiber Channel uses a frequency offset of 637 kHz to 10 MHz from the carrier signal to integrate the area under the phase noise plot to measure phase jitter. Figure 4 shows example of phase noise and phase jitter measurement of one of the PureEdge<sup>TM</sup> PLL devices from the crystal oscillator product family – NBXDBB018 which generates a dual frequency LVPECL output at 155.52 MHz/ 311.04 MHz meeting the jitter requirements of SONET applications.

#### Conclusion

This application note provided an introduction of clock jitter, explained the different types of clock jitter and significance of each type of clock jitter measurement. Examples of the different types of clock jitter measurements were also shown in the content above. With increasing system data rates, sometimes the system performance limit is determined by the system timing margin, hence understanding timing clock jitter is critical for system designers.

#### AND8459/D

ON Semiconductor and images are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use usides to claim alleges that SCILLC was negligent feedesign or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative