# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# **Designing a Quasi-Resonant Adaptor Driven by the NCP1380**

Prepared by Stéphanie CONSEIL

ON Semiconductor

ON Semiconductor®

http://onsemi.com

#### **APPLICATION NOTE**

Quasi-square wave resonant converters also known as Quasi-Resonant (QR) converter are widely used in the adaptor market. They allow designing flyback Switched-Mode Power Supply (SMPS) with reduced Electro-Magnetic Interference (EMI) signature and improved efficiency. However, as the switching frequency of QR converter increases as the load decreases, the frequency must be limited.

In traditional QR converter, the frequency is limited by a frequency clamp. But, when the switching frequency of the system reaches the frequency clamp limit, valley jumping occurs: the controller hesitates between two valleys resulting in an unstable operation and noise in the transformer at medium and light output loads.

In order to overcome this problem, the NCP1380 and the NCP1379 feature a "valley lockout" circuit: the switching frequency is decreased step by step by changing valley as the load decreases. Once the controller selects a valley, it stays locked in this valley until the output power changes significantly. This technique extends the QR operation of the system towards lighter loads without degrading the efficiency.

This application note focuses on the design of an adapter driven by the NCP1380. The equations developed are further used to design a 60 W adapter. The same equations can be applied to the NCP1379.

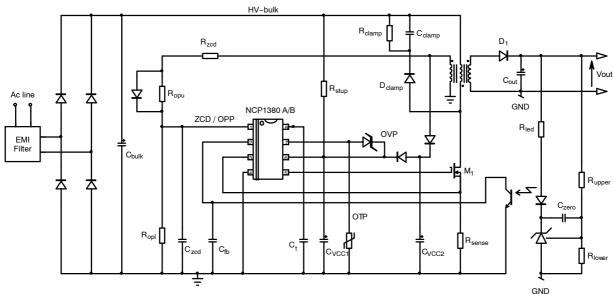

Figure 1. Application Schematic for Versions A and B

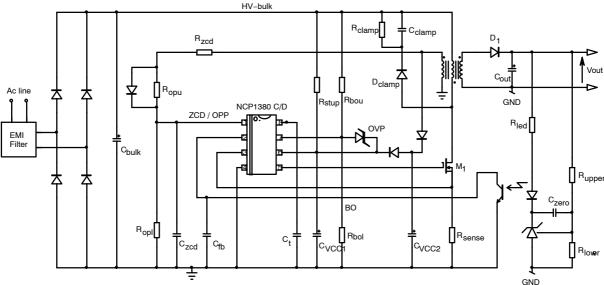

Figure 2. Application Schematic for Versions C and D

#### Introduction

The NCP1379 and NCP1380 implement a standard current-mode architecture operating in quasi-resonance. Due to a proprietary circuitry, the controller prevents valley-jumping instability and steadily locks out in selected valley as the power demand goes down. Once the fourth valley is reached, the controller continues to reduce the frequency further down, offering excellent efficiency over a wide operating range. Due to a fault timer combined to an OPP circuitry, the controller is able to efficiently limit the output power at high-line.

- Quasi-Resonance Current-mode operation: implementing quasi-resonance operation in peak current-mode control, the NCP1379 and NCP1380 optimize the efficiency by switching in the valley of the MOSFET drain-source voltage. Due to a proprietary circuitry, the controller locks-out in a selected valley and remains locked until the output loading significantly changes. When the load becomes lighter, the controller jumps into the next valley. It can go down to the 4<sup>th</sup> valley if necessary. Beyond this point, the controller reduces its switching frequency by freezing the peak current setpoint. During quasi-resonance operation, in case of very damped valleys, a 5.5 µs timer emulates the missing valleys

- Frequency reduction in light-load conditions: when the 4<sup>th</sup> valley is left, the controller reduces the switching frequency which naturally improves the standby power by a reduction of all switching losses.

- Overpower protection (OPP): When the voltage on ZCD pin swings in flyback polarity, a direct image if the input voltage is applied on ZCD pin. We can thus reduce the peak current depending of V<sub>ZCD</sub> during the on–time.

- Internal soft-start: a soft-start precludes the main power switch from being stressed upon start-up. Its duration is fixed and equal to 4 ms.

- Fault input (NCP1380 A and B versions): by combining a dual threshold on the Fault pin, the controller allows the

direct connection of an NTC to ground plus a zener diode to a monitored voltage. In case the pin is brought below the

OTP threshold by the NTC or above the OVP threshold by the zener diode, the circuit permanently latches-off and V<sub>CC</sub>

is clamped to 7.2 V.

- Fault input (NCP1380 C and D versions and NCP1379): the C and D versions of NCP1380 and the NCP1379 include a

brown-out circuit which safely stops the controller in case the input voltage is too low. Restart occurs via a complete

startup sequence (latch reset and soft-start). During normal operation, the voltage on this pin is clamped to V<sub>clamp</sub> to

give enough room for OVP detection. If the voltage on this pin increases above 2.5 V, the part latches-off.

- Short-circuit protection: short-circuit and especially over-load protections are difficult to implement when a strong leakage inductance between auxiliary and power windings affects the transformer (where the auxiliary winding level does not properly collapse in presence of an output short). Here, when the internal 0.8 V maximum peak current limit is activated, the timer starts counting up. If the fault disappears, the timer counts down. If the timer reaches completion while the error flag is still present, the controller stops the pulses. This protection is latched on A and C version (the user must unplug and re-plug the power supply to restart the controller) and auto-recovery on B and D versions (if the fault disappears, the SMPS automatically resumes operation). In addition, all versions feature a winding short-circuit protection, that senses the CS signal and stops the controller if V<sub>CS</sub> reaches 1.5 x V<sub>ILIM</sub> (after a reduced LEB of t<sub>BCS</sub>). This additional comparator is enabled only during the main LEB duration t<sub>LEB</sub>, for noise immunity reason.

### **Specifications of the Adapter**

In order to illustrate this application note, a 19 V, 60 W adapter will be the design example. The specifications are detailed in Table 1.

Table 1. SPECIFICATIONS OF THE 19 V, 60 W ADAPTER

| Parameter                                                           | Symbol                | Value    |

|---------------------------------------------------------------------|-----------------------|----------|

| Minimum input voltage                                               | V <sub>in(min)</sub>  | 85 Vrms  |

| Maximum input voltage                                               | V <sub>in(max)</sub>  | 265 Vrms |

| Output voltage                                                      | V <sub>out</sub>      | 19 V     |

| Nominal output power                                                | P <sub>out(nom)</sub> | 60 W     |

| Switching frequency at V <sub>in(min)</sub> , P <sub>out(nom)</sub> | F <sub>sw</sub>       | 45 kHz   |

| Maximum startup time                                                | T <sub>startup</sub>  | 3 s      |

The experimental results of the 60 W adapter are detailed in the application note NCP1380EVB/D [1]. For details concerning the QR transformer calculation, the power supply designer can refer to the tutorial TND348/D [2].

# **Predicting the Switching Frequency**

As the controller changes valley as the load decreases, the switching frequency of the power supply is naturally limited by the valley lockout. But equations are needed to predict the switching frequency evolution as the output power varies.

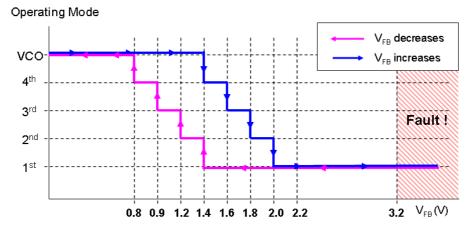

The datasheet gives the FB thresholds at which the controller changes valley, depending if the output power increases or decreases.

Figure 3. Operating Valley According to FB Voltage

With these thresholds, we can calculate the maximum switching frequency inside each valley depending if the output power decreases or increases:

$$F_{SW} = \frac{1}{\left(\frac{v_{FB}}{^{4R}_{sense}} + V_{in(rms)}\sqrt{2}\frac{t_{prop}}{L_{p}}\right)L_{p}\left(\frac{1}{v_{in(rms)}\sqrt{2}} + \frac{v_{ps}}{v_{out}+v_{f}}\right) + (1 + 2n)\pi\sqrt{L_{p}C_{lump}}}$$

(eq. 1)

#### Where:

- V<sub>FB</sub> is the FB threshold at which the controller changes valley

- R<sub>sense</sub> is the sense resistor value

- V<sub>in(rms)</sub> is the rms value of the input voltage

- t<sub>prop</sub> is the propagation delay

- L<sub>p</sub> is the primary inductance

- V<sub>out</sub> is the output voltage

- V<sub>f</sub> is the forward voltage drop of the output diode

- C<sub>lump</sub> regroups all capacitances surrounding the drain node (MOSFET capacitor, transformer parasitics...). As a first approximation, the MOSFET drain–source capacitance C<sub>OSS</sub> can be used instead of C<sub>lump</sub>.

- n is an integer representing the operating valley: n = 0 for  $1^{st}$  valley, n = 1 for  $2^{nd}$  valley, n = 2 for  $3^{rd}$  valley and n = 3 for the  $4^{th}$  valley.

The corresponding output power can be calculated using the traditional formula:

$$\mathsf{P}_{\mathsf{out}} = \frac{1}{2} \mathsf{L}_{\mathsf{p}} \left( \frac{\mathsf{V}_{\mathsf{FB}}}{4 \mathsf{R}_{\mathsf{sense}}} + \mathsf{V}_{\mathsf{in}(\mathsf{rms})} \sqrt{2} \frac{\mathsf{t}_{\mathsf{prop}}}{\mathsf{L}_{\mathsf{p}}} \right)^{2} \mathsf{F}_{\mathsf{SW}} \eta \tag{eq. 2}$$

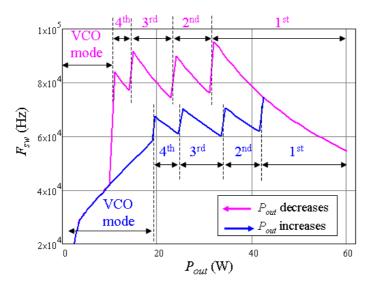

Using the previous equations, we can calculate the maxima of the switching frequency and the corresponding output power for our 60 W adapter.

In order to help the power supply designer, the previous equations have been entered inside a Mathcad spreadsheet that automatically predicts the evolution of the switching frequency as a function of the output power (Figure 4).

Figure 4. Switching Frequency versus Output Power at V<sub>in</sub> = 90 Vrms

#### **VCO Mode**

#### 1. Operating Details

At nominal power, the power supply operates in a variable frequency system where discrete frequency steps occur as the controller looks for the different valley positions.

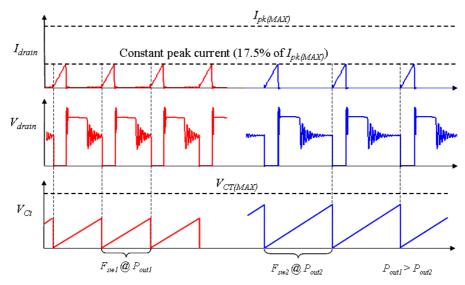

At low output power, the controller enters a Voltage–Controlled Oscillator (VCO) mode where the switching frequency is folded back. This mode is entered when  $V_{FB}$  drops below 0.8 V. The controller remains in this mode until  $V_{FB}$  increases above 1.4 V. During the VCO operation ( $V_{FB}$  < 0.8 V), the peak current is frozen to 17.5% of its maximum value and the frequency diminishes as the output power decreases.

Figure 5. I<sub>drain</sub>, V<sub>drain</sub>, V<sub>Ct</sub>, at Different Output Loads in VCO Mode

# 2. Choosing the Timing Capacitor C<sub>t</sub>

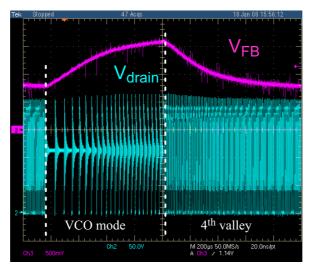

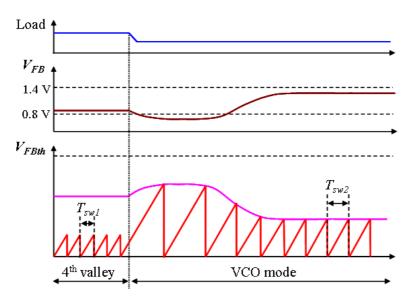

The timing capacitor must be selected with care. Indeed, when the controller leaves the valley switching mode to enter the VCO mode, the frequency changes from a valley–position–controlled value to a switching frequency imposed by the  $C_t$  capacitor. If a too big gap exists between the switching frequency in the  $4^{th}$  valley and the switching frequency imposed by the  $C_t$  capacitor, the frequency jump may create instability: hesitation between  $4^{th}$  valley and the VCO mode takes place (Figure 6) and can create output ripple and noise.

Figure 6. The Controller Hesitates Between VCO Mode and 4th Valley: Ct is Too Big!

Figure 7 shows a normal transition from  $4^{th}$  valley to the VCO mode. At the beginning, the output load is such that it imposes a  $V_{FB}$  near 0.8 V in  $4^{th}$  valley operation, with a switching period  $T_{sw1}$ . Then, if the load is slightly decreased, the FB voltage also passes below the 0.8 V threshold: the VCO mode is entered and the switching frequency decreases. (In VCO mode, the switching frequency is imposed by the FB voltage regardless of the position in the drain signal). The controller will stay in VCO mode until the FB voltage increases above 1.4 V. If we have an optimum timing capacitor value, the new steady state point is such that  $V_{FB}$  is near 1.4 V and imposes a switching period  $T_{sw2}$  larger than  $T_{sw1}$ .

Figure 7. 4th Valley to VCO Mode Transition with an Optimum Timing Capacitor Ct

To calculate  $C_t$ , we first need to estimate the switching period at the end of the  $4^{th}$  valley operation, for a FB voltage near 0.8 V by using Equation 3 or by directly measuring it on our adapter:

$$T_{SW} = \left(\frac{0.8}{4R_{sense}} + V_{in(max)}\sqrt{2}\frac{t_{prop}}{L_p}\right)L_p\left(\frac{1}{V_{in(max)}\sqrt{2}} + \frac{N_{ps}}{V_{out} + V_f}\right) + 7\pi\sqrt{L_pC_{lump}}$$

(eq. 3)

Where:

- 0.8 is the FB voltage where the controller leaves the 4<sup>th</sup> valley and enter VCO mode.

- V<sub>in(max)</sub> is the maximum input voltage

- Based on lab experiments, the switching period gap between the end of  $4^{th}$  valley operation  $(T_{sw1})$  and VCO mode  $(T_{sw2})$  for a FB voltage near 1.4 V (which is the threshold for VCO mode to  $4^{th}$  valley transition,  $V_{FB}$  increasing ) must not exceed 10  $\mu$ s. Thus, for  $V_{FB} = 1.4$  V, we will have:

$$T_{SW2} = T_{SW1} + 8 \,\mu s$$

(eq. 4)

In VCO mode, the timing capacitor voltage V<sub>Ct</sub> is dependant of the FB voltage as follows:

$$V_{Ct} = 6.5 - \frac{10}{3} V_{FB}$$

(eq. 5)

The Equation 5 allows calculating  $V_{Ct}$  for  $V_{FB} = 1.4 \text{ V}$ :

$$V_{Ct} = 6.5 - (10/3) \times 1.4 = 1.83 \text{ V}$$

(eq. 6)

Thus, we can deduce the timing capacitor value knowing  $V_{Ct}$ ,  $T_{sw2}$  and the charging current source  $I_{Ct}$  (20  $\mu$ A typ from datasheet):

$$C_{t} = \frac{I_{Ct}T_{SW2}}{1.83}$$

(eq. 7)

Application Example: 19 V, 60 W Adapter

- $V_{in(max)} = 265 \text{ Vrms}$

- $V_{out} + V_f = 19 + 0.8 \text{ V}$

- $L_p = 285 \, \mu H$

- $C_{lump} = 250 pF$

- $N_{ps} = 0.25$

- $R_{\text{sense}} = 0.23$

First, with Equation 3, we estimate  $T_{sw1}$  which is the switching period of our power supply for an output load corresponding to a  $V_{FB} = 0.8 \text{ V}$ :

$$\begin{split} T_{SW1} &= \left(\frac{0.8}{4 R_{sense}} + V_{in(max)} \sqrt{2} \frac{t_{prop}}{L_p} \right) L_p \left(\frac{1}{V_{in(max)} \sqrt{2}} + \frac{N_{ps}}{V_{out} + V_f} \right) + 7\pi \sqrt{L_p C_{lump}} \\ &= \left(\frac{0.8}{4 \times 0.23} + 265 \sqrt{2} \frac{300 \times 10^{-9}}{285 \times 10^{-6}} \right) 285 \times 10^{-6} \left(\frac{1}{265 \sqrt{2}} + \frac{0.25}{19 + 0.8} \right) + 7\pi \sqrt{285 \times 10^{-6} \times 250 \times 10^{-12}} \end{split} \tag{eq. 8}$$

When measured on the adapter we obtain:  $T_{sw1} = 11.1 \,\mu s$  ( $F_{sw1} = 90 \,kHz$ ) which corresponds to an output power of 23 W. We calculate the timing capacitor value:

$$C_t = \frac{I_{Ct}\!\!\left(T_{SW1} + 10\mu\right)}{1.83} = \frac{20x10^{-6}\!\left(10.7x10^{-6} + 10x10^{-6}\right)}{1.83} = 226 \; \text{pF} \tag{eq. 9}$$

We select  $C_t = 200 \text{ pF}$ .

# **Zero Crossing Detection**

$= 10.7 \,\mu s(93 \,\text{kHz})$

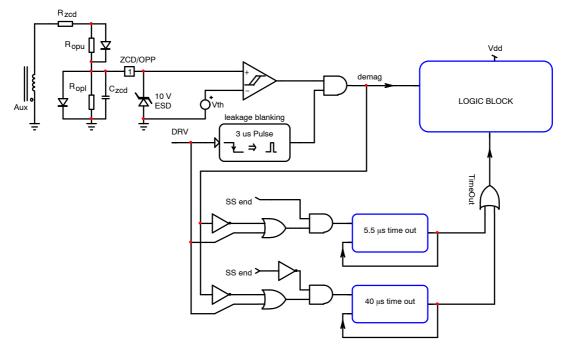

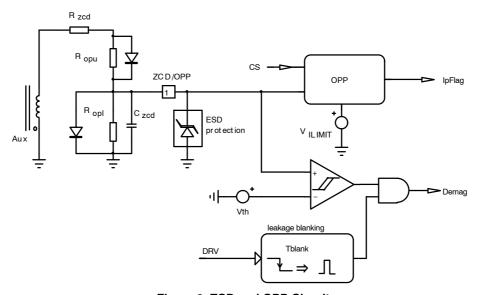

The NCP1380 combines on a single pin the inductor reset detection and the Over Power Protection (OPP). Zero crossing detection and OPP are achieved by observing the auxiliary winding voltage.

The negative part of the voltage is used for the over power protection and the positive part is used for zero crossing detection. The schematic of the zero-crossing detection bloc is shown in Figure 8.

Figure 8. Zero-Crossing Detection Bloc Schematic

# 1. Choosing the zero-crossing resistor ( $R_{zcd}$ ) value

In order to allow enough voltage on the ZCD pin during soft-start, the ratio between  $R_{zcd}$  and  $R_{opl}$  should be equal to 1 or lower than 1:

$$\frac{R_{zcd}}{R_{ool}} \le 1 \qquad \text{(eq. 10)}$$

Practically, we recommended a value of 1 k $\Omega$  for  $R_{zcd}$  and to keep the value of  $R_{opl}$  in the range of 1 k $\Omega$  to 3 k $\Omega$ .

#### 2. Time Out

In case of extremely damped free oscillations, the ZCD comparator can be unable to detect the valleys. To avoid such situation, NCP1380 integrates a Time Out function that acts as a substitute clock for the decimal counter inside the logic bloc. The controller thus continues its normal operation. To avoid having a too big step in frequency, the time–out duration is set to  $5.5 \mu s$ .

The NCP1380 also features an extended time out during the soft-start. Indeed, at startup, the output voltage reflected on the auxiliary winding is low. Because of the voltage drop introduced by the Over Power Compensation diode (Figure 9) the voltage on the ZCD pin is very low and the ZCD comparator might be unable to detect the valleys. In this condition, setting the DRV Latch with the normal 5 µs time-out leads to a continuous conduction mode operation (CCM) at the beginning of the soft-start. This CCM operation only last a few cycles until the voltage on ZCD pin becomes high enough to be detected by the ZCD comparator. To avoid this, the time-out duration is extended to 40 µs during the soft-start in order to ensure that the transformer is fully demagnetized before the MOSFET is turned-on.

#### **Over Power Protection**

#### 1. Operating Details

A flyback operated in Quasi Resonance exhibits wide peak current variations in relationship to the input voltage conditions. As a result, the converter output power range widens as the input voltage increases. To cope with safety requirements, the designer needs to limit the power output capability over the input voltage range. A possible way of doing it is call Over Power Protection (OPP).

Please note that a quasi-resonant converter output power cannot be limited to a very tight range for a universal input voltage specification (85 Vrms to 265 Vrms). Indeed, the quasi-resonance mode exhibits high current slope in the transformer, causing wide peak current variation over the input voltage range compared to a Continuous Conduction Mode (CCM) design. Thus, if a very tight range for the output power capability is needed, the power supply designer should use a CCM design.

The novel technique implemented in the NCP1380 and the NCP1379 takes benefits of the auxiliary winding voltage whose negative amplitude relates to the input rail voltage. When the power MOSFET is conducting, the auxiliary winding voltage becomes the input voltage  $V_{in}$  affected by the auxiliary to primary turn ratio  $(N_{p,aux} = N_{aux}/N_p)$ :

$$V_{aux} = -N_{p,aux}V_{in}$$

(eq. 11

By applying this voltage through a resistor divider on the ZCD pin, we have an image of the input voltage transferred to the controller via this pin. This voltage is added internally to the 0.8 V reference and affects the maximum peak current (Figure 9). As the OPP voltage is negative, an increase of input voltage implies a decrease of the maximum peak current setpoint:

$$V_{CS(max)} = 0.8 + V_{OPP}$$

(eq. 12)

Figure 9. ZCD and OPP Circuit

The maximum OPP voltage that can be applied to ZCD pin is –300 mV, which corresponds to a peak current decrease of 37.5%. In order to avoid saturating the input transistors of the OPP comparator, the positive voltage excursion on the ZCD pin must also be limited. Thus, we recommend adding a diode between ZCD and GND to limit the positive voltage to 0.6 V. This is not mandatory, but if higher positives voltages are applied to this pin, the propagation delay of the OPP comparator will increase.

#### 2. Calculating the needed OPP amount for the design

Because of the propagation delay, the maximum peak current at high line is:

$$I_{pk(high)} = \frac{0.8}{R_{sense}} + V_{in(max),dc} \frac{t_{prop}}{L_{p}}$$

(eq. 13)

The corresponding switching period and output power are:

$$T_{SW(high)} = I_{pk(high)}L_p \left(\frac{1}{V_{in(max),dc}} + \frac{N_{ps}}{V_{out} + V_f}\right) + \pi \sqrt{L_p C_{lump}}$$

(eq. 14)

$$P_{out(high)} = \frac{1}{2} L_p I_{pk(high)}^2 \frac{1}{T_{SW/(high)}} \eta$$

(eq. 15)

We would like to limit the output power to  $P_{out(limit)} > P_{out(nom)}$  at maximum input voltage. In order to perform over power compensation, we need to calculate the peak current  $I_{pk(limit)}$  corresponding to  $P_{out(limit)}$ .

$$I_{pk(limit)} = \frac{L_{p} \left(\frac{1}{V_{in(max),dc}} + \frac{N_{ps}}{V_{out}^{+}V_{f}}\right) + \sqrt{L_{p}^{2} \left(\frac{1}{V_{in(max),dc}} + \frac{N_{ps}}{V_{out}^{+}V_{f}}\right)^{2} + 2\frac{L_{p}^{\eta}}{P_{out(limit)}} \pi \sqrt{L_{p}C_{lump}}}}{\frac{L_{p}^{\eta}}{P_{out(limit)}}}$$

(eq. 16)

The amount of OPP voltage needed is thus:

$$V_{OPP} = 0.8 \left( 1 - \frac{I_{pk(limit)}}{I_{pk(max)}} \right)$$

(eq. 17)

As an example, in order to provide a 15% power margin to our 60 W adapter, we want to limit the output power to 70 W at high line.

Using Equations 13 to 15, we obtain:

$$\begin{split} I_{pk(high)} &= \frac{0.8}{4R_{sense}} + V_{in(max),dc} \frac{t_{prop}}{L_p} = \frac{0.8}{4\times0.23} + 375 \frac{600x10^{-9}}{285x10^{-6}} = 4.32 \, \text{A} \quad \text{(eq. 18)} \\ T_{SW(high)} &= I_{pk(high)} L_p \Biggl( \frac{1}{V_{in(max),dc}} + \frac{N_{ps}}{V_{out} + V_f} \Biggr) + \pi \sqrt{L_p C_{lump}} \\ &= 4.32\times285x10^{-6} \Biggl( \frac{1}{375} + \frac{0.25}{19+0.8} \Biggr) + \pi \sqrt{285x10^{-6}\times250x10^{-12}} = 19.5 \, \mu \text{s} \\ P_{out(high)} &= \frac{1}{2} L_p I_{pk(high)}^2 \frac{1}{T_{SW(high)}} \eta = \frac{1}{2} 285x10^{-6}\times4.32^2 \frac{1}{19.5x10^{-6}} 0.85 = 116 \, \text{W} \end{aligned} \tag{eq. 20}$$

If no over power compensation is applied, the adapter will be able to deliver 116 W at high line! In order to limit the output power to 70 W at 265 Vrms, the peak current must be reduced to:

$$I_{pk(limit)} = \frac{L_p \left(\frac{1}{V_{in(max),dc}} + \frac{N_{ps}}{V_{out}^{+}V_f}\right) + \sqrt{L_p \,^2 \left(\frac{1}{V_{in(max),dc}} + \frac{N_{ps}}{V_{out}^{+}V_f}\right)^2 + 2 \frac{L_p \eta}{P_{out(limit)}} \pi \sqrt{L_p C_{lump}}}{\frac{L_p \eta}{P_{out(limit)}}} = \frac{285 \times 10^{-6} \left(\frac{1}{375} + \frac{0.25}{19 + 0.8}\right) + \sqrt{\left(285 \times 10^{-6}\right)^2 \left(\frac{1}{375} + \frac{0.25}{19 + 8}\right)^2 + 2 \frac{285 \times 10^{-6} \times 0.85}{70} \pi \sqrt{285 \times 10^{-6} \times 250 \times 10^{-12}}}}{\frac{285 \times 10^{-6} \times 0.85}{70}} = 2.67 \text{ A}$$

The amount of OPP voltage that must be applied to the design is:

$$V_{OPP} = 0.8 \left( 1 - \frac{I_{pk(limit)}}{I_{pk(max)}} \right) = 0.8 \left( 1 - \frac{2.67}{4.32} \right) = 300 \text{ mV}$$

(eq. 22)

#### 3. Calculating the OPP resistors

Looking at Figure 9, if we apply the resistor divider law on the pin 1 during the on-time, we obtain the following relationship:

$$\frac{R_{zcd} + R_{opu}}{R_{opl}} = \frac{N_{p,aux}V_{in,dc} - V_{OPP}}{V_{OPP}}$$

(eq. 23)

By choosing a value for  $R_{opl}$  (for example 1 k $\Omega$ ), we can easily deduce  $R_{opu}$  as we already know  $R_{zcd}$  value. Following our example from before, we need 300 mV of OPP voltage to limit the output power to 70 W at 265 Vrms. We choose:  $R_{opl}$  = 1 k $\Omega$

$$R_{opu} = \frac{N_{p,aux}V_{in,dc} - V_{OPP}}{V_{OPP}}R_{opl} - R_{zcd} = \frac{0.18 \times 375 - (0.3)}{(0.3)}1000 - 1000 = 223 \text{ k}\Omega$$

(eq. 24)

Finally, we choose a 220 k $\Omega$  resistor for R<sub>opu</sub>.

#### 4. A Non-Dissipative OPP

The input voltage information is given by the auxiliary winding which offers lower voltage values compared to the bulk rail. In addition, in VCO mode, the switching frequency expands. Thus, the average current in the OPP bridge decreases. Let us calculate the average current circulating in the OPP bridge at light load:

$$I_{bridge(mean)} = \frac{1}{T_{SW}} \int_{0}^{T_{SW}} \left| \frac{V_{aux}(t)}{R_{zcd} + R_{opu} + R_{opl}} \right| dt$$

(eq. 25)

We obtain:

$$I_{bridge(mean)} = \frac{1}{R_{zcd} + R_{opu} + R_{opl}} \frac{t_{on}}{T_{SW}} N_{p,aux} V_{in} \sqrt{2} + \frac{1}{R_{opu} + R_{opl}} \frac{t_{off}}{T_{SW}} \left( V_{CC} + V_f \right)$$

(eq. 26)

On our 60 W adapter, for an output power of 4 W, we measured:

- $t_{on} = 1.2 \, \mu s$

- $t_{off} = 3.6 \,\mu s$

- $T_{sw} = 40 \ \mu s$

- $V_{CC} + V_f = 12 \text{ V}$

We can calculate the OPP bridge current at highest input voltage (265 Vrms):

$$\begin{split} I_{bridge(mean)} &= \frac{1}{R_{zcd} + R_{opu} + R_{opl}} \frac{t_{on}}{T_{SW}} N_{p,aux} V_{in} \sqrt{2} + \frac{1}{R_{opu} + R_{opl}} \frac{T_{off}}{T_{SW}} (V_{CC} + V_f) \\ &= \frac{1}{220k + 1k + 1k} \frac{1.2\mu}{40u} 0.18 \times 265 \sqrt{2} + \frac{1}{220k + 1k} \frac{3.6\mu}{40u} 12 = 14 \,\mu\text{A} \end{split}$$

(eq. 27)

As the bridge current is very low, the power dissipated by the OPP bridge can be neglected.

### **Startup Network for NCP1380**

The NCP1379 has a low  $V_{CC(on)}$  threshold (around 12 V), allowing to use an auxiliary power supply to bias the controller. Also, the NCP1379 will consume much current during the startup phase (1.2 mA), thus if the power designer wants to use startup resistors instead of an auxiliary power supply, the power dissipated in the startup resistors will be high.

On the contrary, the NCP1380 has an higher  $V_{CC(on)}$  threshold but consumes a very low current during the startup (10  $\mu$ A typ, 20  $\mu$ A max). Thus, high values of startup resistors can be used leading to lower power dissipation in the startup network.

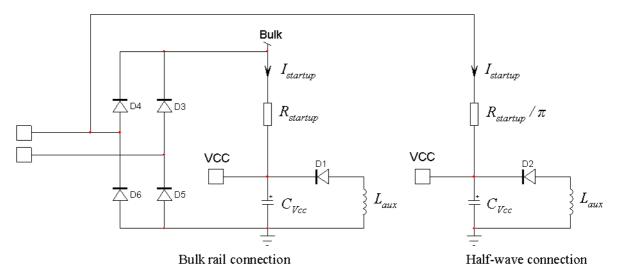

The startup resistor R<sub>startup</sub> can either be connected to the bulk rail or to half-wave (Figure 10). Connecting the startup resistor to the half-wave allows decreasing the power dissipated in the startup resistor.

Figure 10. The Startup Resistor can be Connected to the Bulk Rail or to the Half Wave

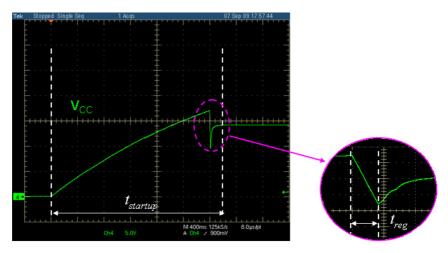

#### 1. Calculating the Startup Capacitor

The startup capacitor is calculated to allow the power supply to close the loop before  $V_{CC}$  falls below  $V_{CC(off)}$ . Thus,  $C_{Vcc}$  must be able to supply the controller alone during a limited time  $t_{reg}$  (Figure 11).

Figure 11.  $V_{CC}$  Waveform During Startup

The startup capacitor value can be calculated as follows:

$$C_{VCC} = \frac{\left(I_{CC3A} + Q_g F_{SW}\right) t_{reg}}{V_{CC(on)} - V_{CC(off)}}$$

(eq. 28)

The current needed to charge C<sub>Vcc</sub> alone during the startup is:

$$I_{CVCC} = \frac{V_{CC(on)}C_{VCC}}{t_{startup}}$$

(eq. 29)

# **Design Example:**

For our 19 V, 60 W adapter, we chose a 9 A, 600 V MOSFET (IPA60R385 from Infineon).

The total gate charge is:  $Q_g = 17 \text{ nC}$

The switching frequency at low line, maximum output load is:  $F_{sw} = 45 \text{ kHz}$

The total startup time of the adapter must be below 3 s. We will consider a startup time t<sub>startup</sub> of 2.8 s.

The value of  $t_{reg}$  can be estimated around 10 ms.

From the datasheet, we can extract the values of the following parameters:

$I_{CC3A} = 2.4 \text{ mA}$

$V_{CC(on)} = 17 \text{ V}$

$V_{CC(off)} = 9 V$

We can deduce:

$$C_{VCC} = \frac{\left(I_{CC3A} + Q_g F_{SW}\right) t_{reg}}{V_{CC(on)} - V_{CC(off)}} = \frac{(2.4m + 17n \times 45000) \times 10m}{17 - 9} = 3.9 \,\mu\text{F} \tag{eq. 30}$$

We choose a 4.7  $\mu$ F capacitor for C<sub>Vcc</sub>.

The current needed to charge  $C_{Vcc}$  is:

$$I_{CVCC} = \frac{V_{CC(on)}C_{VCC}}{t_{startup}} = \frac{17 \times 4.7 \mu}{2.8} = 28.5 \,\mu\text{A}$$

(eq. 31)

#### 2. Startup Resistor Calculation

#### \*Bulk connection

If the resistor is connected to the bulk rail, the following formula can be use to calculate its value:

$$R_{\text{startup}} = \frac{V_{\text{in(min)}}\sqrt{2}}{I_{\text{CVCC}} + I_{\text{CC(start)}}}$$

(eq. 32)

Where:

- ullet  $I_{Cvcc}$  is the current needed to charge the  $V_{CC}$  pin capacitor

- I<sub>CC(start)</sub> is the current consumed by the controller during startup

- V<sub>in(min)</sub> is the minimum input voltage

The power dissipated by the startup resistor connected to the bulk rail is:

#### \*Half-wave connection

If the resistor is connected to the half-wave:

$$R_{\text{startup1/2}} = \frac{\frac{V_{\text{in(min)}}^{\sqrt{2}}}{\pi}}{I_{\text{CVCC}} + I_{\text{CC(start)}}} = \frac{R_{\text{startup}}}{\pi}$$

(eq. 33)

The power dissipated by the startup resistor connected to the half-wave is thus:

$$P_{\text{startup1/2}} = \frac{\left(\frac{V_{\text{in}(\text{max})}\sqrt{2}}{\pi} - V_{\text{CC}}\right)^2}{R_{\text{startup1/2}}}$$

(eq. 34)

#### **Design Example:**

From the datasheet, the maximum value of  $I_{CC(start)}$  is 20  $\mu$ A. We will consider a typical value of 15  $\mu$ A for this parameter. In standby, the supply voltage of the controller decreases to 11 V. We deduce:

$$R_{\text{startup}} = \frac{V_{\text{in(min)}}\sqrt{2}}{I_{\text{CVCC}} + I_{\text{CC(start)}}} = \frac{85\sqrt{2}}{28.5\mu + 10\mu} \approx 3.2 \text{ M}\Omega$$

(eq. 35)

$$\mathsf{R}_{\mathsf{startup1/2}} = \frac{\frac{\mathsf{V}_{\mathsf{in}(\mathsf{min})}^{\sqrt{2}}}{\mathsf{I}_{\mathsf{CVCC}} + \mathsf{I}_{\mathsf{CC}(\mathsf{start})}} = \frac{\frac{85\sqrt{2}}{\pi}}{28.5\mu + 10\mu} \approx 1 \; \mathsf{M}\Omega \tag{eq. 36}$$

The power dissipated for each resistor is:

$$P_{\text{startup}} = \frac{\left(V_{\text{in(max)}}\sqrt{2} - V_{\text{CC}}\right)^2}{R_{\text{startup}}} = \frac{\left(265\sqrt{2} - 11\right)^2}{3.2 \times 10^6} = 44 \text{ mW} \qquad \text{(eq. 37)}$$

$$P_{\text{startup1/2}} = \frac{\left(\frac{V_{\text{in}(\text{max})}^{\sqrt{2}}}{\pi} - V_{\text{CC}}\right)^{2}}{R_{\text{startup1/2}}} = \frac{\left(\frac{265\sqrt{2}}{\pi} - 11\right)^{2}}{1x10^{6}} = 14 \text{ mW}$$

(eq. 38)

Connecting the startup resistor to the half-wave allows saving 30 mW!

#### **Fault Pin**

The Fault pin combines different safety features in order to provide compact design of power supply.

The safeties provided vary according to the version of the NCP1380 or NCP1379. Table 2 summarizes the possible combinations:

Table 2. NCP1379 AND NCP1380 FAULT PIN OPTIONS

|           | Over Voltage Protection | Over Temperature Protection | Brown-Out |

|-----------|-------------------------|-----------------------------|-----------|

| NCP1379   | ✓                       |                             | ✓         |

| NCP1380 A | ✓                       | ✓                           |           |

| NCP1380 B | ✓                       | ✓                           |           |

| NCP1380 C | ✓                       |                             | ✓         |

| NCP1380 D | ✓                       |                             | ✓         |

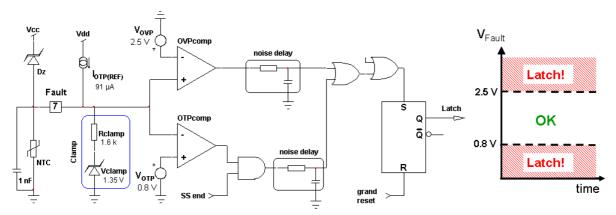

### 1. Over Temperature Protection

The adapter operating in a confined area, e.g. the plastic case protecting the converter, it is important to look after the internal ambient temperature. If this temperature would increase beyond a certain point, catastrophic failures could occur through semiconductors thermal runaway or transformer saturation. To prevent this from happening, the versions A and B of the NCP1380 embed an Over Temperature Protection (OTP) circuitry which can be combined with an Over Voltage Protection appearing in Figure 12.

Figure 12. OTP/OVP Combination in NCP1380 A and B Versions

The  $I_{OTP(REF)}$  current (91  $\mu$ A typ.) biases the Negative Temperature Coefficient sensor (NTC), naturally imposing a dc voltage on the OTP pin. When the temperature increases, the NTC's resistance reduces bringing the pin 7 voltage down until it reaches a typical value of 0.8 V: the comparator trips and latches-off the controller. During the latch-off phase, the  $V_{CC}$  is pulled down to 7.2 V by an internal clamp circuit.

The controller reset occurs when the current circulating in the  $V_{CC}$  pin drop below 30  $\mu A$  or when the  $V_{CC}$  is cycled from on to off.

During start-up and soft-start, the output of the OTP comparator is masked to allow the voltage on pin OTP to grow if a filtering capacitor is installed across the NTC.

The filtering capacitor value should be 1 nF.

In the NCP1380, the OTP trip point corresponds to a resistance of:

$$R_{NTC} = \frac{V_{OTP}}{I_{OTP(REF)}} = \frac{0.8}{91\mu} = 8.79 \text{ k}\Omega$$

(eq. 39)

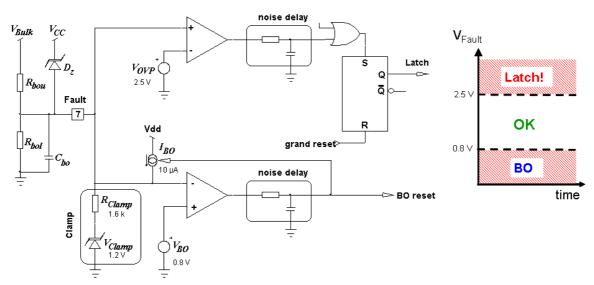

### 2. Brown-Out

The NCP1379, the C and D versions of NCP1380 feature a Brown–Out (BO) circuit which protects the power supply against low input voltage conditions (Figure 13).

The Brown–Out function is combined with an Over voltage Protection on pin 7. This pin permanently monitors a fraction of the bulk voltage through a voltage divider. When this image of bulk voltage is below the BO threshold, the controller stops switching. When the bulk voltage comes back within safe limits, the circuit goes through a new startup sequence including soft–start and re–starts switching. The hysteresis on brown–out pin is implemented with a high side current source sinking  $10~\mu A$  when the brown–out comparator is high ( $V_{bulk} > V_{bulk(on)}$ ).

Figure 13. BO / OVP Combination in NCP1379, NCP1380 C and D Versions

#### **Calculating the BO Resistors**

The following equations show how to calculate the brownout resistors.

First of all, select the bulk voltage value at which the controller must start switching  $(V_{bulk(on)})$  and the bulk voltage for shutdown  $(V_{bulk(off)})$ . Then use the following equation to calculate  $R_{bou}$  and  $R_{bol}$ .

$$R_{bol} = \frac{V_{BO}(V_{bulk(on)} - V_{bulk(off)})}{I_{BO}(V_{bulk(on)} - V_{BO})}$$

(eq. 40)

$$R_{bou} = \frac{R_{bol} (V_{bulk(on)} - V_{BO})}{V_{BO}}$$

(eq. 41)

Design example

- $V_{BO} = 0.8 \text{ V}$

- $I_{BO} = 10 \mu A$

- $V_{bulk(on)} = 110 \text{ V}$

- $V_{bulk(off)} = 50 \text{ V}$

$$R_{bol} = \frac{V_{BO}(V_{bulk(on)} - V_{bulk(off)})}{I_{BO}(V_{bulk(on)} - V_{BO})} = \frac{0.8(110 - 50)}{10x10^{-6}(110 - 0.8)} = 43.9 \text{ k}\Omega \qquad \text{(eq. 42)}$$

$$R_{bou} = \frac{R_{bol} (V_{bulk(on)} - V_{BO})}{V_{BO}} = \frac{43.9 \times 10^3 (110 - 0.8)}{0.8} = 6.0 \text{ M}\Omega$$

(eq. 43)

# 3. Over Voltage Protection

The NCP1379 and the NCP1380 features a protection against an over voltage condition, e.g in case of the optocoupler destruction.

This over voltage protection is combined either with an OTP or a BO protection, as shown previously on Figures 12 and 13. Only a zener diode needs to be added between the  $V_{CC}$  rail and the Fault pin in order to detect an over voltage condition. In case of over voltage, the zener diode starts to conduct and inject current inside the internal clamp resistor  $R_{clamp}$  thus causing the pin 7 voltage to increase. When this voltage reaches the OVP threshold (2.5 V typ), the controller is latched-off. The amount of current that must be injected inside the controller by the zener diode depends on the circuit version and can be calculated as follows:

$$I_{\text{Fault}} = \frac{V_{\text{OVP}} - V_{\text{Clamp}}}{R_{\text{Clamp}}}$$

(eq. 44)

Thus, for the NCP1379 and the NCP1380 C&D, the amount of current needed is:

$$I_{Fault} = \frac{V_{OVP} - V_{Clamp}}{R_{Clamp}} = \frac{2.5 - 1.2}{1.6x10^3} = 812.5 \,\mu\text{A}$$

(eq. 45)

For the versions A and B of the NCP1380, the amount of current to be injected in the pin Fault is:

$$I_{Fault} = \frac{V_{OVP} - V_{Clamp}}{R_{Clamp}} = \frac{2.5 - 1.35}{1.6x10^3} = 719 \,\mu\text{A} \tag{eq. 46}$$

Note: In the NCP1379, the internal latch is reset either by a BO condition or when  $V_{CC}$  falls below  $V_{CC}$  (reset).

# Conclusion

This application note has described the equations needed to design a QR adapter driven by the NCP1380. These equations can be applied to the NCP1379.

All the equations presented have been implemented inside a Mathcad spreadsheet that can be downloaded from our website: <a href="http://www.onsemi.com/">http://www.onsemi.com/</a>

#### References

- 1. Stéphanie Conseil, "Performances of a 60 W Quasi-resonant adapter driven by the NCP1380", Application Note NCP1380EVB/D.

- 2. Stéphanie Conseil, "QR Analysis and Design of Quasi-Resonant Converters", Tutorial TND348/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative