**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# Termination and Interface of ON Semiconductor ECL Devices With CML (Current Mode Logic) OUTPUT Structure

By Paul Shockman

#### Contents

SECTION 1.UNLOADED CML VOLTAGE LEVELS (DC OPEN) SECTION 2.DIRECT CONNECT (DC) CML LOAD TERMINATED 50  $\Omega$  PER LINE TO V<sub>CC</sub> SECTION 3.Cap Coupled (AC) CML LOAD TERMINATED 50  $\Omega$  PER LINE TO V<sub>term</sub> SECTION 4.CML INTERFACE INTERCONNECTS

## **ON Semiconductor®**

http://onsemi.com

## **APPLICATION NOTE**

#### Introduction

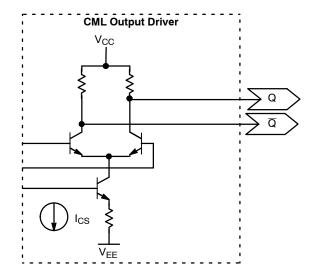

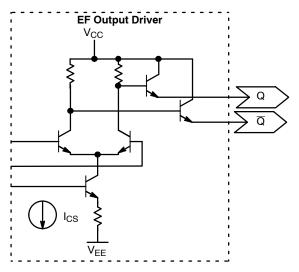

This document will discuss general termination and interface interconnection of On Semiconductor ECL devices with Current Mode Logic (CML) OUTPUT Structures. ECL has a long history of using a coupled emitter differential pair output structure with an Emitter Follower (EF) as shown in Figure 2. This classic EF output displays about 6  $\Omega$  – 8  $\Omega$  internal impedance in both LOW and HIGH output states. A constant internal current, I<sub>CS</sub>, is steered through one side or the other by the two switching transistors. Now, some devices are available using CML outputs structures with internal impedance of 50  $\Omega$  as shown in Figures 1. On Semiconductor ECL CML devices offer back source termination to 50  $\Omega$  impedance and a potential reduction in external components.

Information regarding the Termination of ECL Devices with Emitter Follower (EF) OUTPUT Structure may be found in AND8020.

Figure 1. ECL with CML, Current Mode Logic Output Structures

Figure 2. ECL with Emitter Follower Output, Output Structures

## SECTION 1. UNLOADED CML DRIVER OUTPUT VOLTAGE LEVELS (DC OPEN)

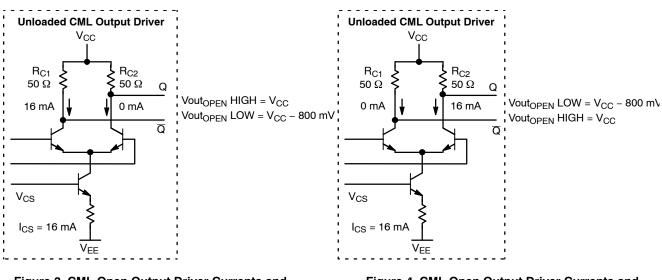

This coupled emitter differential pair output structure incorporates an internal 16 mA constant source bias,  $I_{CS}$ , as "tail current". The unloaded open output voltages,  $V_{OPEN}$ , result from the internal current,  $I_{CS}$ , steered through each 50  $\Omega$ ,  $R_C$ , collector resistor by the output transistors per Figures 3 and 4. The two output states,  $Vout_{OPEN}$  HIGH and  $Vout_{OPEN}$  LOW, are complementary. One output side of the differential pair will present an output voltage of  $V_{CC}$  – 800 mV, or  $Vout_{OPEN}$  LOW due to the 16 mA  $I_{CS}$ , drawn through its  $R_C$ .

The complementary output side, Vout<sub>OPEN</sub> HIGH has essentially no current flow,  $I_{OFF}$ , and so will drop essentially 0 V across its  $R_C$ , thus remaining near  $V_{CC}$ . Switching is accomplished by steering the constant 16 mA  $I_{CS}$  tail current from one side to the other.

$VoutOPEN HIGH = V_{CC} - (I_{OFF} \cdot R_{C}) = V_{CC} - 0$ (eq. 1)

$VoutOPEN \ LOW = V_{CC} - (I_{CS} \cdot R_C) = V_{CC} - 800$  (eq. 2)

Where:

I<sub>CS</sub> = Constant Current Source Bias

$R_{C}$  = Output Transistor Collector Resistor

Unloaded (open) CML Outputs Q and  $\overline{Q}$  will present either a Vout<sub>OPEN</sub> HIGH voltage level near V<sub>CC</sub> or a Vout<sub>OPEN</sub> LOW voltage level of V<sub>CC</sub> – 800 mV. An active complementary signal pair will produce characteristic parameters per Table 1.

# Table 1. CML DRIVER LEVELS (with Open, Unloaded Outputs)

| Parameter                        | Level U               |      |

|----------------------------------|-----------------------|------|

| Vout <sub>OPEN HIGH</sub>        | V <sub>CC</sub>       |      |

| Vout <sub>OPEN CM</sub>          | V <sub>CC</sub> – 400 |      |

| Vout <sub>OPEN LOW</sub>         | V <sub>CC</sub> – 800 | mV   |

| Vout <sub>OPEN SE</sub> (Note 1) | 800                   | mVpp |

| Vout <sub>OPEN DIFF</sub>        | 1600                  | mVpp |

1. Each line measured single-ended.

Figure 3. CML Open Output Driver Currents and Levels (Q HIGH, Q LOW)

Figure 4. CML Open Output Driver Currents and Levels (Q LOW, Q HIGH)

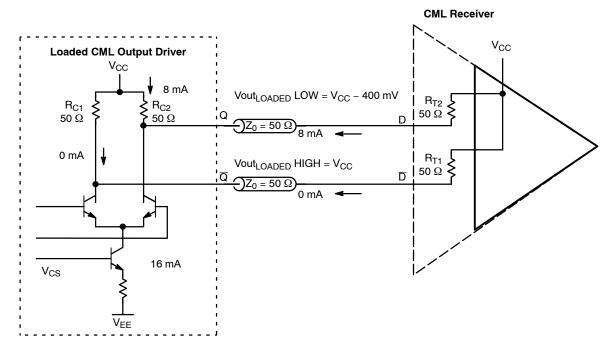

## SECTION 2. DIRECT CONNECT (DC) CML LOAD TERMINATED 50 $\Omega$ PER LINE TO V<sub>CC</sub>

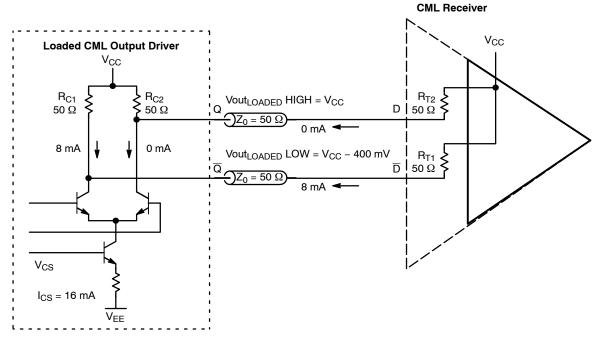

When the output is connected to a current source (loaded), the driver's internal constant 16 mA tail current,  $I_{CS}$ , now draws from the active side transistor through the internal 50  $\Omega$ ,  $R_C$  (collector resistor), and also through the receiver's 50  $\Omega$  ( $R_T$ ) termination to a current source. A typical receiver termination (internal or external termination resistor) is  $50~\Omega$  to  $V_{CC}$  as shown in Figures 5 and 6. Both output lines in a differential pair should have equal loads to maintain balanced dynamic signal loading to the driver. The complementary side draws essentially zero current,  $I_{off}$  and remains near  $V_{CC}.$

Figure 5. CML Output (with Direct Connect Load Termination of 50  $\Omega$  per line to V<sub>CC</sub>), Currents and Levels (Q HIGH,  $\overline{Q}$  LOW)

Figure 6. CML Output (with Direct Connect Load Termination of 50  $\Omega$  per line to V<sub>CC</sub>), Currents and Levels (Q LOW,  $\overline{Q}$  HIGH)

The driver 50  $\Omega$  R<sub>C</sub> is in parallel to the receiver 50  $\Omega$  (R<sub>T</sub>) to V<sub>CC</sub>, presenting a R<sub>(EQ)</sub> of 25  $\Omega$  to the active side's constant 16 mA tail current, and will drop a total of about 400 mV below V<sub>CC</sub> as the Vout<sub>LOADED</sub> LOW. The complementary output side, Vout<sub>LOADED</sub> HIGH, has essentially no current flow, I<sub>OFF</sub>, remains near V<sub>CC</sub>.

$Vout_{LOADED} HIGH = V_{CC} - (I_{OFF} \cdot R_{(EQ)}) = V_{CC} - 0$ (eq. 3)

$VoutLOADED LOW = V_{CC} - (I_{CS} \cdot R_{(EQ)}) = V_{CC} - 400$ (eq. 4)

Where:

$I_{CS}$  = Constant Source Bias  $I_{OFF}$  = Zero Current Side  $R_{C}$  = Output Transistor Collector Resistor With differential CML Output lines loaded and each terminated 50  $\Omega$  (R<sub>T</sub>) to V<sub>CC</sub> at the driver, the voltage levels present either a Vout<sub>LOADED</sub> HIGH level of V<sub>CC</sub> or Vout<sub>LOADED</sub> LOW of V<sub>CC</sub> – 800 mV at the receiver. An active complementary signal pair produces the characteristic parameters per Table 2.

| Table 2. CML DRIVER LEVELS (with Direct Connect      |

|------------------------------------------------------|

| Load Termination of 50 $\Omega$ to V <sub>CC</sub> ) |

| Parameter                          | Parameter Level       |      |

|------------------------------------|-----------------------|------|

| Vout <sub>LOADED</sub> HIGH        | V <sub>CC</sub>       |      |

| Vout <sub>LOADED</sub> CM          | V <sub>CC</sub> – 200 | mV   |

| Vout <sub>LOADED</sub> LOW         | V <sub>CC</sub> – 400 | mV   |

| Vout <sub>LOADED</sub> SE (Note 2) | 400                   | mVpp |

| Vout <sub>LOADED</sub> DIFF        | 800                   | mVpp |

2. Each line measured single-ended.

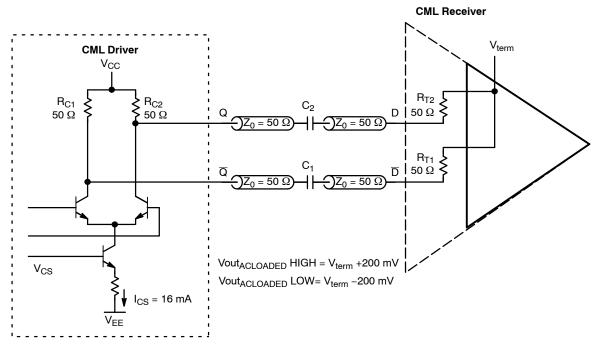

## SECTION 3. Cap Coupled (AC) CML LOAD TERMINATED 50 $\Omega$ PER LINE TO V<sub>term</sub>

A driver and receiver using a cap, Cx, coupled (AC) differential interconnect and receiver side 50  $\Omega$  termination (RT) requires a DC receiver side rebiasing, V<sub>term</sub>, to the signal lines as shown in Figure 7. The coupling cap, Cx, value and the load impedance constitute an RC network affecting the signal edges. Cap coupling (AC) restricts low frequency response and may require coding to maintain a sufficient crossing density.

This AC coupled pair in Figure 7 will produce characteristic signal levels per Table 3.

# Table 3. CML DRIVER LEVELS (with Cap Coupled Termination of 50 $\Omega$ per line to V<sub>CC</sub>)

| Parameter                             | Receiver Level          | Unit |  |

|---------------------------------------|-------------------------|------|--|

| Vout <sub>AC</sub> LOADED HIGH        | V <sub>term</sub> + 200 | mV   |  |

| Vout <sub>AC</sub> LOADED CM          | V <sub>term</sub>       | mV   |  |

| Vout <sub>AC</sub> LOADED LOW         | V <sub>term</sub> – 200 | mV   |  |

| Vout <sub>AC</sub> LOADED SE (Note 3) | 400                     | mVpp |  |

| Vout <sub>AC</sub> LOADED DIFF        | 800                     | mVpp |  |

3. Each line measured single-ended.

Figure 7. CML Output with Cap Coupling (AC) and Load Termination of 50  $\Omega$  to V<sub>term</sub>

## V<sub>term</sub> SUPPLY

The V<sub>term</sub> DC bias supply associated with the CML receiver in Figure 7 needs to accommodate the receiver common mode range and bypassed to enhance rejection of common mode noise. Typically, the V<sub>term</sub> bias supply may be connected directly from the receiver R<sub>T</sub> pins whether internal or external to the driver. When internal, the pin connect to the fixed value 50  $\Omega$  (R<sub>T</sub>) resistors may be singulated or combined. If external, the termination resistor (R<sub>T</sub>) value may be changed to accommodate the specific transmission line impedance.

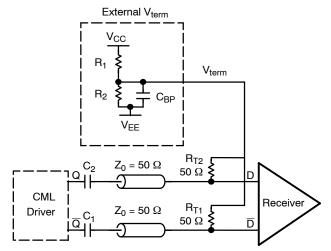

An external DC reference supply,  $V_{term}$ , may be generated by a resistor divider network spanning from the  $V_{CC}$  to  $V_{EE}$  supplies, with appropriate bypass capacitance,  $C_{BP}$ , as shown in Figure 8. Typically bypass capacitor value may range from 0.01  $\mu$ F to 0.001  $\mu$ F. Resistors R1 and R2 should generate an appropriate common mode voltage for the receiver. Current through R2 should be at least 10X the receiver typical input current for both lines.

Figure 8. Typical V<sub>term</sub> Supply Divider Network

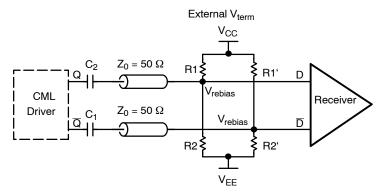

Alternatively, a receiver without internal 50  $\Omega$  (R<sub>T</sub>) resistors may be terminated and DC biased by using a Thevenin parallel equivalent network. Both impedance matching and DC rebias are simultaneously accomplished by a solution of a R1 resistor to V<sub>CC</sub> and a R2 resistor to V<sub>EE</sub> as shown in Figure 9, on each of the complementary lines. See AND8020, Section 3 Thevenin Equivalent Parallel Termination for equations generating the values of R1 and R2.

LVPECL receivers offer a wide range of accepted common mode value solutions for inputs operating in a differential interconnect. Selecting a common mode value of  $V_{CC}$  – 1.3 V would satisfy any standard ECL receiver. Table 4 gives values for the typical pullup resistor to  $V_{CC}$  (R1 or R1'), the pulldown resistor to  $V_{EE}$  (R2 or R2'), and the resulting  $V_{rebias}$  voltage when using  $V_{CC}$  – 1.3 common mode voltage and impedance matching to transmission media with  $Z_0 = 50 \Omega$ .

Figure 9. Thevenin Parallel Termination Scheme

| Resistor            | V <sub>CC</sub> – V <sub>EE</sub>  = 5.0 V | V <sub>CC</sub> – V <sub>EE</sub>   = 3.3 V | $ V_{CC} - V_{EE}  = 2.5 V$ | Unit |

|---------------------|--------------------------------------------|---------------------------------------------|-----------------------------|------|

| R1 (R1')            | 68                                         | 83                                          | 96.15                       | Ω    |

| R2 (R2')            | 192                                        | 127                                         | 104.16                      | Ω    |

| V <sub>rebias</sub> | 3.7                                        | 2.0                                         | 1.2                         | V    |

## SECTION 4. CML INTERFACE INTERCONNECTS

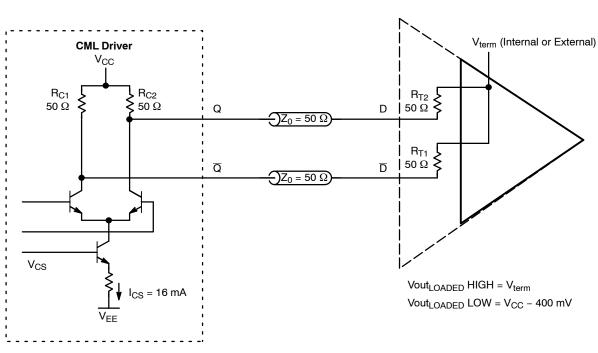

## CML Driver Direct Connect (DC) to LVPECL

The ON Semiconductor ECL Logic Devices with CML OUTPUT Structures easily interconnects directly (DC) to a

typical LVPECL receiver input on similar power supplies. A direct (DC) interface interconnect is shown in Figure 10.

LVPECL Receiver

Figure 10. CML Output with Direct (DC) Interconnect and Termination of 50  $\Omega$  to V<sub>term</sub>

A receiver may have either internal or external 50  $\Omega$  (R<sub>T</sub>) termination resistors, and these resistors may be singulated or combined for pinout. If external, the termination resistors (R<sub>T</sub>) value may be changed to accommodate the transmission line impedance.

The V<sub>term</sub> supply (Figure 8) connects to the 50  $\Omega$  (R<sub>T</sub>) termination resistors and determines the receiver DC bias level. A proper V<sub>term</sub> DC bias must be selected for the receiver to comply with common mode specifications, such as VIHCMR or VCMR. Most devices will tolerate V<sub>term</sub> at V<sub>CC</sub> while others may spec a signal HIGH level, VIHmax (consult device data sheet) requiring an appropriately lower

$V_{term}$  supply. A lower  $V_{term}$  supply affects the receiver Vout<sub>HIGH</sub> and Vout<sub>LOW</sub> levels. A typical On Semiconductor ECL Device with CML OUTPUT Structure, directly (DC) driving an internally terminated LVPECL input with various  $V_{term}$  values, produces a characteristic swing amplitude, Vout<sub>PP</sub> (each line is measured single ended), and a common mode voltage, Vout<sub>CM</sub>, presented in Table 5. Both CML driver and LVPECL receiver were supplied  $V_{CC}$  @ 3.3 V. Note the insensitivity of the output swing to changes in the  $V_{term}$  supply as it ranges from  $V_{CC}$  to  $V_{CC}$  – 2.0 V, the typical  $V_{TT}$  termination voltage for Emitter Follower ECL structures.

| V <sub>term</sub> | Vout <sub>CM</sub> | Vout <sub>HIGH</sub> | Vout <sub>LOW</sub> | Vout <sub>PP</sub> (Note 4) | Unit |

|-------------------|--------------------|----------------------|---------------------|-----------------------------|------|

| 3.3               | 3.1                | 3.25                 | 2.95                | 0.300                       | V    |

| 3.0               | 2.95               | 3.10                 | 2.85                | 0.300                       | V    |

| 2.5               | 2.75               | 2.85                 | 2.55                | 0.295                       | V    |

| 2.0               | 2.45               | 2.60                 | 2.30                | 0.280                       | V    |

Table 5. CML DRIVER LEVELS (WITH DIRECT CONNECT TERMINATION OF 50 Ω PER LINE TO V<sub>term</sub>)

4. Each line measured single-ended

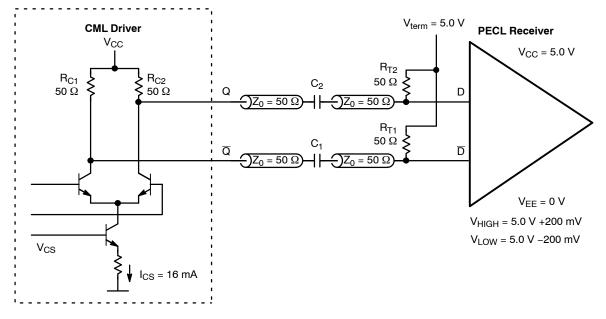

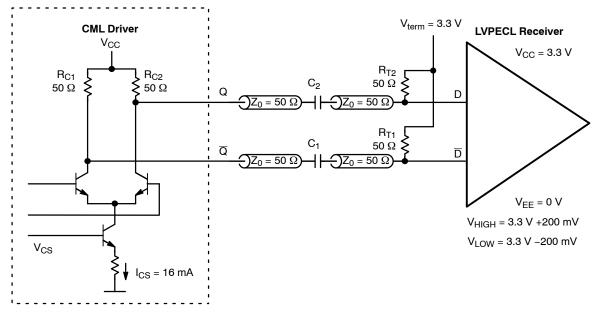

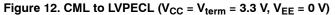

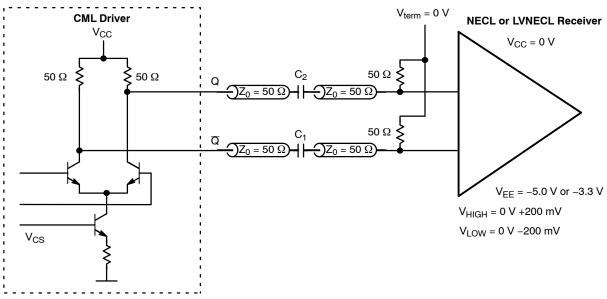

# CML Driver Cap Coupled (AC) to Various Supplied ECL: PECL, LVPECL, LVNECL, NECL

The On Semiconductor ECL Devices with CML OUTPUT Structures easily interconnect with cap coupling

(AC) to ECL type receiver inputs operating with different supply modes such as shown in Figures 11, 12, and 13.

A  $V_{term}$  supply is used to DC bias the receiver input lines. See also  $V_{term}$  Supply, Figure 8 and Table 4.

Figure 11. CML to PECL (V<sub>CC</sub> = V<sub>term</sub> = 5.0 V, V<sub>EE</sub> = 0 V)

Figure 13. CML to NECL (V<sub>term</sub> = 0 V, V<sub>EE</sub> = -5.0 V or -3.3 V)

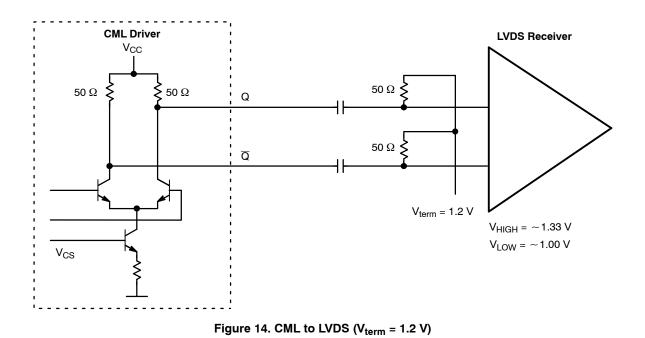

### CML Driver Cap Coupled (AC) to LVDS

A CML Driver interconnect to an LVDS (LVDS, BLVDS, M–LVDS, GLVDS, or LVDM) compliant receiver requires a cap coupled (AC) interface. Typically, a 50  $\Omega$  (R<sub>T</sub>) per line impedance matching termination to V<sub>term</sub> is used as shown in Figure 14, and will produce a V<sub>HIGH</sub> of about 1.33 V, a V<sub>LOW</sub> of 1.0 V, with an amplitude of 330 mVpp (each line measured single–ended). The V<sub>CM</sub> is set to 1.2 V by the V<sub>term</sub> reference.

If the two 50  $\Omega$  (R<sub>T</sub>) per line impedance matching termination resistors are external, the termination resistor scheme may be modified by using a Thevenin parallel scheme as shown in Figure 9. The Thevenin parallel impedance matching resistor network values and rebias voltage for an LVDS cap coupled receiver with Z<sub>0</sub> = 50  $\Omega$  are given in Table 6.

| Table 6. LVDS IMPEDANCE MATCHING RESISTOR NETWORK VALUES AND REBIAS VOLTAGE |

|-----------------------------------------------------------------------------|

|                                                                             |

| Resistor            | V <sub>CC</sub> – V <sub>EE</sub>   = 5.0 V | V <sub>CC</sub> – V <sub>EE</sub>   = 3.3 V | V <sub>CC</sub> – V <sub>EE</sub>   = 2.5 V | Unit |

|---------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|------|

| R1 (R1')            | 210                                         | 138                                         | 104                                         | Ω    |

| R2 (R2')            | 66                                          | 79                                          | 96                                          | Ω    |

| V <sub>rebias</sub> | 1.2                                         | 1.2                                         | 1.2                                         | V    |

ON Semiconductor and

are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

"Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850

For additional information, please contact your local Sales Representative