**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

## Phase Lock Loop General Operations

Prepared by: Paul Shockman ON Semiconductor Logic Applications Engineering

## THEORY OF OPERATION

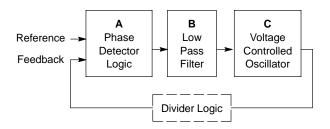

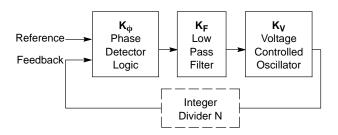

A general phase lock loop may be modeled as a reference signal and a feedback signal driving a phase detector logic network (A). Outputs from the phase detector are processed through a low pass filter network (B) to generate a control voltage. The control voltage drives a voltage controlled oscillator (C). A feedback signal derived from the voltage controlled oscillator output is fed to the phase detector as shown in Figure 1. A divider logic section is often added to the feedback signal path.

Figure 1. General Basic Phase Lock Loop Model

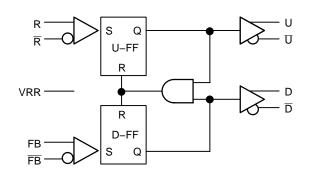

Figure 2. Logic Diagram

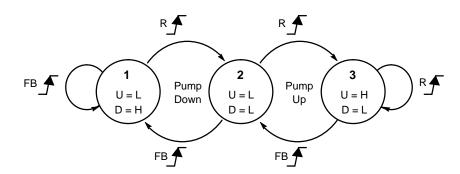

The MC100LVEL40, EP40, and EP140 phase detectors may be represented as two asynchronous edge–driven set–reset flip–flops, Up (U–FF) and Down (D–FF), driving outputs V,  $\overline{V}$ , D, and  $\overline{D}$ , as shown in Figure 2, Logic Diagram. These are ANDed to drive both flip–flops' reset lines. This configuration will be stable in one of three states, as shown in the State Model diagram, Figure 3.

Consider, initially, the outputs of both U–FF and D–DFF are low and forcing State 2. If R is leading FB, the first L–H edge transition of a pulse on R causes U–FF to go high forcing State 3. Additional pulses on R will not affect State 3. Then, an L–H edge of a pulse on FB would cause D–FF to go HIGH and reset both FFs forcing State 2. This pattern repeats depending on the phase angle calling for the V<sub>CO</sub> to PUMP UP in frequency toward LOCK with R, as shown in the operational state table, Table 1.

If FB is leading R, the first L–H edge of a pulse on FB causes D–FF to go high forcing State 1. Additional pulses on FB will not affect State 1. Then, an L–H edge of a pulse on R would cause U–FF to go HIGH and reset both FFs forcing State 2. This pattern repeats depending on the phase angle calling for the  $V_{CO}$  PUMP DOWN in frequency toward LOCK with R, also shown in Table 1.

| Table | 1. | Operational | State |

|-------|----|-------------|-------|

|-------|----|-------------|-------|

| STATE                                                                                                     | INPUT            |                  | OUTPUT           |                  |

|-----------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|

| Pump Down (states: $2 \rightarrow 1 \rightarrow 2$ )                                                      | R                | FB               | U                | D                |

| $2 \\ 2 \rightarrow 1 \\ 1 \rightarrow 2 \\ 2$                                                            | 0<br>0<br>1<br>0 | 0<br>1<br>0<br>0 | 0<br>0<br>0      | 0<br>1<br>0<br>0 |

| Pump Up<br>(states: $2 \rightarrow 3 \rightarrow 2$ )<br>2<br>$2 \rightarrow 3$<br>$3 \rightarrow 2$<br>2 | 0<br>1<br>1<br>0 | 0<br>0<br>1<br>0 | 0<br>1<br>0<br>0 | 0<br>0<br>0<br>0 |

Figure 3. State Model

#### In Lock

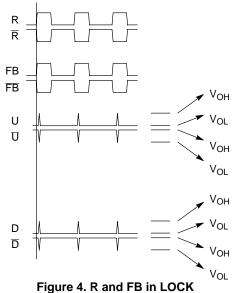

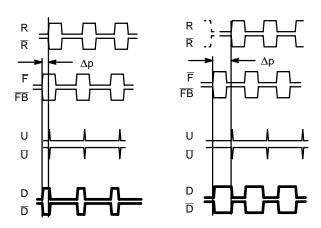

When the frequencies of R and FB are matching and the phase difference,  $\Delta p$ , is 0°, both U and D outputs will display minimum pulse widths and the detector will be considered in LOCK, or State 2, as shown in Figure 4. As the frequency increases and approaches  $f_{max}$ , the output amplitude displays a characteristic rolloff.

#### Out of Lock

When the phases of R and FB are not matching, the R input positive edge is considered the reference. The FB (feedback) input rising edge is regarded as the variable. The variable input edge may either lead or lag over a range of  $\pm 180^{\circ}$  ( $\pm \pi$  radians) with reference to the R input cycle rising edge.

If the FB (feedback positive input edge) lags R (reference positive input edge), **Condition 1** exists calling for the U output to PUMP UP the loop in frequency.

If the FB leads R, **Condition 2** exists calling for the D output to PUMP DOWN the loop in frequency.

#### **Condition 1**

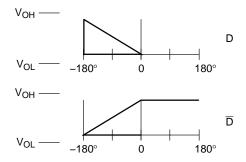

As FB ranges from 0° to  $180^{\circ}$  (0 to  $+\pi$  radians) after R, the U output proportionally changes pulse width at a linear transfer gain rate (see Figure 5).

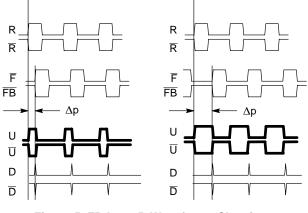

#### Figure 5. FB Lags R Waveforms Showing Phase Difference

This condition alternates between State 2 and State 3 with each period in the R cycle. When FB is a lower frequency than R, the device remains in State 3 with U remaining HIGH. Should the FB lag decrease to  $0^{\circ}$ , this would constitute LOCK. During Condition 1, D and  $\overline{D}$  outputs remain at minimum pulse width.

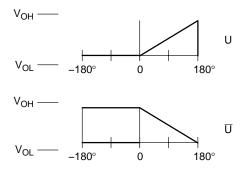

Phase detector output waveforms are usually passed through a low pass filter to produce DC voltage levels. Ideally, the resultant average DC values ( $K_{\varphi}$ ) for ECL output levels on U and  $\overline{U}$  are shown in Figure 6. The D and output remains at a minimum pulse width when R leads FB.

#### **Condition 2**

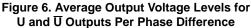

As FB ranges from 0° to  $-180^{\circ}$  (0 to  $-\pi$  radians) prior to R, the D output proportionally changes pulse width at a linear transfer gain rate (see Figure 7).

#### Figure 7. FB Leads R Waveforms Showing Phase Difference

This condition alternates between State 2 and State 1 with each period in the R cycle. When FB is a higher frequency than R, the device remains in State 1 with D remaining HIGH.

Phase detector output waveforms are passed through a low-pass filter system to produce DC voltage levels. Ideally, the resultant average DC value ( $K_{\varphi}$ ) for ECL output levels on D and  $\overline{D}$  are shown in Figure 8. The U and  $\overline{U}$  outputs remain at a minimum pulse width when FB leads R.

#### **EP40**

At lock (zero input phase difference), the U and D outputs will display a minimum pulse width of about 200 pS. Output amplitude swing is measured single ended for each output pin. The "theoretical" Phase Error gain for a single output pin (over a 180° domain) is:

$$\frac{(V_{OH} - V_{OL})}{180^{\circ}} = \frac{400 \text{ mV}}{180^{\circ}} = \frac{2.22 \text{ mV}}{^{\circ}}$$

or

$$\frac{(V_{OH} - V_{OL})}{\pi \text{ rad}} = \frac{400 \text{ mV}}{\pi} = \frac{127 \text{ mV}}{\text{rad}}$$

or

When two outputs (U and D, or  $\overline{U}$  and  $\overline{D}$ ) are combined across the integrator network, as in a typical PLL application, the voltage swing is doubled and the domain is doubled to 360° leaving the gain unchanged:

$$\frac{2^{*}(V_{OH} - V_{OL})}{360^{\circ}} = \frac{800 \text{ mV}}{360^{\circ}} = \frac{2.22 \text{ mV}}{^{\circ}}$$

# Figure 8. Average Output Levels for D and $\overline{D}$ Outputs per Phase Difference

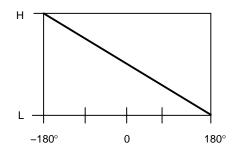

By summing and filtering the outputs  $\overline{U}$  and  $\overline{D}$ , a resultant voltage function ( $K_{\phi}$ ) is shown in Figure 9.

Figure 9. The Transfer Function or Phase Detector Gain ( $K_{\phi}$ )

#### DEVICE SPECIFIC TRANSFER GAIN (K<sub>b</sub>)

or

$$\frac{2^* (\text{VOH} - \text{VOL})}{2^* \pi \text{ rad}} = \frac{800 \text{ mV}}{2^* \pi} = \frac{127 \text{ mV}}{\text{rad}}$$

0.127 V rad

Practical, usable Phase Error Domain when two outputs (U and D, or  $\overline{U}$  and  $\overline{D}$ ) are combined, is limited due to the internal 200 pS reset pulse width and roll–off effects to:

-180° to +180° from 1 Hz to 1.5 GHz -155° to +155° at 1.6 GHz -120° to +120° at 2.0 GHz

This affects gain. A practical Phase Error gain for a single output pin at 1.6 GHz  $(155^{\circ})$  is:

$$\frac{\text{VOH} - \text{VOL})}{155^{\circ}} = \frac{400 \text{ mV}}{155^{\circ}} = \frac{2.58 \text{ mV}}{^{\circ}}$$

or

(

$$\frac{(V_{OH} - V_{OL})}{0.86 * \pi \text{ rad}} = \frac{400 \text{ mV}}{(2.7)} = \frac{148 \text{ mV}}{\text{rad}}$$

When two outputs (U and D, or  $\overline{U}$  and  $\overline{D}$ ) are combined across an integrator network, as in a typical PLL application, the voltage swing is doubled to 800 mV and the domain is doubled to 310° leaving the gain unchanged:

$$\frac{2*(V_{OH} - V_{OL})}{310^{\circ}} = \frac{800 \text{ mV}}{310^{\circ}} = \frac{2.58 \text{ mV}}{^{\circ}}$$

or

$$\frac{2^* (V_{OH} - V_{OL})}{1.72^* \pi \text{ rad}} = \frac{800 \text{ mV}}{(5.4)} = \frac{148 \text{ mV}}{\text{rad}}$$

The MC100EP40 device has a Phase Lock Detect pin (19) indicating (HIGH) when the R and FB inputs rising edges are within from 0 to 80 pS, independent of operating frequency. The PLD pin actually does not exactly detect "LOCK", but compares input rising edges only – independent of pulse width or falling edges. If R and FB show a rising edge difference >80 pS, this pin will go LOW. Near LOCK conditions may cause the PLD pin to be pulsing or flickering. As lock is approached, PLD pin duty cycle increases. This pin output may be integrated to indicate approaching some desired lock range. This single ended PLD output pin swing is about 800 mV (not RSECL – reduced swing ECL of 400 mV). It should be terminated to  $V_{CC} - 2.0$  V (at the receiver) when used, and left open or floating if not used.

#### **EP140**

At lock (zero input phase difference), the U and D outputs will display a minimum pulse width of about 200 pS. Output swing is measured single ended for each output pin so the "theoretical" Phase Error gain for a single output pin (over a 180° domain) is:

$\frac{(V_{OH} - V_{OL})}{180^{\circ}} = \frac{400 \text{ mV}}{180^{\circ}} = \frac{2.22 \text{ mV}}{^{\circ}}$

or

or

$\frac{(VOH - VOL)}{\pi \text{ rad}} = \frac{400 \text{ mV}}{\pi} = \frac{127 \text{ mV}}{\text{rad}}$

When two outputs (U and D, or  $\overline{U}$  and  $\overline{D}$ ) are combined across the integrator network, as in a typical PLL application, the voltage swing is doubled to 800 mV and the domain is doubled to 360°. This leaves the gain unchanged:

$$\frac{2^{*}(V_{OH} - V_{OL})}{360^{\circ}} = \frac{800 \text{ mV}}{360^{\circ}} = \frac{2.22 \text{ mV}}{^{\circ}}$$

or

$$\frac{2^* (V_{OH} - V_{OL})}{2^* \pi \text{ rad}} = \frac{800 \text{ mV}}{2^* \pi} = \frac{127 \text{ mV}}{\text{ rad}}$$

or

Practical, usable Phase Error Domain is limited when two outputs (U and D, or  $\overline{U}$  and  $\overline{D}$ ) are combined, due to the internal 200 pS reset pulse width and roll–off effects to:

This affects gain. A practical Phase Error gain for a single output pin at 1.6 GHz  $(155^{\circ})$  is:

$$\frac{(\text{VOH} - \text{VOL})}{155^{\circ}} = \frac{400 \text{ mV}}{155^{\circ}} = \frac{2.58 \text{ mV}}{\circ}$$

or

$$\frac{(V_{OH} - V_{OL})}{(0.86 * \pi \text{ rad})} = \frac{400 \text{ mV}}{(2.7)} = \frac{148 \text{ mV}}{\text{rad}}$$

When the two outputs (U and D, or  $\overline{U}$  and  $\overline{D}$ ) are combined across an integrator network, as in a typical PLL application, the voltage swing is doubled to 800 mV and the domain is doubled to 310° leaving the gain unchanged:

$$\frac{2*(V_{OH} - V_{OL})}{310^{\circ}} = \frac{800 \text{ mV}}{310^{\circ}} = \frac{2.58 \text{ mV}}{\circ}$$

or

$$\frac{2^{*}(V_{OH} - V_{OL})}{(1.72^{*}\pi \text{ rad})} = \frac{800 \text{ mV}}{(5.4)} = \frac{148 \text{ mV}}{\text{rad}}$$

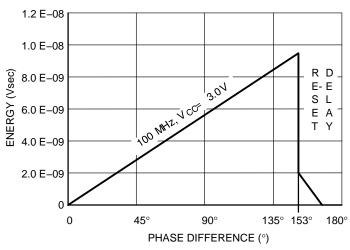

## LVEL40 Output Transfer Function Energy

In Figure 10, an LVEL40 is operating at 100 MHz with  $V_{CC} = 3.0$  V. The typical U output ECL signal pulse energy (in Vsec) is plotted across 0° to 180° of phase difference. Note the PEAK ENERGY of the output pulse is reached at about 153° or about 100 MHz operation. A

minimal ECL signal pulse energy content always occurs around 0° phase difference indicating a LOCK condition. The useable range of phase difference occurs between 0° and the peak energy phase angle. For different frequencies, refer to Table 2.

Figure 10. Typical U Output Pulse Energy vs. Phase Difference

| V <sub>CC</sub> (V) | Temperature<br>(°C) | Frequency<br>(MHz) | Peak Energy<br>(Vsec) | Maximum Usable<br>Phase Angle<br>Difference (Deg) |

|---------------------|---------------------|--------------------|-----------------------|---------------------------------------------------|

| 3.0                 | 25                  | 100                | 9.65 E-9              | 152.0                                             |

| 5.46                | 25                  | 100                | 1.02 E-8              | 152.5                                             |

| 3.0                 | 85                  | 100                | 2.66 E-8              | 149.5                                             |

| 5.46                | 85                  | 100                | 1.06 E-8              | 150.0                                             |

| 3.0                 | 25                  | 150                | 9.34 E-9              | 138.0                                             |

| 3.0                 | 85                  | 150                | 9.53 E-9              | 135.0                                             |

| 5.46                | 85                  | 150                | 9.84 E-9              | 135.0                                             |

| 3.0                 | 25                  | 200                | 4.21 E-9              | 123.5                                             |

| 5.46                | 25                  | 200                | 4.43 E-9              | 124.5                                             |

| 3.0                 | 85                  | 200                | 4.34 E-9              | 120.0                                             |

| 5.46                | 85                  | 200                | 4.45 E-9              | 119.5                                             |

| 3.0                 | 25                  | 250                | 3.25 E-9              | 109.0                                             |

| 5.46                | 25                  | 250                | 3.41 E-9              | 109.0                                             |

| 3.0                 | 85                  | 250                | 3.24                  | 104.0                                             |

| 5.46                | 85                  | 250                | 3.45                  | 104.0                                             |

### Table 2.

#### **TYPICAL APPLICATION**

Fundamental PLL characteristics such as capture range, loop bandwidth, capture time, and transient response are controlled primarily by the loop filter. The loop behavior is described by gains in each component block:

Figure 11. Fundamental Phase Lock Loop

\*The 140  $\Omega$  resistor is for 3.3 V operational power span and a pair of 800 mV<sub>pp</sub> amplitude signals. For 5.0 V operational power span and a pair of 800 mV<sub>pp</sub> amplitude signals, use a 510  $\Omega$  resistor. For 3.3 V operational power span and a pair of 400 mV<sub>pp</sub> amplitude signals, use a 250  $\Omega$  resistor.

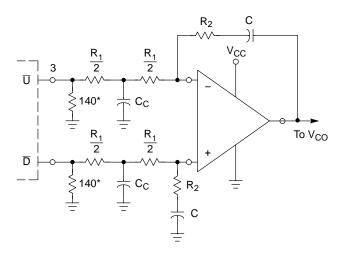

#### Figure 12. Typical Application Schematic

The loop behavior can be described by output  $(\theta_{O(S)})$  to input  $(\theta_{I(S)})$  ratio in a second order low pass filter with a static gain of:

$$\frac{\theta_{O(s)}}{\theta_{I(s)}} = \frac{K_{\varphi}K_{F}K_{V}}{s + \frac{(K_{\varphi}K_{F}K_{V})}{N}}$$

(eq. 1)

Where

$$K_{\Phi}$$

= Phase Detector Gain (Volts/Radian)

$K_F$  = Amplifier/Filter Gain

$$K_V = V_{CO}$$

Gain (Radians/Second/Volt)

N = Integer Divisor

#### LOOP FILTER

For analysis and design of the loop filter, the amplifier/filter gain may be represented as:

$$K_{F} = \frac{1 + T_{1}(s)}{T_{2}(s)}$$

(eq. 2)

T1 and T2 are the timing constants from Figure 12.

$$T_1 = R_2 * C$$

(eq. 3)

$$\Gamma_2 = R_1 * C \qquad (eq. 4)$$

Substituting the timing constants into the loop behavior equation produces:

$$\label{eq:rescaled_optimal_states} \begin{split} \frac{\theta O(s)}{\theta J(s)} &= \frac{N\left(1+T_1(s)\right)}{\left(\frac{s^2\,NT_2}{K_\varphi\,K_V}+T_1(s)+1\right)} \quad (eq.\,5) \end{split}$$

The natural loop frequency  $(\omega_n)$  and the damping factor  $(\zeta)$  are characteristics of the transient response to a step change in phase or frequency:

$$\omega_{n} = \sqrt{\frac{(K_{\Phi} K_{V})}{(NT_{2})}} \qquad (eq. 6)$$

$$\zeta = \sqrt{\frac{(K_{\Phi} K_V)}{(NT_2)}} * \frac{T_1}{2}$$

(eq. 7)

Substituting these terms into the above equation produces:

$$\frac{\theta_{O}(s)}{\theta_{I}(s)} = \frac{N\left(1 + T_{1}(s)\right)}{\left(\frac{s^{2}}{\left(\left.\omega_{n}\right.\right)^{2}} + \frac{2\zeta\left(s\right)}{\omega_{n}} + 1\right)} \quad (eq. 8)$$

Loop factors such as  $\omega_n$  and  $\zeta$  may be defined by design or imposed as application criteria. The transfer functions for phase detector gain and V<sub>CO</sub> gain, K<sub> $\varphi$ </sub> and K<sub>V</sub>, are usually device constraints, leaving T<sub>1</sub> and T<sub>2</sub> as variables to determine  $\omega_n$  and  $\zeta$ . Since only T<sub>2</sub> appears in the  $\omega_n$ definition equation, it is the easiest to solve for initially.

$$\omega_{\text{n}} = \sqrt{\frac{(K_{\phi} K_{V})}{(NT_{2})}}$$

(eq. 9)

Since:

$$\zeta = \sqrt{\frac{(\kappa_{\Phi} \kappa_{V})}{(\kappa_{T_{2}})}} * \frac{T_{1}}{2}$$

(eq. 10)

Then:

$$T_1 = \frac{2\zeta}{\omega_n}$$

(eq. 11)

$$R_{1} = \frac{K_{\varphi} K_{V}}{N^{*} \omega_{n}^{2} * C}$$

(eq. 12)

$$R_2 = \frac{2 \cdot \zeta}{\omega_n \cdot C}$$

(eq. 13)

Considerations to sidebands indicate  $R_1$  is determined first, then  $R_2$  and C.

$$C = \frac{K_{\Phi} K_{V}}{N^{*} \omega_{n}^{2^{*}} R_{1}}$$

(eq. 14)

Low amplifier/filter gain usually minimizes phase error between  $f_{in}$  and  $f_{out}$  and stabilizes the loop performance at the out–of–lock and near–out–of–lock envelope extremes.

Any loss in loop gain will in general cause a decrease in  $\zeta$  and a consequent increase in overshoot and ringing. If the loss in gain is caused by saturation or near saturation conditions, the loop will be slow and oscillatory when settling into lock.

An amplifier may exceed spec limits when subjected to large overshoot transients during times of peak energy output from the phase detector. Amplifier input frequency will exceed the R<sub>2</sub>C time constant, and the gain, K<sub>F</sub>, for these annoying pulses will then be R<sub>2</sub>/R<sub>1</sub>. Ordinarily this ratio will be less than 1, but a low loop gain and high  $\omega_n$  may cause a R<sub>2</sub>/R<sub>1</sub> ratio higher than 10 and saturation of the amplifier. Since the V<sub>CO</sub> control voltage is an average of the phase detector's output pulses, clipping equates to reduction in gain and slows settling.

#### PULSE TRANSIENT SUPPRESSION

These pulse transients may be filtered by an additional  $RC_C$  low pass network imbedded in input resistor  $R_1$  as shown in Figure 12 using:

$$C_{C} = \frac{4}{\omega_{c} * R_{1}} \qquad (eq. 15)$$

Alternatively, this additional  $RC_C$  low pass network may be implemented by placing a capacitor,  $C_C$ , across feedback  $R_2$  and using:

$$C_{C} = \frac{1}{\omega_{C} * R_{2}} \qquad (eq. 16)$$

Besides inhibiting pulse transients, these networks add an additional pole,  $\omega_c$ , to the loop performance. Such a pole must be carefully located since further overshoot may result if ( $\omega_c$ ) is too close to  $\omega_n$ . Ideally,  $\omega_c$  should be 5 to 10 times  $\omega_n$ .

$V_{CO}$  output sidebands are also reduced for synthesizers with N> 1. However, additional RC filters results in phase error at the loop crossover (approx.  $\omega_n$ ) point and may cause instability. Determination of care must be taken in placement of any low pass roll off with regard to the loop natural frequency ( $\omega_n$ ).

Sideband suppression per pole is the ratio of  $\omega_c$  to  $\omega_{REF^*}$

$$SB_{dB} = n \ 20 \log_{10} \left( \frac{\omega_{c}}{\omega_{REF}} \right)$$

(eq. 17)

where n is the number of poles in the filter.

#### V<sub>CO</sub> NOISE

Effects of  $V_{CO}$  noise,  $e_n$ , and the resultant modulation of the  $V_{CO}$  out by error voltage,  $\varepsilon$ , can be analyzed by a second order high pass function:

$$\frac{\epsilon}{e_n} = \frac{s^2}{s^2 + 2\zeta \omega_n s + \omega_n^2} \qquad (eq. 18)$$

Noise components below  $\omega_n$  (loop natural frequency) in the V<sub>CO</sub> will be suppressed by the 12 dB/octave roll-off slope with no attenuation in desired signal.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be rokided in each customer applications by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications in the BSCILLC product cauld create a situation where personal nipury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use pays that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.