# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# Design Considerations for Clamping Networks for Very High Voltage Monolithic Off-line PWM Controllers

ON

ON Semiconductor<sup>™</sup>

http://onsemi.com

APPLICATION NOTE

Prepared by: Christophe BASSO

MOTOROLA SPS BP-1029, Le Mirail 31023 Toulouse France

email: R38010@email.sps.mot.com;

Tel.: 33 5 61 19 90 12

#### INTRODUCTION

In the large family of Switch-Mode Power Supply (SMPS) components, the recently introduced high-voltage monolithic switchers start to play an important role. First of all because they provide an easy mean to instantaneously build an efficient off-line supply but also because their internal structure offers everything a designer needs: internal clock, pulse-by-pulse limitation, Leading Edge Blanking (LEB) etc. However, the internal MOSFET exhibits a low-energy capability body-diode which no longer protects the device against accidental avalanche. This element thus needs an adequate protection network against the electromagnetic leakage energy. This paper details what network is best adapted to the protection of

these devices and how to predict its efficiency in the application.

## The Leakage Inductance

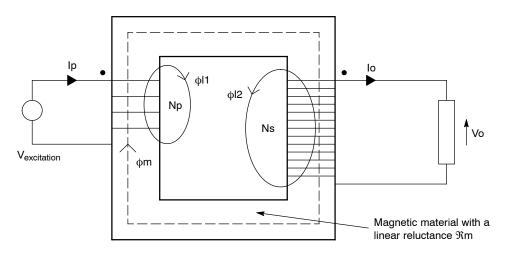

Figure 1. shows a transformer wound across a standard magnetic material. The primary side made of Np turns creates the necessary force F which gives birth to two components: φm who links both windings, but also φl1 which does not couple to the secondary and corresponds to a leakage path through the air. Thanks to φm, a current Io circulates in the secondary, but this current also gives birth to another leakage flux φl2 whose polarity is opposite of that of φm. It is important to note that φm produces Io while φl2 is a consequence of it.

Figure 1. A Two-winding Transformer Showing the Leakage Paths

As one can see from the picture,  $\phi l1$  and  $\phi l2$  close through the air. As any (magnetic) medium, the air is affected by a Reluctance  $\Re$ , or its inverse, the permeance P. These permeances create in the primary and secondary two leakage inductance with a value of:  $L_{leak} = N^2 \cdot P_{air}$ , with N

being the primary or secondary turns. As an effect, these parasitic leakage elements degrade the energy transfer between the primary and secondary (ies). In a FLYBACK converter, the presence of the leakage element will a) generate a voltage spike at turn-off and b) divert a portion

of the primary current into the clamping network. Point a) implies the use of protection network to prevent a lethal drain voltage excursion while point b) explains the root of a degraded open-loop gain: the peak current needs to be higher than theoretically calculated to deliver the full rated output power.

### The Principle of a Protection Network

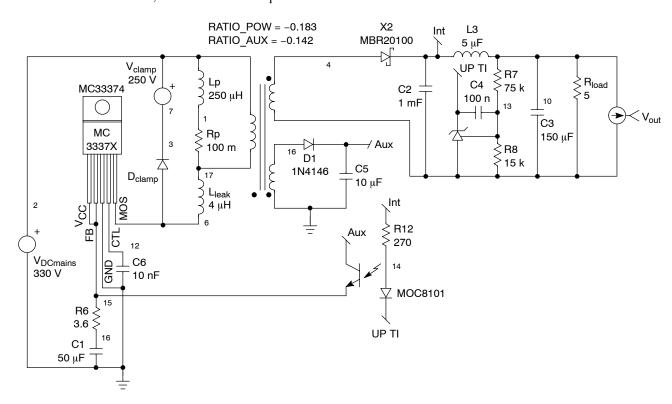

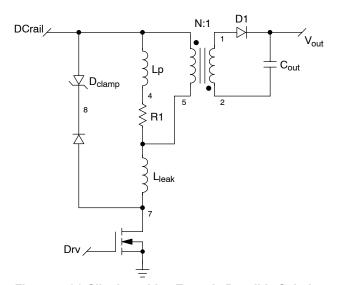

The goal of the clamping network is to prevent the drain voltage to exceed a given limit. For instance, in the new ON Semiconductor MC3337X family, the maximum voltage shall stay within 700 V. A worse case arises when the mains is at its highest level, e.g., 285 VAC in a universal mains application. To prevent the drain from reaching this value, Figure 2. (a) shows how a perfect network would work: when the MOSFET closes, the current builds-up in both

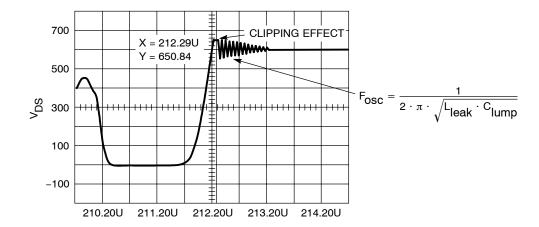

primary and leakage coils. When the ON periods stops, the MOSFET opens and interrupts its current. Since no current discontinuities can take place in an inductor, both magnetic fields collapse and the voltage across the inductances reverses in an attempt to keep the amps-turn constant: Lp energy is thus coupled to the secondary and gives birth to the output current charge. Since  $L_{leakage}$  cannot find a circulating path, it pulls-up 2 the drain voltage until  $D_{clamp}$  starts to conduct and protects the switcher at a maximum theoretical level of:  $V_{mains} + V_{clamp} = 650 \text{ V}$ . Figure 2. (b) shows the results of an INTUSOFT's IsSpice4 (San Pedro, CA) simulations. When all the leakage energy is released, a short parasitic oscillation takes place involving  $L_{leakage}$  and all the parasitic capacitive elements present in the circuit (transformer's primary capacitance, MOSFET's  $C_{oss}$  etc.)

Figure 2. (a) A Simple FLYBACK Configuration Implementing a Clamping Network

Figure 2. (b) The Drain is Safely Clipped Below 700 V at High Mains

#### **Diverting the Primary Current**

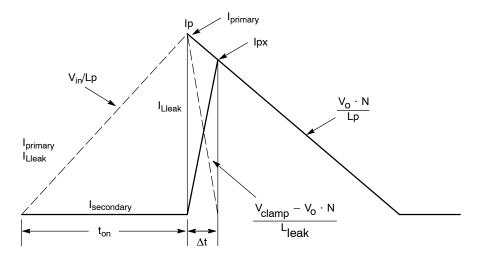

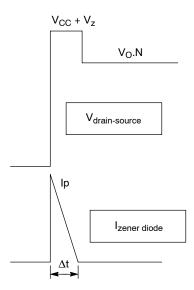

Figure 2. (a) is interesting because it helps understanding how the reflected secondary voltage resets the leakage energy and how much of primary current this leakage inductance "steals away" by diverting it into the clamp. Everything is detailed on Figure 2. (c) graph. When the MOSFET turns-off, a reset voltage is applied to the leakage inductance. This reset voltage depends on the clipping voltage but also on the FLYBACK's. The higher this level, the faster the leakage energy drops to zero and authorizes the secondary current to take place. The time  $\Delta t$  needed to complete the energy transfer is easily defined by:

$$\Delta t = \frac{L_{leak} \cdot Ip}{V_{clamp} - (V_{out} + Vf_{sec}) \cdot N},$$

where Ip is the final primary current, N the transformer ratio secondary to primary,  $Vf_{sec}$  the secondary diode forward drop and  $L_{leak}$  the primary leakage inductance.

Estimating the percentage of diverted current tells you the real peak current you will actually put in the primary to deliver the rated power. Figure 2. (c)'s Ipx point shows

where the secondary diode catches-up with the primary current. The slope of the decreasing primary current is simply

$$\frac{N \cdot (V_{out} + Vf_{sec})}{Lp},$$

but this equation can also be written as:

$$\frac{\text{lp} - \text{lpx}}{\Delta t} = \frac{\text{N} \cdot (\text{V}_{\text{out}} + \text{Vf}_{\text{sec}})}{\text{Lp}}.$$

Replacing  $\Delta t$  and solving for Ipx gives:

$$\frac{Ipx}{Ip} = 1 - \frac{L_{leak}}{Lp \cdot \left(\frac{V_{clamp}}{(V_{out}^{+}Vf) \cdot N} - 1\right)}$$

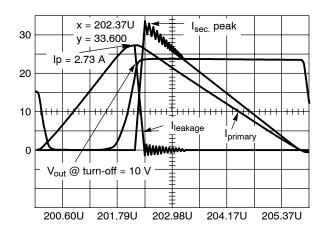

This last equation gives you the effective percentage of primary current stolen by the leakage inductance. Applying Figure 2. numerical values gives: Ipx = 98.4% of Ip. Since Ip grows up to 2.73 A, then the theoretical peak secondary current establishes at:  $0.984 \cdot 2.73 \cdot 12.5 = 33.58$  A. Figure 2. (d) validates the calculation.

Figure 2. (c) Waveforms at Turn-off: the Leakage Coil Prevents an Immediate Transfer

Figure 2. (d) IsSpice4 Simulation of Figure 2's Circuit

#### **Protecting the MOSFET with an Active Element**

The easiest way to clamp at a known level is to replace the null-impedance  $V_{\text{clamp}}$  source by a zener diode or a transient suppressor. Figures 4. (a) and 4. (b) detail the connections and their associated waveforms. Since we have two diodes in series, we have to care about both dissipated powers. Diodes can be modeled by a voltage source V (which equals  $V_{\text{zener}}$  or  $V_{\text{forward}}$ ) in series with a dynamic resistance Rd. The total average *conducted* power dissipated is therefore:

$$P_{avg} = V \cdot I_{avg} + R_d \cdot I^2 rms.$$

For the zener diode, the first part is easily deducted from Figure 3. (b):

$$P_{avg}1 = \frac{V_Z \cdot Ip}{2} \cdot \frac{\Delta t}{T}$$

or, once solving with  $\Delta t$ :

$$P_{avg}1 = \frac{V_Z \cdot Ip^2 \cdot L_{leak} \cdot F}{2 \cdot (V_Z - (V_{out} + Vf_{sec}) \cdot N)}$$

with F the switching frequency and  $V_{\text{Z}}$  the nominal zener level.

Figure 3. (a) Clipping with a Zener is Possible Solution

Figure 3. (b) Clipping Waveforms with a Zener Diode

To account for the Rd term, MOTOROLA specifies a clamping factor  $F_C$  which gives the real peak zener voltage at a given peak current:  $V_{Z(Peak)} = V_{Z(Nom)} \cdot F_C$ . From this formula, we can write:  $V_{z(Nom)} + Rd \cdot I_{z(peak)} = Fc \cdot V_{z(Nom)}$ . Solving for Rd gives:

$$Rd = \frac{(Fc - 1) \cdot V_{z(Nom)}^{2}}{P_{PK(Nom)}},$$

with  $P_{PK(Nom)}$  being the maximum peak power accepted by the zener diode or the transient suppressor. From Figure 3(b), let's now calculate the RMS and average values of the zener current:

$$I_{zener}(t) = Ip \cdot \frac{\Delta t - t}{\Delta t}$$

to obtain the RMS value simply solve:

$$\sqrt{\frac{1}{T}} \int_{0}^{\Delta t} I^{2} zener(t).dt \text{ or } I_{zener}RMS = Ip \cdot \sqrt{\frac{\Delta t}{3 \cdot T}}, T$$

is the switching period. Pavg2 is thus:

$$P_{avg}2 = \frac{Rd \cdot Ip^2 \cdot F \cdot \Delta t}{3}.$$

The I<sub>zener</sub>AVG value, which affects the conduction losses of the diode in series with the zener is evaluated by:

$$I_{zener}AVG = \frac{Ip \cdot \Delta t \cdot F}{2}.$$

As we previously wrote, the diode conduction losses are expressed the same way as the zener's, except that

$$Rd = \frac{dVf}{dId}$$

extracted from the Vf versus Id curve in the diode data-sheet at Id = Ip. To summarize we have:

$$\begin{aligned} & P_{cond\_zener} = \frac{|p^2 \cdot L_{leak} \cdot F \cdot (V_Z + 0.66 \cdot Rd \cdot Ip)}{2 \cdot (V_Z - N \cdot (V_{out} + Vf_{sec}))} \\ & P_{cond\_diode} = \frac{|p^2 \cdot L_{leak} \cdot F \cdot (V_f + 0.66 \cdot Rd_{lp} \cdot Ip)}{2 \cdot (V_Z - N \cdot (V_{out} + Vf_{sec}))} \end{aligned}$$

The final clipping level will be affected by two components: the zener clamping factor  $F_C$  but also the time the series diode takes to react. If we select a fast MOTOROLA MUR160, the data-sheet specifies a turn-on time of 50 ns. In presence of drain voltage rising with a 1.5 kV/ $\mu$ s slope, the diode will start to conduct at  $V_{mainsDC}$  +  $Vz \cdot F_C$ . If we take the highest mains level of 275VAC and

a 180 V zener diode, then the series diode starts to clip at 605 V. However, because the injection time into the low-doped N-region takes about 50 ns, the dynamic resistance of the MUR160 gradually drops to its nominal value, accordingly generating an overshoot upon the drain. Measurements have to be carried upon the final board to confirm the safety of the final drain level.

Figure 4. (a) An RC Network Clamps the Drain Voltage at Turn-off

Figure 4. (b) Turn-off Waveforms with a MOSFET Clipping the Peak

### When to Use a Zener or a Transient Suppressor?

There are little technology differences behind a standard zener diode and a transient. However, the die area is far bigger for a transient suppressor than that of zener. A 5 W zener diode like the 1N5388B will accept 180 W peak power if it lasts less than 8.3 ms. If the peak current in the worse case (e.g., when the PWM circuit maximum current limit works) multiplied by the nominal zener voltage exceeds these 180 W, then the diode will be destroyed when the supply experiences overloads. A transient suppressor like the P6KE200 still dissipates 5 W of continuous power but is able to accept surges up to 600 W @ 1 ms. If the peak power is really high, then turn to a 1.5KE200 which accepts up to 1.5 kW @ 1 ms.

#### A Passive RC Network to Clamp the Drain

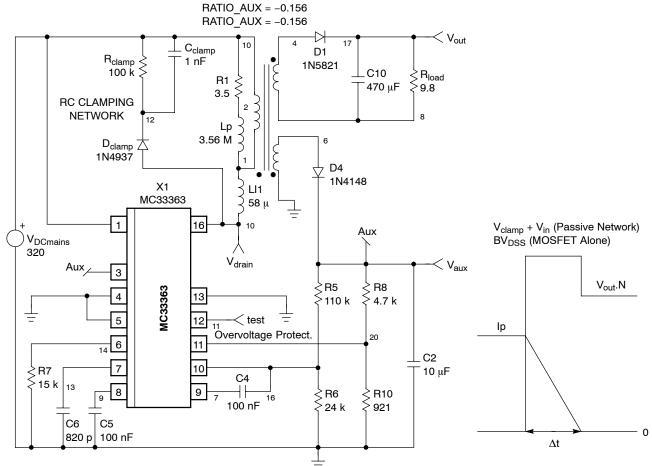

If the above solution provides a stable clamping level rather independent from peak current variations, the cost of those zener elements can degrade the overall price of your SMPS. The alternative lies in implementing a passive RC network as the one depicted in Figure 4.

If we assume we do not have any external clipping network, we can calculate the amount of energy  $E_T$  dissipated in the transistor every time it opens, assuming it would safely avalanche the voltage (Figure 4. (b)). As we said, the leakage tries to keep the current circulating at its level (Ip, when the transistor opens) during  $\Delta t$  and pushes the drain voltage up to  $BV_{DSS}$ . Ip(t) can be expressed by:

$$lp(t) = lp \cdot \frac{\Delta t - t}{\Delta t}.$$

You calculate the energy by integrating over time the cross-over area between current and voltage:

$$\mathsf{E}_\mathsf{T} = \int\limits_0^{\Delta t} \mathsf{Id}(\mathsf{t}) \cdot \mathsf{V}_{\mathsf{DS}(\mathsf{t})} \cdot \mathsf{d}\mathsf{t} = \frac{1}{2} \cdot \mathsf{Ip} \cdot \mathsf{BV}_{\mathsf{DSS}} \cdot \Delta \mathsf{t}$$

If we now introduce the term  $\Delta t$  previously calculated, we get:

$$\label{eq:PT} \begin{aligned} \textbf{P}_{T} &= \frac{1}{2} \cdot \textbf{Ip}^{2} \cdot \textbf{L}_{leak} \cdot \textbf{F} \cdot \frac{\textbf{BV}_{DSS}}{\textbf{BV}_{DSS} - (\textbf{V}_{out} + \textbf{Vf}_{sec}) \cdot \textbf{N}} \end{aligned}$$

This result depicts the average power the transistor would be the seat of, if no mean were implemented to re-route the energy spike elsewhere.

By wiring an RC network from drain to  $V_{DCmains}$  via a fast diode, we will prevent the drain voltage to rise above  $V_{DCmains} + V_{clamp}$ , the clipping voltage we want to impose (Figure 4. (b)). Let us first consider that the voltage across the RC network is constant (ripple is low compared to average voltage) and equals  $V_{clamp}$ . The average power dissipated at turn-off in the clamp is:

$$P_{clamp} = \frac{1}{2} \cdot V_{clamp} \cdot Ip \cdot \Delta t \cdot F$$

$\Delta t$  has already been defined, but this time,  $BV_{DSS}$  is replaced by  $V_{clamp}$ . Once introduced in the previous equation, we obtain the power dissipated in the clipping network:

$$\mathsf{P}_{\mathsf{clamp}} = \frac{1}{2} \cdot \mathsf{Ip^2} \cdot \mathsf{L}_{\mathsf{leak}} \cdot \mathsf{F} \cdot \frac{\mathsf{V}_{\mathsf{clamp}}}{\mathsf{V}_{\mathsf{clamp}} - (\mathsf{V}_{\mathsf{out}} + \mathsf{Vf}_{\mathsf{sec}})\mathsf{N}}$$

Since this power will mainly be dissipated by the resistor  $R_{clamp}$  at steady-state, we can write the following equality:

$$\frac{\frac{V_{clamp}^{2}}{R_{clamp}} = \frac{1}{2} \cdot Ip^{2} \cdot L_{leak} \cdot F \frac{V_{clamp}}{V_{clamp} - (V_{out} + Vf_{sec})N}$$

By solving for R<sub>clamp</sub> we calculate its value for a given level of clamping voltage:

$$\mathsf{R}_{\mathsf{clamp}} = \frac{2 \cdot \mathsf{V}_{\mathsf{clamp}} \cdot (\mathsf{V}_{\mathsf{clamp}} - (\mathsf{V}_{\mathsf{out}} + \mathsf{Vf}_{\mathsf{Sec}}) \cdot \mathsf{N})}{\mathsf{L}_{\mathsf{leak}} \cdot \mathsf{lp}^2 \cdot \mathsf{F}}$$

It is important to minimize the ripple level Vripple superimposed on  $V_{clamp}.$  A capacitor  $C_{clamp}$  will fulfill this function. If we agree that the amount of charge Q will equally split between  $R_{clamp}$  and  $C_{clamp}$  at turn-off we can write:  $V_{ripple}$ .  $C_{clamp} = I_{Rclamp}$ . T. Knowing that  $I_{Rclamp} = V_{clamp} / R_{clamp}$  and then solving for  $C_{clamp}$  it comes:

$$C_{clamp} = \frac{V_{clamp}}{V_{ripple} \cdot F \cdot R_{clamp}}$$

In steady-state operation, by neglecting the RMS current circulating in  $R_{clamp}$ , the RMS current which flows in the capacitor is the same as in the fast series diode:

$$I_{RMS}C_{clamp} = Ip \cdot \sqrt{\frac{\Delta t}{3 \cdot T}}$$

It is also sometimes interesting to know the clamp voltage set by known RC elements. In that case, simply apply:

$$\begin{aligned} V_{clamp} &= \frac{1}{2} \cdot V_{out} \cdot N + \frac{1}{2} \cdot \\ & \sqrt{V_{out}^2 \cdot N^2 + 2 \cdot R_{clamp} \cdot L_{leak} \cdot Ip^2 \cdot F} \end{aligned}$$

## **Watch-out for the Current Dependency!**

If RC networks are more attractive than zeners when talking about price, they suffer from a poor behavior when the peak current varies. As a matter of fact, the clamping level will always be calculated at the highest primary current. The highest primary current depends, of course, on the internal current limit (at the highest T<sub>J</sub>) but also from the turn-off response time due to the over-current comparator propagation delay. For the MC3337X family, this value is typically 280 ns, while the maximum current limit increases by roughly 3.5% at the maximum operating temperature. As an example, let us take a primary inductance of 290 µH. With this value in mind, a high mains of 285 VAC imposes a slope of 1.38 A/µs when the MOSFET closes. The maximum current limit of the MC33374 is set at 3.7 + 3.5% = 3.83 A. With the previous slope and a total delay of 280 ns, the switch will close when the current finally reaches:  $3.83 \text{ A} + 0.28 \,\mu\text{s} \cdot 1.38 = 4.21 \,\text{A}$ .

To have an idea of the peak current dependency of the RC network's clamp level, we built a 13 W power supply supposed to operate on wide mains. Despite a 400 mA nominal peak current, we used an MC33373 to operate without an heatsink. MC33373 authorizes peak currents up to 3 A. The RC network was specified to clamp at 240 V @ Ip nominal and gave values of 11 k $\Omega$  and 100 nF. With a 118  $\mu$ H leakage inductance and a 13.8 turn ratio, the normal operating clamping voltage was measured at 238 V.

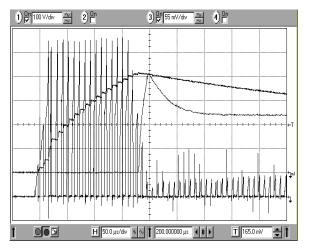

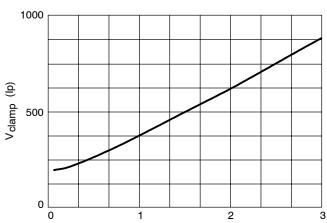

However, as one can see from Figure 5., the clamping level grows-up by adding successive voltage steps, corresponding to every switch turn-off. At power-on, V<sub>clamp</sub> and V<sub>out</sub> are both at zero. The internal error amplifier pushes the duty-cycle toward 70% but each cycle is fortunately truncated when Idrain exceeds the internal limitation. V<sub>clamp</sub> starts to grow and keeps rising until V<sub>out</sub> nominal is reached and forces the PWM modulator to brake: V<sub>clamp</sub> then diminishes to establish at the calculated 240 V. If for some reasons maximum I<sub>peak</sub> conditions would stay longer than expected (e.g., Vout could not reach it nominal value), V<sub>clamp</sub> would continue its grow, no longer protecting the internal MOSFET. To avoid this condition, Figure 5. (b)'s plot depicting  $V_{clamp} = f(Ip)$  will help the designer to track worse case conditions and react by either lowering R<sub>clamp</sub> or simply selecting a member of the MC3337X family exhibiting a maximum peak current of 400-500 mA (e.g., MC33369). Another solution is to use an adequate zener diode whose clamping level will be less sensitive to peak current variations.

Figure 5. (a) Turn-on Sequence Showing V<sub>clamp</sub> Running Away to Large Values

Figure 5. (b) This Plot Shows How  $\ensuremath{V_{clamp}}$  Moves with  $\ensuremath{I_{\Gamma}}$

## **Selecting the Right Active Components**

The series diode should be fast enough to clamp as soon as the drain voltage exceeds  $V_{clamp} + V_{DCrail}.$  As you can understand, the switching time should be selected accordingly with the drain voltage rising slope,  $dV_{DS} \, / \, dt.$

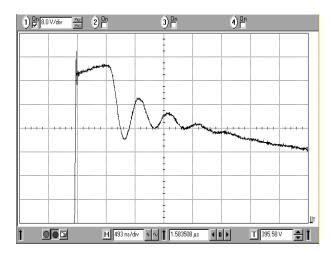

To illustrate this point, Figure 6. shows a little spike superimposed upon the drain voltage at turn-off due to this diode turn-on time. This shot is directly taken from Figure 4. circuit. Once again, this spike should never exceeds BV<sub>DSS</sub>.

Figure 6. The Diode Turn-on Time Allows V<sub>DS</sub> to Continue its Rise Before it Actually Clamps

The zener clamping level must be selected to be between 40 to 80 volts above the reflected output voltage when the supply is heavily loaded. The given formulae will help you

determining the average losses of the zener but also its maximum peak power (e.g., during power-on).

The following ON Semiconductor references can be used as active clipping elements:

| Reference | Nominal Voltage (V) | Average Power (W) | Maximum Peak Power |

|-----------|---------------------|-------------------|--------------------|

| 1N5953B   | 150                 | 1.5               | 98 W @ 1 ms        |

| 1N5955B   | 180                 | 1.5               | 98 W @ 1 ms        |

| 1N5383B   | 150                 | 5                 | 180 W @ 8.3 ms     |

| 1N5386B   | 180                 | 5                 | 180 W @ 8.3 ms     |

| 1N5388B   | 200                 | 5                 | 180 W @ 8.3 ms     |

| P6KE150A  | 150                 | 5                 | 600 W @ 1 ms       |

| P6KE180A  | 180                 | 5                 | 600 W @ 1 ms       |

| P6KE200A  | 200                 | 5                 | 600 W @ 1 ms       |

| 1.5KE150A | 150                 | 5                 | 1.5 kW @ 1 ms      |

| 1.5KE180A | 180                 | 5                 | 1.5 kW @ 1 ms      |

| 1.5KE200A | 200                 | 5                 | 1.5 kW @ 1 ms      |

X = Full Scale Span

Another benefit of using a zener diode is to limit the inverse voltage applied upon the fast series diode during turn-on at  $V_{RRM} = V_{DCmains}$ . In the presence of an RC

clamping network, the clamping level unfortunately adds to the input voltage and forces the adoption of a diode with better  $V_{RRM}$  parameter:  $V_{RRM} = V_{DCmains} + V_{clamp}$ .

Depending on the dV<sub>DS</sub>/dt slope and maximum reverse voltage conditions, the following MOTOROLA references can be used:

| Reference  | V <sub>RRM</sub> | T <sub>on</sub> (typical) | I <sub>F</sub> max |

|------------|------------------|---------------------------|--------------------|

| MUR160     | 600 V            | 50 ns                     | 3 A                |

| MUR100E    | 1000 V           | 25 ns                     | 3 A                |

| 1N4937     | 600 V            | 200 ns                    | 1 A                |

| MSR860*    | 600 V            | 100 ns                    | 8 A                |

| MSRB860-1* | 600 V            | 100 ns                    | 8 A                |

<sup>\*</sup> soft recovery diodes

### **Parameter Evolutions with Temperature**

Once protected, the equipment must survive in its operating environment. That is to say, despite the component's key specs (e.g., T<sub>fr</sub> for the series diode)

MC3337X's MOSFET BVDSS: positive temperature coefficient

MC3337X's maximum current limit: +1.03% at  $T_J = 125^{\circ}$ C MC3337X's oscillator frequency: 115 kHz at max  $T_J$  Zener breakdown voltage: positive temperature coefficient Diode reverse recovery time: positive temperature coefficient

Data-sheets can be downloaded at: http://mot-sps.com/books/current.html

Spice models of diodes and MC3337X: http://mot-sps.com/models/html/models.html

variations with the ambient temperature, they must not jeopardize the SMPS operation. The below lines give an idea on the way these parameters move with temperature:

#### Conclusion

In FLYBACK converters, leakage inductance always stresses the switching elements. An efficient active or passive protection network is, therefore, mandatory to ensure the SMPS will survive in any operating conditions. This paper details some possibilities on how to implement the adequate level of protection.

# **Notes**

# **Notes**

# **Notes**

ON Semiconductor and UN are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### **NORTH AMERICA Literature Fulfillment:**

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

#### N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303-308-7140 (Mon-Fri 2:30pm to 7:00pm CET) Email: ONlit-german@hibbertco.com

Phone: (+1) 303-308-7141 (Mon-Fri 2:00pm to 7:00pm CET)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303-308-7142 (Mon-Fri 12:00pm to 5:00pm GMT)

Email: ONlit@hibbertco.com

### EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

Toll-Free from Mexico: Dial 01-800-288-2872 for Access then Dial 866-297-9322

ASIA/PACIFIC: LDC for ON Semiconductor - Asia Support

Phone: 303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-0031

Phone: 81-3-5740-2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.