**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# KAI-2093

# 1920 (H) x 1080 (V) Interline CCD Image Sensor

#### Description

The KAI-2093 Image Sensor is a high-performance multi-megapixel image sensor designed for a wide range of medical imaging and machine vision applications.

The 7.4  $\mu$ m square pixels with microlenses provide high sensitivity and the large full well capacity results in high dynamic range. The split horizontal register offers a choice of single or dual output allowing either 15 or 30 frame per second (fps). The architecture allows for either progressive scan or interlaced readout. The imager features 5 V clocking to facilitate camera design. The vertical overflow drain structure provides antiblooming protection, and enables electronic shuttering for precise exposure control.

| Parameter                                                                                                  | Typical Value                                            |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Architecture                                                                                               | Interline CCD, Progressive Scan or<br>Interlaced Readout |

| Total Number of Pixels                                                                                     | 1984 (H) × 1092 (V)                                      |

| Number of Effective Pixels                                                                                 | 1928 (H) × 1084 (V)                                      |

| Number of Active Pixels                                                                                    | 1920 (H) × 1080 (V)                                      |

| Pixel Size                                                                                                 | 7.4 $\mu m$ (H) $\times$ 7.4 $\mu m$ (V)                 |

| Active Image Size                                                                                          | 14.208 mm (H) × 7.992 mm (V),<br>16.3 mm (Diagonal)      |

| Aspect Ratio                                                                                               | 16:9                                                     |

| Number of Outputs                                                                                          | 1 or 2                                                   |

| Saturation Signal                                                                                          | 40,000 e⁻                                                |

| Output Sensitivity                                                                                         | 14 μV/e <sup>-</sup>                                     |

| Quantum Efficiency<br>–ABA (490 nm)<br>–CBA (R = 620 nm, G = 540 nm,<br>B = 460 nm)                        | 40%<br>37%, 34%, 30%                                     |

| Total Noise                                                                                                | 40 e <sup>–</sup> rms                                    |

| Dark Current (Typical)                                                                                     | < 0.5 nA/cm <sup>2</sup>                                 |

| Dynamic Range                                                                                              | 60 dB                                                    |

| Maximum Pixel Clock Speed                                                                                  | 40 MHz                                                   |

| Blooming Suppression                                                                                       | 100 X                                                    |

| Smear                                                                                                      | < 0.03%                                                  |

| Image Lag                                                                                                  | < 10 electrons                                           |

| Frame Rate<br>Single Output, 20 MHz<br>Single Output, 35 MHz<br>Dual Output, 20 MHz<br>Dual Output, 37 MHz | 9 fps<br>15 fps<br>17 fps<br>30 fps                      |

| Maximum Data Rate                                                                                          | 40 MHz/Channel (2 Channels)                              |

| Package                                                                                                    | 32 pin CerDIP                                            |

| Cover Glass                                                                                                | Clear Glass or Quartz Glass with<br>AR Coating (2 sides) |

NOTE: Parameters above are specified at T =  $40^{\circ}$ C unless otherwise noted.

# **ON Semiconductor®**

www.onsemi.com

Figure 1. KAI–2093 Interline CCD Image Sensor

#### Features

- Progressive Scan (Non-interlaced)

- HCCD and Output Amplifier Capable of 40 MHz Operation

- 5 V HCCD Clocking

- Single or Dual Video Output Operation

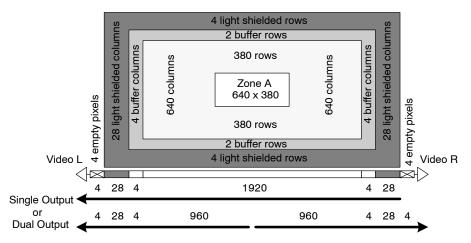

- 28 Light Shielded Reference Columns per Output

- Only 2 Vertical CCD Clocks and 2 Horizontal CCD Clocks

- Electronic Shutter

- Low Dark Current

#### Applications

- Intelligent Transportation Systems

- Machine Vision

- Surveillance

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

# **ORDERING INFORMATION**

#### Table 2. ORDERING INFORMATION – KAI–2093 IMAGE SENSOR

| Part Number                                                                                                                                          | Part Number Description                                                                                                                     |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| KAI-2093-AAA-CP-AE                                                                                                                                   | Monochrome, No Microlens, CERDIP Package (Sidebrazed),<br>Taped Clear Cover Glass (No Coatings), Engineering Sample                         | KAI-2093 |

| KAI-2093-AAA-CP-BA                                                                                                                                   | 3-AAA-CP-BA Monochrome, No Microlens, CERDIP Package (Sidebrazed),<br>Taped Clear Cover Glass (No Coatings), Standard Grade                 |          |

| KAI-2093-ABA-CB-AE                                                                                                                                   | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass (No Coatings), Engineering Sample                      |          |

| KAI-2093-ABA-CB-B1                                                                                                                                   | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass (No Coatings), Grade 1                                 |          |

| KAI-2093-ABA-CB-B2                                                                                                                                   | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass (No Coatings), Grade 2                                 |          |

| KAI-2093-ABA-CK-AE                                                                                                                                   | K-AE Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Quartz Cover Glass with AR Coating (Both Sides), Engineering Sample |          |

| KAI-2093-ABA-CK-BA                                                                                                                                   | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Quartz Cover Glass with AR Coating (Both Sides), Standard Grade          |          |

| KAI-2093-ABA-CP-AE                                                                                                                                   | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Taped Clear Cover Glass (No Coatings), Engineering Sample                |          |

| KAI-2093-ABA-CP-BA      Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),        Taped Clear Cover Glass (No Coatings), Standard Grade |                                                                                                                                             |          |

| KAI-2093-CBA-CB-AE                                                                                                                                   | A-CB-AE Color (Bayer RGB), Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass (No Coatings), Engineering Sample       |          |

| KAI-2093-CBA-CB-BA                                                                                                                                   | 93-CBA-CB-BA Color (Bayer RGB), Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass (No Coatings), Standard Grade      |          |

#### Table 3. ORDERING INFORMATION – EVALUATION SUPPORT

| Part Number          | Description                                     |

|----------------------|-------------------------------------------------|

| KAI-2093-10-40-A-EVK | Evaluation Board, 10 Bit, 40 MHz (Complete Kit) |

| KAI-2093-12-20-A-EVK | Evaluation Board, 12 Bit, 20 MHz (Complete Kit) |

See the ON Semiconductor *Device Nomenclature* document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at <a href="http://www.onsemi.com">www.onsemi.com</a>.

# **DEVICE DESCRIPTION**

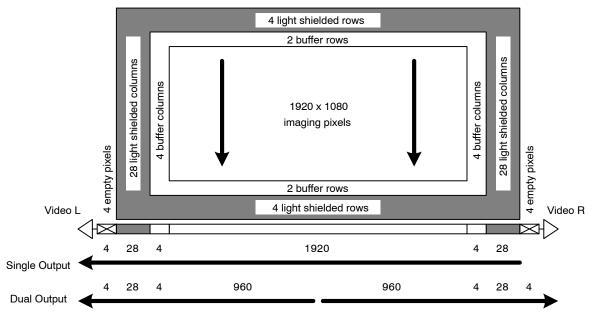

#### Architecture

There are 4 light shielded rows followed by 1084 photoactive rows and finally 4 more light shielded rows. The first and last 2 photoactive rows are buffer rows giving a total of 1080 lines of image data.

In the single output mode all pixels are clocked out of the Video L output in the lower left corner of the sensor. The first four empty pixels of each line do not receive charge from the vertical shift register. The next 28 pixels receive charge from the left light shielded edge followed by 1928 photoactive pixels and finally 28 more light shielded pixels from the right edge of the sensor. The first and last 4 photoactive

pixels are buffer pixels giving a total of 1920 pixels of image data.

In the dual output mode the clocking of the right half of the horizontal CCD is reversed. The left half of the image is clocked out Video L and the right half of the image is clocked out Video R. Each row consists of 4 empty pixels followed by 28 light shielded pixels followed by 964 photoactive pixels. When reconstructing the image, data from Video R will have to be reversed in a line buffer and appended to the Video L data.

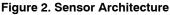

#### **Pin Description and Physical Orientation**

Figure 3. Package Pin Designations - Top View

| Pin | Label |

|-----|-------|

| 1   | φRL   |

| 2   | φH2BL |

| 3   | φH1BL |

| 4   | φH1SL |

| 5   | φH2SL |

| 6   | GND   |

| 7   | OG    |

| 8   | RD    |

| 9   | RD    |

| 10  | OR    |

| 11  | GND   |

| 12  | φH2SR |

| 13  | φH1SR |

| 14  | φH1BR |

| 15  | φH2BR |

| 16  | φR    |

**Table 4. PIN DESCRIPTION**

The horizontal shift register is on the side of the sensor parallel to the row of pins 1 through 16. In single output mode the pixel closest to pin 1 will be read out first through

| Pin | Label |

|-----|-------|

| 17  | VSS   |

| 18  | VOUTR |

| 19  | GND   |

| 20  | φV2O  |

| 21  | φV1   |

| 22  | VSUB  |

| 23  | GND   |

| 24  | VDDR  |

| 25  | VDDL  |

| 26  | GND   |

| 27  | VSUB  |

| 28  | φV1   |

| 29  | φV2E  |

| 30  | ESD   |

| 31  | VOUTL |

| 32  | VSS   |

Video L, the pixel closest to pin 17 will be read out last. In dual output mode the pixel closest to pin 16 will be read out first through Video R.

# IMAGING PERFORMANCE

#### Table 5. TYPICAL OPERATIONAL CONDITIONS

| Description      | Condition                                        |

|------------------|--------------------------------------------------|

| Temperature      | 40°C                                             |

| Integration Time | 33 ms (40 MHz HCCD Frequency, 30 fps Frame Rate) |

| Operation        | Nominal Voltages and Timing                      |

NOTE: Image defects are excluded from performance tests.

#### Specifications

### **Table 6. OPTICAL SPECIFICATIONS**

| Description                                                 | Symbol            | Min. | Nom. | Max. | Units   | Notes |

|-------------------------------------------------------------|-------------------|------|------|------|---------|-------|

| Peak Quantum Efficiency                                     | QE <sub>MAX</sub> | 33   | 36   |      | %       | 1     |

| Peak Quantum Efficiency Wavelength                          | λQE               |      | 490  |      | nm      | 1     |

| Quantum Efficiency at 540 nm                                | QE(540)           | 31   | 33   |      | %       | 1     |

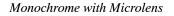

| Microlens Acceptance Angle (horizontal)                     | θQEh              | ±12  | ±13  |      | degrees | 2     |

| Microlens Acceptance Angle (vertical)                       | θQEv              | ±25  | ±30  |      | degrees | 2     |

| Maximum Photoresponse Non-Linearity                         | NL                |      | 2    |      | %       | 3, 4  |

| Maximum Gain Difference between Outputs                     | ΔG                |      | 10   |      | %       | 3, 4  |

| Maximum Signal Error caused by Non-Linearity<br>Differences | ΔNL               |      | 1    |      | %       | 3, 4  |

1. For monochrome sensors.

2. Value is the angular range of incident light for which the quantum efficiency is at least 50% of  $QE_{max}$  at a wavelength of  $\lambda QE$ . Angles are measured with respect to the sensor surface normal in a plane parallel to the horizontal axis ( $\theta QEh$ ) or in a plane parallel to the vertical axis ( $\theta QE\nu$ ).

3. Value is over the range of 10% to 90% of photodiode saturation.

4. Value is for the sensor operated without binning.

### Table 7. CCD SPECIFICATIONS

| Description                    | Symbol          | Min. | Nom. | Max. | Units              | Notes      |

|--------------------------------|-----------------|------|------|------|--------------------|------------|

| Vertical CCD Charge Capacity   | V <sub>Ne</sub> | 45   | 50   |      | ke-                |            |

| Horizontal CCD Charge Capacity | H <sub>Ne</sub> |      | 100  |      | ke-                |            |

| Photodiode Charge Capacity     | P <sub>Ne</sub> | 35   | 40   |      | ke-                | 1          |

| Dark Current                   | Ι <sub>D</sub>  |      | 0.3  | 1.0  | nA/cm <sup>2</sup> |            |

| Image Lag                      | Lag             |      | < 10 | 50   | e-                 | 2          |

| Anti-Blooming Factor           | X <sub>AB</sub> | 100  | 300  |      |                    | 3, 4, 5, 6 |

| Vertical Smear                 | Smr             |      | -75  | -72  | dB                 | 3, 4       |

1. This value depends on the substrate voltage setting. Higher photodiode saturation charge capacities will lower the antiblooming specification. Substrate voltage will be specified with each part for nominal photodiode charge capacity.

2. This is the first field decay lag at 70% saturation. Measured by strobe illumination of the device at 70% of photodiode saturation, and then measuring the subsequent frame's average pixel output in the dark.

3. Measured with a spot size of 100 vertical pixels.

4. Measured with F/4 imaging optics and continuous green illumination centered at 550 nm.

5. A blooming condition is defined as when the spot size doubles in size.

6. Antiblooming factor is the light intensity which causes blooming divided by the light intensity which first saturates the photodiodes.

# KAI-2093

# **Table 8. OUTPUT AMPLIFIER SPECIFICATIONS**

| Description       | Symbol                | Min. | Nom. | Max. | Units | Notes |

|-------------------|-----------------------|------|------|------|-------|-------|

| Power Dissipation | PD                    |      | 120  |      | mW    | 1     |

| Bandwidth         | f <sub>-3DB</sub>     |      | 140  |      | MHz   | 1     |

| Max Off-chip Load | CL                    |      | 10   |      | pF    | 2     |

| Gain              | A <sub>V</sub>        |      | 0.75 |      |       | 1     |

| Sensitivity       | $\Delta V / \Delta N$ |      | 14   |      | μV/e⁻ | 1     |

1. For a 5 mA output load on each amplifier. Per amplifier. 2. With total output load capacitance of  $C_L = 10 \text{ pF}$  between the outputs and AC ground.

# **Table 9. GENERAL SPECIFICATIONS**

| Description   | Symbol           | Min. | Nom. | Max. | Units  | Notes |

|---------------|------------------|------|------|------|--------|-------|

| Total Noise   | n <sub>e-T</sub> |      | 40   |      | e⁻ rms | 1     |

| Dynamic Range | DR               |      | 60   |      | dB     | 2     |

1. Includes system electronics noise, dark pattern noise and dark current shot noise at 20 MHz. 2. Uses  $20LOG(P_{Ne}/n_{e-T})$

# **TYPICAL PERFORMANCE CURVES**

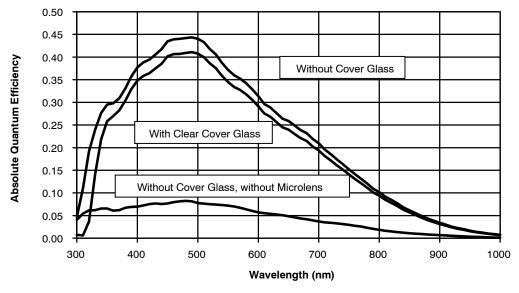

#### Monochrome Quantum Efficiency

Figure 4. Quantum Efficiency Spectrum for Monochrome Sensors

# Monochrome with Microlens Angular Quantum Efficiency

For the curve marked "Horizontal", the incident light angle is varied in a plane parallel to the HCCD. For the curve marked "Vertical", the incident light angle is varied in a plane parallel to the VCCD.

Figure 5. Angular Dependence of Quantum Efficiency

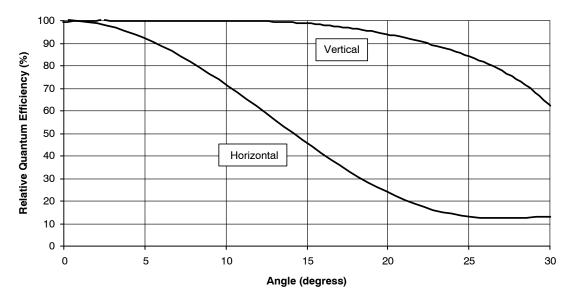

# **Color with Microlens Quantum Efficiency**

Figure 6. Quantum Efficiency Spectrum for Color Filter Array Sensors

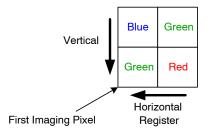

Figure 7. Color Filter Array Pattern

#### Frame Rate (fps) Dual Output Single Output HCCD Clock Frequency (MHz)

Figure 8. Frame Rates

#### Frame Rates

# **DEFECT DEFINITIONS**

## Table 10. OPERATIONAL CONDITIONS

| Description      | Condition                                                    |

|------------------|--------------------------------------------------------------|

| Temperature      | 40°C                                                         |

| Integration Time | 33 ms (40 MHz HCCD Frequency, No Binning, 30 fps Frame Rate) |

| Light Source     | Continuous Green Illumination Centered at 550 nm             |

| Operation        | Nominal Voltages and Timing                                  |

#### **Table 11. SPECIFICATIONS**

| Name                  | Definition                                                                                                                                                                                                                         |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Major Defective Pixel | A pixel whose signal deviates by more than 25 mV from the mean value of all active pixels under dark field condition or by more than 15% from the mean value of all active pixels under uniform illumination of 80% of saturation. |

| Minor Defective Pixel | A pixel whose signal deviates by more than 8 mV from the mean value of all active pixels under dark field conditions.                                                                                                              |

| Cluster Defect        | A group of 2 to 10 contiguous major defective pixels with a width no wider than 2 defective pixels.                                                                                                                                |

| Column Defect         | A group of more than 10 contiguous major defective pixels along a single column.                                                                                                                                                   |

There will be at least two non-defective pixels separating any two major defective pixels.

Buffer and dark reference pixels are not used for defect tests.

#### **Defect Zones**

#### **Defect Classes**

## Table 12. MAXIMUM NUMBER OF DEFECTS

| Major Point                                 |                | Minor         | Point          | Cluster       |                | Column        |                |

|---------------------------------------------|----------------|---------------|----------------|---------------|----------------|---------------|----------------|

| KAI-2093-ABA-CB-B1                          |                |               |                |               |                |               |                |

| Within Zone A                               | Outside Zone A | Within Zone A | Outside Zone A | Within Zone A | Outside Zone A | Within Zone A | Outside Zone A |

| 3                                           | 10             | 20            | 100            | 0 4           |                | 0             | 0              |

| All Other Part Numbers (Zone A is not used) |                |               |                |               |                |               |                |

| 10                                          |                | 1(            | 00             | 4             |                | 0             |                |

# **OPERATION**

#### Table 13. ABSOLUTE MAXIMUM RATINGS

| Description          |                               | Minimum | Maximum | Units | Notes |

|----------------------|-------------------------------|---------|---------|-------|-------|

| Temperature          | Operation without damage      | -50     | 70      | °C    |       |

| Voltage between pins | VSUB to GND                   | 8       | 20      | V     | 1, 3  |

|                      | VDD, OG to GND                | 0       | 17      | V     |       |

|                      | VRD to GND                    | 0       | 14      | V     |       |

|                      | $\varphi V1$ to $\varphi V2$  | -20     | 20      | V     |       |

|                      | φH1 to φH2                    | -15     | 15      | V     |       |

|                      | φR to GND                     | -15     | 15      | V     |       |

|                      | φH1, φH2 to OG                | -15     | 15      | V     |       |

|                      | φH1, $φ$ H2 to $φ$ V1, $φ$ V2 | -15     | 15      | V     |       |

| Current              | Video Output Bias Current     | 0       | 10      | mA    | 2     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. For electronic shuttering VSUB may be pulsed to 50 V for up to 10  $\mu$ s.

2. Total for both outputs. Current is 5 mA for each output. Note that the current bias affects the amplifier bandwidth.

3. Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visibility Lighting Conditions.

#### **Table 14. DC BIAS OPERATING CONDITIONS**

| Description             | Symbol          | Min. | Nom. | Max. | Units | Notes |

|-------------------------|-----------------|------|------|------|-------|-------|

| Output Gate             | OG              | -3.0 | -2.5 | -2.0 | V     |       |

| Reset Drain             | VRD             | 10.0 | 10.5 | 11.0 | V     |       |

| Output Amplifier Return | V <sub>SS</sub> | 0.0  | 0.7  | 1.0  | V     |       |

| Output Amplifier Supply | V <sub>DD</sub> | 14.5 | 15.0 | 15.5 | V     |       |

| Ground, P-well          | GND             |      | 0.0  |      | V     |       |

| Substrate               | VSUB            | 8.0  | TBD  | 17.0 | V     | 2     |

| ESD Protection          | VESD            | -8.0 | -7.0 | -6.0 | V     | 1     |

V<sub>ESD</sub> must be at least 1 V more negative than φH1L and φH2L during sensors operation AND during camera power turn on.

Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

# **AC Operating Conditions**

#### Table 15. CLOCK LEVELS

| Description                  | Symbol               | Min. | Nom. | Max. | Unit | Notes |

|------------------------------|----------------------|------|------|------|------|-------|

| Vertical CCD Clock High      | φV2H                 | 7.5  | 8.0  | 8.5  | V    |       |

| Vertical CCD Clocks Midlevel | φV1M, φV2M           | -1.6 | -1.5 | -1.4 | V    |       |

| Vertical CCD Clocks Low      | φV1L, φV2L           | -9.5 | -9.0 | -8.5 | V    |       |

| Horizontal CCD Clocks High   | φΗ1Η, φΗ2Η           | 0.5  | 1.0  | 2.0  | V    |       |

| Horizontal CCD Clocks Low    | φH1L, φH2L           | -5.0 | -4.0 | -3.8 | V    |       |

| Reset Clock Amplitude        | φR                   |      | 5.0  |      | V    |       |

| Reset Clock Low              | φRL                  | -4.0 | -3.5 | -3.0 | V    |       |

| Electronic Shutter Voltage   | V <sub>SHUTTER</sub> | 44   | 48   | 52   | V    | 1     |

1. Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

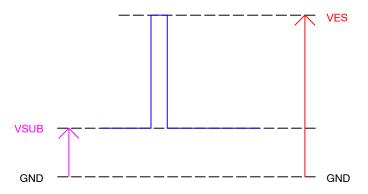

The figure below shows the DC bias (VSUB) and AC clock (VES) applied to the SUB pin. Both the DC bias and AC clock are referenced to ground.

Figure 10. DC Bias and AC Clock Applied to the SUB Pin

| Clocks                   | Capacitance | Units | Notes |

|--------------------------|-------------|-------|-------|

| φV1 to GND               | 25          | nF    | 1     |

| φV2 to GND               | 25          | nF    | 1     |

| $\phi$ V1 to $\phi$ V2   | 5           | nF    |       |

| φH1S to GND              | 45          | pF    | 2     |

| φH2S to GND              | 38          | pF    | 2     |

| φH1B to GND              | 21          | pF    | 2     |

| φH2B to GND              | 20          | pF    | 2     |

| $\phi$ H2B to $\phi$ H1S | 10          | pF    | 2     |

| φH1B to φH1S             | 10          | pF    | 2     |

| φH2B to φH2S             | 10          | pF    | 2     |

| φH1B to φH2S             | 10          | pF    | 2     |

| φR to GND                | 10          | pF    |       |

#### Table 16. CLOCK CAPACITANCE

1. Gate capacitance to GND is voltage dependent. Value is for nominal VCCD clock voltages.

2. For nominal HCCD clock voltages, total capacitance for one half (H1SR only or H1SL only).

# **Operation Notes**

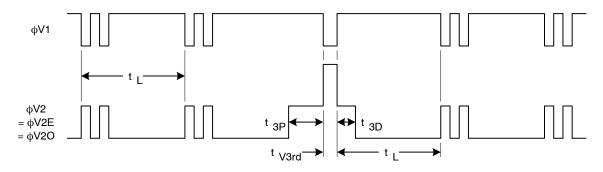

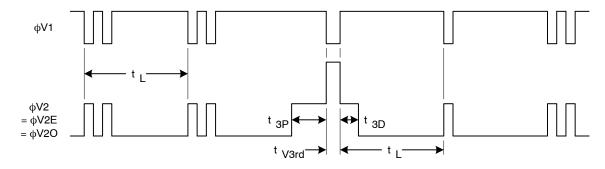

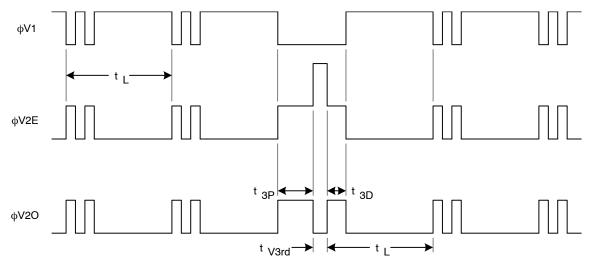

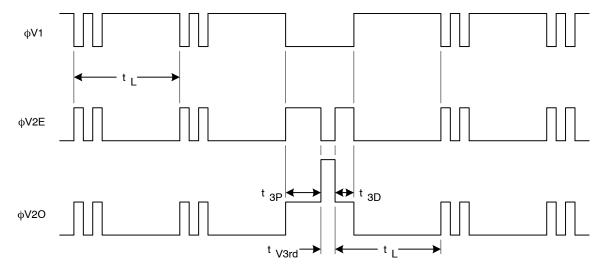

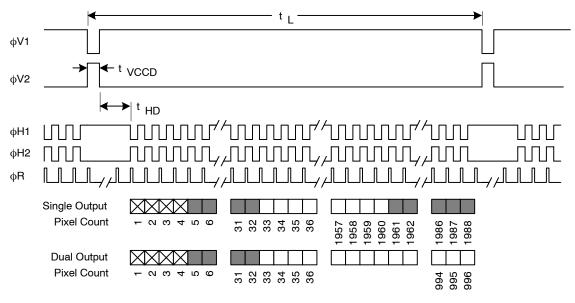

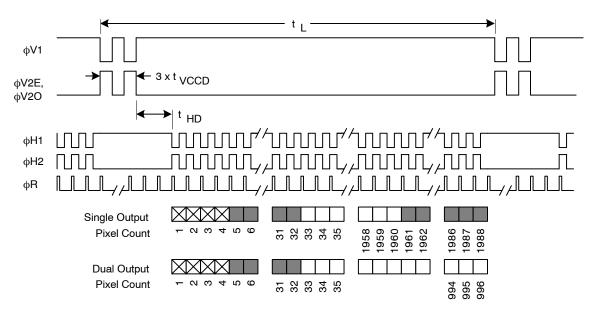

# Progressive and Interlaced Timing

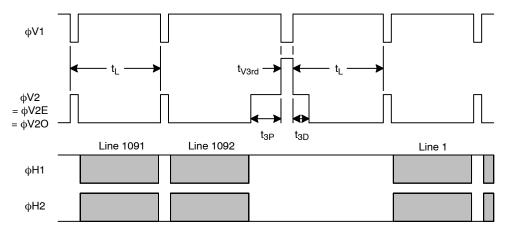

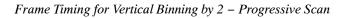

Progressive and interlaced output modes are achieved by the applying the proper waveforms to the vertical clock input pins  $\phi V1$ ,  $\phi V2E$  and  $\phi V2O$ . For progressive output,  $\phi V2 = \phi V2E = \phi V2O$ , with each of the 1092 lines read out individually using the timing in Figures 11 and 12.

For interlaced output, there are two modes, field integration mode and frame integration mode. In both modes, 1092/2 = 546 lines are read in each frame readout, with one even frame readout and one odd frame readout necessary for a complete frame. Field integration mode bins together alternate lines, and the timing is shown in Figures 14 and 15. As with progressive readout,

#### $\phi V2 = \phi V2E = \phi V2O.$

Frame integration mode reads out the photodiodes of the even and odd lines separately, and the timing is shown in Figures 16 and 17. In this case,  $\phi V2E$  and  $\phi V2O$  are clocked individually.

# Single Output Mode

When operating the sensor in single output mode all pixels of the image sensor will be shifted out the Video L output (pin 31). To conserve power and lower heat generation the output amplifier for Video R may be turned off by connecting VDDR (pin 24) and VOUTR (pin 18) to GND (zero volts).

The  $\phi$ H1 timing from the timing diagrams should be applied to  $\phi$ H1SL,  $\phi$ H1BL,  $\phi$ H1SR,  $\phi$ H2BR, and the  $\phi$ H2 timing should be applied  $\phi$ H2SL,  $\phi$ H2BL,  $\phi$ H2SR,  $\phi$ H1BR. In other words, the clock driver generating the  $\phi$ H1 timing should be connected to pins 4, 3, 13, and 15. The clock driver generating the  $\phi$ H2 timing should be connected to pins 2, 5, 12, and 14.

The horizontal CCD should be clocked for 4 empty pixels plus 28 light shielded pixels plus 1928 photoactive pixels plus 28 light shielded pixels for a total of 1988 pixels.

# Dual Output Mode

In dual output mode the connections to the  $\phi$ H1BR and  $\phi$ H2BR pins are swapped from the single output mode to change the direction of charge transfer of the right side horizontal shift register. In dual output mode both VDDL and VDDR (pins 25, 24) should be connected to 15 V.

The  $\phi$ H1 timing from the timing diagrams should be applied to  $\phi$ H1SL,  $\phi$ H1BL,  $\phi$ H1SR,  $\phi$ H1BR, and the  $\phi$ H2 timing should be applied to  $\phi$ H2SL,  $\phi$ H2BL,  $\phi$ H2SR,  $\phi$ H2BR. The clock driver generating the  $\phi$ H1 timing should be connected to pins 4, 3, 13, and 14. The clock driver generating the  $\phi$ H2 timing should be connected to pins 2, 5, 12, and 15.

The horizontal CCD should be clocked for 4 empty pixels plus 28 light shielded pixels plus 964 photoactive pixels for a total of 996 pixels.

If the camera is to have the option of dual or single output mode, the clock driver signals sent to  $\phi$ H1BR and  $\phi$ H2BR

may be swapped by using a relay. Another alternative is to have two extra clock drivers for  $\phi$ H1BR and  $\phi$ H2BR and invert the signals in the timing logic generator. If two extra clock drivers are used, care must be taken to ensure the rising and falling edges of the  $\phi$ H1BR and  $\phi$ H2BR clocks occur at the same time (within 3 ns) as the other HCCD clocks.

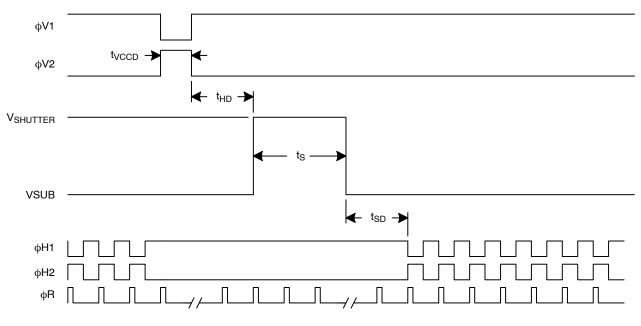

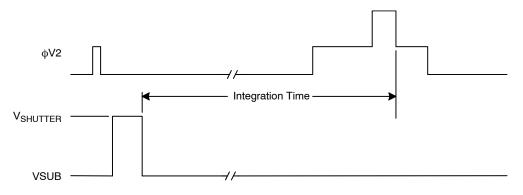

# Exposure Control

If the sensor is operated at 20 MHz horizontal CCD frequency then the frame rate will be 9 fps and the integration time will be 1/9 s or 111 ms. To achieve shorter integration times, the electronic shutter option may be used by applying a pulse to the substrate (pins 22 and 27). The time between the falling edge of the substrate pulse and the falling edge of the transition of the  $\phi$ V2 clock from  $\phi$ V2H to  $\phi$ V2M is defined as the integration time. The substrate pulse and integration time are shown in Figure 14.

Integration times longer than one frame time (111 ms in this example) do not require use of the electronic shutter. Without the electronic shutter the integration time is defined as the time between when the  $\phi$ V2 clock is at the  $\phi$ V2H level of 9.5 V (when the  $\phi$ V2 clock is at the  $\phi$ V2H level charge collected in the photodiodes is transferred to the vertical shift register). To extend the integration time, increase the time between each  $\phi$ V2H level of the  $\phi$ V2 clock. While the photodiodes are integrating photoelectrons the vertical and horizontal shift registers should be continuously clocked to prevent the collection of dark current in the vertical shift register. This is most easily done by increasing the number of lines read out of the image sensor. For example, to double the integration time read out 2184 lines instead of 1092 lines (but remember only the first 1092 lines will contain image data).

Depending on the image quality desired and temperature of the sensor, integration times longer than one second may require the sensor to be cooled to control dark current. The output amplifiers will also generate a non–uniform dark current pattern near the bottom corners of the sensor. This can be reduced at long integration times by only turning on VDD to each amplifier during image readout. If the vertical and horizontal shift registers are also stopped during integration time, the dark current in the shift registers should be flushed out completely before transferring charge from the photodiodes to the vertical shift register.

# Dark Reference

There are 28 light shielded columns at the left and right side of the image sensor. The first and last two light shielded columns should not be used as a dark reference due to some light leakage under the edges of the light shielding. Only the center 24 columns should be used for dark reference line clamping. There are 4 light shielded rows at the top and bottom of the image sensor. Only the center two light shielded rows should be used as a dark reference.

#### Connections to the Image Sensor

The reset clock signal operates at the pixel frequency. The traces on the circuit board to the reset clock pins should be kept short and of equal length to ensure that the reset pulse arrives at each pin simultaneously. The circuit board traces to the horizontal clock pins should also be placed to ensure that the clock edges arrive at each pin simultaneously. If reset pulses and the horizontal clock edges are misaligned the noise performance of the sensor will be degraded and balancing the offset and gain of the two output amplifiers will be difficult.

The bias voltages on OG, RD, VSS and VDD should be well filtered with capacitors placed as close to the pins as possible. Noise on the video outputs will be most strongly affected by noise on VSS, VDD, GND, and VSUB. If the electronic shutter is not used then a filtering capacitor should also be placed on VSUB. If the electronic shutter is used, the VSUB voltage should be kept as clean and noise free as possible.

The voltage on VSS may be set by using the 0.6 to 0.7 volt drop across a diode. Place the diode from VSS to GND. To disable one of the output amplifiers connect VDD to GND, do not let VDD float.

The ESD voltage must reach its operating point before any of the horizontal clocks reach their low level. If any pin on the sensor comes within 1 V of the ESD pin the electrostatic damage protection circuit will become active and will not turn off until all voltages are powered down. Operating the sensor with the ESD protection circuit active may damage the sensor.

# TIMING

# Table 17. REQUIREMENTS AND CHARACTERISTICS

| Description                   | Symbol            | Min. | Nom. | Max.  | Unit |

|-------------------------------|-------------------|------|------|-------|------|

| HCCD Delay                    | t <sub>HD</sub>   | 1.3  | 1.5  | 10.0  | μs   |

| VCCD Transfer Time            | t <sub>VCCD</sub> | 1.3  | 1.5  |       | μs   |

| Photodiode Transfer Time      | t <sub>V3rd</sub> | 8.0  | 12.0 | 15.0  | μs   |

| VCCD Pedestal Time            | t <sub>3P</sub>   | 20.0 | 25.0 | 50.0  | μs   |

| VCCD Delay                    | t <sub>3D</sub>   | 15.0 | 20.0 | 100.0 | μs   |

| Reset Pulse Time              | t <sub>R</sub>    | 5.0  | 10.0 |       | ns   |

| Shutter Pulse Time            | t <sub>S</sub>    | 3.0  | 5.0  | 10.0  | μs   |

| Shutter Pulse Delay           | t <sub>SD</sub>   | 1.0  | 1.6  | 10.0  | μs   |

| HCCD Clock Period             | t <sub>H</sub>    | 25.0 | 50.0 | 200.0 | ns   |

| VCCD Rise/Fall Time           | t <sub>VR</sub>   | 0.0  | 0.1  | 1.0   | μs   |

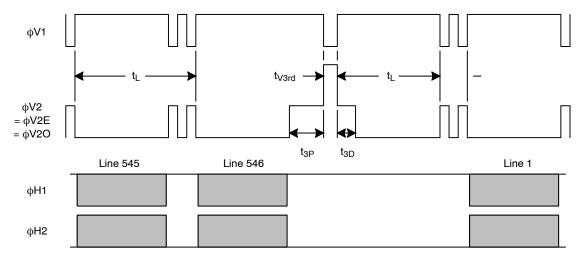

| Vertical Clock Edge Alignment | t <sub>VE</sub>   | 0.0  |      | 100.0 | ns   |

# Frame Timing

Frame Timing – Progressive Scan

Figure 11. Progressive Frame Timing

Figure 12. Frame Timing for Vertical Binning by 2

# KAI-2093

# Vertical Clock Edge Alignment

#### KAI-2093 Vertical Clock Timing - Edge Position

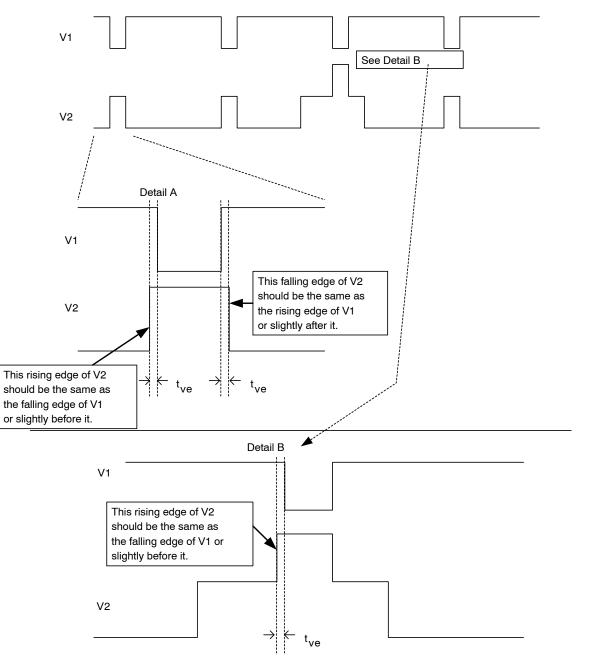

# Frame Timing – Field Integration Mode

Interlaced Frame Timing – Field Integration Mode – Even Field Readout

Figure 14. Interlaced Frame Timing – Field Integration Mode – Even Field Readout

Interlaced Frame Timing - Field Integration Mode - Odd Field Readout

Figure 15. Interlaced Frame Timing – Field Integration Mode – Odd Field Readout

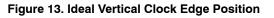

# Frame Timing – Frame Integration Mode

Interlaced Frame Timing – Frame Integration Mode – Even Field Readout

Figure 16. Interlaced Frame Timing – Frame Integration Mode – Even Field Readout

Interlaced Frame Timing – Frame Integration Mode – Odd Field Readout

Figure 17. Interlaced Frame Timing – Frame Integration Mode – Odd Field Readout

# Line Timing

Progressive Line Timing

Figure 18. Progressive Line Timing

Interlaced Line Timing and Line Timing for Vertical Binning by Two

Figure 19. Interlaced Line Timing and Line Timing for Vertical Binning by Two

# **Electronic Shutter Timing**

Electronic Shutter Line Timing

Figure 20. Electronic Shutter Line Timing

Electronic Shutter – Integration Time Definition

# Figure 21. Integration Time Definition

# STORAGE AND HANDLING

#### Table 18. STORAGE CONDITIONS

| Description         | Symbol          | Minimum | Maximum | Unit | Notes |

|---------------------|-----------------|---------|---------|------|-------|

| Storage Temperature | T <sub>ST</sub> | -55     | 80      | °C   | 1     |

| Humidity            | RH              | 5       | 90      | %    | 2     |

1. Long-term exposure toward the maximum temperature will accelerate color filter degradation.

2. T = 25°C. Excessive humidity will degrade MTTF.

For information on ESD and cover glass care and cleanliness, please download the *Image Sensor Handling and Best Practices* Application Note (AN52561/D) from www.onsemi.com.

For information on environmental exposure, please download the Using Interline CCD Image Sensors in High Intensity Lighting Conditions Application Note (AND9183/D) from www.onsemi.com.

For information on soldering recommendations, please download the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D) from www.onsemi.com. For quality and reliability information, please download the *Quality & Reliability* Handbook (HBD851/D) from www.onsemi.com.

For information on device numbering and ordering codes, please download the *Device Nomenclature* technical note (TND310/D) from <u>www.onsemi.com</u>.

For information on Standard terms and Conditions of Sale, please download <u>Terms and Conditions</u> from <u>www.onsemi.com</u>.

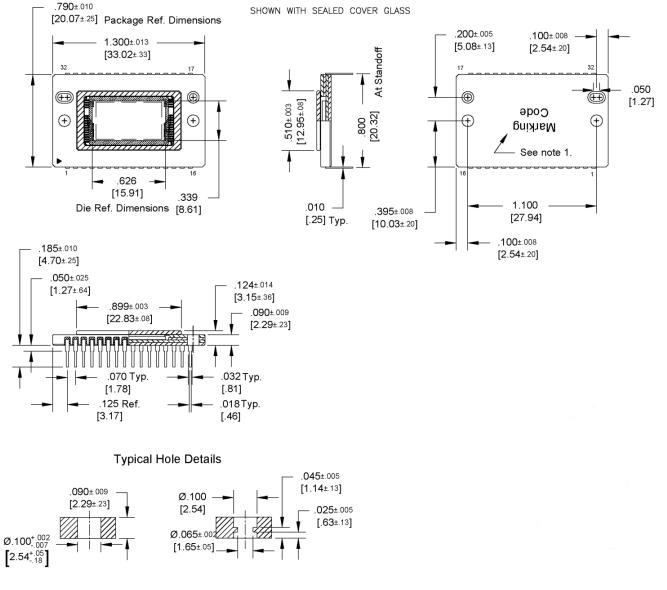

# **MECHANICAL DRAWINGS**

#### **Completed Assembly**

Notes:

1. See Ordering Information for marking code.

2. Cover glass is manually placed and visually aligned

over die - location accuracy is not guaranteed.

Figure 22. Completed Assembly (1 of 2)

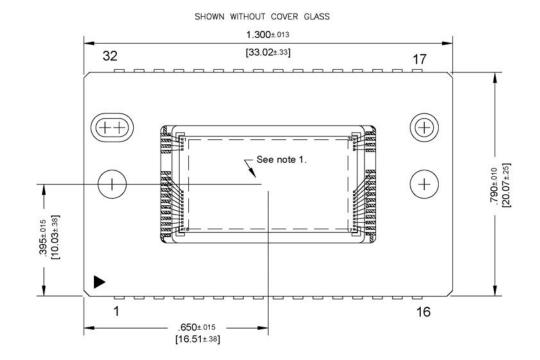

# KAI-2093

SHOWN WITH SEALED COVER GLASS

Notes:

- 1. Center of image is nominally coincident with the center of the package. 2. Die is aligned within  $\pm 2$  degree of any package cavity edge.

#### Figure 23. Completed Assembly (2 of 2)

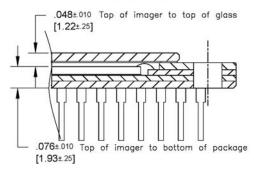

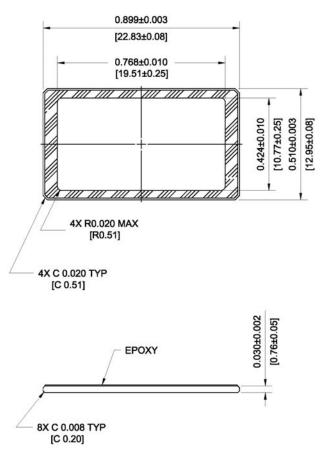

# **Cover Glass**

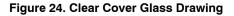

Clear Cover Glass

Notes:

1. Cover Glass Material: Schott D236T eco or equivalent 2. Dust/Scratch: 5 microns maximum

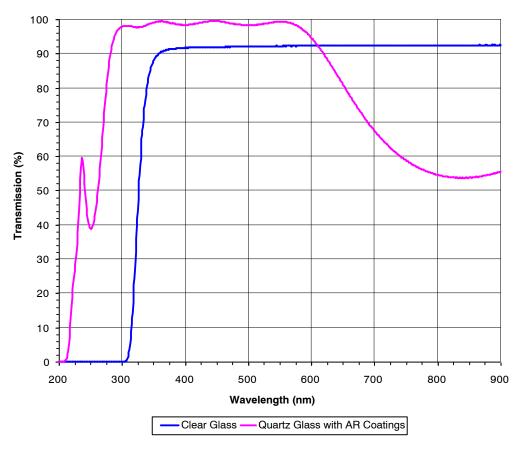

# Quartz Cover Glass with AR Coatings

- Cover Glass Material: SK1300 or equivalent

Dust/Scratch: 10 microns maximum

- 3. MAR Coat Each Side:

- 340 nm 360 nm: Reflectance  $\leq 0.5\%$ 520 nm – 550 nm: Reflectance  $\leq$  4%

Figure 25. Quartz Cover Glass with AR Coating Drawing

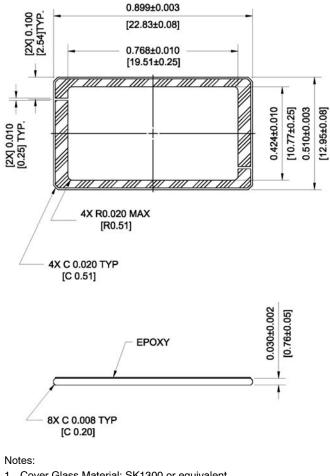

#### **Glass Transmission**

Figure 26. Cover Glass Transmission

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all aws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights or the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor handles, and expenses, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associate

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative