# **Green Mode Power Switch**

# FSL136HR

## Description

The FSL136HR integrated Pulse Width Modulator (PWM) and SENSEFET<sup>®</sup> is specifically designed for high-performance offline Switch-Mode Power Supplies (SMPS) with minimal external components. FSL136HR includes integrated high-voltage power switching regulators that combine an avalanche-rugged SENSEFET with a current-mode PWM control block.

The integrated PWM controller includes: Under-Voltage Lockout (UVLO) protection, Leading-Edge Blanking (LEB), a frequency generator for EMI attenuation, an optimized gate turn-on/turn-off driver, Thermal Shutdown (TSD) protection, and temperature-compensated precision current sources for loop compensation and fault protection circuitry. The FSL136HR offers good soft-start performance. When compared to a discrete MOSFET and controller or RCC switching converter solution, the FSL136HR reduces total component count, design size, and weight; while increasing efficiency, productivity, and system reliability. This device provides a basic platform that is well suited for the design of cost-effective flyback converters.

## Features

- Internal Avalanche-Rugged SENSEFET (650 V)

- Under 50 mW Standby Power Consumption at 265 Vac, No-load Condition with Burst Mode

- Precision Fixed Operating Frequency with Frequency Modulation for Attenuating EMI

- Internal Startup Circuit

- Built-in Soft-Start: 20 ms

- Pulse-by-Pulse Current Limit

- Various Protection: Over Voltage Protection (OVP), Overload Protection (OLP), Output–Short Protection (OSP), Abnormal Over–Current Protection (AOCP), Internal Thermal Shutdown Function with Hysteresis (TSD)

- Auto-Restart Mode

- Under-Voltage Lockout (UVLO)

- Low Operating Current: 1.8 mA

- Adjustable Peak Current Limit

## Table 1. MAXIMUM OUTPUT POWER (Note 1)

| 230 Vac ± 15% (Note 2) |            | 85–26            | 5 Vac      |

|------------------------|------------|------------------|------------|

| Adapter (Note 3)       | Open Frame | Adapter (Note 3) | Open Frame |

| 19 W                   | 26 W       | 14 W             | 20 W       |

1. The junction temperature can limit the maximum output power.

2. 230 Vac or 100/115 Vac with doubler.

3. Typical continuous power in a non–ventilated enclosed adapter measured at 50  $^{\circ}\text{C}$  ambient.

## MARKING DIAGRAM

|           | \$Y&E&Z&2&K<br>FSL136HR |            | \$Y&E&Z&2&K<br>FSL136HR |

|-----------|-------------------------|------------|-------------------------|

| $\circ$   |                         |            | 0                       |

| \$Y<br>&E | = ON Sen<br>= Designa   |            | ductor Logo             |

| &Z        | = Assemb                | ly Pla     | nt Code                 |

| &2        | = 2-Digit               | Date       | code format             |

| &K        | = 2-Digits              | s Lot F    | Run Traceability Code   |

|           | 0                       | <b>D</b> · | 0 I D I                 |

FSL136HR = Specific Device Code Data

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 5 of this data sheet.

## Applications

- SMPS for VCR, STB, DVD & DVCD Players

- SMPS for Home Appliance

- Adapter

## **Related Resources**

- <u>https://www.onsemi.com/pub/Collateral/</u> <u>AN-4137.pdf.pdf</u>

- <u>https://www.onsemi.com/pub/Collateral/</u> <u>AN-4141.pdf.pdf</u>

- <u>https://www.onsemi.com/PowerSolutions/</u> <u>home.do</u>

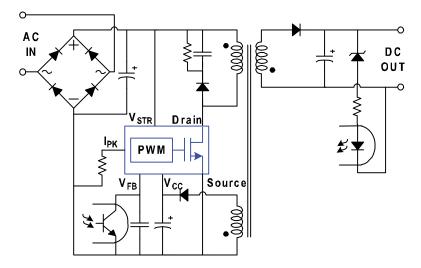

# **TYPICAL APPLICATION DIAGRAM**

Figure 1. Typical Application

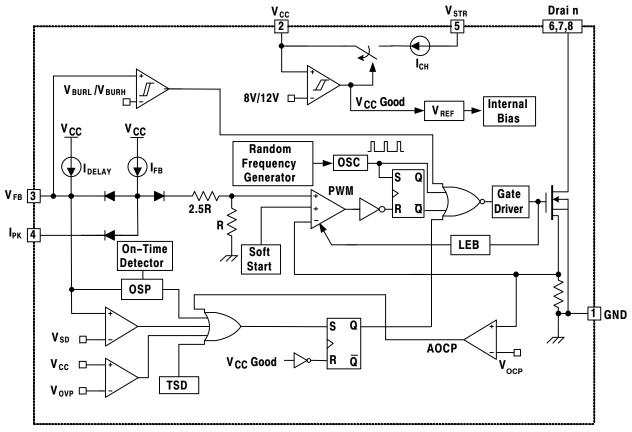

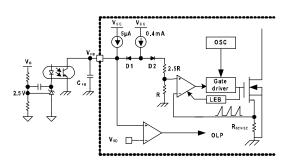

# INTERNAL BLOCK DIAGRAM

Figure 2. Internal Block Diagram

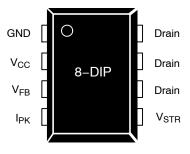

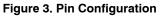

# **PIN CONFIGURATION**

# **PIN DEFINITIONS**

| Pin No. | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND   | Ground. SENSEFET source terminal on the primary side and internal control ground.                                                                                                                                                                                                                                                                                                                                                                                                    |

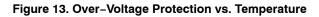

| 2       | Vcc   | <b>Positive Supply Voltage Input.</b> Although connected to an auxiliary transformer winding, current is supplied from pin 5 (V <sub>STR</sub> ) via an internal switch during startup ( <i>see Figure 2</i> ). Once V <sub>CC</sub> reaches the UVLO upper threshold (12 V), the internal startup switch opens and device power is supplied via the auxiliary transformer winding.                                                                                                  |

| 3       | Vfb   | <b>Feedback Voltage</b> . The non–inverting input to the PWM comparator, it has a 0.4 mA current source connected internally, while a capacitor and opto–coupler are typically connected externally. There is a delay while charging external capacitor $C_{FB}$ from 2.4 V to 6 V using an internal 5 $\mu$ A current source. This delay prevents false triggering under transient conditions, but still allows the protection mechanism to operate under true overload conditions. |

| 4       | Ірк   | <b>Peak Current Limit.</b> Adjusts the peak current limit of the SENSEFET. The feedback 0.4 mA current source is diverted to the parallel combination of an internal 6 k $\Omega$ resistor and any external resistor to GND on this pin to determine the peak current limit.                                                                                                                                                                                                         |

| 5       | VSTR  | <b>Startup.</b> Connected to the rectified AC line voltage source. At startup, the internal switch supplies internal bias and charges an external storage capacitor placed between the $V_{CC}$ pin and ground. Once $V_{CC}$ reaches 12 V, the internal switch is opened.                                                                                                                                                                                                           |

| 6, 7, 8 | Drain | <b>Drain.</b> Designed to connect directly to the primary lead of the transformer and capable of switching a maximum of 650 V. Minimizing the length of the trace connecting these pins to the transformer decreases leakage inductance.                                                                                                                                                                                                                                             |

# **ABSOLUTE MAXIMUM RATINGS** (T<sub>J</sub> = 25°C unless otherwise specified)

| Symbol           | Parameter                                  | Min        | Мах       | Unit |

|------------------|--------------------------------------------|------------|-----------|------|

| V <sub>STR</sub> | V <sub>STR</sub> Pin Voltage               | -0.3       | 650       | V    |

| V <sub>DS</sub>  | Drain Pin Voltage                          | -0.3       | 650       | V    |

| V <sub>CC</sub>  | Supply Voltage                             | -          | 26        | V    |

| V <sub>FB</sub>  | Feedback Voltage Range                     | -0.3       | 12.0      | V    |

| ID               | Continuous Drain Current                   | -          | 3         | А    |

| I <sub>DM</sub>  | Drain Current Pulsed (Note 4)              | -          | 12        | А    |

| E <sub>AS</sub>  | Single Pulsed Avalanche Energy (Note 5)    | -          | 230       | mJ   |

| PD               | Total Power Dissipation                    | -          | 1.5       | W    |

| TJ               | Operating Junction Temperature             | Internally | y Limited | °C   |

| T <sub>A</sub>   | Operating Ambient Temperature              | -40        | +150      | °C   |

| T <sub>STG</sub> | Storage Temperature                        | -55        | +150      | °C   |

| ESD              | Human Body Model, JESD22-A114 (Note 6)     | 5.0        | -         | kV   |

|                  | Charged Device Model, JESD22-C101 (Note 6) | 1.5        | -         |      |

#### ABSOLUTE MAXIMUM RATINGS (continued)(T<sub>J</sub> = 25°C unless otherwise specified) (continued)

| Symbol          | Parameter                                          | Min | Max  | Unit |

|-----------------|----------------------------------------------------|-----|------|------|

| $\Theta_{JA}$   | Junction-to-Ambient Thermal Resistance (Note 7, 8) | -   | 80   | °C/W |

| Θ <sub>JC</sub> | Junction-to-Case Thermal Resistance (Note 7, 9)    | -   | 19   |      |

| Θ <sub>JT</sub> | Junction-to-Top Thermal Resistance (Note 7, 10)    | -   | 33.7 |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

4. Repetitive rating: pulse width limited by maximum junction temperature.

5. L = 51 mH, starting  $T_J = 25^{\circ}C$ .

6. Meets JEDEC standards JESD 22-A114 and JESD 22-C101.

7. All items are tested with the standards JESD 51-2 and JESD 51-10.

8.  $\Theta_{JA}$  free-standing, with no heat-sink, under natural convection.

9.  $\Theta_{JC}$  junction-to-lead thermal characteristics under  $\Theta_{JA}$  test condition.  $T_C$  is measured on the source #7 pin closed to plastic interface for  $\Theta_{JA}$  thermo-couple mounted on soldering.

10.  $\Theta_{JA}$  junction-to-top of thermal characteristic under  $\Theta_{JA}$  test condition. Tt is measured on top of package. Thermo-couple is mounted in epoxy glue.

### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol              | Parameter                        | Test Condition                                          | Min  | Тур  | Max  | Unit |

|---------------------|----------------------------------|---------------------------------------------------------|------|------|------|------|

| ENSEFET             | SECTION                          |                                                         |      | 1    |      |      |

| BV <sub>DSS</sub>   | Drain-Source Breakdown Voltage   | $V_{CC}$ = 0 V, $I_D$ = 250 $\mu$ A                     | 650  | -    | -    | V    |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current  | $V_{DS} = 650 \text{ V}, \text{ V}_{GS} = 0 \text{ V}$  | -    | -    | 250  | μA   |

| R <sub>DS(ON)</sub> | Drain-Source On-State Resistance | $V_{GS}$ = 10 V, $V_{GS}$ = 0 V, $T_{C}$ = 25°C         | -    | 3.5  | 4.0  | Ω    |

| C <sub>ISS</sub>    | Input Capacitance                | $V_{GS}$ = 0 V, $V_{DS}$ = 25 V, f = 1MHz               | -    | 290  | -    | pF   |

| C <sub>OSS</sub>    | Output Capacitance               | $V_{GS}$ = 0 V, $V_{DS}$ = 25 V, f = 1MHz               | -    | 45   | -    | pF   |

| C <sub>RSS</sub>    | Reverse Transfer Capacitance     | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 25 V, f = 1MHz | -    | 5.5  | -    | pF   |

| t <sub>d(on)</sub>  | Turn–on Delay                    | V <sub>DD</sub> = 350 V, I <sub>D</sub> = 3.5 A         | -    | 12   | -    | ns   |

| t <sub>r</sub>      | Rise Time                        | V <sub>DD</sub> = 350 V, I <sub>D</sub> = 3.5 A         | -    | 22   | -    | ns   |

| t <sub>d(off)</sub> | Turn-off Delay                   | V <sub>DD</sub> = 350 V, I <sub>D</sub> = 3.5 A         | -    | 20   | -    | ns   |

| t <sub>f</sub>      | Fall Time                        | V <sub>DD</sub> = 350 V, I <sub>D</sub> = 3.5 A         | -    | 19   | -    | ns   |

| ONTROL              | SECTION                          |                                                         | •    |      |      | •    |

| fosc                | Switching Frequency              | $V_{DS}$ = 650 V, $V_{GS}$ = 0 V                        | 90   | 100  | 110  | kHz  |

| $\Delta f_{OSC}$    | Switching Frequency Variation    | $V_{GS}$ = 10 V, $V_{GS}$ = 0 V, $T_{C}$ = 125°C        | -    | ±5   | ±10  | %    |

| f <sub>FM</sub>     | Frequency Modulation             |                                                         | -    | ±3   | -    | kHz  |

| D <sub>MAX</sub>    | Maximum Duty Cycle               | V <sub>FB</sub> = 4 V                                   | 71   | 77   | 83   | %    |

| D <sub>MIN</sub>    | Minimum Duty Ratio               | V <sub>FB</sub> = 0 V                                   | 0    | 0    | 0    | %    |

| V <sub>START</sub>  | UVLO Threshold Voltage           |                                                         | 11   | 12   | 13   | V    |

| V <sub>STOP</sub>   | -                                | After Turn-on                                           | 7.0  | 8.0  | 9.0  | V    |

| I <sub>FB</sub>     | Feedback Source Current          | V <sub>FB</sub> = 0                                     | 320  | 400  | 480  | μA   |

| t <sub>S/S</sub>    | Internal Soft-Start Time         | V <sub>FB</sub> = 4 V                                   | 15   | 20   | 25   | ms   |

| URST-MO             | DE SECTION                       |                                                         |      |      |      |      |

| V <sub>BURH</sub>   | Burst-Mode Voltage               | $T_{\rm J} = 25^{\circ}{\rm C}$                         | 0.4  | 0.5  | 0.6  | V    |

| V <sub>BURL</sub>   | 7                                |                                                         | 0.25 | 0.35 | 0.45 | V    |

|                     | -                                |                                                         |      | 1    | 1    |      |

## PROTECTION SECTION

V<sub>BURH(HYS)</sub>

| I <sub>LIM</sub> | Peak Current Limit                 | $T_J = 25^{\circ}C$ , di/dt = 300 mA/µs | 1.89 | 2.15 | 2.41 | А  |

|------------------|------------------------------------|-----------------------------------------|------|------|------|----|

| t <sub>CLD</sub> | Current Limit Delay Time (Note 11) |                                         | 200  | -    | -    | ns |

| V <sub>SD</sub>  | Shutdown Feedback Voltage          | V <sub>CC</sub> = 15 V                  | 5.5  | 6.0  | 6.5  | V  |

150

mV

# **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ unless otherwise specified) (continued)

| Symbol             | Parameter                     |                               | Test Condition                                                                                                                                 | Min  | Тур  | Max  | Unit |  |

|--------------------|-------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| PROTECTION SECTION |                               |                               |                                                                                                                                                |      |      |      |      |  |

| IDELAY             | Shutdown Delay Curre          | nt                            | V <sub>FB</sub> = 5 V                                                                                                                          | 3.5  | 5.0  | 6.5  | μA   |  |

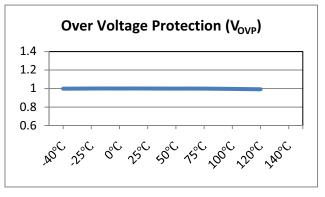

| V <sub>OVP</sub>   | Over-Voltage Protection       | on Threshold                  | V <sub>FB</sub> = 2 V                                                                                                                          | 22.5 | 24.0 | 25.5 | V    |  |

| t <sub>OSP</sub>   | Output Short                  | Threshold Time                | $T_{\rm J} = 25^{\circ}{\rm C}$                                                                                                                | -    | 1.00 | 1.35 | μs   |  |

| V <sub>OSP</sub>   | Protection (Note 11)          | Threshold<br>Feedback Voltage | OSP Triggered when t <sub>ON</sub> < t <sub>OSP</sub> &<br>V <sub>FB</sub> > V <sub>OSP</sub> , which lasts longer than<br>t <sub>OSP FB</sub> | 1.44 | 1.60 | -    | V    |  |

| tosp_fb            |                               | Feedback Blanking<br>Time     |                                                                                                                                                | 2.0  | 2.5  | _    | μs   |  |

| VAOCP              | AOCP Voltage (Note 1          | 1)                            | $T_J = 25^{\circ}C$                                                                                                                            | 0.85 | 1.00 | 1.15 | V    |  |

| TSD                | Thermal Shutdown<br>(Note 11) | Shutdown<br>Temperature       |                                                                                                                                                | 125  | 137  | 150  | °C   |  |

| HYS <sub>TSD</sub> | 1                             | Hysteresis                    |                                                                                                                                                | -    | 60   | -    | °C   |  |

| t <sub>LEB</sub>   | Leading-Edge Blanking         | g Time (Note 11)              |                                                                                                                                                | 300  | -    | -    | ns   |  |

#### TOTAL DEVICE SECTION

| I <sub>OP1</sub> | Operating Supply Current (Note 11)<br>(While Switching) | V <sub>CC</sub> = 14 V, V <sub>FB</sub> > V <sub>BURH</sub> | -   | 2.5 | 3.5 | mA |

|------------------|---------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|----|

| I <sub>OP2</sub> | Operating Switching Current,<br>(Control Part Only)     | $V_{CC}$ = 14 V, $V_{FB}$ < $V_{BURL}$                      | -   | 1.8 | 2.5 | mA |

| I <sub>CH</sub>  | Startup Charging Current                                | V <sub>CC</sub> = 0 V                                       | 0.9 | 1.1 | 1.5 | mA |

| V <sub>STR</sub> | Minimum V <sub>STR</sub> Supply Voltage                 | $V_{CC} = V_{FB} = 0 V$ , $V_{STR}$ Increase                | 35  | -   | _   | V  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

11. Though guaranteed by design, it is not 100% tested in production.

# **ORDERING INFORMATION**

| Part Number | Operating Temperature Range | Top Mark | Package                           | Packing Method <sup>†</sup> |

|-------------|-----------------------------|----------|-----------------------------------|-----------------------------|

| FSL136HR    | –40 to 105 °C               | FSL136HR | 8-Lead, Dual Inline Package (DIP) | Rail                        |

| FSL136HRL   |                             |          | 8-Lead, Surface Mount Package     | Rail                        |

| FSL136HRLX  |                             |          | (LSOP)                            | Tape & Reel                 |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

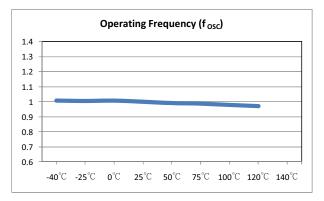

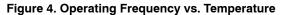

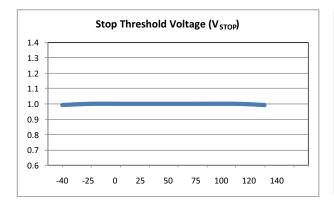

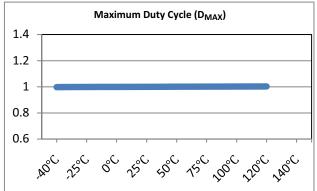

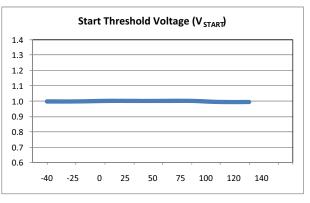

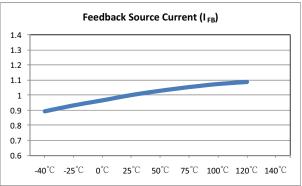

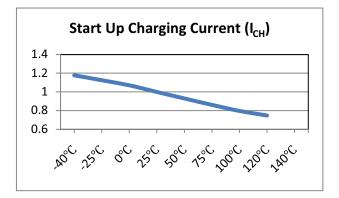

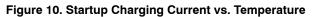

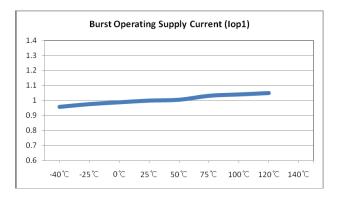

# **TYPICAL PERFORMANCE CHARACTERISTICS**

(These characteristics graphs are normalized  $T_A$  = 25°C.)

Figure 6. Operating Supply Current vs. Temperature

Figure 8. Stop Threshold Voltage vs. Temperature

Figure 5. Maximum Duty Cycle vs. Temperature

Figure 7. Start Threshold Voltage vs. Temperature

Figure 9. Feedback Source Current vs. Temperature

# TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(These Characteristic graphs are normalized at  $T_{\text{A}}$  = 25.)

Figure 12. Burst Operating Supply Current vs. Temperature

Figure 11. Peak Current Limit vs. Temperature

### FUNCTIONAL DESCRIPTION

#### Startup

At startup, an internal high–voltage current source supplies the internal bias and charges the external capacitor (C<sub>A</sub>) connected with the V<sub>CC</sub> pin, as illustrated in Figure 14. When V<sub>CC</sub> reaches the start voltage of 12 V, the power switch begins switching and the internal high–voltage current source is disabled. The power switch continues normal switching operation and the power is provided from the auxiliary transformer winding unless V<sub>CC</sub> goes below the stop voltage of 8 V.

Figure 14. Startup Circuit

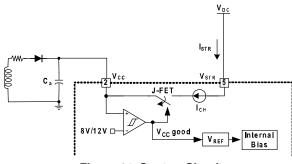

#### **Oscillator Block**

The oscillator frequency is set internally and the power switch has a random frequency fluctuation function. Fluctuation of the switching frequency of a switched power supply can reduce EMI by spreading the energy over a wider frequency range than the bandwidth measured by the EMI test equipment. The amount of EMI reduction is directly related to the range of the frequency variation. The range of frequency variation is fixed internally; however, its selection is randomly chosen by the combination of external feedback voltage and internal free–running oscillator. This randomly chosen switching frequency effectively spreads the EMI noise nearby switching frequency and allows the use of a cost– effective inductor instead of an AC input line filter to satisfy the world–wide EMI requirements.

Figure 15. Frequency Fluctuation Waveform

#### Feedback Control

FSL136HR employs current-mode control, as shown in Figure 16. An opto-coupler (such as the FOD817A) and shunt regulator (such as the KA431) are typically used to implement the feedback network. Comparing the feedback voltage with the voltage across the  $R_{SENSE}$  resistor makes it possible to control the switching duty cycle. When the shunt regulator reference pin voltage exceeds the internal reference voltage of 2.5 V, the optocoupler LED current increases, the feedback voltage  $V_{FB}$  is pulled down, and the duty cycle is reduced. This typically occurs when the input voltage is increased or the output load is decreased.

Figure 16. Pulse–Width–Modulation Circuit

#### Leading-Edge Blanking (LEB)

At the instant the internal SENSEFET is turned on, the primary–side capacitance and secondary–side rectifier diode reverse recovery typically cause a high–current spike through the SENSEFET. Excessive voltage across the  $R_{SENSE}$  resistor leads to incorrect feedback operation in the current–mode PWM control. To counter this effect, the power switch employs a leading–edge blanking (LEB) circuit (*see the Figure 16*). This circuit inhibits the PWM comparator for a short time (t<sub>LEB</sub>) after the SENSEFET is turned on.

#### **Protection Circuit**

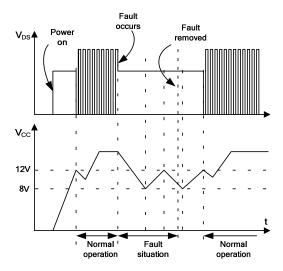

The power switch has several protective functions, such as overload protection (OLP), over-voltage protection (OVP), output-short protection (OSP), under-voltage lockout (UVLO), abnormal over-current protection (AOCP), and thermal shutdown (TSD). Because these various protection circuits are fully integrated in the IC without external components, the reliability is improved without increasing cost. Once a fault condition occurs, switching is terminated and the SENSEFET remains off. This causes V<sub>CC</sub> to fall. When V<sub>CC</sub> reaches the UVLO stop voltage, VSTOP (8 V), the protection is reset and the internal high-voltage current source charges the V<sub>CC</sub> capacitor via the VSTR pin. When VCC reaches the UVLO start voltage, V<sub>START</sub> (12 V), the power switch resumes normal operation. In this manner, the auto-restart can alternately enable and disable the switching of the power SENSEFET until the fault condition is eliminated.

Figure 17. Pulse–Width–Modulation Circuit

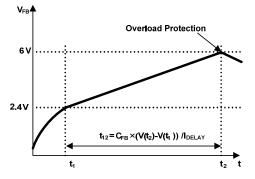

#### **Overload Protection (OLP)**

Overload is defined as the load current exceeding a preset level due to an unexpected event. In this situation, the protection circuit should be activated to protect the SMPS. However, even when the SMPS is operating normally, the overload protection (OLP) circuit can be activated during the load transition or startup. To avoid this undesired operation, the OLP circuit is designed to be activated after a specified time to determine whether it is a transient situation or a true overload situation.

In conjunction with the I<sub>PK</sub> current limit pin (if used), the current-mode feedback path limits the current in the SENSEFET when the maximum PWM duty cycle is attained. If the output consumes more than this maximum power, the output voltage (V<sub>O</sub>) decreases below its rating voltage. This reduces the current through the opto-coupler LED, which also reduces the opto-coupler transistor current, thus increasing the feedback voltage (V<sub>FB</sub>). If V<sub>FB</sub> exceeds 2.4 V, the feedback input diode is blocked and the 5  $\mu$ A current source (I<sub>DELAY</sub>) starts to charge C<sub>FB</sub> slowly up to V<sub>CC</sub>. In this condition, V<sub>FB</sub> increases until it reaches 6 V, when the switching operation is terminated, as shown in Figure 18. The shutdown delay is the time required to charge C<sub>FB</sub> from 2.4 V to 6 V with 5  $\mu$ A current source.

Figure 18. Overload Protection (OLP)

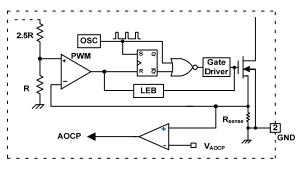

#### Abnormal Over–Current Protection (AOCP)

When the secondary rectifier diodes or the transformer pin are shorted, a steep current with extremely high di/dt can flow through the SENSEFET during the LEB time. Even though the power switch has OLP (Overload Protection), it is not enough to protect the FPS in that abnormal case, since severe current stress is imposed on the SENSEFET until OLP triggers. The power switch includes the internal AOCP (Abnormal Over-Current Protection) circuit shown in Figure 19. When the gate turn-on signal is applied to the power SENSEFET, the AOCP block is enabled and monitors the current through the sensing resistor. The voltage across the resistor is compared with a preset AOCP level. If the sensing resistor voltage is greater than the AOCP level, the set signal is applied to the latch, resulting in the shutdown of the SMPS.

Figure 19. Abnormal Over–Current Protection

#### Thermal Shutdown (TSD)

The SENSEFET and the control IC are integrated, making it easier to detect the temperature of the SENSEFET. When the temperature exceeds approximately 137°C, thermal shutdown is activated.

#### **Over-Voltage Protection (OVP)**

In the event of a malfunction in the secondary-side feedback circuit or an open feedback loop caused by a soldering defect, the current through the opto-coupler transistor becomes almost zero. Then, VFB climbs up in a similar manner to the overload situation, forcing the preset maximum current to be supplied to the SMPS until the overload protection is activated. Because excess energy is provided to the output, the output voltage may exceed the rated voltage before the overload protection is activated, resulting in the breakdown of the devices in the secondary side. To prevent this situation, an over-voltage protection (OVP) circuit is employed. In general, V<sub>CC</sub> is proportional to the output voltage and the power switch uses V<sub>CC</sub> instead of directly monitoring the output voltage. If  $V_{CC}$  exceeds 24 V, OVP circuit is activated, resulting in termination of the switching operation. To avoid undesired activation of OVP during normal operation, V<sub>CC</sub> should be designed to be below 24 V.

#### **Output-Short Protection (OSP)**

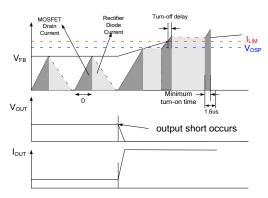

If the output is shorted, steep current with extremely high di/dt can flow through the SENSEFET during the LEB time. Such a steep current brings high–voltage stress on the drain of SENSEFET when turned off. To protect the device from such an abnormal condition, OSP detects  $V_{FB}$  and SENSEFET turn–on time. When the  $V_{FB}$  is higher than 1.6 V and the SENSEFET turn–on time is lower than 1.0  $\mu$ s, the FPS recognizes this condition as an abnormal error and shuts down PWM switching until  $V_{CC}$  reaches  $V_{START}$  again. An abnormal condition output is shown in Figure 20.

Figure 20. Output Short Waveforms (OSP)

#### Soft-Start

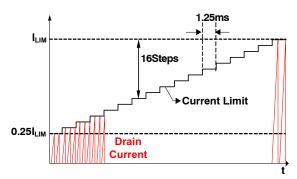

The power switch has an internal soft-start circuit that slowly increases the feedback voltage, together with the SENSEFET current, after it starts. The typical soft-start time is 20 ms, as shown in Figure 21, where progressive increments of the SENSEFET current are allowed during the startup phase. The pulse width to the power switching device is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors. The voltage on the output capacitors is progressively increased with the intention of smoothly establishing the required output voltage. Soft-start helps to prevent transformer saturation and reduce the stress on the secondary diode.

Figure 21. Internal Soft-Start

#### **Burst Operation**

To minimize power dissipation in standby mode, the FPS enters burst mode. As the load decreases, the feedback voltage decreases. As shown in Figure 22, the device automatically enters burst mode when the feedback voltage drops below V<sub>BURH</sub>. Switching continues, but the current limit is fixed internally to minimize flux density in the transformer. The fixed current limit is larger than that defined by  $V_{FB} = V_{BURH}$  and, therefore,  $V_{FB}$  is driven down further. Switching continues until the feedback voltage drops below V<sub>BURL</sub>. At this point, switching stops and the output voltages start to drop at a rate dependent on the standby current load. This causes the feedback voltage to rise. Once it passes V<sub>BURH</sub>, switching resumes. The feedback voltage then falls and the process repeats. Burst mode alternately enables and disables switching of the SENSEFET and reduces switching loss in standby mode.

Figure 22. Burst-Mode Operation

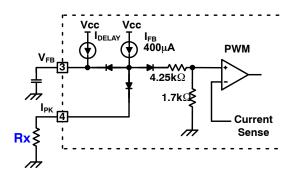

#### **Adjusting Peak Current Limit**

As shown in Figure 23, a combined 6 k $\Omega$  internal resistance is connected to the non-inverting lead on the PWM comparator. An external resistance of Rx on the current limit pin forms a parallel resistance with the 6 k $\Omega$  when the internal diodes are biased by the main current source of 400  $\mu$ A. For example, FSL136HR has a typical SENSEFET peak current limit (I<sub>LIM</sub>) of 2.15 A. I<sub>LIM</sub> can be adjusted to 1.5 A by inserting Rx between the I<sub>PK</sub> pin and the ground. The value of the Rx can be estimated by the following equations:

$$2.15 \text{ A} : 1.5 \text{ A} = 6 \text{ k}\Omega : \text{X k}\Omega$$

(eq. 1)

$$\zeta = Rx \parallel 6 k\Omega \qquad (eq. 2)$$

Where X is the resistance of the parallel network.

>

Figure 23. Peak Current Limit Adjustment

SENSEFET is a registered trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

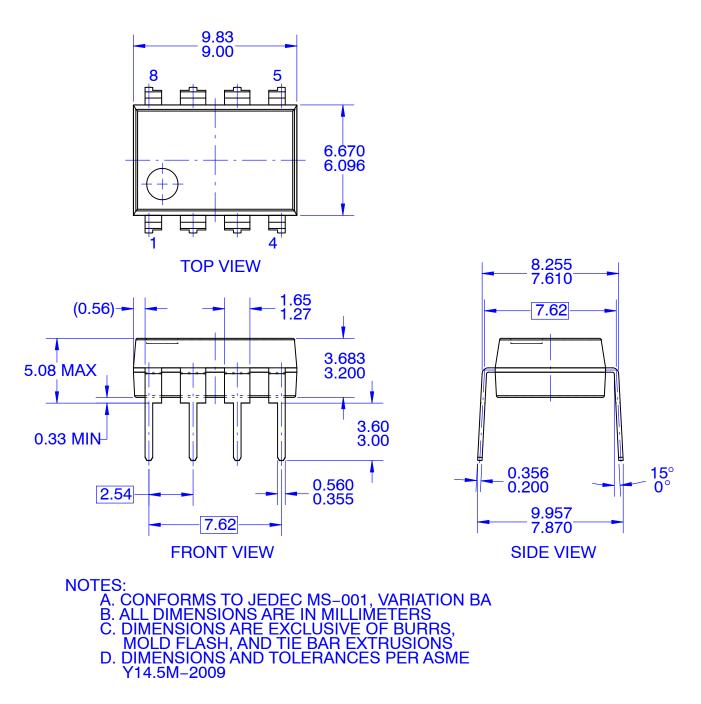

PDIP8 9.42x6.38, 2.54P CASE 646CM ISSUE O

DATE 31 JUL 2016

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                          | 98AON13468G            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                              | PDIP8 9.42X6.38, 2.54P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding |                        |                                                                                                                                                                                     |             |  |  |

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

3.60

3.20

0.25

**SEATING PLANE**

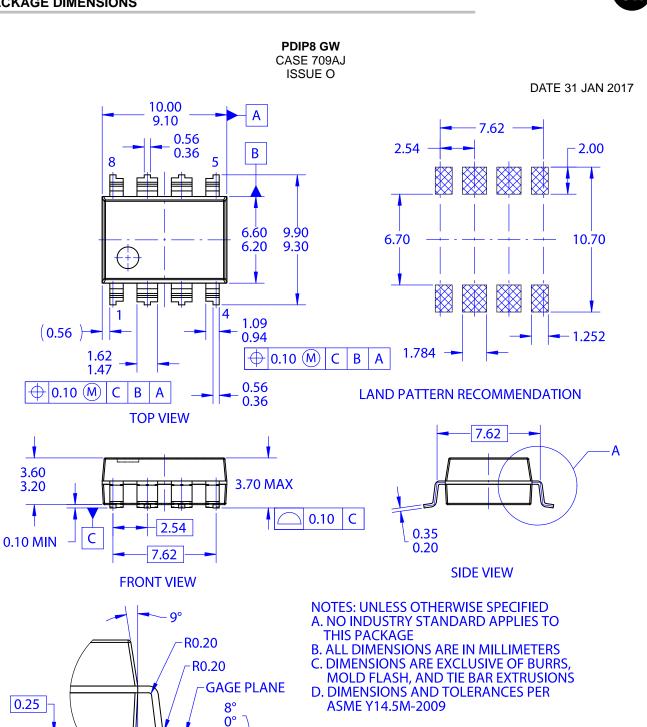

|                  | TAIL A<br>ALE 2:1         |                                                                                                       |             |  |

|------------------|---------------------------|-------------------------------------------------------------------------------------------------------|-------------|--|

| DOCUMENT NUMBER: | 98AON13756G               | Electronic versions are uncontrolle                                                                   |             |  |

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document Repository. Prir<br>versions are uncontrolled except when stamped |             |  |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                                                             |             |  |

| DESCRIPTION:     | PDIP8 GW                  |                                                                                                       | PAGE 1 OF 2 |  |

1.12 0.72

1.60 REF

DOCUMENT NUMBER: 98AON13756G

PAGE 2 OF 2

| ISSUE | REVISION                                                                                      | DATE        |

|-------|-----------------------------------------------------------------------------------------------|-------------|

| 0     | RELEASED FOR PRODUCTION FROM FAIRCHILD MKT-MLSOP08A TO ON SEMICONDUCTOR. REQ. BY D. TRUHITTE. | 31 JAN 2017 |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

|       |                                                                                               |             |

ON Semiconductor and with a registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the BSCILLC product call create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use payers that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>