# Logic Gate Optocoupler, High CMR, Bi-Directional FOD8012A

### **Description**

The FOD8012A is a half duplex, bi–directional, high–speed logic gate Optocoupler, which supports isolated communications allowing digital signals to communicate between systems without conducting ground loops or hazardous voltages. It utilizes **onsemi**'s patented coplanar packaging technology, OPTOPLANAR <sup>®</sup>, and optimized IC design to achieve minimum 20 kV/ $\mu$ s Common Mode Noise Rejection (CMR) rating.

This high–speed logic gate optocoupler is highly integrated with 2 optically coupled channels arranged in bi–directional configuration, and housed in a compact 8–pin small outline package. Each optocoupler channel consists of a high–speed AlGaAs LED driven by a CMOS buffer IC coupled to a CMOS detector IC. The detector IC comprises of an integrated photodiode, a high–speed trans–impedance amplifier and a voltage comparator with an output driver. The CMOS technology coupled to the high efficiency of the LED achieves low power consumption as well as very high speed (60 ns propagation delay, 15 ns pulse width distortion).

#### **Features**

- Half Duplex, Bi-Directional

- 20 kV/µs Minimum Common Mode Rejection

- High Speed:

- ◆ 15 Mbit/s Date Rate (NRZ)

- 60 ns Maximum Propagation Delay

- 15 ns Maximum Pulse Width Distortion

- 30 ns Maximum Propagation Delay Skew

- 3.3 V and 5 V CMOS Compatibility

- Extended Industrial Temperate Range, -40 to +110°C Temperature Range

- Safety and Regulatory Approvals:

- ◆ UL1577, 3750 VAC<sub>RMS</sub> for 1 min.

- ◆ DIN EN/IEC60747-5-5 (approval pending)

### **Applications**

- Industrial Fieldbus Communications

- DeviceNet, CAN, RS485

- Microprocessor System Interface

- ◆ SPI, I<sup>2</sup>C

- Programmable Logic Control

- Isolated Data Acquisition System

- Voltage Level Translator

### **Related Resources**

FOD8001/D, High Noise Immunity, 3.3 V/5 V Logic Gate Optocoupler Datasheet

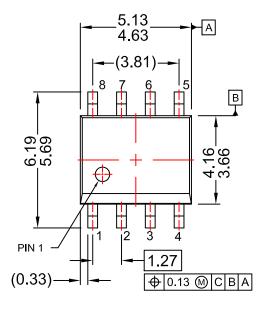

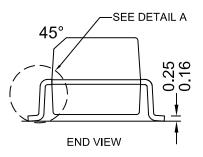

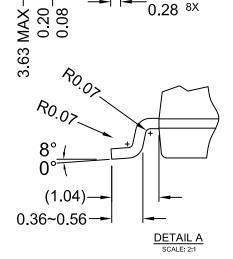

SOIC8 CASE 751DZ

### MARKING DIAGRAM

- 1. ON = onsemi Logo

- 2. 8012A= Device Number

- 3. X = One-Digit Year Code, e.g. '8'

- 4. YY = Two Digit Work Week Ranging from '01' to '53'

- 5. S1 = Assembly Package Code

### ORDERING INFORMATION

See detailed ordering and shipping information on page 9 of this data sheet.

# **TRUTH TABLE**

| V <sub>IN</sub> | LED | v <sub>o</sub> |

|-----------------|-----|----------------|

| High            | OFF | High           |

| Low             | ON  | Low            |

NOTE: When not communicating,  $\ensuremath{V_{\text{IN}}}$  must be in static high logic condition.

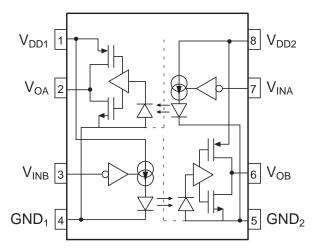

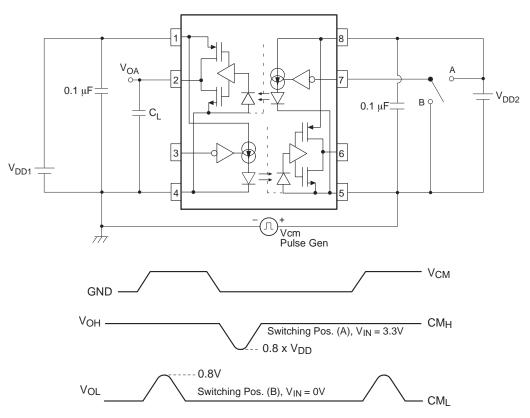

# **Functional Schematic**

$0.1 \mu F$  bypass capacitor required from  $V_{DD}$  to GND

Figure 1. Functional Schematic

# **PIN DEFINITIONS**

| Pin Number | Pin Name         | Description                                                     |

|------------|------------------|-----------------------------------------------------------------|

| 1          | $V_{DD1}$        | Supply Voltage to Channel-A detector IC and Channel-B buffer IC |

| 2          | $V_{OA}$         | Output Voltage from Channel–A detector IC                       |

| 3          | V <sub>INB</sub> | Input Voltage to Channel-B buffer IC                            |

| 4          | GND <sub>1</sub> | Ground for Channel-A detector IC and Channel-B buffer IC        |

| 5          | GND <sub>2</sub> | Ground for Channel-A buffer IC and Channel-B detector IC        |

| 6          | $V_{OB}$         | Output Voltage from Channel–B detector IC                       |

| 7          | V <sub>INA</sub> | Input Voltage to Channel-A buffer IC                            |

| 8          | $V_{DD2}$        | Supply Voltage to Channel-A buffer IC and Channel-B detector IC |

## ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol                              | Parameter                                                     | Value                         | Units |

|-------------------------------------|---------------------------------------------------------------|-------------------------------|-------|

| T <sub>STG</sub>                    | Storage Temperature                                           | -40 to +125                   | °C    |

| T <sub>OPR</sub>                    | Operating Temperature                                         | -40 to +110                   | °C    |

| T <sub>J</sub>                      | Junction Temperature                                          | -40 to +130                   | °C    |

| T <sub>SOL</sub>                    | Lead Solder Temperature (Refer to Reflow Temperature Profile) | 260 for 10 s                  | °C    |

| V <sub>DD1</sub> , V <sub>DD2</sub> | Supply Voltage                                                | 0 to 6.0                      | V     |

| $V_{IA}, V_{IB}$                    | Input Voltage                                                 | –0.5 to V <sub>DD</sub> + 0.5 | V     |

| I <sub>IA</sub> , I <sub>IB</sub>   | Input DC Current                                              | -10 to +10                    | μΑ    |

| V <sub>OA</sub> , V <sub>OB</sub>   | Output Voltage                                                | –0.5 to V <sub>DD</sub> + 0.5 | V     |

| I <sub>OA</sub> , I <sub>OB</sub>   | Average Output Current                                        | 10                            | mA    |

| PDI                                 | Input Power Dissipation (Note 1)                              | 60                            | mW    |

| PDO                                 | Output Power Dissipation (Note 1)                             | 60                            | mW    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. No derating required.

### RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                                  | Min. | Max.            | Unit |

|---------------------------------|--------------------------------------------|------|-----------------|------|

| T <sub>A</sub>                  | Ambient Operating Temperature              | -40  | +110            | °C   |

| $V_{DD1}, V_{DD2}$              | Supply Voltages (3.3 V Operation) (Note 2) | 3.0  | 3.6             | V    |

|                                 | Supply Voltages (5.0 V Operation) (Note 2) | 4.5  | 5.5             |      |

| V <sub>IH</sub>                 | Logic High Input Voltage                   | 2.0  | V <sub>DD</sub> | V    |

| V <sub>IL</sub>                 | Logic Low Input Voltage                    | 0    | 0.8             | V    |

| t <sub>r</sub> , t <sub>f</sub> | Input Signal Rise and Fall Time            |      | 1.0             | ms   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

2. 0.1 μF bypass capacitor must be connected between Pin 1 and 4, and 5 and 8. The capacitors should be kept close to the supply pins.

# **ISOLATION CHARACTERISTICS** (Apply over all recommended conditions, typical value is measured at $T_A = 25$ °C)

| Symbol           | Characteristics                | Test Conditions                                                                            | Min.             | Тур. | Max. | Unit               |

|------------------|--------------------------------|--------------------------------------------------------------------------------------------|------------------|------|------|--------------------|

| V <sub>ISO</sub> | Input-Output Isolation Voltage | $f = 60 \text{ Hz}, t = 1.0 \text{ min.}, I_{I-O} \le 10 \mu\text{A} \text{ (Notes 3, 4)}$ | 3750             |      |      | Vac <sub>RMS</sub> |

| R <sub>ISO</sub> | Isolation Resistance           | V <sub>I-O</sub> = 500 V (Note 3)                                                          | 10 <sup>11</sup> |      |      | Ω                  |

| C <sub>ISO</sub> | Isolation Capacitance          | V <sub>I-O</sub> = 0 V, f = 1.0 MHz (Note 3)                                               |                  | 0.2  |      | pF                 |

- 3. Device is considered a two terminal device: Pins 1, 2, 3 and 4 are shorted together and Pins 5, 6, 7 and 8 are shorted together.

- 4. 3,750 VAC<sub>RMS</sub> for 1 minute duration is equivalent to 4,500 VAC<sub>RMS</sub> for 1 second duration.

# **ELECTRICAL CHARACTERISTICS** ( $T_A = -40^{\circ}\text{C}$ to +110°C, 3.0 V $\leq$ V<sub>DD</sub> $\leq$ 5.5 V, unless otherwise specified. Apply over all recommended conditions, typical value is measured at V<sub>DD1</sub> = V<sub>DD2</sub> = +3.3 V, $T_A = 25^{\circ}\text{C}$ )

| Symbol                                | Parameter                 | Conditions                                                              | Min. | Тур. | Max. | Units |

|---------------------------------------|---------------------------|-------------------------------------------------------------------------|------|------|------|-------|

| I <sub>DD1L</sub> , I <sub>DD2L</sub> | Logic Low Supply Current  | $V_{IA}$ , $V_{IB} = 0 V$                                               |      | 5.8  | 8.0  | mA    |

| I <sub>DD1H</sub> , I <sub>DD2H</sub> | Logic High Supply Current | $V_{IA}, V_{IB} = V_{DD}$                                               |      | 2.5  | 4.0  | mA    |

| I <sub>IA</sub> , I <sub>IB</sub>     | Input Current             |                                                                         | -10  |      | +10  | μΑ    |

| V <sub>OH</sub>                       | Logic High Output Voltage | $I_{O} = -20 \mu A, V_{I} = V_{IH}, V_{DD} = 3.3 V$                     | 3.2  | 3.3  |      | V     |

|                                       |                           | $I_{O} = -4 \text{ mA}, V_{I} = V_{IH}, V_{DD} = 3.3 \text{ V}$         | 3.0  | 3.1  |      |       |

|                                       |                           | $I_{O} = -20 \mu A, V_{I} = V_{IH}, V_{DD} = 5 V$                       | 4.9  | 5.0  |      |       |

|                                       |                           | $I_{O} = -4 \text{ mA}, V_{I} = V_{IH}, V_{DD} = 5 \text{ V}$           | 4.7  | 4.8  |      |       |

| V <sub>OL</sub>                       | Logic Low Output Voltage  | $I_{O} = 20 \mu A$ , $V_{I} = V_{IL}$ , $V_{DD} = 3.3 \text{ V or 5 V}$ |      | 0    | 0.1  | V     |

|                                       |                           | $I_{O} = 4 \text{ mA}, V_{I} = V_{IL}, V_{DD} = 3.3 \text{ V or 5 V}$   |      | 0.26 | 0.6  |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

**SWITCHING CHARACTERISTICS** ( $T_A = -40^{\circ}C$  to +110°C, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, unless otherwise specified. Apply over all recommended conditions, typical value is measured at V<sub>DD1</sub> = V<sub>DD2</sub> = +3.3 V,  $T_A = 25^{\circ}C$ )

| Symbol               | Parameter                                                     | Conditions                                                                         | Min. | Тур. | Max. | Unit   |

|----------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|--------|

|                      | Data Rate                                                     |                                                                                    |      |      | 15   | Mbit/s |

| t <sub>PHL</sub>     | Propagation Delay Time to Logic Low Output                    | PW = 66.7 ns, C <sub>L</sub> = 15 pF                                               |      | 37   | 60   | ns     |

| t <sub>PLH</sub>     | Propagation Delay Time to Logic High Output                   | PW = 66.7 ns, C <sub>L</sub> = 15 pF                                               |      | 40   | 60   | ns     |

| PWD                  | Pulse Width Distortion,   t <sub>PHL</sub> - t <sub>PLH</sub> | PW = 66.7 ns, C <sub>L</sub> = 15 pF<br>(Note 5)                                   |      | 3    | 15   | ns     |

| t <sub>PSK(CC)</sub> | Channel-Channel Skew                                          | PW = 66.7 ns, C <sub>L</sub> = 15 pF<br>(Note 6)                                   |      | 12   | 25   | ns     |

| t <sub>PSK(PP)</sub> | Part-Part Skew                                                | PW = 66.7 ns, C <sub>L</sub> = 15 pF<br>(Note 7)                                   |      |      | 30   | ns     |

| t <sub>R</sub>       | Output Rise Time (10% to 90%)                                 | PW = 66.7 ns, C <sub>L</sub> = 15 pF                                               |      | 6.5  |      | ns     |

| t <sub>F</sub>       | Output Fall Time (90% to 10%)                                 | PW = 66.7 ns, C <sub>L</sub> = 15 pF                                               |      | 6.5  |      | ns     |

| CM <sub>H</sub>      | Common Mode Transient Immunity at Output High                 | $V_I = V_{DD1}, V_O > 0.8 V_{DD1}, V_{CM} = 1000 V \text{ (Note 8)}$               | 20   | 40   |      | kV/μs  |

| CM <sub>L</sub>      | Common Mode Transient Immunity at Output Low                  | V <sub>I</sub> = 0 V, V <sub>O</sub> < 0.8 V,<br>V <sub>CM</sub> = 1000 V (Note 8) | 20   | 40   |      | kV/μs  |

PWD is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen for one channel switching, while holding the other channel output at a low or high state, or while both channels are in synchronous data transmission mode.

t<sub>PSK(CC)</sub> is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between the two channels within a single device.

<sup>7.</sup> t<sub>PSK(PP)</sub> is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between any two units from the same manufacturing date code that are operated at same case temperature, at same operating conditions, with equal loads.

<sup>8.</sup> Common mode transient immunity at output high is the maximum tolerable positive dVcm/dt on the leading edge of the common mode impulse signal, Vcm, to assure that the output will remain high. Common mode transient immunity at output low is the maximum tolerable negative dVcm/dt on the trailing edge of the common pulse signal, Vcm, to assure that the output will remain low.

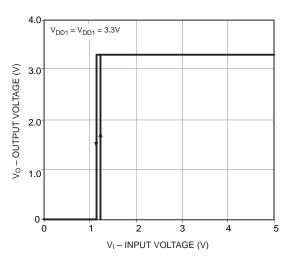

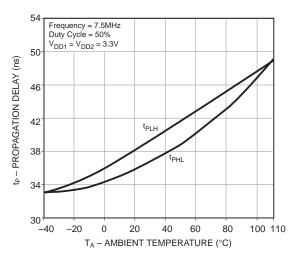

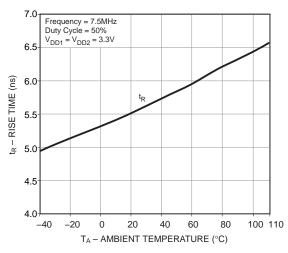

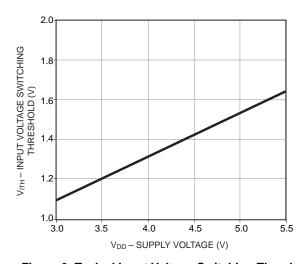

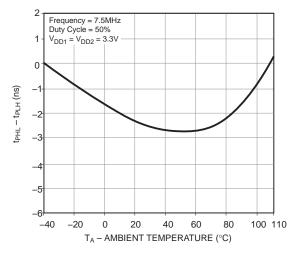

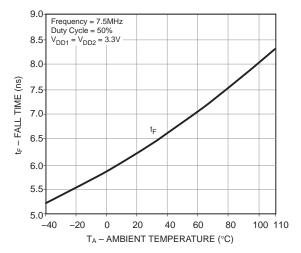

### **TYPICAL PERFORMANCE CURVES**

Figure 2. Typical Output Voltage vs. Input Voltage (Channel A & B)

Figure 4. Typical Propagation Delay vs. Ambient Temperature (Channel A & B)

Figure 6. Typical Rise Time vs. Ambient Temperature (Channel A & B)

Figure 3. Typical Input Voltage Switching Threshold vs. Input Supply Voltage (Channel A & B)

Figure 5. Typical t<sub>PHL</sub> – t<sub>PLH</sub> vs. Ambient Temperature (Channel A & B)

Figure 7. Typical Fall Time vs. Ambient Temperature (Channel A & B)

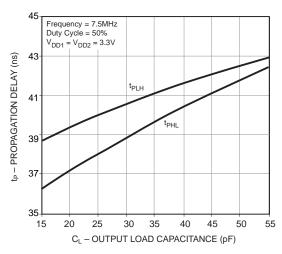

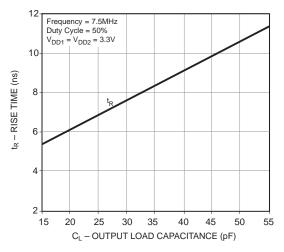

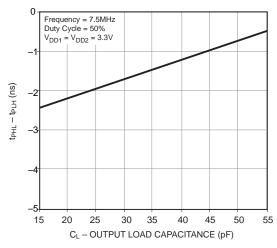

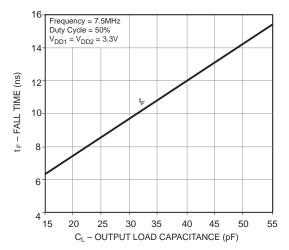

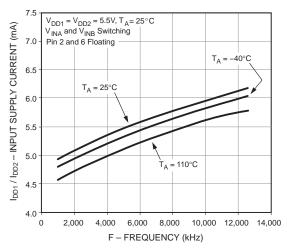

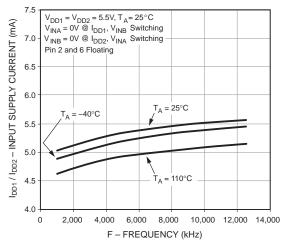

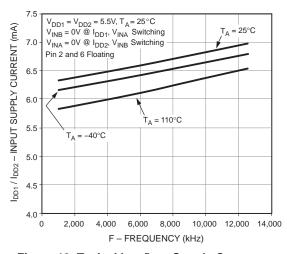

## TYPICAL PERFORMANCE CURVES (Continued)

Figure 8. Typical Propagation Delay vs. Output Load Capacitance (Channel A & B)

Figure 10. Typical Rise Time vs. Output Load Capacitance (Channel A & B)

Figure 9. Typical t<sub>PHL</sub> – t<sub>PLH</sub> vs. Output Load Capacitance (Channel A & B)

Figure 11. Typical Fall Time vs. Output Load Capacitance (Channel A & B)

## TYPICAL PERFORMANCE CURVES (Continued)

Figure 12. Typical I<sub>DD1</sub>/I<sub>DD2</sub> Supply Current vs. Frequency

Figure 14. Typical I<sub>DD1</sub>/I<sub>DD2</sub> Supply Current vs. Frequency

Figure 13. Typical I<sub>DD1</sub>/I<sub>DD2</sub> Supply Current vs. Frequency

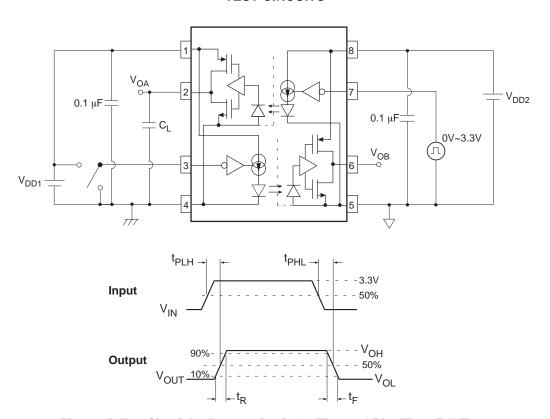

# **TEST CIRCUITS**

Figure 15. Test Circuit for Propagation Delay Time and Rise Time, Fall Time

Figure 16. Test Circuit for Instantaneous Common Mode Rejection Voltage

## **ORDERING INFORMATION**

| Option    | Order Entry Identifier | Package          | Packing Method <sup>†</sup>          |

|-----------|------------------------|------------------|--------------------------------------|

| No Suffix | FOD8012A               | SOIC8 (Pb-Free)* | Tube (50 Units per Tube)             |

| R2        | FOD8012AR2             | SOIC8 (Pb-Free)* | Tape and Reel (2,500 Units per Reel) |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

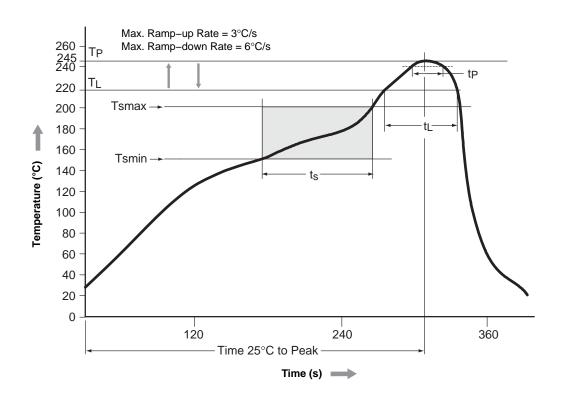

### **REFLOW PROFILE**

| Profile Freature                                          | Pb-Free Assembly Profile |

|-----------------------------------------------------------|--------------------------|

| Temperature Min. (Tsmin)                                  | 150°C                    |

| Temperature Max. (Tsmax)                                  | 200°C                    |

| Time (t <sub>S</sub> ) from (Tsmin to Tsmax)              | 60 – 120 s               |

| Ramp-up Rate (t <sub>L</sub> to t <sub>P</sub> )          | 3°C/s max.               |

| Liquidous Temperature (T <sub>L</sub> )                   | 217°C                    |

| Time (t <sub>L</sub> ) Maintained Above (T <sub>L</sub> ) | 60 – 150 s               |

| Peak Body Package Temperature                             | 245°C + 0°C / -5°C       |

| Time (t <sub>P</sub> ) within 5°C of 245°C                | 30 s                     |

| Ramp-down Rate (T <sub>P</sub> to T <sub>L</sub> )        | 6°C/s max.               |

| Time 25°C to Peak Temperature                             | 8 minutes max.           |

OPTOPLANAR is a registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

<sup>\*</sup>All packages are lead free per JEDEC: J-STD-020B standard.

SOIC8 CASE 751DZ **ISSUE O**

**DATE 30 SEP 2016**

С O.10 C 0.53 0.28 8X

- A) NO STANDARD APPLIES TO THIS PACKAGE

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS.

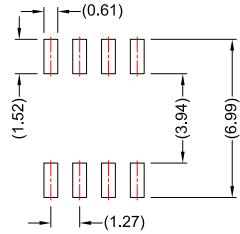

- D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

| DOCUMENT NUMBER: | 98AON13733G | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC8       |                                                                                                                                                                                    | PAGE 1 OF 1 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales