**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# Three-Phase Synchronous Switching Step-Down Controller with Single Wire Current Sharing

The CS5305 provides a low-cost, single-controller solution for the low-voltage, high-current power needs of next-generation workstation and server processors. This IC provides high accuracy and the industry's fastest transient response, reducing the need for large banks of output capacitors and providing the most compact, reliable, and economical power supply.

Since each phase's output voltage and current feed back to develop the PWM ramp signal (enhanced  $V^{2 \text{ TM}}$  control), the CS5305 shares output current accurately between phases. Accurate current sharing means that the power supply design does not need to use power components rated to handle mismatched current per phase. The enhanced  $V^2$  control compensates for variations in both line and load.

The IC's built-in single wire current sharing capability allows easy paralleling of multiple Voltage Regulator Modules (VRMs) based on the CS5305. The paralleled VRMs use a shared bus to provide high current and high reliability to multiple microprocessor workstations or servers.

The CS5305 meets VRM 9.x specifications with its Power Good, Enable, Differential Remote Sense, and single-wire Current Share features. The product fits server and workstation VRMs, and can be used to power Embedded Processors. The IC provides the simplest, lowest-cost solution for any low voltage, high current power supply.

# Features

- Enhanced V<sup>2</sup> Control Method

- VRM 9.x Compatible VID Codes

- Lossless Inductor Current Sensing

- Single Wire Active Current Sharing Between Converters

- Auto Master-Slave Current Share Control Method

- Programmable 200 to 800 kHz Switching Frequency

- Programmable Adaptive Voltage Positioning

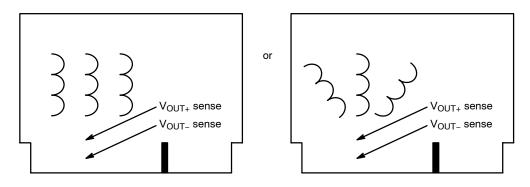

- Differential Remote Sense

- Pulse-by-Pulse Current Limit

- Master Hiccup Overcurrent Protection through Single Wire Share Bus

- 5-Bit DAC with 1% Tolerance

- ENABL Input

- VRM 9.x-Compliant Power Good Output

- Active Current Sharing During Soft Start

# **ON Semiconductor™**

http://onsemi.com

#

| R <sub>OSC</sub> ⊏   | GATE1                |

|----------------------|----------------------|

| ENABL 📼              | GATE2                |

| CS1 🞞                | 🖽 GATE3              |

| CS2 🞞                | DRVON                |

| CS3 📼                | III V <sub>CC</sub>  |

| CS <sub>REF</sub> ा⊏ | 🖽 SGND               |

| I <sub>FB</sub> 📼    | PWRGDS               |

| I <sub>OUT</sub> 📼   | III V <sub>ID0</sub> |

| SHARE 📼              |                      |

| SCOMP 📼              | III V <sub>ID2</sub> |

| V <sub>DRP</sub> 📼   | 🖽 V <sub>ID3</sub>   |

| V <sub>FB</sub> 📼    | ⊐∎ V <sub>ID4</sub>  |

| COMP 📼               | 🖽 PWRGD              |

|                      |                      |

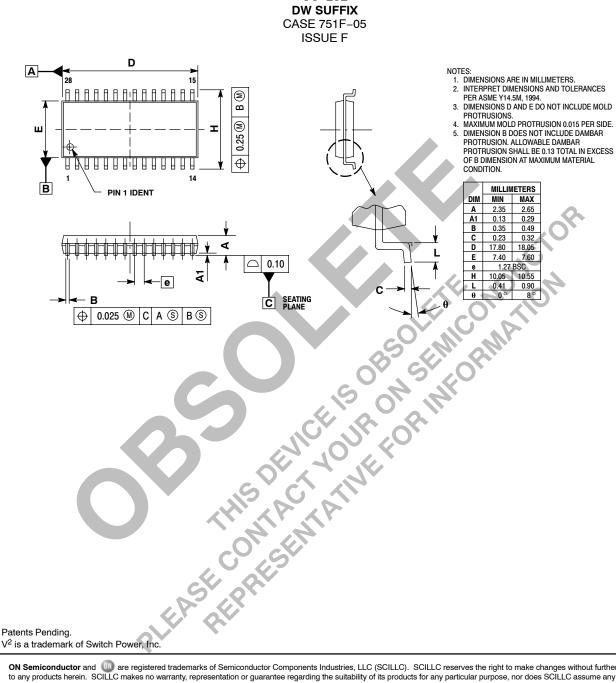

# **ORDERING INFORMATION**

| Device       | Package | Shipping         |

|--------------|---------|------------------|

| CS5305GDW28  | SO-28L  | 27 Units/Rail    |

| CS5305GDWR28 | SO-28L  | 1000 Tape & Reel |

#### **APPLICATION DIAGRAMS**

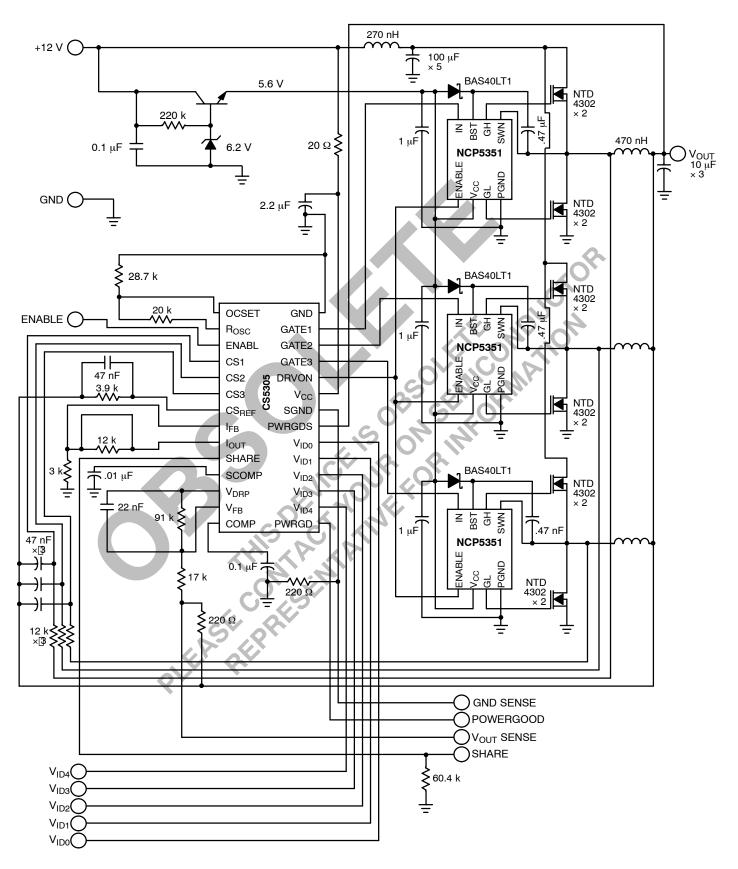

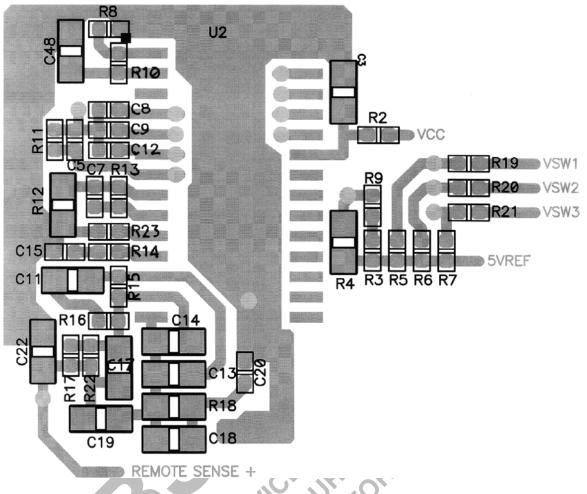

Figure 1. VRM 9.0, 60 A Converter

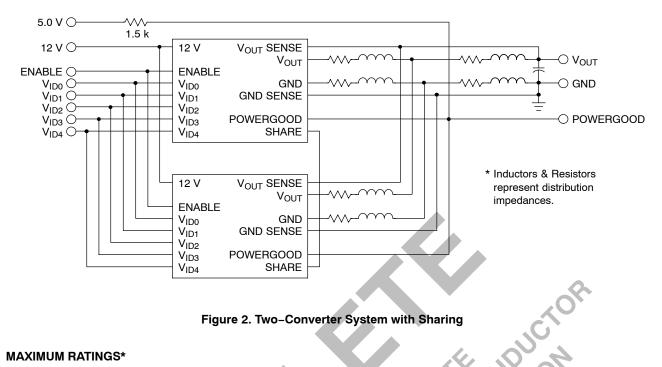

#### Figure 2. Two-Converter System with Sharing

#### **MAXIMUM RATINGS\***

|                                                          | Rating    |        | $\mathcal{O}$     | <u> </u>          | Value      | Unit |

|----------------------------------------------------------|-----------|--------|-------------------|-------------------|------------|------|

| Operating Junction Temperature                           |           |        | N.C               |                   | 150        | °C   |

| Storage Temperature Range                                |           | C      | O INI             | $\mathcal{O}_{H}$ | -65 to 150 | °C   |

| ESD Susceptibility (Human Body Model)                    |           | 00     | 5,0               |                   | 2.0        | kV   |

| Thermal Resistance, Junction-to-Case, $R_{\theta JC}$    |           | Sà     | 2 J               |                   | 15         | °C/W |

| Thermal Resistance, Junction-to-Ambient, $R_{\theta JA}$ |           |        | 0                 |                   | 75         | °C/W |

| JEDEC Moisture Sensitivity                               | ,,C       |        | 0                 |                   | Level 5    | -    |

| Lead Temperature Soldering:                              |           | Reflow | v: (SMD styles on | ly) Note 1.       | 230 peak   | °C   |

| . 60 second maximum above 183°C.                         | X O       |        |                   |                   |            |      |

| The maximum package power dissipation must be            | observed. | 11-    |                   |                   |            |      |

#### **MAXIMUM RATINGS**

| Pin Number | Pin Symbol        | VMAX  | V <sub>MIN</sub> | ISOURCE | I <sub>SINK</sub> |

|------------|-------------------|-------|------------------|---------|-------------------|

| 1          | OCSET             | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 2          | R <sub>osc</sub>  | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 3          | ENABL             | 16 V  | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 4–6        | CS1-3             | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 7          | CS <sub>REF</sub> | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 8          | I <sub>FB</sub>   | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 9          | I <sub>OUT</sub>  | 7.0 V | –0.3 V           | 10 mA   | 10 mA             |

| 10         | SHARE             | 16 V  | –0.3 V           | 50 mA   | 1.0 mA            |

| 11         | SCOMP             | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 12         | V <sub>DRP</sub>  | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 13         | V <sub>FB</sub>   | 7.0 V | –0.3 V           | 1.0 mA  | 1.0 mA            |

| 14         | COMP              | 7.0 V | –0.3 V           | 10 mA   | 1.0 mA            |

| 15         | PWRGD             | 16 V  | –0.3 V           | 1.0 mA  | 20 mA             |

#### MAXIMUM RATINGS (continued)

| Pin Number | Pin Symbol                         | V <sub>MAX</sub> | V <sub>MIN</sub> | ISOURCE                  | I <sub>SINK</sub>       |

|------------|------------------------------------|------------------|------------------|--------------------------|-------------------------|

| 16–20      | V <sub>ID4</sub> -V <sub>ID0</sub> | 16 V             | –0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 21         | PWRGDS                             | 7.0 V            | –0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 22         | SGND                               | 0.3 V            | –0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 23         | V <sub>CC</sub>                    | 16 V             | –0.3 V           | N/A                      | 0.4 A, 1.0 μs 100 mA DC |

| 24         | DRVON                              | 7.0 V            | –0.3 V           | 10 mA                    | 1.0 mA                  |

| 25–27      | GATE 3-1                           | 16 V             | –0.3 V           | 0.1 A, 1.0 μs; 25 mA DC  | 0.1 A, 1.0 μs 25 mA DC  |

| 28         | GND                                | N/A              | N/A              | 0.4 A, 1.0 μs; 100 mA DC | N/A                     |

**ELECTRICAL CHARACTERISTICS** (0°C <  $T_A$  < 70°C; 0°C <  $T_J$  < 125°C; 9.5 V < V<sub>CC</sub> < 14 V; C<sub>GATEX</sub> = 100 pF, C<sub>COMP</sub> = 0.01 $\mu$ F, C<sub>VCC</sub> = 0.1 $\mu$ F, R<sub>ROSC</sub> = 32.4 k $\Omega$ , R<sub>SHARE</sub> = 60.4 k $\Omega$ , V(OCSET) = 0.54 V, DAC Code 01110; unless strained by otherwise stated.)

|                  | Pa                                        | Parameter        |                  |                                                              | Test Conditions                          | Min                  | Тур               | Max              | Unit      |

|------------------|-------------------------------------------|------------------|------------------|--------------------------------------------------------------|------------------------------------------|----------------------|-------------------|------------------|-----------|

| Volta            | ge Iden                                   | tificatio        | on DAC           | C (0 = C                                                     | onnected to GND, 1 = Open (Pulled-u      | up to internal 3.3 V | ) or Pulled–up to | external voltage | e ≤ 13 V) |

|                  | Accuracy (all codes)<br>VID code – 125 mV |                  |                  | Connect VFB to COMP,<br>SGND < 55 mV,<br>Measure COMP – SGND |                                          | 4.0                  | ±[].0             | %                |           |

| $V_{\text{ID4}}$ | V <sub>ID3</sub>                          | $V_{\text{ID2}}$ | $V_{\text{ID1}}$ | $V_{\text{ID0}}$                                             | V <sub>ID</sub> Maximum Voltage          |                      |                   | 0                |           |

| 1                | 1                                         | 1                | 1                | 1                                                            | DRVON < 1.0 V, GATE <sub>X</sub> < 1.0 V |                      | FAULT Mode        |                  | V         |

| 1                | 1                                         | 1                | 1                | 0                                                            | 1.100                                    | 0.965                | 0.975             | 0.985            | V         |

| 1                | 1                                         | 1                | 0                | 1                                                            | 1.125                                    | 0.990                | 1.000             | 1.010            | V         |

| 1                | 1                                         | 1                | 0                | 0                                                            | 1.150                                    | 1.015                | 1.025             | 1.035            | V         |

| 1                | 1                                         | 0                | 1                | 1                                                            | 1.175                                    | 1.040                | 1.050             | 1.061            | V         |

| 1                | 1                                         | 0                | 1                | 0                                                            | 1.200                                    | 1.064                | 1.075             | 1.086            | V         |

| 1                | 1                                         | 0                | 0                | 1                                                            | 1.225                                    | 1.089                | 1.100             | 1.111            | V         |

| 1                | 1                                         | 0                | 0                | 0                                                            | 1.250                                    | 1.114                | 1.125             | 1.136            | V         |

| 1                | 0                                         | 1                | 1                | 1                                                            | 1,275                                    | 1.139                | 1.150             | 1.162            | V         |

| 1                | 0                                         | 1                | 1                | 0                                                            | 1.300                                    | 1.163                | 1.175             | 1.187            | V         |

| 1                | 0                                         | 1                | 0                | 1                                                            | 1.325                                    | 1.188                | 1.200             | 1.212            | V         |

| 1                | 0                                         | 1                | 0                | 0                                                            | 1.350                                    | 1.213                | 1.225             | 1.237            | V         |

| 1                | 0                                         | 0                | 1                | 1                                                            | 1.375                                    | 1.238                | 1.250             | 1.263            | V         |

| 1                | 0                                         | 0                | 1                | 0                                                            | 1.400                                    | 1.263                | 1.275             | 1.288            | V         |

| 1                | 0                                         | 0                | 0                | 1                                                            | 1.425                                    | 1.287                | 1.300             | 1.313            | V         |

| 1                | 0                                         | 0                | 0                | 0                                                            | 1.450                                    | 1.312                | 1.325             | 1.338            | V         |

| 0                | 1                                         | 1                | 1                | 1                                                            | 1.475                                    | 1.337                | 1.350             | 1.364            | V         |

| 0                | 1                                         | 1                | 1                | 0                                                            | 1.500                                    | 1.361                | 1.375             | 1.389            | V         |

| 0                | 1                                         | 1                | 0                | 1                                                            | 1.525                                    | 1.386                | 1.400             | 1.414            | V         |

| 0                | 1                                         | 1                | 0                | 0                                                            | 1.550                                    | 1.411                | 1.425             | 1.439            | V         |

| 0                | 1                                         | 0                | 1                | 1                                                            | 1.575                                    | 1.436                | 1.450             | 1.465            | V         |

| 0                | 1                                         | 0                | 1                | 0                                                            | 1.600                                    | 1.460                | 1.475             | 1.490            | V         |

| 0                | 1                                         | 0                | 0                | 1                                                            | 1.625                                    | 1.485                | 1.500             | 1.515            | V         |

| 0                | 1                                         | 0                | 0                | 0                                                            | 1.650                                    | 1.510                | 1.525             | 1.540            | V         |

**ELECTRICAL CHARACTERISTICS (continued)** (0°C <  $T_A$  < 70°C; 0°C <  $T_J$  < 125°C; 9.5 V <  $V_{CC}$  < 14 V;  $C_{GATEX}$  = 100 pF,  $C_{COMP}$  = 0.01µF,  $C_{SCOMP}$  = 0.01µF,  $C_{VCC}$  = 0.1µF,  $R_{ROSC}$  = 32.4 kΩ,  $R_{SHARE}$  = 60.4 kΩ, V(OCSET) = 0.54 V, DAC Code 01110; unless otherwise stated.)

| Parameter                         |                  |                  | Test Conditions  | Min      | Тур                                                         | Max                                                                                 | Unit                                  |                                                                            |         |

|-----------------------------------|------------------|------------------|------------------|----------|-------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------|---------|

| Voltage Identification DAC (0 = 0 |                  |                  | on DAC           | ; (0 = C | onnected to GND, 1 = Open (Pulled-                          | up to internal 3.3 V)                                                               | or Pulled-up to                       | external voltage                                                           | ≤ 13 V) |

| 0                                 | 0                | 1                | 1                | 1        | 1.675                                                       | 1.535                                                                               | 1.550                                 | 1.566                                                                      | V       |

| 0                                 | 0                | 1                | 1                | 0        | 1.700                                                       | 1.560                                                                               | 1.575                                 | 1.591                                                                      | V       |

| 0                                 | 0                | 1                | 0                | 1        | 1.725                                                       | 1.584                                                                               | 1.600                                 | 1.616                                                                      | V       |

| 0                                 | 0                | 1                | 0                | 0        | 1.750                                                       | 1.609                                                                               | 1.625                                 | 1.641                                                                      | V       |

| 0                                 | 0                | 0                | 1                | 1        | 1.775                                                       | 1.634                                                                               | 1.650                                 | 1.667                                                                      | V       |

| 0                                 | 0                | 0                | 1                | 0        | 1.800                                                       | 1.658                                                                               | 1.675                                 | 1.692                                                                      | V       |

| 0                                 | 0                | 0                | 0                | 1        | 1.825                                                       | 1.683                                                                               | 1.700                                 | 1.717                                                                      | V       |

| 0                                 | 0                | 0                | 0                | 0        | 1.850                                                       | 1.708                                                                               | 1.725                                 | 1.742                                                                      | V       |

| Input                             | Thresh           | nold             |                  |          | $V_{ID4}, V_{ID3}, V_{ID2}, V_{ID1}, V_{ID0}$               | 1.00                                                                                | 1.25                                  | 1.5                                                                        | V       |

| Input                             | : Pull–u         | p Resis          | stance           |          | $0 V < V_{ID4}, V_{ID3}, V_{ID2}, V_{ID1}, V_{ID0} < 3.3 V$ | 25                                                                                  | 50                                    | 100                                                                        | kΩ      |

| Pull-                             | up Volt          | age              |                  |          | 1.0 MΩ to GND                                               | 2.5                                                                                 | 2.7                                   | 3.0                                                                        | V       |

| SGN                               | D Bias           | Curren           | t                |          | SGND < 55 mV, All DAC Codes                                 | 10                                                                                  | 20                                    | 40                                                                         | μA      |

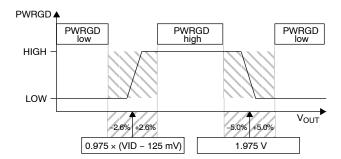

| Powe                              | r Good           | Outpu            | ıt               |          |                                                             |                                                                                     |                                       |                                                                            |         |

| Uppe                              | er Thres         | shold            |                  |          | Force PWRGDS-SGND<br>SGND < 55 mV                           | 1.876 (–5%)                                                                         | 1.975                                 | 2.074 (+5%)                                                                | V       |

| Lowe                              | er Thres         | shold            |                  |          | Force PWRQDS-SGND<br>SGND < 55 mV                           | 0.95 ×<br>(V <sub>ID</sub> – 125 mV)<br>or –2.6% from<br>nominal PWRGD<br>Threshold | 0,975 ×<br>(V <sub>ID</sub> – 125 mV) | V <sub>ID</sub> – 125 mV<br>or +2.6% from<br>nominal<br>PWRGD<br>Threshold | V       |

| V <sub>ID4</sub>                  | $V_{\text{ID3}}$ | $V_{\text{ID2}}$ | $V_{\text{ID1}}$ | VIDO     |                                                             |                                                                                     |                                       |                                                                            |         |

| 1                                 | 1                | 1                | -                | 0        |                                                             | 0.926                                                                               | 0.951                                 | 0.975                                                                      | V       |

| 1                                 | 1                | 1                | 0                | 1        | S C X                                                       | 0.950                                                                               | 0.975                                 | 1.000                                                                      | V       |

| 1                                 | 1                | 1                | 0                | 0        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                       | 0.974                                                                               | 1.000                                 | 1.025                                                                      | V       |

| 1                                 | 1                | 0                | 7                | 1        | 21 20                                                       | 0.998                                                                               | 1.024                                 | 1.050                                                                      | V       |

| 1                                 | 1                | 0                | 1                | 0        | . C , S                                                     | 1.021                                                                               | 1.048                                 | 1.075                                                                      | V       |

| 1                                 | 1                | 0                | 0                | 1        |                                                             | 1.045                                                                               | 1.073                                 | 1.100                                                                      | V       |

| 1                                 | 1                | 0                | 0                | 0        |                                                             | 1.069                                                                               | 1.097                                 | 1.125                                                                      | V       |

| 1                                 | 0                | 1                | 1                | 1        |                                                             | 1.093                                                                               | 1.122                                 | 1.150                                                                      | V       |

| 1                                 | 0                | 1                | 1                | 0        | <u>r</u>                                                    | 1.116                                                                               | 1.146                                 | 1.175                                                                      | V       |

| 1                                 | 0                | 1                | 0                | 1        |                                                             | 1.140                                                                               | 1.170                                 | 1.200                                                                      | V       |

| 1                                 | 0                | 1                | 0                | 0        |                                                             | 1.164                                                                               | 1.195                                 | 1.225                                                                      | V       |

| 1                                 | 0                | 0                | 1                | 1        |                                                             | 1.188                                                                               | 1.219                                 | 1.250                                                                      | V       |

| 1                                 | 0                | 0                | 1                | 0        |                                                             | 1.211                                                                               | 1.243                                 | 1.275                                                                      | V       |

| 1                                 | 0                | 0                | 0                | 1        |                                                             | 1.235                                                                               | 1.268                                 | 1.300                                                                      | V       |

| 1                                 | 0                | 0                | 0                | 0        |                                                             | 1.259                                                                               | 1.292                                 | 1.325                                                                      | V       |

| 0                                 | 1                | 1                | 1                | 1        |                                                             | 1.283                                                                               | 1.316                                 | 1.350                                                                      | V       |

| 0                                 | 1                | 1                | 1                | 0        |                                                             | 1.306                                                                               | 1.341                                 | 1.375                                                                      | V       |

**ELECTRICAL CHARACTERISTICS (continued)** (0°C <  $T_A$  < 70°C; 0°C <  $T_J$  < 125°C; 9.5 V <  $V_{CC}$  < 14 V;  $C_{GATEX}$  = 100 pF,  $C_{COMP}$  = 0.01 $\mu$ F,  $C_{VCC}$  = 0.1 $\mu$ F,  $R_{ROSC}$  = 32.4 k $\Omega$ ,  $R_{SHARE}$  = 60.4 k $\Omega$ , V(OCSET) = 0.54 V, DAC Code 01110; unless otherwise stated.)

|                                          | Pa       | aramet                  | er                    |         | Test Conditions                                                    | Min   | Тур   | Max   | Unit |

|------------------------------------------|----------|-------------------------|-----------------------|---------|--------------------------------------------------------------------|-------|-------|-------|------|

| Powe                                     | r Good   | Outpu                   | ıt                    |         |                                                                    |       |       |       |      |

| 0                                        | 1        | 1                       | 0                     | 1       |                                                                    | 1.330 | 1.365 | 1.400 | V    |

| 0                                        | 1        | 1                       | 0                     | 0       |                                                                    | 1.354 | 1.389 | 1.425 | V    |

| 0                                        | 1        | 0                       | 1                     | 1       |                                                                    | 1.378 | 1.414 | 1.450 | V    |

| 0                                        | 1        | 0                       | 1                     | 0       |                                                                    | 1.401 | 1.438 | 1.475 | V    |

| 0                                        | 1        | 0                       | 0                     | 1       |                                                                    | 1.425 | 1.463 | 1.500 | V    |

| 0                                        | 1        | 0                       | 0                     | 0       |                                                                    | 1.449 | 1.487 | 1.525 | V    |

| 0                                        | 0        | 1                       | 1                     | 1       |                                                                    | 1.473 | 1.511 | 1.550 | V    |

| 0                                        | 0        | 1                       | 1                     | 0       |                                                                    | 1.496 | 1.536 | 1.575 | V    |

| 0                                        | 0        | 1                       | 0                     | 1       |                                                                    | 1.520 | 1.560 | 1.600 | V    |

| 0                                        | 0        | 1                       | 0                     | 0       |                                                                    | 1.544 | 1.584 | 1.625 | V    |

| 0                                        | 0        | 0                       | 1                     | 1       |                                                                    | 1.568 | 1.609 | 1.650 | V    |

| 0                                        | 0        | 0                       | 1                     | 0       |                                                                    | 1.591 | 1.633 | 1.675 | V    |

| 0                                        | 0        | 0                       | 0                     | 1       |                                                                    | 1.615 | 1.658 | 1.700 | V    |

| 0                                        | 0        | 0                       | 0                     | 0       |                                                                    | 1.639 | 1.682 | 1.725 | V    |

| Switch Leakage Current                   |          |                         | urrent                |         | V <sub>CC</sub> = 14 V, PWRGDS = 1.4 V                             | 25 1  | 0     | 1.0   | μA   |

| Delay                                    |          |                         |                       |         | PWRGDS low to PWRGD low                                            | 50 50 | 250   | 600   | μs   |

| Outp                                     | out Low  | Voltage                 | e                     |         | PWRGDS = 1.0 V,<br>I <sub>PWRGOOD</sub> = 4.0 mA                   |       | 0.15  | 0.4   | V    |

| Volta                                    | ge Feed  | back                    | Error A               | mplifie | er CV.                                                             |       |       |       |      |

| $V_{FB}$                                 | Bias Cu  | irrent                  |                       |         | Note 2.                                                            | 9.5   | 10.3  | 11.5  | μA   |

| Com                                      | p Sourc  | ce Curr                 | ent                   |         | COMP = 0.5 V to 2.0 V,<br>V <sub>FB</sub> = 1.6 V                  | 15    | 30    | 60    | μΑ   |

| Com                                      | p Sink ( | Current                 |                       |         | COMP = 0.5 V to 2,0 V,<br>V <sub>FB</sub> = 1.0 V                  | 15    | 30    | 60    | μΑ   |

| Tran                                     | scondu   | ctance                  |                       |         | –10 μA < I <sub>COMP</sub> < +10 μA, Note 3.                       | -     | 32.0  | -     | mmho |

| Outp                                     | out Impe | edance                  |                       |         | Note 3.                                                            | _     | 2.5   | -     | mΩ   |

| Oper                                     | n Loop   | DC Ga                   | in                    |         | Note 3.                                                            | 60    | 95    | -     | dB   |

| Unity                                    | / Gain E | Bandwi                  | dth                   |         | COMP = 0.01 μF, Note 3.                                            | -     | 50    | -     | kHZ  |

| PSRR @ 1.0 kHz                           |          | ~                       | Note 3.               | -       | 70                                                                 | -     | dB    |       |      |

| COMP Max Voltage                         |          | X                       | V <sub>FB</sub> = 0 V | 2.4     | 2.7                                                                | -     | V     |       |      |

| COMP Min Voltage V <sub>FB</sub> = 1.6 V |          | V <sub>FB</sub> = 1.6 V | -                     | 0.1     | 0.2                                                                | V     |       |       |      |

| CON                                      | 1P Disc  | harge 7                 | Thresho               | old     | -                                                                  | 0.15  | 0.2   | 0.25  | V    |

| Hicc                                     | up Latcl | h Disch                 | arge C                | urrent  | CSx - CS <sub>REF</sub> = .05 V,<br>OCSET = 0.1 V,<br>COMP = 0.5 V | 2.0   | 5.0   | 10    | μΑ   |

| Hiccu                                    | up Char  | ge / Dis                | charge                | Ratio   | _                                                                  | 4.5   | 6.0   | 7.5   | _    |

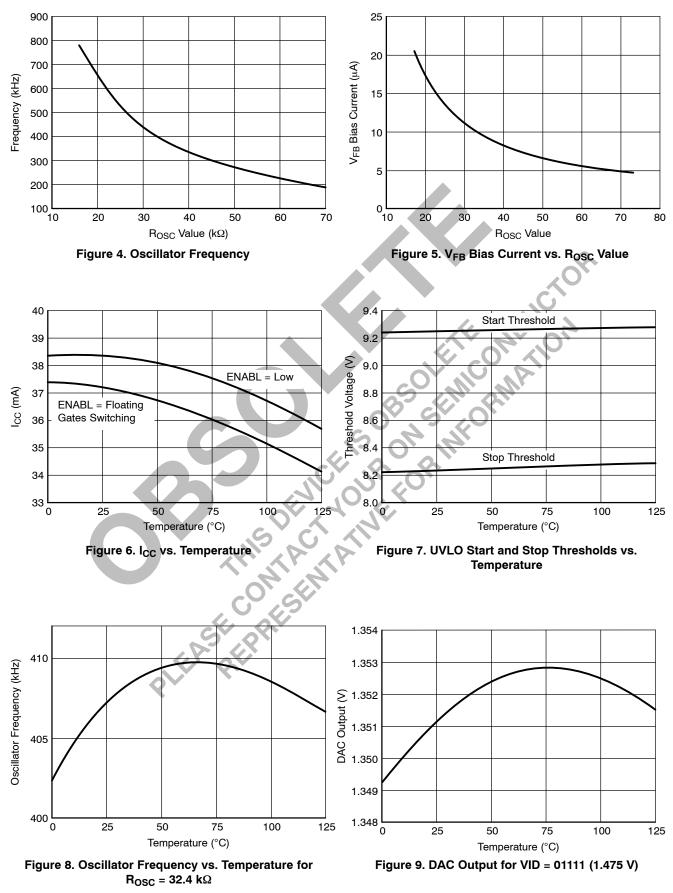

2. The  $V_{FB}$  Bias Current changes with the value of  $R_{OSC}$  per Figure 5.

**ELECTRICAL CHARACTERISTICS (continued)** (0°C <  $T_A$  < 70°C; 0°C <  $T_J$  < 125°C; 9.5 V <  $V_{CC}$  < 14 V;  $C_{GATEX}$  = 100 pF,  $C_{COMP}$  = 0.01µF,  $C_{SCOMP}$  = 0.01µF,  $C_{VCC}$  = 0.1µF,  $R_{ROSC}$  = 32.4 kΩ,  $R_{SHARE}$  = 60.4 kΩ, V(OCSET) = 0.54 V, DAC Code 01110; unless otherwise stated.)

| Parameter                           | Test Conditions                                                                                                                                                                                                       | Min  | Тур  | Max  | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Voltage Feedback Error Amplifie     | er                                                                                                                                                                                                                    |      |      |      |      |

| SHARE Fault Discharge Current       | SHARE = 3.5 V,<br>COMP = 0.5 V,<br>CSx = CS <sub>REF</sub> = 0 V,<br>OCSET = 0.5 V                                                                                                                                    | 0.3  | 2.5  | 5.0  | mA   |

| Enable Input                        |                                                                                                                                                                                                                       |      |      | •    |      |

| Threshold Voltage                   | Monitor DRVON                                                                                                                                                                                                         | 1.12 | 1.25 | 1.38 | V    |

| Pull-up Voltage                     | 1 M $\Omega$ to GND                                                                                                                                                                                                   | 2.5  | 2.7  | 3.0  | V    |

| Input Pull-up Resistance            | _                                                                                                                                                                                                                     | 25   | 50   | 100  | kΩ   |

| PWM Comparators                     |                                                                                                                                                                                                                       |      |      | L    |      |

| Minimum Pulse Width                 | Measured from CSx to GATEx,<br>$V_{FB} = CS_{REF} = 0.5 V$ ,<br>COMP = 0.5 V,<br>60 mV step on CSx;<br>measure at GATEx = 1.0 V                                                                                       |      | 75   | 220  | ns   |

| Transient Response Time             | $\begin{array}{l} \mbox{Measured from } CS_{REF} \mbox{ to GATEx}, \\ COMP = 2.1 \mbox{ V}, \\ CSx = CS_{REF} = 0.5 \mbox{ V}, \\ CS_{REF} \mbox{ stepped} \\ \mbox{from } 1.2 \mbox{ V} - 2.0 \mbox{ V} \end{array}$ | COL  |      | 150  | ns   |

| Channel Start-up Offset             | CSx = CS <sub>REF</sub> = V <sub>FB</sub> = 0 V,<br>measure V(COMP) when<br>GATEx switch high                                                                                                                         | 0.34 | 0,6  | 0.75 | V    |

| Channel Start-up Offset<br>Mismatch | CSx = CS <sub>REF</sub> = V <sub>FB</sub> = 0 V,<br>measure V(COMP) when<br>GATEx switch high, Note 4.                                                                                                                | -5.0 | _    | 5.0  | mV   |

| Gates                               |                                                                                                                                                                                                                       |      |      |      |      |

| High Voltage                        | I <sub>GATEx</sub> = 1.0 mA                                                                                                                                                                                           | 2.25 | 2.5  | 3.0  | V    |

| Low Voltage                         | I <sub>GATEx</sub> = 1.0 mA                                                                                                                                                                                           | _    | 0.2  | 0.4  | V    |

| Rise Time GATE                      | 0.8 V < GATE < 2.0 V,<br>V <sub>CC</sub> = 10 V                                                                                                                                                                       | _    | 15   | 30   | ns   |

| Fall Time GATE                      | 2.0 V > GATE > 0.8 V,<br>V <sub>CC</sub> = 10 V                                                                                                                                                                       | -    | 15   | 30   | ns   |

| Oscillator                          | 2.8                                                                                                                                                                                                                   |      |      |      |      |

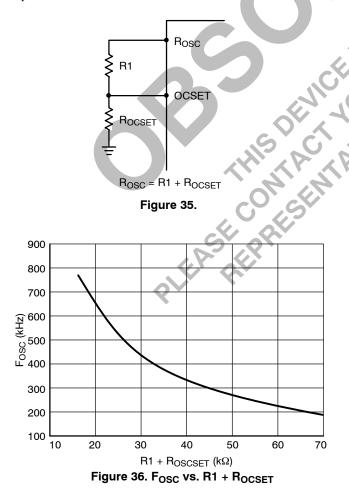

| Switching Frequency                 | R <sub>OSC</sub> = 32.4 kΩ                                                                                                                                                                                            | 300  | 400  | 500  | kHz  |

| Switching Frequency                 | R <sub>OSC</sub> = 63.4 kΩ, Note 4.                                                                                                                                                                                   | 150  | 200  | 250  | kHz  |

| Switching Frequency                 | $R_{OSC}$ = 16.2 k $\Omega$ , Note 4.                                                                                                                                                                                 | 600  | 800  | 1000 | kHz  |

| R <sub>OSC</sub> Voltage            | Note 4.                                                                                                                                                                                                               | 0.90 | 1.00 | 1.10 | V    |

| Phase Delay                         | _                                                                                                                                                                                                                     | 90   | 120  | 150  | deg  |

**ELECTRICAL CHARACTERISTICS (continued)** (0°C <  $T_A$  < 70°C; 0°C <  $T_J$  < 125°C; 9.5 V <  $V_{CC}$  < 14 V;  $C_{GATEX}$  = 100 pF,  $C_{COMP}$  = 0.01µF,  $C_{SCOMP}$  = 0.01µF,  $C_{VCC}$  = 0.1µF,  $R_{ROSC}$  = 32.4 kΩ,  $R_{SHARE}$  = 60.4 kΩ, V(OCSET) = 0.54 V, DAC Code 01110; unless otherwise stated.)

| Parameter                                                       | Test Conditions                                                                                                                                                                | Min  | Тур  | Max  | Unit   |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| Current Sense Amplifiers                                        |                                                                                                                                                                                |      |      |      |        |

| CS <sub>REF</sub> Input Bias Current                            | CS <sub>REF</sub> = CSx = 0 V                                                                                                                                                  | _    | 0.3  | 3.0  | μA     |

| CSx Input Bias Current                                          | CS <sub>REF</sub> = CSx = 0 V                                                                                                                                                  | -    | 0.1  | 1.0  | μΑ     |

| Sense Amp Gain                                                  | CS <sub>REF</sub> = 0 V, CSx = 0.05 V,<br>Measure V(COMP) when<br>GATEx switches high                                                                                          | .95  | 1.06 | 1.17 | V/V    |

| Mismatch                                                        | 0[]≤(CSx – CS <sub>REF</sub> )[]≤50 mV,<br>Note 5.                                                                                                                             | -3.0 | -    | 3.0  | mV     |

| Common Mode Input Range                                         | Note 5.                                                                                                                                                                        | 0    | -    | 2.0  | V      |

| Bandwidth                                                       | Note 5.                                                                                                                                                                        |      | 7.0  | -    | MHz    |

| Single Phase Pulse by Pulse<br>Current Limit                    | $\label{eq:VFB} \begin{array}{l} V_{FB} = CS_{REF} = 0.5 \text{ V},\\ COMP = 2.0 \text{ V}, \text{ Measure}\\ CSx - CS_{REF} \text{ when GATEx}\\ \text{goes low} \end{array}$ | 80   | 90   | 100  | mV     |

| OCSET Input Bias Current                                        | OCSET = 0 V                                                                                                                                                                    | -    | 0.1  | 1.0  | μA     |

| Current Sense Input to OCSET<br>Gain                            | OCSET / R (CSx – CS <sub>REF</sub> ),<br>OCSET = 0.6 V,<br>Monitor DRVON < 1.0 V                                                                                               | 3.4  | 3.7  | 4.0  | V / V  |

| Current Limit Filter Slew Rate                                  | CS <sub>REF</sub> = 1.1 V, CSx = 1.0 V,<br>pulse CSx to 1.16 V, Note 5.                                                                                                        | 2.0  | 5.0  | 13   | mV / μ |

| Adaptive Voltage Positioning                                    |                                                                                                                                                                                | 0    |      |      |        |

| V <sub>DRP</sub> Output Voltage to<br>DAC <sub>OUT</sub> Offset | CSx = CS <sub>REF</sub> , V <sub>FB</sub> = COMP,<br>Measure V <sub>DRP</sub> – COMP                                                                                           | -30  | 2.0  | 60   | mV     |

| Maximum V <sub>DRP</sub> Voltage                                | $CSx - CS_{REF} = 50 \text{ mV},$<br>$V_{FB} = COMP,$<br>Measure $V_{DRP} - COMP$                                                                                              | 500  | 560  | 620  | mV     |

| Current Sense Amp to V <sub>DRP</sub><br>Gain                   | $CSx - CS_{REF} = 50 \text{ mV},$<br>$V_{FB} = COMP,$<br>Measure $V_{DRP} - COMP$                                                                                              | 3.4  | 3.7  | 4.0  | V / V  |

| V <sub>DRP</sub> Source Current                                 | $\begin{array}{l} \text{CSx} - \text{CS}_{\text{REF}} = 50 \text{ mV}, \\ \text{V}_{\text{FB}} = \text{COMP}, \\ \text{V}_{\text{DRP}} = 1.5 \text{ V} \end{array}$            | 1.0  | 7.0  | 14   | mA     |

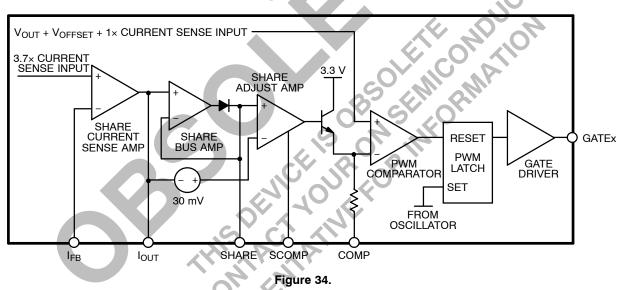

| SHARE Current Sense Amplifier                                   |                                                                                                                                                                                |      | L    |      |        |

| I <sub>FB</sub> Input Bias Current                              | I <sub>FB</sub> = 0 V                                                                                                                                                          | -    | 0.2  | 1.0  | μA     |

| Input Offset Voltage                                            | Note 5.                                                                                                                                                                        | -5.0 | 0    | 5.0  | mV     |

| Common Mode Input Range                                         | Note 5.                                                                                                                                                                        | 0    | _    | 2.0  | V      |

| Output Current                                                  | I <sub>OUT</sub> = 0 V, CSx = 0.667 V,<br>CS <sub>REF</sub> = 0.5 V                                                                                                            | 1.0  | 10   | 22   | mA     |

| Gain                                                            | Note 5.                                                                                                                                                                        | -    | 120  | -    | dB     |

| Output Unity Gain BW                                            | Note 5.                                                                                                                                                                        | _    | 5.0  | _    | MHz    |

**ELECTRICAL CHARACTERISTICS (continued)** (0°C <  $T_A$  < 70°C; 0°C <  $T_J$  < 125°C; 9.5 V <  $V_{CC}$  < 14 V;  $C_{GATEX}$  = 100 pF,  $C_{COMP}$  = 0.01µF,  $C_{SCOMP}$  = 0.01µF,  $C_{VCC}$  = 0.1µF,  $R_{ROSC}$  = 32.4 kΩ,  $R_{SHARE}$  = 60.4 kΩ, V(OCSET) = 0.54 V, DAC Code 01110; unless otherwise stated.)

| Parameter                                       | Test Conditions                                                                                                                                                                                                  | Min  | Тур  | Max  | Unit           |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------------|

| SHARE Bus                                       |                                                                                                                                                                                                                  |      |      | L    |                |

| SHARE Amplifier Offset Voltage                  | Measure V(SHARE) – V(I <sub>OUT</sub> ),<br>0 < I <sub>OUT</sub> < 2.0 V                                                                                                                                         | 20   | 40   | 60   | mV             |

| SHARE Amplifier Source<br>Current               | I <sub>OUT</sub> = 2.1 V, SHARE = 2.0 V                                                                                                                                                                          | 1.0  | 7.5  | 24   | mA             |

| SHARE Amplifier Max Voltage                     | $I_{OUT} = 3.5 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$                                                                                                                                                    | 2.65 | 2.80 | 3.20 | V              |

| SHARE Fault Threshold                           | DRVON < 1.0 V, $T_A = 25^{\circ}C$                                                                                                                                                                               | 3.2  | 3.4  | 3.7  | V              |

| SHARE OK Threshold                              | DRVON > 1.0 V                                                                                                                                                                                                    | 2.0  | 2.3  | 2.5  | V              |

| SHARE Fault Hysteresis                          | -                                                                                                                                                                                                                | 1.0  | 1.15 | 1.3  | V              |

| SHARE Fault Output Voltage                      | -                                                                                                                                                                                                                | 3.8  | 4.25 | 4.7  | V              |

| SHARE Fault Output Current                      | SHARE = 3.8 V                                                                                                                                                                                                    | 1.2  | 2.0  | 2.5  | mA             |

| SHARE Full Load Accuracy                        | $\label{eq:cs_res} \begin{array}{l} \text{CS}_{\text{REF}} = 0.5 \text{ V}, \text{ CSx} = 0.52 \text{ V}, \\ \text{I}_{\text{OUT}}  /  \text{FB Divider} = 22 \ \text{k}\Omega/3.0 \ \text{k}\Omega \end{array}$ | 1.7  | 1.95 | 2.2  | V              |

| SHARE Short Circuit Current                     | V(I <sub>OUT</sub> ) = 2.0 V, SHARE = GND                                                                                                                                                                        | 1.0  | 17   | 28   | mA             |

| SHARE Fault Short Circuit<br>Current            | CS <sub>REF</sub> = 0.5 V, CSx = 0.6 V                                                                                                                                                                           | 2.0  | 19   | 30   | mA             |

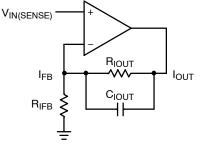

| Current SHARE Adjust Amplifie                   |                                                                                                                                                                                                                  | cO'. |      |      |                |

| Transconductance from I <sub>OUT</sub> to SCOMP | 0 < I <sub>OUT</sub> < 2.0 V,<br>0 < SCOMP < 2.0 V                                                                                                                                                               | 23   | 40   | 53   | μ <b>Α</b> / V |

| Gain from I <sub>OUT</sub> to COMP              | Note 6.                                                                                                                                                                                                          | 30   | 50   | 140  | mA / V         |

| Maximum SCOMP source<br>current                 | SCOMP = 1.5 V                                                                                                                                                                                                    | 15   | 30   | 60   | μΑ             |

| Maximum SCOMP sink current                      | SCOMP = 1.5 V                                                                                                                                                                                                    | 15   | 30   | 60   | μA             |

| Unity Gain BW                                   | C(SCOMP) = TBD, Note 6.                                                                                                                                                                                          | 30   | 56   | 100  | Hz             |

| MOSFET Driver Enable                            | 12 20.2                                                                                                                                                                                                          |      |      |      |                |

| Pull-Up Voltage                                 | DRVON Floating                                                                                                                                                                                                   | 4.5  | 5.5  | 6.0  | V              |

| DRVON Source Current                            | DRVON = 1.5 V                                                                                                                                                                                                    | .5   | 3.0  | 6.5  | mA             |

| DRVON Pull Down Resistor                        | DRVON = 1.5 V, ENABL = 0 V,<br>R = 1.5 V / I(1.5 V)                                                                                                                                                              | 35   | 70   | 140  | kΩ             |

| General Electrical Specification                |                                                                                                                                                                                                                  | •    |      |      | -!             |

| V <sub>CC</sub> Disable Current                 | ENABLE = 0 V (no switching)                                                                                                                                                                                      | -    | 30   | 60   | mA             |

| UVLO Start Threshold                            | COMP charging, DRVON > 1.0 V                                                                                                                                                                                     | 8.5  | 9.0  | 9.5  | V              |

| UVLO Stop Threshold                             | Gates not switching, COMP<br>discharging, DRVON < 1.0 V                                                                                                                                                          | 7.5  | 8.0  | 8.5  | V              |

| UVLO Hysteresis                                 | Start – Stop                                                                                                                                                                                                     | 0.8  | 1.0  | 1.2  | V              |

| V <sub>CC</sub> Operating Current               | ENABLE Open                                                                                                                                                                                                      | _    | 22   | 30   | mA             |

# PACKAGE PIN DESCRIPTION

| Package Pin Number |                                    |                                                 |                                                                                                                                                                                                    |  |

|--------------------|------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SO-28L             | Pin Symbol                         | Pin Name                                        | Function                                                                                                                                                                                           |  |

| 1                  | OCSET                              | Over-Current Set                                | Resistor divider from R <sub>OSC</sub> to GND programs the threshold of the hiccup over-current protection.                                                                                        |  |

| 2                  | R <sub>OSC</sub>                   | Oscillator Frequency<br>Adjust                  | Resistance to GND programs the oscillator frequency. It also programs the ${\rm V}_{\rm FB}$ bias current shown in Figure 5.                                                                       |  |

| 3                  | ENABL                              | Enable Input                                    | TTL–Compatible logic input with 50 k $\Omega$ internal pull–up resistor to 3.3 V. A logic low puts the IC in FAULT mode.                                                                           |  |

| 4-6                | CS1-3                              | Current Sense Inputs                            | Non-inverting inputs to the current sense amplifiers.                                                                                                                                              |  |

| 7                  | CS <sub>REF</sub>                  | Current Sense<br>Reference                      | Inverting input to the current sense amplifiers, and fast feedback input to the PWM comparator.                                                                                                    |  |

| 8                  | I <sub>FB</sub>                    | Share Current Amp<br>Inverting Input            | Inverting input to share current amp. Connect resistor divider between $I_{OUT},I_{FB}$ and IC GND pin 28 to program Share Current Amp gain.                                                       |  |

| 9                  | I <sub>OUT</sub>                   | Share Current Amp<br>Output                     | Share current amplifier output and input to share adjust amplifier.                                                                                                                                |  |

| 10                 | SHARE                              | Share Bus                                       | Connect with other modules for single-wire current sharing.                                                                                                                                        |  |

| 11                 | SCOMP                              | Share Compensation                              | Connect compensation network to stabilize share loop.                                                                                                                                              |  |

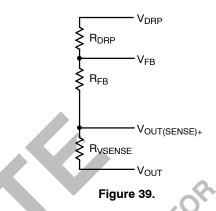

| 12                 | V <sub>DRP</sub>                   | Current Sense Output<br>for AVP                 | The offset of this pin above the DAC voltage is proportional to the output curren Connect a resistor from this pin to $V_{FB}$ to program the AVP voltage or leave this pin open for no AVP.       |  |

| 13                 | V <sub>FB</sub>                    | Voltage Feedback                                | Error Amp inverting input. Input bias current used to program AVP light load offset via resistor connected to converter output voltage. Short $V_{FB}$ to the converter output voltage for no AVP. |  |

| 14                 | СОМР                               | Error Amp Output and<br>PWM Comparator<br>Input | Provides loop compensation. Also used to control Softstart and Fault timing.                                                                                                                       |  |

| 15                 | PWRGD                              | Power Good Output                               | Open collector output goes low when V <sub>FB</sub> is out of regulation. User must externally limit current into this pin to less than 20 mA.                                                     |  |

| 16–20              | V <sub>ID4</sub> -V <sub>ID0</sub> | Voltage ID DAC<br>Inputs                        | Programs Output Voltage. 50 k $\Omega$ internal pull-up resistors to 3.3 V.                                                                                                                        |  |

| 21                 | PWRGDS                             | Power Good Sense                                | Provides remote output voltage sensing.                                                                                                                                                            |  |

| 22                 | SGND                               | Reference Ground                                | Ground connection for the DAC. Provides remote sensing of ground at the load                                                                                                                       |  |

| 23                 | V <sub>CC</sub>                    | Supply Input                                    | IC Power Supply Input.                                                                                                                                                                             |  |

| 24                 | DRVON                              | Driver Enable                                   | Logic High enables outputs of compatible MOSFET Driver ICs. Low turns all MOSFETs OFF. Pin driven from internal 5.5 V; 70 k $\Omega$ internal resistor to GND.                                     |  |

| 25–27              | GATE 3-1                           | FET Driver Outputs                              | PWM Signal Input to external MOSFET Gate Driver ICs.                                                                                                                                               |  |

| 28                 | GND                                | Ground                                          | IC Power Supply Return; connected to IC substrate.                                                                                                                                                 |  |

http://onsemi.com 11

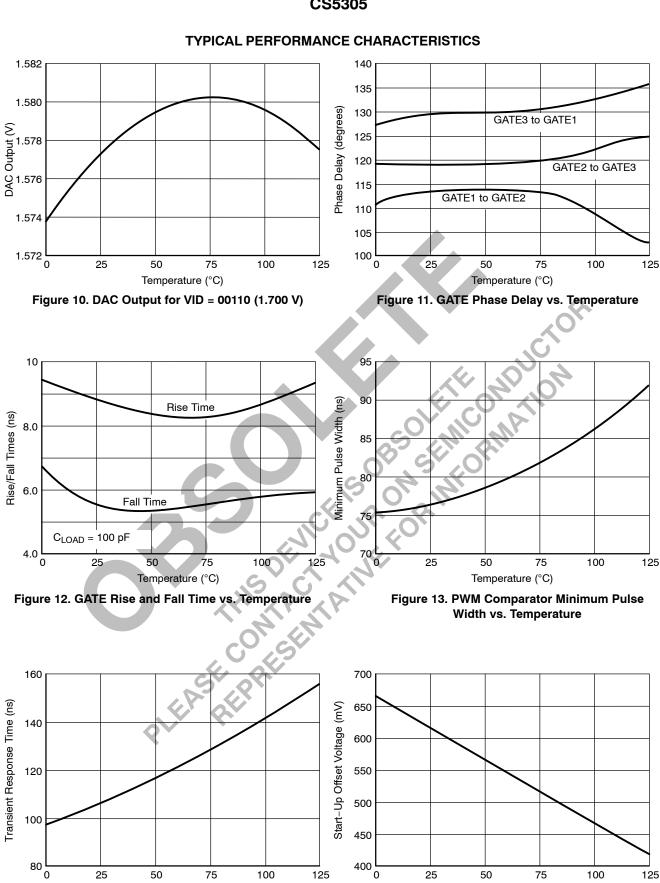

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

Rise/Fall Times (ns)

Transient Response Time (ns)

Temperature (°C) Figure 15. Current Sense Amp Channel Start-Up

**Offset Voltage vs. Temperature**

Temperature (°C)

Figure 14. PWM Transient Response Time vs. Temperature

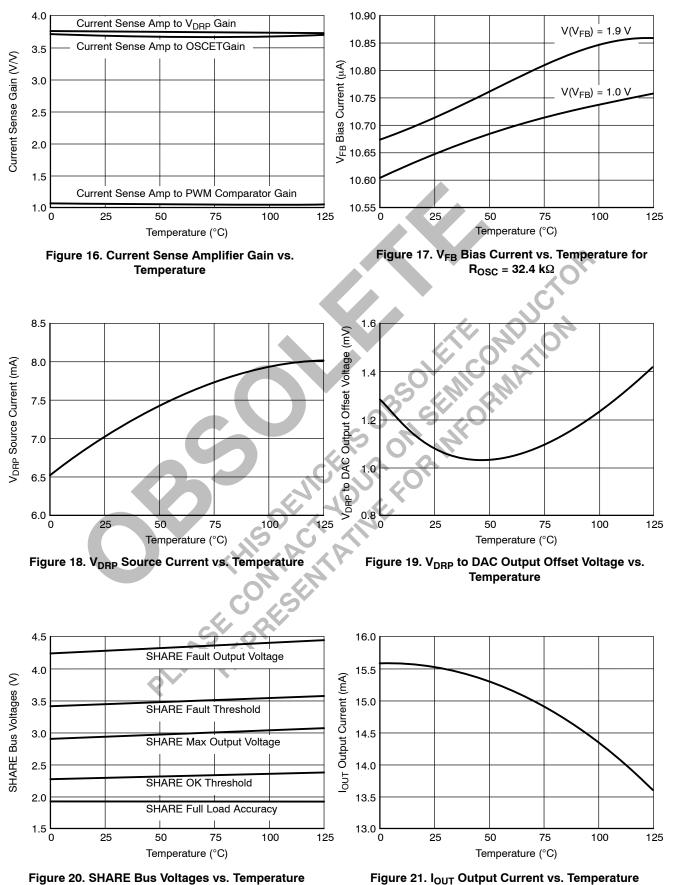

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

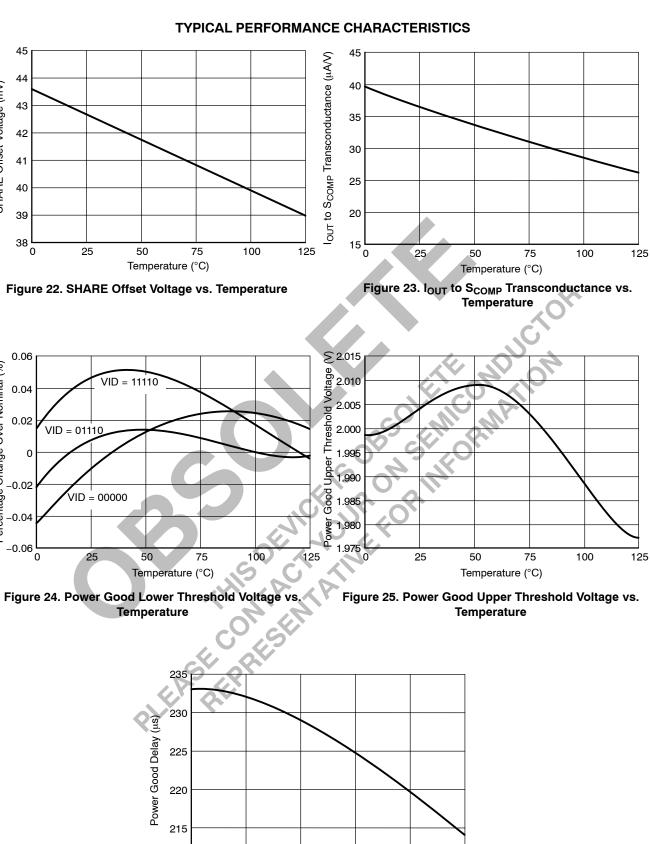

SHARE Offset Voltage (mV)

Percentage Change Over Nominal (%)

http://onsemi.com

Temperature (°C) Figure 26. Power Good Delay vs. Temperature

75

50

100

125

210

0

25

#### APPLICATIONS INFORMATION

#### THEORY OF OPERATION

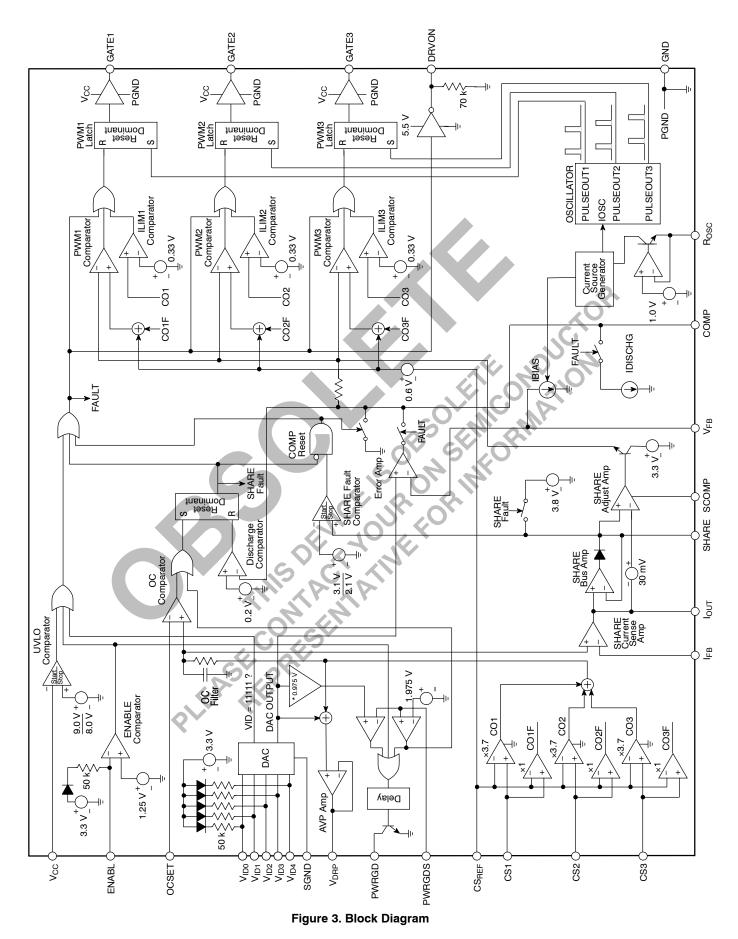

#### **Fixed Frequency Multi-phase Control**

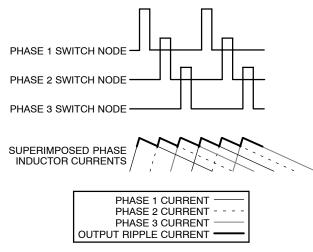

Multi-phase CPU controllers include the necessary control circuitry to implement several buck converters in parallel. These converters are configured to turn on at different times. This allows much higher output current than could be provided by a single converter. The apparent ripple frequency is increased and so output current can ramp up or down faster than a single converter with the same value of output inductor. Heat is also spread among multiple components.

The CS5305 uses a fixed frequency, Enhanced V<sup>2</sup> architecture. Each phase is delayed by approximately 120° from the previous phase. The GATE output for each channel changes to a logic high at the beginning of its oscillator cycle. Inductor current ramps up until the combination of the current sense signal and the output ripple trip the PWM comparator, at which time the GATE output changes to a logic low. Once low, the GATE output remains low until the next oscillator cycle begins, and the control loop will not respond until that time. The Enhanced V<sup>2</sup> control loop will respond to line and load transients while the GATE output is high. Enhanced V<sup>2</sup> control will respond within the off time of the converter.

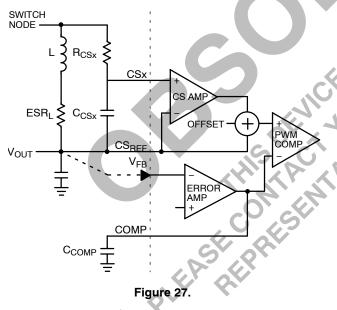

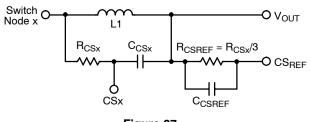

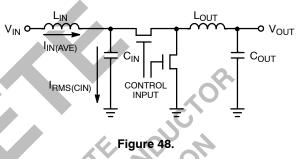

The Enhanced V<sup>2</sup> architecture measures and adjusts current in each phase. An additional input (CSx pin) provides current information for each output phase to the control loop as shown in Figure 27. Inductor current is measured across capacitor Ccsx. The voltage across this capacitor is equal to the product of the output current and the inductor ESR if these components are chosen such that (Ccsx)(Rcsx) = (L)/ESR<sub>L</sub>. This signal is buffered by the current sense amplifier (unity gain in the CS5305) and summed with an offset voltage before it is presented as input to non-inverting input of the PWM comparator. Inductor current provides the PWM ramp. As inductor current increases, the voltage at the positive input to the PWM comparator rises and terminates the PWM cycle. If the inductor starts the next cycle with higher current, the PWM cycle terminates earlier, thus providing negative feedback. A CSx input is provided for each channel, but the CS<sub>REF</sub>,  $V_{FB}$  and COMP inputs are common to all phases. Current sharing between phases is accomplished by referencing all phases to the same error amplifier. Any phase with a larger current signal will turn off earlier than the channels with a lower current signal.

Including both current and voltage information in the feedback signal allows the open loop output impedance of the power stage to be controlled. In the absence of any load current, the COMP pin voltage will be equal to the sum of the output voltage, the offset voltage and half of the steady–state ramp voltage. (At no load, the output ripple current's positive and negative contributions are equal, and the DC averaged voltage is equal to half the ripple voltage.) If the COMP pin is held steady and the inductor current is forced to change, the output voltage will also change. In a closed–loop situation, changing the inductor current will force the COMP voltage to change so the output voltage can remain the same. The change in COMP voltage depends on the scaling of the current feedback signal, and can be defined as:

$\Delta V_{COMP} = (ESR_L)(Current Sense Gain)(\Delta IPHASE)$ Since the current sense gain for this loop is unity, this equation reduces to:

#### $\Delta V_{COMP} = (ESR_L)(\Delta I_{PHASE})$

and so the single-phase power stage output impedance is:

#### $\Delta V_{COMP} / \Delta I_{PHASE} = ESR_{L}$

The CS5305 has three phases, so the total power stage output impedance is then  $\text{ESR}_{L}/3$ .

#### **Lossless Inductive Current Sensing**

Current can be sensed across the inductor as shown in Figure 27. The output inductor is designated L and the inductor's equivalent series resistance is designated ESR<sub>L</sub>. In the ideal case, the values of Rcsx and Ccsx are chosen such that  $(L/ESR_{I}) = (Rcsx)(Ccsx)$ . If this criterion is met, the current sense signal will have the same shape as the inductor current, and the circuit can be analyzed as if a sense resistor with value equal to ESRL was placed in series with the inductor. However, these components also determine the ramp signal that is used to prevent pulse skipping and duty cycle jitter. Choosing  $(Rcsx)(Ccsx) < (L/ESR_I)$  will result in the AC portion of the current sense signal being scaled more than the DC portion. This results in a larger ramp signal, but the current signal will overshoot during transients. This will affect transient response, adaptive voltage positioning and current limit. The COMP pin voltage will overshoot along with the current signal in order to maintain the output voltage. The COMP voltage will eventually find the correct level for regulation, but the error

will decay with the time constant (Rcsx)(Ccsx). The  $V_{DRP}$  voltage will also overshoot and response will be slowed, since the current signal is a component of that voltage. The single phase current limit will trip earlier since the current signal appears larger than it should be, and the module current limit will have a lower threshold for fast transients than it will for slow transients. Additional external components in the droop circuit and in the error amp compensation will correct this condition. Details are provided in the data sheet section on choosing external components.

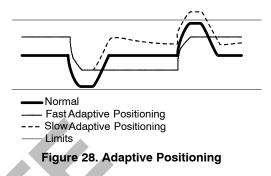

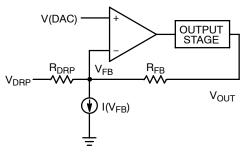

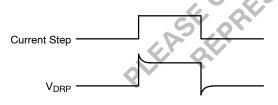

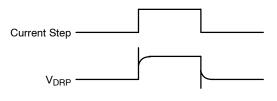

#### Adaptive Voltage Positioning

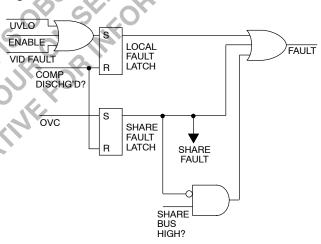

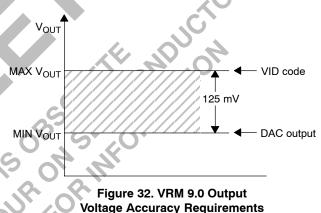

Adaptive voltage positioning is a technique used to reduce peak-to-peak output deviations during output current transients. The output voltage is set higher than nominal at light loads to reduce output voltage sag when load current is suddenly increased. Similarly, output voltage is set lower than nominal at heavy loads to reduce overshoot when load current suddenly decreases. The CS5305 implements adaptive voltage positioning by placing a resistor divider between V<sub>DRP</sub> and V<sub>OUT</sub>. The center tap of the divider connects to V<sub>FB</sub>. These resistors, along with two or three other external components, implement a lossless droop voltage function.