# Step Down Converter - AOT, Configurable

## 5.0 A

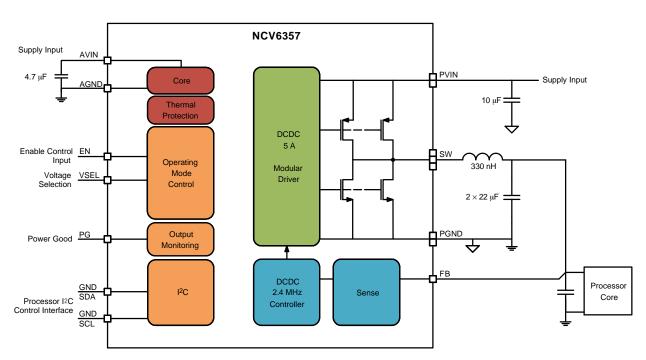

The NCV6357 is a synchronous AOT (Adaptive On–time) buck converter optimized to supply the different sub systems of automotive applications post regulation system up to 5 V input. The device is able to deliver up to 5.0 A, with programmable output voltage from 0.6 V to 3.3 V. Operation at up to 2.4 MHz switching frequency allows the use of small components. Synchronous rectification and automatic PFM Pseudo–PWM (PPWM) transitions improve overall solution efficiency. The NCV6357 is in low profile  $3.0 \times 4.0$  mm DFN–14 package.

#### **Features**

- Input Voltage Range from 2.5 V to 5.5 V: Battery, 3.3 V and 5.0 V Rail Powered Applications

- Power Capability:  $3.0 \text{ A T}_A = 105^{\circ}\text{C} 5.0 \text{ A T}_A = 85^{\circ}\text{C}$

- Programmable Output Voltage: 0.6 V to 3.3 V in 12.5 mV Steps

- Up to 2.4 MHz Switching Frequency with On Chip Oscillator

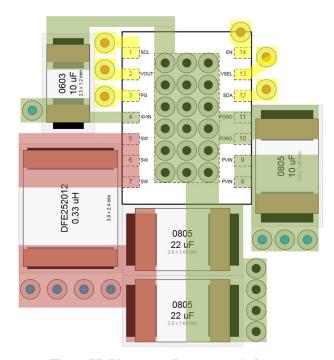

- Uses 330 nH Inductor and at Least 22 μF Capacitors for Optimized Footprint and Solution Thickness

- PFM/PPWM Operation for Optimum Efficiency

- Low 60 μA Quiescent Current

- I<sup>2</sup>C Control Interface with Interrupt and Dynamic Voltage Scaling Support

- Enable / VSEL Pins, Power Good / Interrupt Signaling

- Thermal Protections and Temperature Management

- Transient Load Helper: Share the Same Rail with another Rail

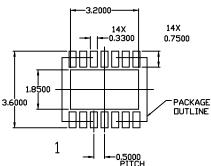

- $3.0 \times 4.0 \text{ mm} / 0.5 \text{ mm}$  Pitch DFN 14 Package

- AEC-Q100 Qualified and PPAP Capable

#### **Typical Applications**

- Snap Dragon

- Automotive POL

- Instrumentation, Clusters

- Infotainment

- ADAS System (Vision, Radar)

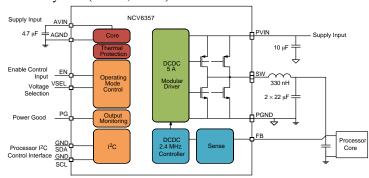

**Figure 1. Typical Application Circuit**

#### ON Semiconductor®

www.onsemi.com

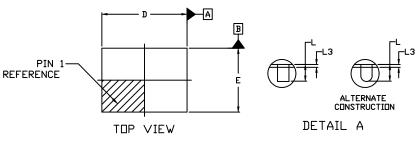

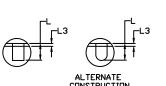

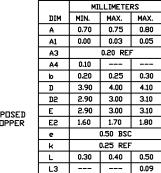

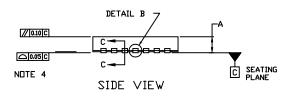

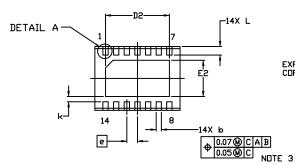

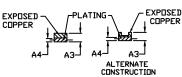

WDFNW14 4x3, 0.5P CASE 511CM

**MARKING**

6357 XX AYWW

XX = A: 1.80 V /1.10 V = B: 0.90 V / 1.00 V = C: 1.80 V /1.10 V = D: 1.25 V / 1.25 V = F: 1.00 V / 1.10 V A = Assembly Location Y = Year

WW = Work Week

■ = Pb–Free Package

(Note: Microdot may be in either location)

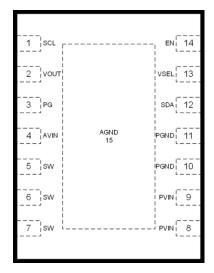

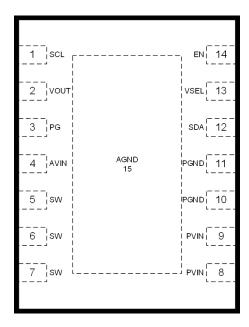

#### **PIN CONNECTIONS**

(Top View) 14– Pin 0.50 mm pitch DFN

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 32 of this data sheet.

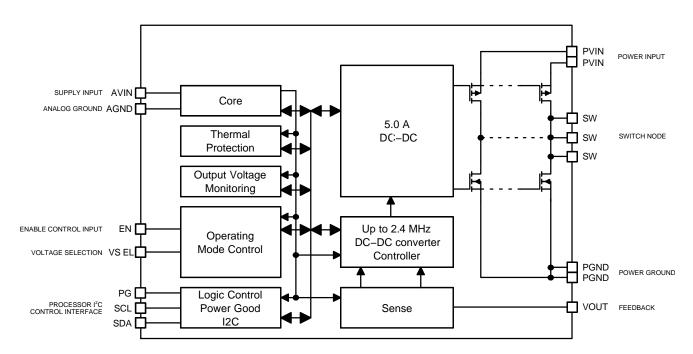

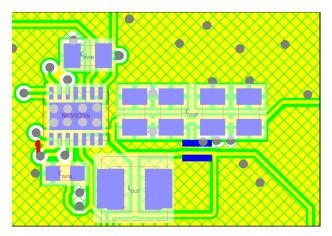

Figure 2. Simplified Block Diagram

Figure 3. Pin Out (Top View)

## PIN FUNCTION DESCRIPTION

| Pin        | Name          | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE  |               |                         |                                                                                                                                                                                                                                                                                                                                                                                |

| 4          | AVIN          | Analog Input            | Analog Supply. This pin is the device analog and digital supply. Could be connected directly to the VIN plane with a dedicated 4.7 $\mu$ F ceramic capacitor. Must be equal to PVIN                                                                                                                                                                                            |

| 15         | AGND          | Analog<br>Ground        | Analog Ground. Analog and digital modules ground. Must be connected to the system ground                                                                                                                                                                                                                                                                                       |

| CONTROL A  | ND SERIAL INT | ERFACE                  |                                                                                                                                                                                                                                                                                                                                                                                |

| 14         | EN            | Digital Input           | Enable Control. Active high will enable the part. There is an internal pull down resistor on this pin                                                                                                                                                                                                                                                                          |

| 13         | VSEL          | Digital Input           | Output voltage / Mode Selection. The level determines which of two programmable configurations to utilize (operating mode / output voltage). There is an internal pull down resistor on this pin; could be left open if not used                                                                                                                                               |

| 3          | PG            | Digital<br>Output       | Power Good Indicator open drain output. Must be connected to the ground plane if not used                                                                                                                                                                                                                                                                                      |

| 1          | SCL           | Digital Input           | I <sup>2</sup> C interface <b>Clock</b> line. There is an internal pull down resistor on this pin; could be left open if not used                                                                                                                                                                                                                                              |

| 12         | SDA           | Digital<br>Input/Output | I <sup>2</sup> C interface Bi–directional <b>Data</b> line. There is an internal pull down resistor on this pin; could be left open if not used                                                                                                                                                                                                                                |

| DC TO DC C | ONVERTER      |                         |                                                                                                                                                                                                                                                                                                                                                                                |

| 8, 9       | PVIN          | Power Input             | Switch Supply. These pins must be decoupled to ground by at least a 10 $\mu$ F ceramic capacitor. It should be placed as close as possible to these pins. All pins must be used with short heavy connections. Must be equal to AVIN                                                                                                                                            |

| 5, 6, 7    | SW            | Power<br>Output         | Switch Node. These pins supply drive power to the inductor. Typical application uses $0.33~\mu\text{H}$ inductor; refer to application section for more information. All pins must be used with short heavy connections                                                                                                                                                        |

| 10, 11     | PGND          | Power<br>Ground         | Switch Ground. This pin is the power ground and carries the high switching current. High quality ground must be provided to prevent noise spikes. To avoid high-density current flow in a limited PCB track, a local ground plane that connects all PGND pins together is recommended. Analog and power grounds should only be connected together in one location with a trace |

| 2          | VOUT          | Analog Input            | Feedback Voltage input. Must be connected to the output capacitor positive terminal with a trace, not to a plane. This is the positive input to the error amplifier                                                                                                                                                                                                            |

#### **MAXIMUM RATINGS**

| Rating                                                                                                                | Symbol                             | Value                             | Unit    |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|---------|

| Analog and power pins (Note 1):  AVIN, PVIN, SW, PG, VOUT, DC non switching  PVIN-PGND pins, transient 3 ns - 2.4 MHz | V <sub>A</sub>                     | - 0.3 to + 6.0<br>-0.3 to +7.5    | V       |

| I <sup>2</sup> C pins: SDA, SCL                                                                                       | V <sub>I</sub> <sup>2</sup> C      | - 0.3 to + 6.0                    | V       |

| Digital pins : EN, VSEL<br>Input Voltage<br>Input Current                                                             | V <sub>DG</sub><br>I <sub>DG</sub> | -0.3 to V <sub>A</sub> +0.3 ≤ 6.0 | V<br>mA |

| Human Body Model (HBM) ESD Rating (Note 2)                                                                            | ESD HBM                            | 2500                              | V       |

| Charged Device Model (CDM) ESD Rating (Note 2)                                                                        | ESD CDM                            | 2000                              | V       |

| Latch Up Current: (Note 3) Digital Pins All Other Pins                                                                | I <sub>LU</sub>                    | 100<br>100                        | mA      |

| Storage Temperature Range                                                                                             | T <sub>STG</sub>                   | - 65 to + 150                     | °C      |

| Maximum Junction Temperature                                                                                          | T <sub>JMAX</sub>                  | -40 to +150                       | °C      |

| Moisture Sensitivity (Note 4)                                                                                         | MSL                                | Level 1                           |         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- This device series contains ESD protection and passes the following ratings: Human Body Model (HBM) ±2.5 kV per JEDEC standard: JESD22 – A114. Charged Device Model (CDM) ±2.0 kV per JEDEC standard: JESD22–C101 Class IV

- 3. Latch up Current per JEDEC standard: JESD78 class II.

- 4. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

### **OPERATING CONDITIONS**

| Symbol                              | Parameter                                        | Conditions                                                  | Min  | Тур  | Max  | Unit |

|-------------------------------------|--------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| AV <sub>IN</sub> , PV <sub>IN</sub> | Power Supply                                     | $AV_{IN} = PV_{IN}$                                         | 2.5  |      | 5.5  | V    |

| TJ                                  | Junction Temperature Range (Note 6)              |                                                             | - 40 | 25   | +125 | °C   |

| $R_{\theta JA}$                     | Thermal Resistance Junction to Ambient (Note 7)  | DFN-14 on Demo-board                                        | _    | 30   | _    | °C/W |

| P <sub>D</sub>                      | Power Dissipation Rating (Note 8)                | $T_A \le 105^{\circ}C$ ,<br>$R_{\theta JA} = 30^{\circ}C/W$ | -    | 666  | -    | mW   |

|                                     |                                                  | $T_A \le 85^{\circ}C$<br>$R_{\theta JA} = 30^{\circ}C/W$    | -    | 1333 | -    | mW   |

|                                     |                                                  | $T_A = 65^{\circ}C$<br>$R_{\theta JA} = 30^{\circ}C/W$      | -    | 2000 | -    | mW   |

| L                                   | Inductor for DC to DC converter (Note 5)         |                                                             | 0.15 | 0.33 | 0.47 | μΗ   |

| Со                                  | Output Capacitor for DC to DC Converter (Note 5) |                                                             | 15   | -    | 200  | μF   |

| Cin                                 | Input Capacitor for DC to DC Converter (Note 5)  | Per 1.0 A of I <sub>OUT</sub>                               | 6.0  | 10.0 | _    | μF   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

- 5. Including de-ratings (Refer to the Application Information section of this document for further details)

- 6. The thermal shutdown set to 150°C (typical) avoids potential irreversible damage on the device due to power dissipation.

- 7. The R<sub>0JA</sub> is dependent of the PCB heat dissipation. Board used to drive this data was a NCV6357EVB board. It is a multilayer board with 1–once internal power and ground planes and 2–once copper traces on top and bottom of the board.

- 8. The maximum power dissipation (PD) is dependent on input voltage, maximum output current, pcb stack up and layout, and external components selected.

## **ELECTRICAL CHARACTERISTICS** (Note 9)

Min and Max Limits apply for  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , AVIN = PVIN = 3.3 V and default configuration, unless otherwise specified. Typical values are referenced to  $T_A = +25^{\circ}\text{C}$ , AVIN = PVIN = 3.3 V and default configuration, unless otherwise specified.

| Symbol               | Parameter                        | Conditions                                                                                                           | Min                      | Тур                      | Max                      | Unit |

|----------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| SUPPLY CUR           | RENT: PINS AVIN – PVINX          | •                                                                                                                    | 1                        |                          | 1                        |      |

| I <sub>Q-PPWM</sub>  | Operating quiescent current PPWM | DCDC active in Forced PPWM no load                                                                                   | _                        | 22                       | 25                       | mA   |

| I <sub>Q PFM</sub>   | Operating quiescent current PFM  | DCDC active in Auto mode no load – minimal switching                                                                 | -                        | 60                       | 90                       | μΑ   |

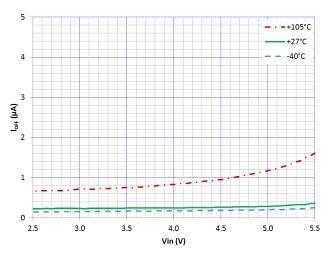

| I <sub>SLEEP</sub>   | Product sleep mode current       | Product in sleep mode<br>V <sub>IN</sub> = 5.5 V, T <sub>J</sub> up to 85°C                                          | _                        | 5                        | 10                       | μΑ   |

| I <sub>OFF</sub>     | Product in off mode              | EN, VSEL and Sleep_Mode low, No I <sup>2</sup> C pull up                                                             | _                        | 0.8                      | 3                        | μΑ   |

|                      |                                  | $V_{IN} = 5.5 \text{ V}, T_J \text{ up to } 85^{\circ}\text{C}$                                                      |                          |                          |                          |      |

| DC TO DC CC          | DNVERTER                         |                                                                                                                      | _                        |                          | _                        |      |

| $PV_{IN}$            | Input Voltage Range              |                                                                                                                      | 2.5                      | _                        | 5.5                      | V    |

| Іоит                 | Load Current Range               | (Note 11, 12)<br>lpeak[10] = 00<br>lpeak[10] = 01<br>lpeak[10] = 10<br>lpeak[10] = 11                                | 0<br>0<br>0<br>0         | -<br>-<br>-              | 3.5<br>4.0<br>4.5<br>5.0 | A    |

| $\Delta V_{OUT}$     | Output Voltage DC Error          | Forced PPWM mode, No                                                                                                 | -1.5                     | _                        | 1.5                      | %    |

| △,001                | Culput voltage DO Elloi          | load                                                                                                                 | -1.5                     |                          | 1.5                      | 70   |

|                      |                                  | Forced PPWM mode,<br>I <sub>OUT</sub> up to I <sub>OUTMAX</sub> (Note 11)                                            | -2                       | -                        | 2                        |      |

|                      |                                  | Auto mode,<br>I <sub>OUT</sub> up to I <sub>OUTMAX</sub> (Note 11)                                                   | -3                       | -                        | 2                        |      |

| F <sub>SW</sub>      | Switching Frequency              |                                                                                                                      | 2.16                     | 2.4                      | 2.64                     | MHz  |

| R <sub>ONHS</sub>    | P-Channel MOSFET On Resistance   | From PVIN to SW<br>V <sub>IN</sub> = 5.0 V                                                                           | _                        | 39                       | 60                       | mΩ   |

| R <sub>ONLS</sub>    | N-Channel MOSFET On Resistance   | From SW to PGND<br>V <sub>IN</sub> = 5.0 V                                                                           | _                        | 32                       | 45                       | mΩ   |

| I <sub>PK</sub>      | Peak Inductor Current            | Open loop - Ipeak[10] = 00<br>Open loop - Ipeak[10] = 01<br>Open loop - Ipeak[10] = 10<br>Open loop - Ipeak[10] = 11 | 4.6<br>5.2<br>5.6<br>6.2 | 5.2<br>5.8<br>6.2<br>6.8 | 5.8<br>6.4<br>6.8<br>7.4 | А    |

| I <sub>PKN</sub>     | Negative Current limit           |                                                                                                                      | _                        | 1.4                      | _                        | Α    |

| DC <sub>LOAD</sub>   | Load Regulation                  | I <sub>OUT</sub> from 0 A to I <sub>OUTMAX</sub><br>Forced PPWM mode                                                 | -                        | 5                        | _                        | mV   |

| DC <sub>LINE</sub>   | Line Regulation                  | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$<br>Forced PPWM mode                                       | _                        | 6                        | -                        | mV   |

| AC <sub>LOAD</sub>   | Transient Load Response          | $t_r = t_f = 100 \text{ ns}$<br>Load step 1.5 A                                                                      | -                        | ±20                      | -                        | mV   |

| AC <sub>LINE</sub>   | Transient Line Response          | $t_{r} = t_{f} = 10 \; \mu s$ Line step 3.0 V / 3.6 V                                                                | -                        | ±20                      | -                        | mV   |

| D                    | Maximum Duty Cycle               |                                                                                                                      | -                        | 100                      | -                        | %    |

| t <sub>START</sub>   | Turn on time                     | Time from EN transitions from Low to High to 90% of Output Voltage (DVS[10] = 00b), VOUT = 1.10 V                    | -                        | 100                      | 130                      | μs   |

| R <sub>DISDCDC</sub> | DCDC Active Output Discharge     | V <sub>OUT</sub> = 1.10 V                                                                                            | _                        | 12                       | 25                       | Ω    |

| บนอบตบต              | _ 555 / tours Output Disoriaryo  | *UU1 =u v                                                                                                            | 1                        | l '-                     |                          |      |

#### **ELECTRICAL CHARACTERISTICS** (Note 9)

Min and Max Limits apply for  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , AVIN = PVIN = 3.3 V and default configuration, unless otherwise specified. Typical values are referenced to  $T_A = +25^{\circ}C$ , AVIN = PVIN = 3.3 V and default configuration, unless otherwise specified.

| Symbol                           | Parameter                                      | Conditions                                             | Min      | Тур  | Max     | Unit |

|----------------------------------|------------------------------------------------|--------------------------------------------------------|----------|------|---------|------|

| EN, VSEL                         |                                                | •                                                      |          |      | •       | •    |

| V <sub>IH</sub>                  | High input voltage                             |                                                        | 1.05     | _    | _       | V    |

| $V_{IL}$                         | Low input voltage                              |                                                        | _        | -    | 0.4     | V    |

| T <sub>FTR</sub>                 | Digital input X Filter                         | EN, VSEL rising and falling<br>DBN_Time = 01 (Note 11) | 0.5      | -    | 4.5     | μs   |

| I <sub>PD</sub>                  | Digital input X Pull–Down (input bias current) | For EN and VSEL pins                                   | -        | 0.05 | 1.00    | μΑ   |

| PG (OPTIONA                      | L)                                             | •                                                      | •        | •    |         |      |

| $V_{PGL}$                        | Power Good Threshold                           | Falling edge as a percentage of nominal output voltage | 86       | 90   | 94      | %    |

| V <sub>PGHYS</sub>               | Power Good Hysteresis                          |                                                        | 0        | 3    | 5       | %    |

| T <sub>RT</sub>                  | Power Good Reaction Time for DCDC              | Falling (Note 11)<br>Rising (Note 11)                  | -<br>3.5 | 1.0  | -<br>14 | μS   |

| V <sub>PGL</sub>                 | Power Good low output voltage                  | I <sub>PG</sub> = 5 mA                                 | _        | -    | 0.2     | V    |

| PG <sub>LK</sub>                 | Power Good leakage current                     | 3.3V at PG pin when power good valid                   | -        | -    | 100     | nA   |

| $V_{PGH}$                        | Power Good high output voltage                 | Open drain                                             | -        | -    | 5.5     | V    |

| I <sup>2</sup> C                 |                                                |                                                        | •        | •    |         |      |

| V <sub>I</sub> <sup>2</sup> CINT | High level at SCL/SCA line                     |                                                        | 1.7      | -    | 4.5     | V    |

| V <sub>I</sub> <sup>2</sup> CIL  | SCL, SDA low input voltage                     | SCL, SDA pin                                           | _        | -    | 0.4     | V    |

| V <sub>I</sub> <sup>2</sup> CIH  | SCL high input voltage                         | SCL pin (Note 10, 11)                                  | 1.6      | _    | _       | V    |

|                                  | SDA high input voltage                         | SDA pin (Note 10, 11)                                  | 1.2      | _    | _       |      |

| V <sub>I</sub> <sup>2</sup> COL  | SDA low output voltage                         | I <sub>SINK</sub> = 3 mA                               | _        | _    | 0.4     | V    |

| F <sub>SCL</sub>                 | I <sup>2</sup> C clock frequency               | (Note 11)                                              | _        | _    | 3.4     | MHz  |

| TOTAL DEVIC                      | E                                              |                                                        |          |      |         |      |

| V <sub>UVLO</sub>                | Under Voltage Lockout                          | V <sub>IN</sub> falling                                | _        | _    | 2.5     | V    |

| V <sub>UVLOH</sub>               | Under Voltage Lockout Hysteresis               | V <sub>IN</sub> rising                                 | 60       | -    | 200     | mV   |

| T <sub>SD</sub>                  | Thermal Shut Down Protection                   |                                                        | _        | 150  | _       | °C   |

| T <sub>WARNING</sub>             | Warning Rising Edge                            |                                                        | _        | 135  | _       | °C   |

| T <sub>PWTH</sub>                | Pre-Warning Threshold                          | I <sup>2</sup> C default value                         | _        | 105  | _       | °C   |

| T <sub>SDH</sub>                 | Thermal Shut Down Hysteresis                   |                                                        | -        | 30   | -       | °C   |

| T <sub>WARNINGH</sub>            | Thermal warning Hysteresis                     |                                                        | -        | 15   | -       | °C   |

| T <sub>PWTH H</sub>              | Thermal pre-warning Hysteresis                 |                                                        | -        | 6    | -       | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>9.</sup> Refer to the Application Information section of this data sheet for more details.

<sup>10.</sup> Devices that use non-standard supply voltages which do not conform to the intent I<sup>2</sup>C bus system levels must relate their input levels to the V<sub>DD</sub> voltage to which the pull-up resistors R<sub>P</sub> are connected.

<sup>11.</sup> Guaranteed by design and characterized.

<sup>12.</sup> Junction temperature must be maintained below 125°C. Output load current capability depends on the application thermal capability.

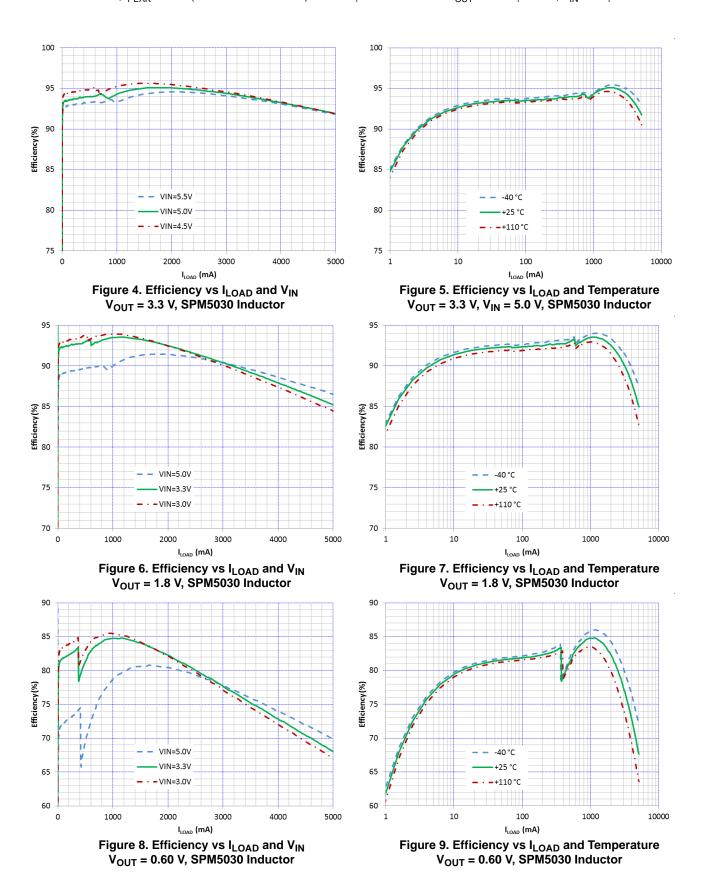

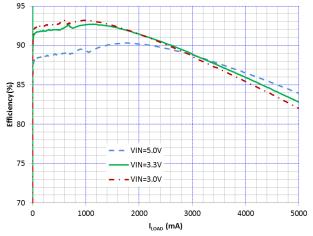

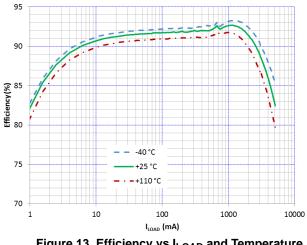

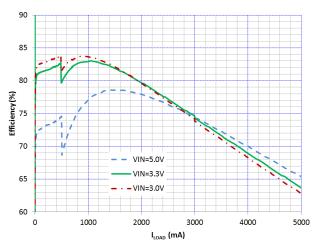

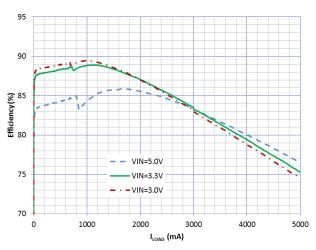

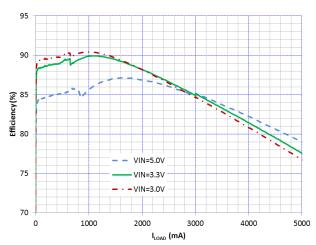

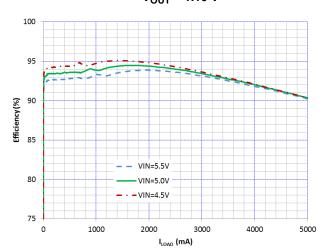

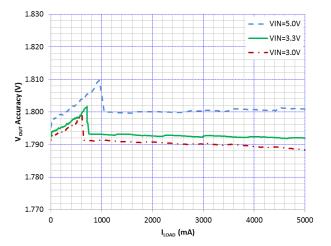

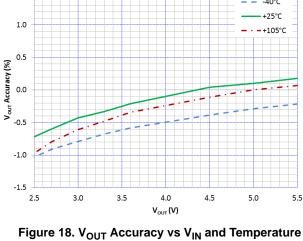

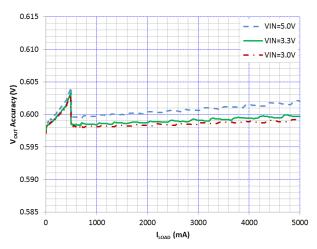

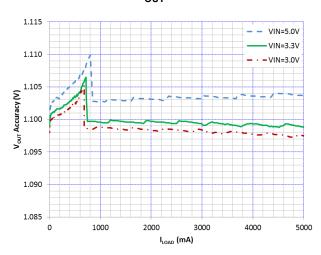

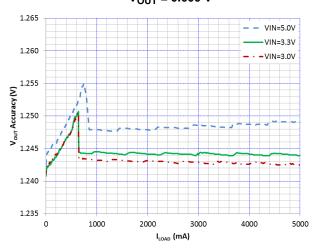

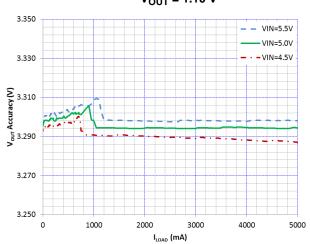

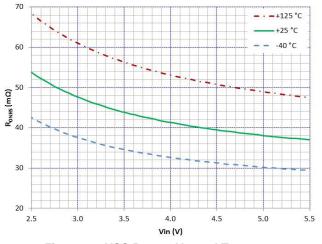

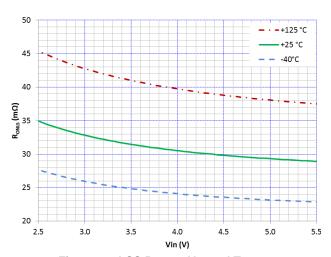

## TYPICAL OPERATING CHARACTERISTICS $AV_{IN} = PV_{IN} = 3.3 \text{ V}, T_J = +25^{\circ}\text{C}$

DCDC = 1.80 V,  $I_{PEAK}$  = 6.8 A (Unless otherwise noted). L = 0.33  $\mu$ H DFE252012F - C<sub>OUT</sub> = 2 x 22  $\mu$ F 0603, C<sub>IN</sub> = 4.7  $\mu$ F 0603.

Figure 10. Efficiency vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.80 V

Figure 13. Efficiency vs  $I_{\mbox{\scriptsize LOAD}}$  and Temperature  $V_{\mbox{\scriptsize OUT}}$  = 1.80 V

Figure 11. Efficiency vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 0.60 V

Figure 12. Efficiency vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.10 V

Figure 15. Efficiency vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.25 V

Figure 14. Efficiency vs  $I_{LOAD}$  and  $V_{IN}$  $V_{OUT}$  = 3.30 V

1.5

Figure 17.  $V_{OUT}$  Accuracy vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.80 V

Figure 18.  $V_{OUT}$  Accuracy vs  $V_{IN}$  and Temperature  $V_{OUT} = 1.80 \text{ V}$

Figure 20.  $V_{OUT}$  Accuracy vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 0.600 V

Figure 21.  $V_{OUT}$  Accuracy vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.10 V

Figure 19.  $V_{OUT}$  Accuracy vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.25 V

Figure 16.  $V_{OUT}$  Accuracy vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 3.3 V

Figure 22. HSS  $R_{ON}$  vs  $V_{IN}$  and Temperature

Figure 27. LSS R<sub>ON</sub> vs V<sub>IN</sub> and Temperature

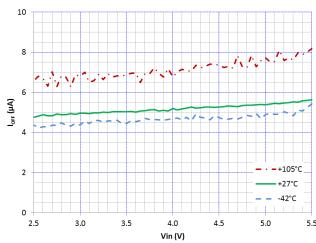

Figure 23.  $I_{\text{OFF}}$  vs  $V_{\text{IN}}$  and Temperature

Figure 24.  $\rm I_{SLEEP}$  vs  $\rm V_{IN}$  and Temperature

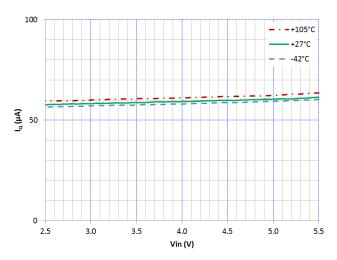

Figure 25.  $I_{Q PFM}$  vs  $V_{IN}$  and Temperature  $V_{OUT}$  = 1.25 V

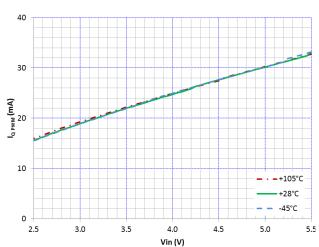

Figure 26.  $I_{Q\ PPWM}$  vs  $V_{IN}$  and Temperature  $V_{OUT}=1.25\ V$

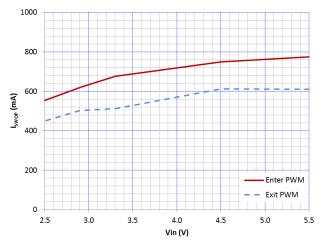

1000 800 600 Iswop (mA) 400 200 Enter PWM Exit PWM 0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 Vin (V)

Figure 28. Switchover Point V<sub>OUT</sub> = 1.15 V

Figure 29. Switchover Point V<sub>OUT</sub> = 1.4 V

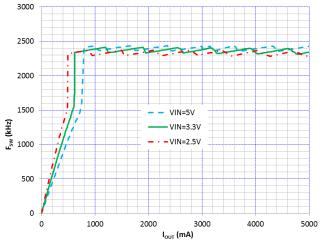

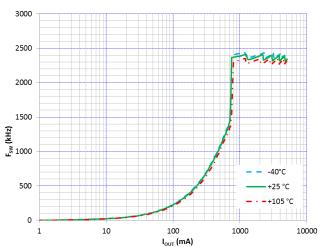

Figure 30. Switching Frequency vs  $I_{LOAD}$  and  $V_{IN}$   $V_{OUT}$  = 1.10 V

Figure 31. Switching Frequency vs  $I_{LOAD}$  and Temperature  $V_{OUT}$  = 1.10 V

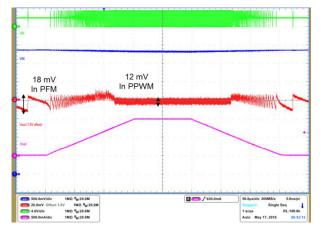

Figure 32. Ripple

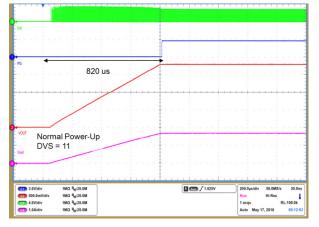

Figure 33. Normal Power Up,  $V_{OUT} = 1.15 \text{ V}$ DVS[1..0] = 00

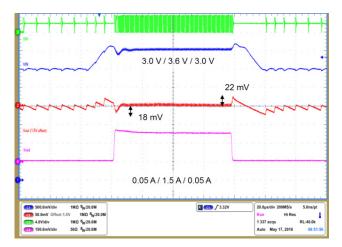

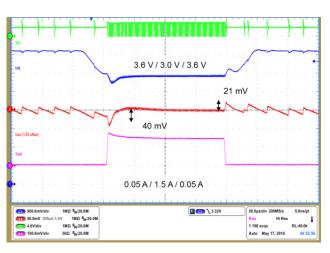

Figure 34. Transient load 0.05 to 1.5 A Transient line 3.0 – 3.6 V Auto mode

Figure 35. Transient load 0.05 to 1.5 A Transient line 3.6 – 3.0 V Auto mode

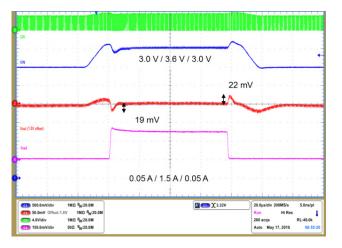

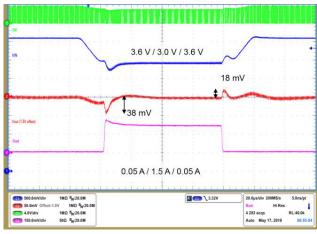

Figure 36. Transient load 0.05 to 1.5 A Transient line 3.0 – 3.6 V Forced PPW

Figure 37. Transient load 0.05 to 1.5 A Transient line 3.6 – 3.0 V Forced PPWM

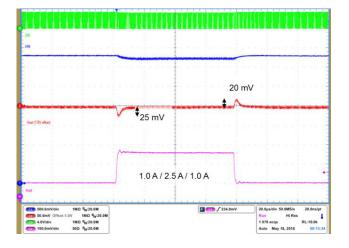

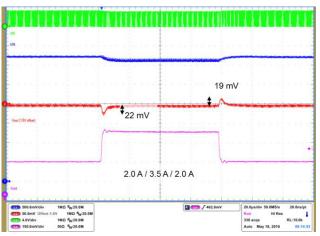

Figure 38. Transient load 1.0 to 2.5 A

Figure 39. Transient load 2.0 to 3.5 A

#### **DETAILED OPERATING DESCRIPTION**

## **Detailed Descriptions**

The NCV6357 is voltage mode stand—alone DC to DC converter optimized to supply different sub systems of automotive applications post regulation system up to 5 V input. It can deliver up to 5 A at an I<sup>2</sup>C selectable voltage ranging from 0.6 V to 3.3 V. The switching frequency up to 2.4 MHz allows the use of small output filter components. Power Good indicator and Interrupt management are available. Operating modes, configuration, and output power can be easily selected either by using digital I/O pins or by programming a set of registers using an I<sup>2</sup>C compatible interface capable of operation up to 3.4 MHz.

Default I<sup>2</sup>C settings are factory programmable.

## **DC to DC Converter Operation**

The converter integrates both high side and low side (synchronous) switches. Neither external transistors nor diodes are required for NCV6357 operation. Feedback and compensation network are also fully integrated.

It uses the AOT (Adaptive On–Time) control scheme and can operate in two different modes: PFM and PPWM (Pseudo–PWM). The transition between modes can occur automatically or the switcher can be placed in forced PPWM mode by I<sup>2</sup>C programming (PPWMVSEL0 / PPWMVSEL1 bits of COMMAND register).

## PPWM (Pseudo Pulse Width Modulation) Operating Mode

In medium and high load conditions, NCV6357 operates in PPWM mode to regulate the desired output voltage. In this mode, the inductor current is in CCM (Continuous Conduction Mode) and the AOT guaranties a pseudo–fixed frequency with 10% accuracy. The internal N–MOSFET switch operates as synchronous rectifier and is driven complementary to the P–MOSFET switch.

#### PFM (Pulse Frequency Modulation) Operating Mode

In order to save power and improve efficiency at low loads, the NCV6357 operates in PFM mode as the inductor current drops into DCM (Discontinuous Conduction Mode). The upper FET on–time is kept constant and the switching frequency becomes proportional to the loading current. As it does in PPWM mode, the internal N–MOSFET operates as a synchronous rectifier after each P–MOSFET on–pulse until there is no longer current in the coil.

When the load increases and the current in the inductor become continuous again, the controller automatically turns back to PPWM mode.

#### Forced PPWM

The NCV6357 can be programmed to only use PPWM and the transition to PFM can be disabled if so desired, thanks to the PPWMVSEL0 or PPWMVSEL1 I2C bits (COMMAND register).

#### **Output Stage**

NCV6357 is a 3.5 A to 5.0 A output current capable DC to DC converter with both high side and low side (synchronous) switches integrated.

#### **Inductor Peak Current Limitation / Short Protection**

During normal operation, peak current limitation monitors and limits the inductor current by checking the current in the P-MOSFET switch. When this current exceeds the Ipeak threshold, the P-MOSFET is immediately opened.

To protect again excessive load or short circuit, the number of consecutive Ipeak is counted. When the counter reaches 16, the DCDC is powered down during about 2 ms and the ISHORT interrupt is flagged. It will re–start following the REARM bit in the LIMCONF register:

- If REARM = 0, then NCV6357 does not re–start automatically, an EN pin toggle is required

- If REARM = 1, NCV6357 re-starts automatically after the 2 ms with register values set prior the fault condition

This current limitation is particularly useful to protect the inductor. The peak current can be set by writing IPEAK[1..0] bits in the LIMCONF register.

Table 1. IPEAK VALUES

| IPEAK[10] | Inductor Peak Current (A)    |

|-----------|------------------------------|

| 00        | 5.2 – for 3.5 output current |

| 01        | 5.8 – for 4.0 output current |

| 10        | 6.2 – for 4.5 output current |

| 11        | 6.8 – for 5.0 output current |

To protect the low side switch, the negative current protection limits potential excessive current from output.

## **Output Voltage**

The output voltage is set internally by an integrated resistor bridge and no extra components are needed to set the output voltage. Writing in the VoutVSEL0[7..0] bits of the PROGVSEL0 register or VoutVSEL1[7..0] bits of the PROGVSEL1 register will change the output voltage. The output voltage level can be programmed by 12.5 mV steps between 0.6 V to 3.3 V. The VSEL pin and VSELGT bit will determine which register between PROGVSEL0 and PROGVSEL1 will set the output voltage.

- If VSELGT = 1 AND VSEL = 0 → Output voltage is set by VoutVSEL0[7..0] bits (PROGVSEL0 register)

- Else → Output voltage is set by VoutVSEL1[7..0] bits (PROGVSEL1 register)

#### **Under Voltage Lock Out (UVLO)**

NCV6357 core does not operate for voltages below the Under Voltage Lock Out (UVLO) level. Below the UVLO threshold, all internal circuitry (both analog and digital) is held in reset. NCV6357 operation is guaranteed down to UVLO as the battery voltage is dropping off. To avoid erratic on / off behavior, a maximum 200 mV hysteresis is implemented. Restart is guaranteed at 2.7 V when the VBAT voltage is recovering or rising.

#### **Thermal Management**

Thermal Shut Down (TSD)

Battery monitoring for UVLO and Overvoltage Protectione thermal capability of the NCV6357 can be exceeded due to the step down converter output stage power level.. A thermal protection circuitry with associated interrupt is therefore implemented to prevent the IC from damage. This protection circuitry is only activated when the core is in active mode (output voltage is turned on). During thermal shut down, output voltage is turned off.

During thermal shut down, the output voltage is turned off.

When NCV6357 returns from thermal shutdown, it can re-start in 2 different configurations depending on the REARM bit in the LIMCONF register (refer to the register description section):

- If REARM = 0 then NCV6357 does not re–start after TSD. To restart, an EN pin toggle is required

- If REARM = 1, NCV6357 re-starts with register values set prior to thermal shutdown

The thermal shut down threshold is set at 150°C (typical) and a 30°C hysteresis is implemented in order to avoid erratic on / off behavior. After a typical 150°C thermal shut down, NCV6357 will resume to normal operation when the die temperature cools to 120°C.

## Thermal Warnings

In addition to the TSD, the die temperature monitoring circuitry includes a thermal warning and thermal pre-warning sensor and interrupts. These sensors can inform the processor that NCV6357 is close to its thermal shutdown and preventive measures to cool down die temperature can be taken by software.

The Warning threshold is set by hardware to 135°C typical. The Pre–Warning threshold is set by default to 105°C but it can be changed by setting the TPWTH[1..0] bits in the LIMCONF register.

## **Active Output Discharge**

To make sure that no residual voltage remains in the power supply rail when disabled, an active discharge path can ground the NCV6357 output voltage. For maximum flexibility, this feature can be easily disabled or enabled with the DISCHG bit in the PGOOD register. By default the

discharge path is enabled and is activated during the first 100 µs after battery insertion.

#### **Enabling**

The EN pin controls NCV6357 start up. EN pin Low to High transition starts the power up sequencer. If EN is low, the DC to DC converter is turned off and device enters:

- Sleep Mode if Sleep\_Mode I<sup>2</sup>C bit is high or VSEL is high or I<sup>2</sup>C pull up present

- Off Mode if Sleep\_Mode I<sup>2</sup>C bit and VSEL are low and no I<sup>2</sup>C pull up

When EN pin is set to a high level, the DC to DC converter can be enabled / disabled by writing the ENVSEL0 or ENVSEL1 bit of the COMMAND registers:

- Enx I<sup>2</sup>C bit is high, the DC to DC converter is activated.

- Enx I2C is low, the DC to DC converter is turned off and the device enters in Sleep Mode.

A built in pull down resistor disables the device when this pin is left unconnected or not driven. EN pin activity does not generate any digital reset.

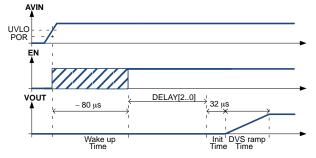

## Power Up Sequence (PUS)

In order to power up the circuit, the input voltage AVIN has to rise above the VUVLO threshold. This triggers the internal core circuitry power up which is the "Wake Up Time" (including "Bias Time").

This delay is internal and cannot be bypassed. EN pin transition within this delay corresponds to the "Initial power up sequence" (IPUS):

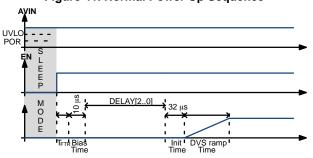

Figure 40. Initial Power Up Sequence

In addition a user programmable delay will also take place between the Wake Up Time and the Init time: The DELAY[2..0] bits of the TIME register will set this user programmable delay with a 2 ms resolution. With default delay of 0 ms, the NCV6357 IPUS takes roughly 100  $\mu$ s, and the DC to DC converter output voltage will be ready within 150  $\mu$ s.

The power up output voltage is defined by the VSEL state.

NOTE: During the Wake Up time, the I<sup>2</sup>C interface is not active. Any I<sup>2</sup>C request to the IC during this time period will result in a NACK reply.

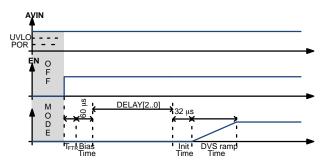

Normal, Quick and Fast Power Up Sequence

The previous description applies only when the EN transitions during the internal core circuitry power up (Wake up and calibration time). Otherwise 3 different cases are possible:

- Enabling the part by setting the EN pin from Off Mode will result in "Normal power up sequence" (NPUS, with DELAY;[2..0])

- Enabling the part by setting the EN pin from Sleep Mode will result in "Quick power up sequence" (QPUS, with DELAY;[2..0])

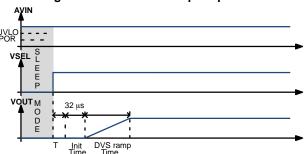

- Enabling the DC to DC converter, whereas EN is already high, either by setting the ENVSEL0 or ENVSEL1 bits or by VSEL pin transition will results in "Fast power up sequence" (FPUS, without DELAY[2..0])

Figure 41. Normal Power Up Sequence

Figure 42. Quick Power Up Sequence

Figure 43. Fast Power Up Sequence

In addition the delay set in DELAY[2..0] bits in TIME register will apply only for the EN pins turn ON sequence (NPUS and QPUS).

The power up output voltage is defined by VSEL state.

#### DC to DC Converter Shut Down

When shutting down the device, no shut down sequence is required. The output voltage is disabled and, depending on the DISCHG bit state of the PGOOD register, the output may be discharged.

DC to DC converter shutdown is initiated by either grounding the EN pin (Hardware Shutdown) or, depending on the VSEL internal signal level, by clearing the ENVSEL0 or ENVSEL1 bits (Software shutdown) in the PROGVSEL0 or PROGVSEL1 registers.

In hardware shutdown (EN = 0), the internal core is still active and  $I^2C$  accessible.

The internal core of the NCV6357 shuts down when AVIN falls below UVLO.

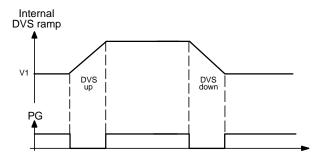

#### **Dynamic Voltage Scaling (DVS)**

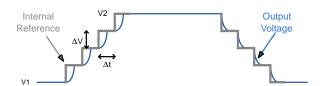

The NCV6357 supports dynamic voltage scaling (DVS) allowing the output voltage to be reprogrammed via I<sup>2</sup>C commands and provides the different voltages required by the processor. The change between set points is managed in a smooth fashion without disturbing the operation of the processor.

When programming a higher voltage, the output raises with controlled dV/dt defined by DVS[1..0] bits in the TIME register. When programming a lower voltage the output voltage will decrease accordingly. The DVS step is fixed and the speed is programmable.

The DVS sequence is automatically initiated by changing the output voltage settings. There are two ways to change these settings:

- Directly change the active setting register value (VoutVSEL0[7..0] of the PROGVSEL0 register or VoutVSEL1[7..0] of the PROGVSEL1 register) via an I<sup>2</sup>C command

- Change the VSEL internal signal level by toggling the VSEL pin

The second method eliminates the I<sup>2</sup>C latency and is therefore faster.

The DVS transition mode can be changed with the DVSMODE bit in the COMMAND register:

• In forced PPWM mode when accurate output voltage control is needed. Rise and fall time are controlled with the DVS[1..0] bits

Figure 44. DVS in Forced PPWM Mode Diagram

Figure 45. DVS in Auto Mode Diagram

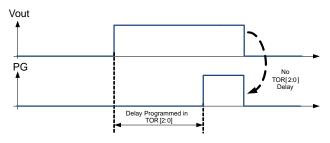

#### Power Good Pin

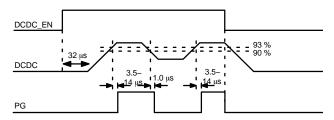

To indicate the output voltage level is established, a power good signal is available on PG pin. The power good signal is low when the DC to DC converter is off. Once the output voltage reaches 93% of the expected output level, the power good logic signal becomes high and the open drain output becomes high impedance.

During operation, when the output drops below 90% of the programmed level, the power good logic signal goes low, indicating a power failure. When the voltage rises again to above 93%, the power good signal goes high again.

During a DVS sequence, the Power Good signal is set low during the transition and goes back to high once the transition is completed.

The Power Good signal during normal operation can be disabled by clearing the PGDCDC bit in the PGOOD register.

The Power Good operation during DVS can be activated with PGDVS bit of the PGOOD register.

Figure 46. Power Good signal when PGDCDC = 1

Figure 47. Power Good during DVS Transition PGDVS = 1

### Power Good Delay

In order to generate a Reset signal, a delay can be programmed between when the output voltage gets 93% of its final value and when the Power Good pin is released to a high level.

Figure 48. Power Good Operation

#### **Digital IO Settings**

VSEL pin

By changing VSEL pin levels, the user has a latency free way to change NCV6357 configuration: operating mode (Auto or PWM forced), the output voltage as well as enable.

**Table 2. VSEL PIN PARAMETERS**

| Parameter VSEL<br>Pin Can Set             | REGISTER<br>VSEL = LOW | REGISTER<br>VSEL = HIGH |

|-------------------------------------------|------------------------|-------------------------|

| ENABLE                                    | ENVSEL0<br>COMMAND[3]  | ENVSEL1<br>COMMAND[2]   |

| VOUT                                      | VoutVSEL0[70]          | VoutVSEL1[70]           |

| OPERATING<br>MODE (Auto /<br>PPWM Forced) | PWMVSEL0<br>COMMAND[7] | PWMVSEL1<br>COMMAND[6]  |

VSEL pin action can be masked by writing 0 to the VSELGT bit in the COMMAND register. In that case I<sup>2</sup>C bit corresponding to VSEL high will be taken into account.

#### EN pin

The EN pin can be gated by writing the ENVSEL0 or ENVSEL1 bits of the COMMAND register, depending on which register is activated by the VSEL internal signal.

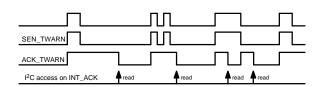

#### Interrupt (Optional)

The interrupt controller continuously monitors internal interrupt sources, generating an interrupt signal when a system status change is detected (dual edge monitoring).

**Table 3. INTERUPT SOURCES**

| Interrupt Name | Description                                      |

|----------------|--------------------------------------------------|

| TSD            | Thermal Shut Down                                |

| TWARN          | Thermal Warning                                  |

| TPREW          | Thermal Pre-Warning                              |

| UVLO           | Under Voltage Lock Out                           |

| IDCDC          | DC to DC converter Current<br>Over / below limit |

| ISHORT         | DC to DC converter<br>Short–Circuit Protection   |

| PG             | Power Good                                       |

Individual bits generating interrupts will be set to 1 in the INT\_ACK register (I<sup>2</sup>C read only registers), indicating the interrupt source. INT\_ACK register is automatically reset by an I<sup>2</sup>C read. The INT\_SEN register (read only register) contains real time indicators of interrupt sources.

When the host reads the INT\_ACK registers the interrupt register INT\_ACK is cleared.

Figure 49. TWARN Interrupt Operation Example

## Configurations

Default output voltages, enables, DCDC modes, current limit and other parameters can be factory programmed upon request. Below is the default configurations pre-defined:

**Table 4. NCV6357 CONFIGURATION**

| Configuration                                                                                                      | 5.0 A<br>NCV6357A                                | 5.0 A<br>NCV6357B                                | 5.0 A<br>NCV6357C                                | 5.0 A<br>NCV6357D                                | 5.0 A<br>NCV6357F                                |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Default I <sup>2</sup> C address PID product identification RID revision identification FID feature identification | ADD1 – 14h:<br>0010100R/W<br>21h<br>Metal<br>00h | ADD2 – 18h:<br>0011000R/W<br>21h<br>Metal<br>01h | ADD1 – 14h:<br>0010100R/W<br>21h<br>Metal<br>00h | ADD2 – 18h:<br>0011000R/W<br>21h<br>Metal<br>08h | ADD4 – 60h:<br>1100100R/W<br>21h<br>Metal<br>04h |

| Default VOUT - VSEL = 1                                                                                            | 1.10 V                                           | 1.00 V                                           | 1.10 V                                           | 1.25 V                                           | 1.1 V                                            |

| Default VOUT - VSEL = 0                                                                                            | 1.80 V                                           | 0.90 V                                           | 1.80 V                                           | 1.25 V                                           | 1.0 V                                            |

| Default MODE - VSEL = 1                                                                                            | Auto mode                                        | Forced PPWM                                      | Auto mode                                        | Auto mode                                        | Forced PPWM                                      |

| Default MODE – VSEL = 0                                                                                            | Forced PPWM                                      |

| Default IPEAK                                                                                                      | 6.8 A                                            |

| Discharge path                                                                                                     | Activated                                        | Activated                                        | Not Activated                                    | Activated                                        | Activated                                        |

| DVS                                                                                                                | 6.25 mV/2.666 μs                                 | 6.25 mV/0.666 μs                                 | 6.25 mV/2.666 μs                                 | 6.25 mV/0.666 μs                                 | 6.25 mV/0.666 μs                                 |

| OPN                                                                                                                | NCV6357MTWAT<br>XG                               | NCV6357MTWB<br>TXG                               | NCV6357MTWC<br>TXG                               | NCV6357MTWD<br>TXG                               | NCV6357MTWF<br>TXG                               |

| Marking                                                                                                            | 6357A                                            | 6357B                                            | 6357C                                            | 6357D                                            | 6357F                                            |

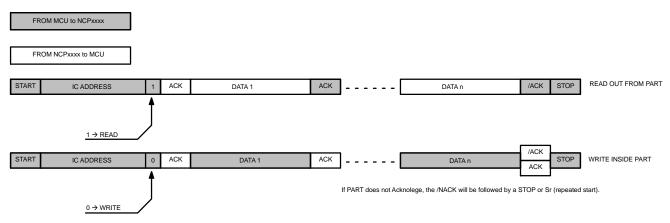

#### I<sup>2</sup>C Compatible Interface

NCV6357 can support a subset of the I<sup>2</sup>C protocol as detailed below.

## I<sup>2</sup>C Communication Description

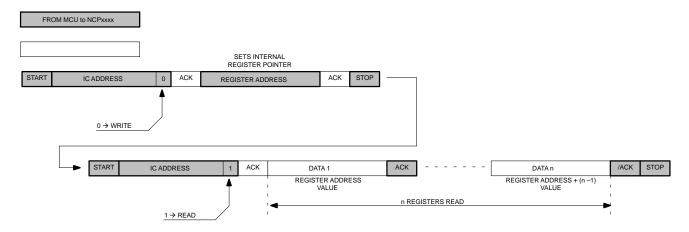

Figure 50. General Protocol Description

The first byte transmitted is the Chip address (with the LSB bit set to 1 for a read operation, or set to 0 for a Write operation). The following data will be:

- During a Write operation, the register address (@REG) is written in followed by the data. The writing process is auto-incremental, so the first data will be written in @REG, the contents of @REG are incremented and the next data byte is placed in the location pointed to by @REG + 1 ..., etc

- During a Read operation, the NCV6357 will output the data from the last register that has been accessed by the last write operation. Like the writing process, the reading process is auto-incremental.

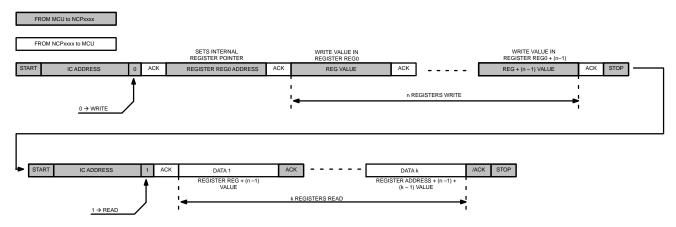

#### **Read Sequence**

The Master will first make a "Pseudo Write" transaction with no data to set the internal address register. Then, a stop then start or a Repeated Start will initiate the read transaction from the register address the initial write transaction has pointed to:

Figure 51. Read Sequence

The first WRITE sequence will set the internal pointer to the register that is selected. Then the read transaction will start at the address the write transaction has initiated.

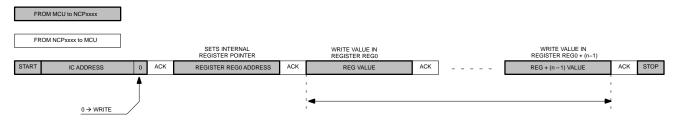

## **Write Sequence**

Write operation will be achieved by only one transaction. After chip address, the REG address has to be set, then following data will be the data we want to write in REG, REG + 1, REG + 2, ..., REG + n.

Write n Registers:

Figure 52. Write Sequence

## Write then Read Sequence

With Stop Then Start

Figure 53. Write Followed by Read Transaction

## I<sup>2</sup>C Address

The NCV6357 has 8 available  $I^2C$  addresses selectable by factory settings (ADD0 to ADD7). Different address settings can be generated upon request to ON Semiconductor. See Table 5 (NCV6357 Configuration) for the default  $I^2C$  address.

## Table 5. I2C ADDRESS

| I <sup>2</sup> C Address | Hex              | A7   | A6 | A5 | A4   | А3 | A2 | A1 | A0  |

|--------------------------|------------------|------|----|----|------|----|----|----|-----|

| ADD0                     | W 0x20<br>R 0x21 | 0    | 0  | 1  | 0    | 0  | 0  | 0  | R/W |

|                          | Add              |      | •  | •  | 0x10 |    | •  | 1  | _   |

| ADD1                     | W 0x28<br>R 0x29 | 0    | 0  | 1  | 0    | 1  | 0  | 0  | R/W |

|                          | Add              |      | •  |    | 0x14 |    | •  | •  | _   |

| ADD2                     | W 0x30<br>R 0x31 | 0    | 0  | 1  | 1    | 0  | 0  | 0  | R/W |

|                          | Add              |      | •  |    | 0x18 |    | •  | •  | -   |

| ADD3                     | W 0x38<br>R 0x39 | 0    | 0  | 1  | 1    | 1  | 0  | 0  | R/W |

|                          | Add              | 0x1C |    |    |      |    |    | _  |     |

| ADD4                     | W 0xC0<br>R 0xC1 | 1    | 1  | 0  | 0    | 0  | 0  | 0  | R/W |

|                          | Add              |      | •  |    | 0x60 |    | •  | •  | _   |

| ADD5                     | W 0xC8<br>R 0xC9 | 1    | 1  | 0  | 0    | 1  | 0  | 0  | R/W |

|                          | Add              |      | •  |    | 0x64 |    | •  | •  | _   |

| ADD6                     | W 0xD0<br>R 0xD1 | 1    | 1  | 0  | 1    | 0  | 0  | 0  | R/W |

|                          | Add              |      | •  | •  | 0x68 |    | •  | 1  | -   |

| ADD7                     | W 0xD8<br>R 0xD9 | 1    | 1  | 0  | 1    | 1  | 0  | 0  | R/W |

|                          | Add              |      | •  |    | 0x6C | •  |    | •  | _   |

## **Register Map**

The tables below describe the I<sup>2</sup>C registers.

Registers / Bits Operations:

R Read only register

RC Read then Clear

RW Read and Write register

Reserved Address is reserved and register / bit is not physically designed

## Table 6. I<sup>2</sup>C REGISTERS MAP CONFIGURATION (NCV6357A)

| Add.       | Register<br>Name | Туре | Def.  | Function                                            |

|------------|------------------|------|-------|-----------------------------------------------------|

| 00h        | INT_ACK          | RC   | 00h   | Interrupt register                                  |

| 01h        | INT_SEN          | R    | 01h   | Sense register (real time status)                   |

| 02h        | -                | -    | -     | Reserved for future use                             |

| 03h        | PID              | R    | 20h   | Product Identification                              |

| 04h        | RID              | R    | Metal | Revision Identification                             |

| 05h        | FID              | R    | 00h   | Features Identification (trim)                      |

| 06h to 11h | -                | -    | _     | Reserved for future use                             |

| 12h        | PGOOD            | RW   | 11h   | Power good and active discharge settings (trim)     |

| 13h        | TIME             | RW   | 19h   | Enabling and DVS timings (trim)                     |

| 14h        | COMMAND          | RW   | 8Dh   | Enabling and Operating mode Command register (trim) |

| 15h        | -                | -    | _     | Reserved for future use                             |

| 16h        | LIMCONF          | RW   | E3h   | Reset and limit configuration register (trim)       |

| 17h        | PROGVSEL1        | RW   | 28    | Output voltage settings for VSEL pin = High (trim)  |

| 18h        | PROGVSEL0        | RW   | 60    | Output voltage settings for VSEL pin = Low (trim)   |

| 19h to 26h | -                | -    | _     | Reserved for future use                             |

| 27h to FFh | -                | -    | -     | Reserved. Test Registers                            |

## Table 7. I<sup>2</sup>C REGISTERS MAP CONFIGURATION (NCV6357B)

| Add.       | Register<br>Name | Туре | Def.  | Function                                            |

|------------|------------------|------|-------|-----------------------------------------------------|

| 00h        | INT_ACK          | RC   | 00h   | Interrupt register                                  |

| 01h        | INT_SEN          | R    | 01h   | Sense register (real time status)                   |

| 02h        | -                | -    | -     | Reserved for future use                             |

| 03h        | PID              | R    | 20h   | Product Identification                              |

| 04h        | RID              | R    | Metal | Revision Identification                             |

| 05h        | FID              | R    | 00h   | Features Identification (trim)                      |

| 06h to 11h | -                | _    | _     | Reserved for future use                             |

| 12h        | PGOOD            | RW   | 11h   | Power good and active discharge settings (trim)     |

| 13h        | TIME             | RW   | 09h   | Enabling and DVS timings (trim)                     |

| 14h        | COMMAND          | RW   | CD    | Enabling and Operating mode Command register (trim) |

| 15h        | -                | -    | -     | Reserved for future use                             |

| 16h        | LIMCONF          | RW   | E3h   | Reset and limit configuration register (trim)       |

| 17h        | PROGVSEL1        | RW   | 20    | Output voltage settings for VSEL pin = High (trim)  |

| 18h        | PROGVSEL0        | RW   | 18    | Output voltage settings for VSEL pin = Low (trim)   |

| 19h to 26h | -                | -    | _     | Reserved for future use                             |

| 27h to FFh | -                | -    | -     | Reserved. Test Registers                            |

Table 8. I<sup>2</sup>C REGISTERS MAP CONFIGURATION (NCV6357C)

| Add.       | Register<br>Name | Туре | Def.  | Function                                            |

|------------|------------------|------|-------|-----------------------------------------------------|

| 00h        | INT_ACK          | RC   | 00h   | Interrupt register                                  |

| 01h        | INT_SEN          | R    | 01h   | Sense register (real time status)                   |

| 02h        | -                | _    | -     | Reserved for future use                             |

| 03h        | PID              | R    | 20h   | Product Identification                              |

| 04h        | RID              | R    | Metal | Revision Identification                             |

| 05h        | FID              | R    | 00h   | Features Identification (trim)                      |

| 06h to 11h | -                | -    | _     | Reserved for future use                             |

| 12h        | PGOOD            | RW   | 01h   | Power good and active discharge settings (trim)     |

| 13h        | TIME             | RW   | 19h   | Enabling and DVS timings (trim)                     |

| 14h        | COMMAND          | RW   | 8Dh   | Enabling and Operating mode Command register (trim) |

| 15h        | -                | -    | _     | Reserved for future use                             |

| 16h        | LIMCONF          | RW   | E2h   | Reset and limit configuration register (trim)       |

| 17h        | PROGVSEL1        | RW   | 28    | Output voltage settings for VSEL pin = High (trim)  |

| 18h        | PROGVSEL0        | RW   | 60    | Output voltage settings for VSEL pin = Low (trim)   |

| 19h to 26h | -                | -    | -     | Reserved for future use                             |

| 27h to FFh | -                | -    | -     | Reserved. Test Registers                            |

Table 9. I<sup>2</sup>C REGISTERS MAP CONFIGURATION (NCV6357D)

| Add.       | Register<br>Name | Туре | Def.  | Function                                            |

|------------|------------------|------|-------|-----------------------------------------------------|

| 00h        | INT_ACK          | RC   | 00h   | Interrupt register                                  |

| 01h        | INT_SEN          | R    | 01h   | Sense register (real time status)                   |

| 02h        | _                | _    | -     | Reserved for future use                             |

| 03h        | PID              | R    | 20h   | Product Identification                              |

| 04h        | RID              | R    | Metal | Revision Identification                             |

| 05h        | FID              | R    | 08h   | Features Identification (trim)                      |

| 06h to 11h | -                | -    | _     | Reserved for future use                             |

| 12h        | PGOOD            | RW   | 11h   | Power good and active discharge settings (trim)     |

| 13h        | TIME             | RW   | 09h   | Enabling and DVS timings (trim)                     |

| 14h        | COMMAND          | RW   | 8Fh   | Enabling and Operating mode Command register (trim) |

| 15h        | -                | -    | _     | Reserved for future use                             |

| 16h        | LIMCONF          | RW   | E3h   | Reset and limit configuration register (trim)       |

| 17h        | PROGVSEL1        | RW   | 34    | Output voltage settings for VSEL pin = High (trim)  |

| 18h        | PROGVSEL0        | RW   | 34    | Output voltage settings for VSEL pin = Low (trim)   |

| 19h to 26h | _                | -    | -     | Reserved for future use                             |

| 27h to FFh | -                | -    | -     | Reserved. Test Registers                            |

## Table 10. I<sup>2</sup>C REGISTERS MAP CONFIGURATION (NCV6357F)

| Add.       | Register<br>Name | Туре | Def.  | Function                                            |

|------------|------------------|------|-------|-----------------------------------------------------|

| 00h        | INT_ACK          | RC   | 00h   | Interrupt register                                  |

| 01h        | INT_SEN          | R    | 01h   | Sense register (real time status)                   |

| 02h        | -                | _    | -     | Reserved for future use                             |

| 03h        | PID              | R    | 20h   | Product Identification                              |

| 04h        | RID              | R    | Metal | Revision Identification                             |

| 05h        | FID              | R    | 04h   | Features Identification (trim)                      |

| 06h to 11h | -                | _    | -     | Reserved for future use                             |

| 12h        | PGOOD            | RW   | 11h   | Power good and active discharge settings (trim)     |

| 13h        | TIME             | RW   | 09h   | Enabling and DVS timings (trim)                     |

| 14h        | COMMAND          | RW   | 8Fh   | Enabling and Operating mode Command register (trim) |

| 15h        | -                | -    | -     | Reserved for future use                             |

| 16h        | LIMCONF          | RW   | E3h   | Reset and limit configuration register (trim)       |

| 17h        | PROGVSEL1        | RW   | 28    | Output voltage settings for VSEL pin = High (trim)  |

| 18h        | PROGVSEL0        | RW   | 20    | Output voltage settings for VSEL pin = Low (trim)   |

| 19h to 26h | -                | -    | -     | Reserved for future use                             |

| 27h to FFh | -                |      | -     | Reserved. Test Registers                            |

## **Registers Description**

## Table 11. INTERRUPT ACKNOWLEDGE REGISTER

| Name: INTAC                                                                                          | CK                                                                                           |                                                             |                                                       |     | Address: 00h    |           |    |    |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|-----|-----------------|-----------|----|----|

| Type: RC                                                                                             |                                                                                              |                                                             |                                                       |     | Default: 000000 | 00b (00h) |    |    |

| Trigger: Dual                                                                                        | Edge [D7                                                                                     | 7D0]                                                        |                                                       |     |                 |           |    |    |

| D7                                                                                                   | D                                                                                            | 6                                                           | D5                                                    | D4  | D3              | D2        | D1 | D0 |

| ACK_TSD                                                                                              | ACK_T                                                                                        | WARN ACK_TPREW Spare = 0 ACK_ISHORT ACK_UVLO ACK_IDCDC ACK_ |                                                       |     |                 |           |    |    |

| Bit                                                                                                  | -                                                                                            |                                                             |                                                       |     | Bit Description | 1         |    |    |

| ACK_P                                                                                                | 'G                                                                                           | 0: Clear                                                    | Good Sense Acknow<br>ed<br>C Power Good Even          | Ü   |                 |           |    |    |

| ACK_IDC                                                                                              | CDC                                                                                          | 0: Clear                                                    | Over Current Sense A<br>ed<br>C Over Current Even     |     | ent             |           |    |    |

| ACK_UV                                                                                               | /LO                                                                                          | 0: Clear                                                    | oltage Sense Ackno<br>ed<br>r Voltage Event dete      | ŭ   |                 |           |    |    |

| ACK_ISH                                                                                              | ORT                                                                                          | 0: Clear                                                    | Short-Circuit Protect<br>ed<br>C Short circuit protec |     | nowledgement    |           |    |    |

| ACK_TPREW Thermal Pre Warning Sense Acknowledgement 0: Cleared 1: Thermal Pre Warning Event detected |                                                                                              |                                                             |                                                       |     |                 |           |    |    |

| ACK_TW/                                                                                              | ACK_TWARN Thermal Warning Sense Acknowledgement 0: Cleared 1: Thermal Warning Event detected |                                                             |                                                       |     |                 |           |    |    |

| ACK_TS                                                                                               | SD                                                                                           | 0: Clear                                                    | Shutdown Sense A<br>ed<br>nal Shutdown Event          | · · | nt              |           |    |    |

## **Table 12. INTERRUPT SENSE REGISTER**

| Name: INTSE  | N     |                                                                                                                              |                                                                   |                | Address: 01h             |          |           |        |  |  |

|--------------|-------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------|--------------------------|----------|-----------|--------|--|--|

| Type: R      |       |                                                                                                                              |                                                                   |                | Default: 00000000b (00h) |          |           |        |  |  |

| Trigger: N/A |       |                                                                                                                              |                                                                   |                |                          |          |           |        |  |  |

| D7           | D     | 6                                                                                                                            | D5                                                                | D4             | D3                       | D2       | D1        | D0     |  |  |

| SEN_TSD      | SEN_T | WARN SEN_TPREW Spare = 0                                                                                                     |                                                                   |                | SEN_ISHORT               | SEN_UVLO | SEN_IDCDC | SEN_PG |  |  |

|              |       | В                                                                                                                            | it                                                                |                |                          | Bit Desc | ription   |        |  |  |

| SEN_P        | G     | 0: DCD0                                                                                                                      | Good Sense<br>C Output Voltage bel<br>C Output Voltage wit        | J              | ge                       |          |           |        |  |  |

| SEN_IDC      | CDC   | DCDC over current sense 0: DCDC output current is below limit 1: DCDC output current is over limit                           |                                                                   |                |                          |          |           |        |  |  |

| SEN_UV       | /LO   | 0: Input                                                                                                                     | oltage Sense<br>Voltage higher than<br>Voltage lower than U       |                |                          |          |           |        |  |  |

| SEN_ISH      | ORT   | 0: Short                                                                                                                     | Short-Circuit Protect -Circuit detected not -Circuit not detected | detected       |                          |          |           |        |  |  |

| SEN_TPF      | REW   | 0: Juncti                                                                                                                    | Pre–Warning Sense<br>on temperature belo<br>on temperature over   | w thermal pre- |                          |          |           |        |  |  |

| SEN_TW/      | ARN   | Thermal Warning Sense 0: Junction temperature below thermal warning limit 1: Junction temperature over thermal warning limit |                                                                   |                |                          |          |           |        |  |  |

| SEN_TS       | SD    | 0: Juncti                                                                                                                    | Shutdown Sense on temperature below temperature over              |                |                          |          |           |        |  |  |

## Table 13. PRODUCT ID REGISTER

| Name: PID    |       |       | Address: 03h |                          |       |       |       |

|--------------|-------|-------|--------------|--------------------------|-------|-------|-------|

| Type: R      |       |       |              | Default: 00011011b (21h) |       |       |       |

| Trigger: N/A |       |       |              | Reset on N/A             |       |       |       |

| D7           | D6    | D5    | D4           | D3                       | D2    | D1    | D0    |

| PID_7        | PID_6 | PID_5 | PID_4        | PID_3                    | PID_2 | PID_1 | PID_0 |

## Table 14. REVISION ID REGISTER

| Name: RID    |     |          |                                                    |       | Address: 04h    |       |       |       |  |

|--------------|-----|----------|----------------------------------------------------|-------|-----------------|-------|-------|-------|--|

| Type: R      |     |          |                                                    |       | Default: Metal  |       |       |       |  |

| Trigger: N/A |     |          |                                                    |       |                 |       |       |       |  |

| D7           | D   | D6 D5 D4 |                                                    |       | D3              | D2    | D1    | D0    |  |

| RID_7        | RIE | 0_6      | RID_5                                              | RID_4 | RID_3           | RID_2 | RID_1 | RID_0 |  |

| Bit          | •   |          |                                                    |       | Bit Description |       |       |       |  |

| RID[7        | 0]  |          | Revision Identification<br>00000000: First Silicon |       |                 |       |       |       |  |

## Table 15. FEATURE ID REGISTER

| Name: FID    |       |                  |                                                                                                                                           | Address: 05h    |                           |       |       |  |  |

|--------------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|-------|-------|--|--|