**ON Semiconductor**

Is Now

Tc learn more about onsemi™, clease visit our website at <u>vww.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information product faures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and resonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application or mufacture of the part. Onsemi as Equa

## **Digital Servo Processor LSI** for Compact Disc Player with **RF** Amplifier

## **ON Semiconductor®**

www.onsemi.com

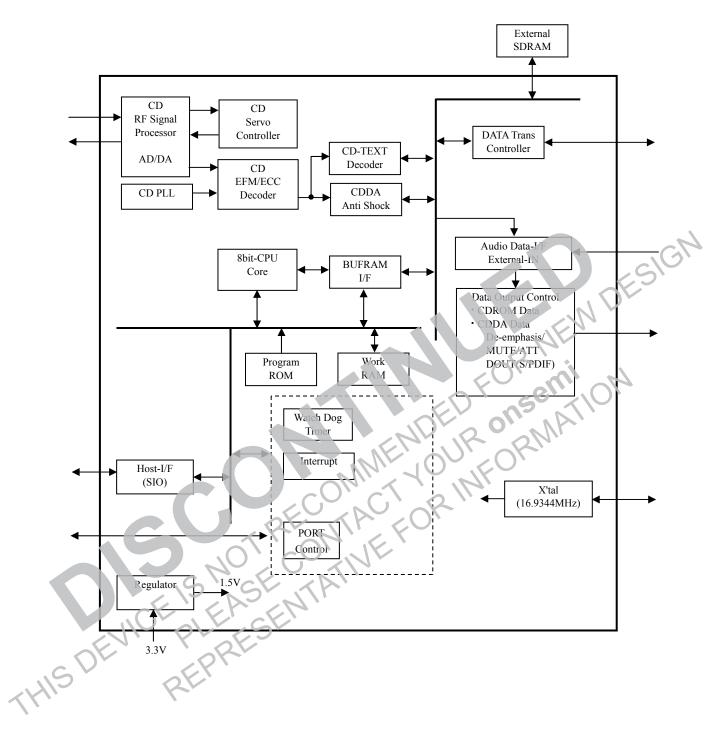

#### **Overview**

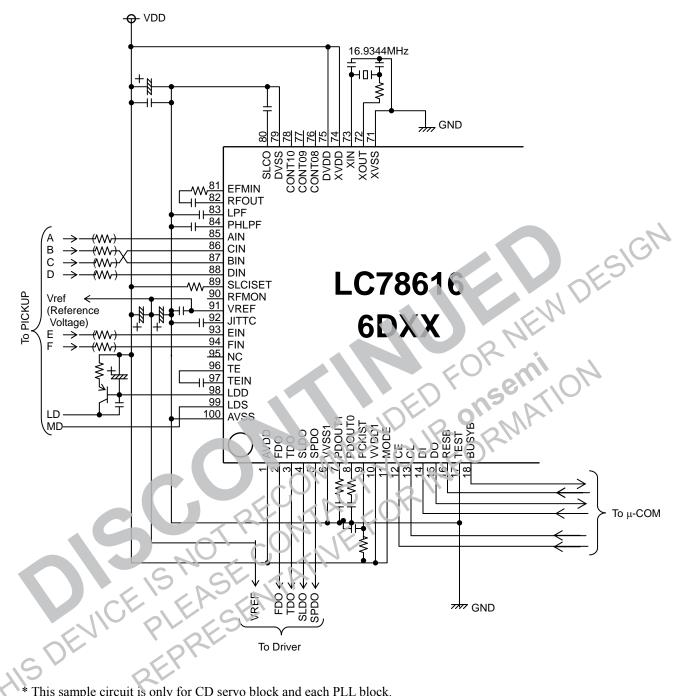

The LC78616PE integrates RF signal processor for CD-DA/R/RW, servo control, EFM signal processing, anti-shock processing and playback controller (Sequencer : 8bits CPU). It is possible to make CD player system using with micro controller, driver and SDRAM IC's with less components.

#### **Features**

- · RF signal processing for CD-DA/R/RW, servo control and EFM signal processing

- · Outputs CDDA, CDROM data

- · Maximum approximately 40 seconds shock protection by shock prooffunction with external 64M bits SDRAM

- · CD-TEXT decoded data are stored in external SDRAM

- · CD playback system is realized with simple macro commands by the external controller because of the internal Sequencer (8 bits - CPU).

- · Operating Voitage 3.3 V Typical

- Operating Temperature -40°C to +85°C PRESER

- Package : QIP100E(14×20) THISDE

# PQFP100 14x20 / QIP100E JRMATION

onser

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 27 of this data sheet.

#### **Detail of Functions** [CD-DSP functions]

## < Playback functions>

Playback mode : CLV playback / Jitter free playback (VCEC)

• Playback speed : Normal speed, double speed, quadruple speed (CLV playback / Jitter free playback)

<RF processing block>

• RF system : AGC, CD-R and CD-R/W playback support, peak hold, bottom hold : TE signal generation, FE signal generation

• Error system

- Detection : Track count signal, Jitter, Defect (black, mirror)

- LASER power controller (APC)

• DC offset voltage cancellation

#### <Servo control block>

· All servo systems as tracking, focus, sled and spindle are implemented with digital processing.

• Automatic adjustment functions : focus gain, focus bias, focus offset, tracking gain, tracking offset and tracking balance FOR NEW DESIGN

## Shock detection / Interruption detection

#### <CD signal processing block>

· EFM signal synchronization detection, protection and interpolation

- Error detection, correction (C1 = double, C2 = quadruple/double)

- Jitter margin  $\pm 19$  frames

<CD-TEXT processing block>

- · Buffers CD-TEXT decoded data to the buffer memory.

- Starts buffering of CD-TEXT decoded data from desired ID3/ID4

#### <Shock proof processing block>

Shock proof processing using with external 16M-bit or 64M-bit Memory

Approximately 10sec. with 16Mbit or 40sec. with 64Mbit

## [CD data processing functions]

- <CDDA data processing block> Interpolation

- Mute function (-12 dB,

- Digital attenuator

- De-emphasis filter

- <CDROM data processing block> CLV playback

- Fixed normal speed or double speed

- Jitter free playback (VCEC) : Free speed within guadruple speed

- \*CDROM Data is not buffering to SDRAM and output directly

## <Outputs format>

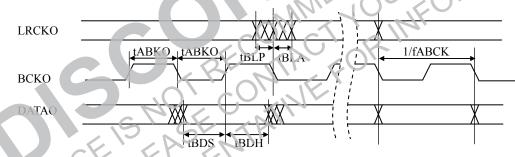

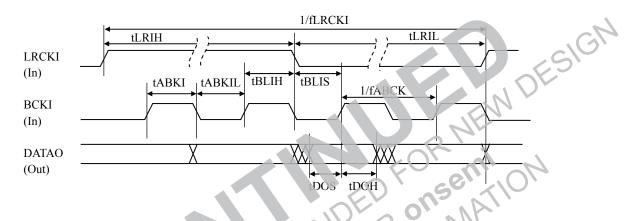

- Digital 3 lines output(L.CK, BCK, DATA)

- Supports various external audio data output format

- IS (48-1s), MSB First, Right-Justified, Left-Justified (32 fs / 48 fs), 16-bit data length Slave mode

- Output DATA synchronized to external Clock input (LRCK and BCK)

- D gital output (S/PDIF, only CLV playback mode)

## [Internal Microcontroller functions]

- <Sequencer control>

- · CD playback control

- Servo control, CD-TEXT processing, Digital data output control, etc.

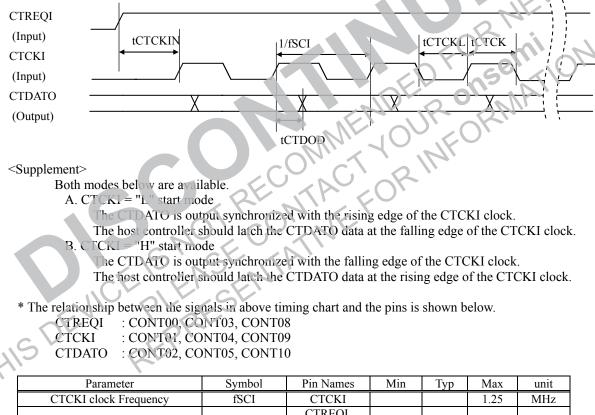

## Communication control between main controller>

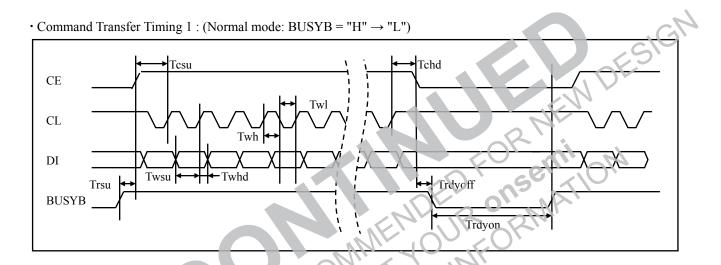

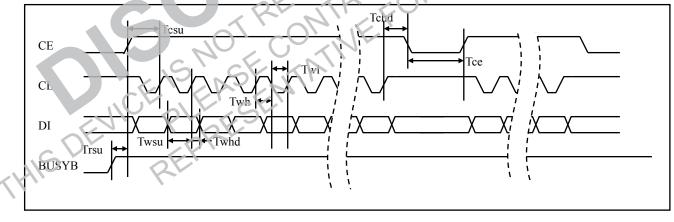

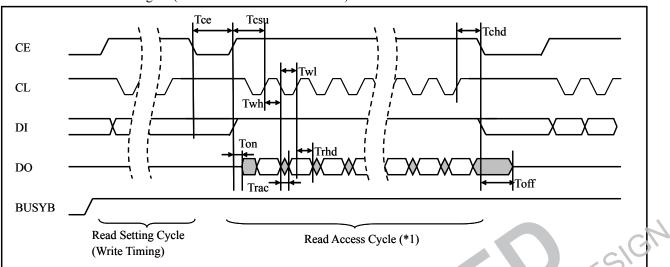

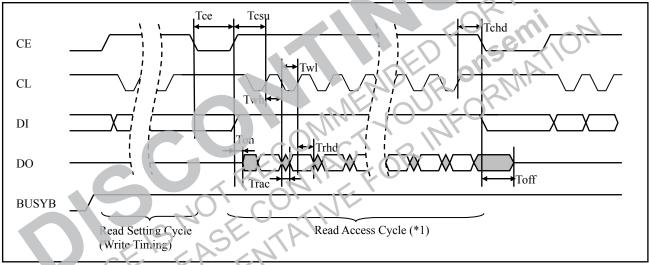

- The SIO interface using CE, CL, DI, DO and BUSYB pins is available as communication format.

- · External main controller can control this IC directly such as "stop oscillation" or "restart oscillation" or so on at the internal register open mode (REG READY high condition).

- Even while the oscillation is stopped, some of general port can be controlled by host controller.

#### <Peripheral interface block>

· GPIO port 8 ports maximum (Shared with other functions.)

<Program memory block>

· Mask-ROM type

- ROM Correct function is built in for the partial change of the program and Host controller can use this.

- <Others>

- · Watch Dog Timer

- Notifies to outside from a pin or resets internally.

- Power management (Two kinds of sleep mode)

- (1) Only the clock for CPU core is operating and clocks for other blocks are stopping.

- (2) All clocks are stopping.

## [Others]

<Internal power supply>

1.5 V regulator for internal blocks

#### **Specifications** Absolute Maximum Ratings at Ta = 25°C, DV<sub>SS</sub> = AV<sub>SS</sub> = XV<sub>SS</sub> = VV<sub>SS</sub>1 = 0 V

| <b>3 3 3 3 3 3 3 3 3 3</b>  |                     |                                            |                                 |      |  |  |  |  |

|-----------------------------|---------------------|--------------------------------------------|---------------------------------|------|--|--|--|--|

| Parameter                   | Symbol              | Conditions                                 | Ratings                         | Unit |  |  |  |  |

| Maximum supply voltage      | V <sub>DD</sub> max | DVDD, AVDD, XVDD, VVDD1                    | -0.3 to +3.95                   |      |  |  |  |  |

| Input voltage 1             | V <sub>IN</sub> 1   |                                            | -0.3 to DV <sub>DD</sub> +0.3   | V    |  |  |  |  |

| Output voltage              | V <sub>OUT</sub>    |                                            | -0.3 to DV <sub>DD</sub> $+0.3$ |      |  |  |  |  |

| Allowable power dissipation | Pd max              | Ta $\leq$ 85°C<br>Mounted reference PCB(*) | 300                             | mW   |  |  |  |  |

| Operating temperature       | Topr                |                                            | -40 to +85                      |      |  |  |  |  |

| Storage temperature         | Tstg                |                                            | -40 to +125                     | °C   |  |  |  |  |

(\*) Reference PCB : 114.3 mm × 76.1 mm × 1.6 mm, glass epoxy resin

<Notes>

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. <u>F</u>S

# Allowable Operating Ranges at Ta = -40 to $85^{\circ}$ C, DV<sub>SS</sub> = AV<sub>SS</sub> = XV<sub>SS</sub> = VV<sub>SS</sub>1 = 0.

| Parameter                       | Symbol          | Pin Names                                                                                                                                                            | Туре                  | Conditions | MIN  | ТҮР     | MAX  | Unit |

|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|------|---------|------|------|

| Supply voltage                  | V <sub>DD</sub> | DVDD, AVDD,<br>XVDD, VVDD1                                                                                                                                           |                       |            | 3.00 |         | 3.60 |      |

| High-level input<br>voltage     | VIH             | XIN,RESB, MODE, MODE?<br>CE, CL, DI,<br>CONT00, CONT01, CONT02,<br>CONT03, CONT04, CONT05,<br>CONT08, CONT09, CONT10,<br>DO,<br>SDDAT00 to 15<br>SDADK 11, SDADRS12  | Schmitt               | DED        | 2.00 | ent     | VDD  | V    |

| Low-level-input<br>voltage      | VIL.            | XIN, ESB, TEST, MODE3,<br>CF CL, DI<br>CONT00, CONT01, CONT02,<br>CONT03, CONT04, CONT05,<br>CONT08, CONT09, CONF10,<br>DO,<br>SE DA100 to 15,<br>CDADRS11, SDADRS12 | Schmitt               | 04         | 0.00 |         | 0.80 |      |

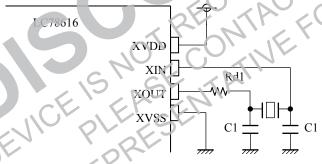

| Crystal Osciliator<br>Frequency | FX              | XIN<br>XOUT                                                                                                                                                          | Oscillator<br>circuit |            |      | 16.9344 |      | MHz  |

| External<br>clock Input         | EXCK            | XIN                                                                                                                                                                  | Schmitt               |            |      | 16.9344 | 18.0 | MHz  |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability

| Parameter                         | Symbol              | Pin Names                                                                                                                                                                                               | Туре         | Conditions                                                                    | MIN          | TYP | MAX   | Unit |

|-----------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------|--------------|-----|-------|------|

| Current drain                     | I <sub>DD</sub> 1   | DVDD, AVDD,<br>XVDD, VVDD1                                                                                                                                                                              |              |                                                                               |              | 40  | 60    | mA   |

| High-level input current          | IIH                 | RESB, MODE, MODE3,<br>CE, CL, DI,<br>CONT00, CONT01, CONT02,<br>CONT03, CONT04, CONT05,<br>CONT08, CONT09, CONT10,<br>DO,<br>SDDAT00 to 15,<br>SDADRS11, SDADRS12                                       | Schmitt      | V <sub>IN</sub> = V <sub>DD</sub><br>Built-in<br>Pull-down<br>Resistor<br>OFF |              |     | 10.00 | μΑ   |

| Low-level input current           | IIL                 | RESB, TEST, MODE3,<br>CE, CL, DI,<br>CONT00, CONT01, CONT02,<br>CONT03, CONT04, CONT05,<br>CONT08, CONT09, CONT10,<br>SDDAT00 to 15,<br>SDADRS11, SDADRS12                                              | Schmitt      | V <sub>IN</sub> = 0.0V<br>Built-in<br>Pull-down<br>Resistor<br>OFF            | -10.00       |     |       |      |

| High-level<br>output voltage      | V <sub>OH</sub> (1) | DO, BUSYB,<br>CONT00, CONT01, CONT02,<br>CONT03, CONT05,<br>CONT08, CONT09, CONT10,<br>SDDAT00 to SDDAT15,<br>SDADRS00 to SDADRS12,<br>SDBA,<br>SDCKE, SDCSB, SDRASB,<br>SDCASB, SDWEB, SDDQM           | CMOS         | IOH = -2 mA                                                                   | VD1)<br>-0.6 | NEV | DE    | SIC  |

|                                   | $V_{OH}(2)$         | CL, DI, CONT04, SDCLK                                                                                                                                                                                   | CMOS         | IOH = -4 mA                                                                   | G            | 6   | Ú,    | v    |

| Low-level<br>output voltage       | V <sub>OL</sub> (1) | DO, BUSYB,<br>CONT00, CONTC CON 2,<br>CONT03, CONT05<br>CONT08 CON 9, CONT10,<br>SDDAT to SDL T15<br>SDDAT to SDL AT15<br>SDBA,<br>SDCK1 SDCSB SDRASB,<br>SDCA B, SDWEB, SDDQM<br>CL, DI, CONT04, SDCLK | CMOS<br>CMOS | IOL = 2 mA<br>IOL = 4 mA                                                      | FOR          | MA  | 0.40  | v    |

| Output                            | $I_{OFF}(1)$        | PDOUT), PDOUT1                                                                                                                                                                                          | 12           | Hi-Z Out                                                                      | -10.00       |     | 10.00 |      |

| off-leakage<br>current            | 1 <sub>OF</sub> (2) | DO ASSATA                                                                                                                                                                                               | -            | Hi-Z Out                                                                      | -10.00       |     | 10.00 | μA   |

| Built-in<br>Pull-dcwn<br>resistor | RPD                 | CE,<br>CONT00, CONT01, CONT02,<br>CONT03 CONT04, CONT05,<br>CONT03, CONT09, CONT10,<br>SDDAT00 to SDDAT15,<br>SDADRS11,SDADRS12                                                                         |              |                                                                               | 50           | 100 | 200   | kΩ   |

| Charge pump                       | IPDOH               | PDOUT1, PDOUT0                                                                                                                                                                                          |              | PCKIST =<br>100 kΩ                                                            | 35           | 50  | 65    |      |

| output current                    | IPDOL               | PDOUT1, PDOUT0                                                                                                                                                                                          |              | Current value<br>Setting : 1x                                                 | -65          | -50 | -35   | μΑ   |

(Notes)

• Connect and use the pull-up or the pull-down resister with the outside when you use serial communications because the terminal DO is 3- State output (initial state).

• The DO, BUSYB, CONT00, CONT01, CONT02, CONT03, CONT04, CONT05, CONT08, CONT09 and CONT10 pins can be used as the N channel open drain pins. When used as the N channel open drain pin, external pull-up resistor must be connected to those pins.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

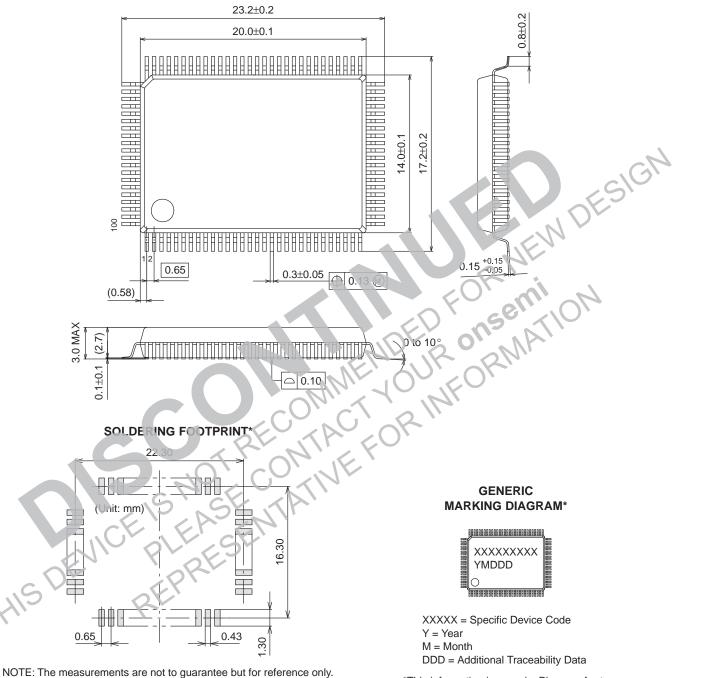

Package Dimensions unit : mm

PQFP100 14x20 / QIP100E CASE 122BV ISSUE A

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present.

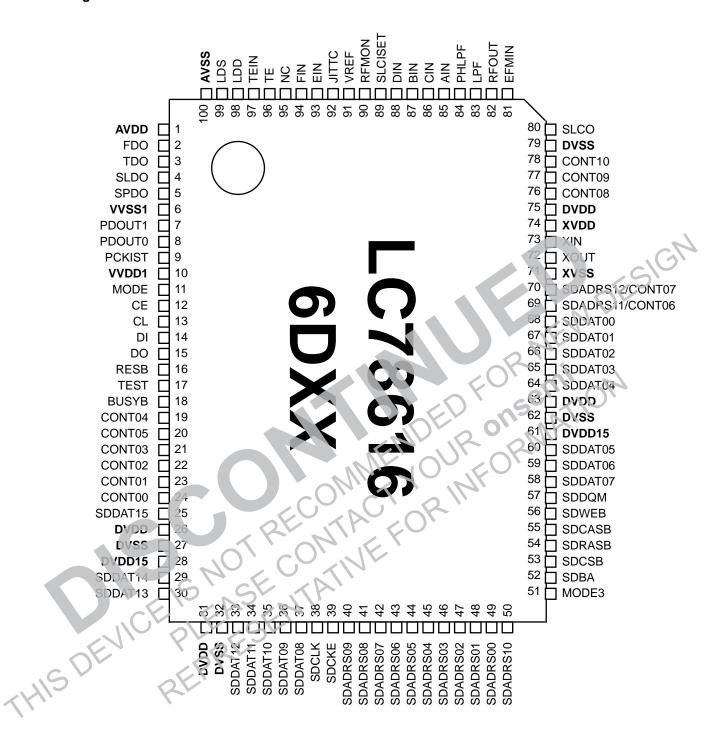

## PIN Assignment

## LC78616PE

## **Pin Description**

| Pin<br>No. | Pin name | I/O    | State when<br>"Reset" | Function                                                                                                                                                      |

|------------|----------|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | AVDD     | _      | _                     | Analog system power supply                                                                                                                                    |

| 2          | FDO      | AO     | AVDD/2                | Focus control signal output                                                                                                                                   |

| 3          | TDO      | AO     | AVDD/2                | Tracking control signal output                                                                                                                                |

| 4          | SLDO     | AO     | AVDD/2                | Sled control signal output                                                                                                                                    |

| 5          | SPDO     | AO     | AVDD/2                | Spindle control signal output                                                                                                                                 |

| 6          | VVSS1    | -      |                       | EFMPLL ground. This pin must be connected to the 0V level.                                                                                                    |

| 7          | PDOUT1   | AO     | Undefined             | EFMPLL charge pump output 1                                                                                                                                   |

| 8          | PDOUT0   | AO     | Undefined             | EFMPLL charge pump output 0                                                                                                                                   |

| 9          | PCKIST   | AI     | Input                 | EFMPLL charge pump current setting resistor connection pin                                                                                                    |

| 9          | VVDD1    |        | mput                  | EFMPLL power supply                                                                                                                                           |

| -          |          | —<br>I |                       |                                                                                                                                                               |

| 11         | MODE     | 1      | Input                 | LSI mode set pin. This pin must be connected to the DVDD level.<br>Host I/F                                                                                   |

| 12         | CE       | Ι      | Input                 | Enable signal input for serial communication<br>This pin must be connected to the 0V level in IIC communication mode.                                         |

| 13         | CL       | I/O    | Input                 | Host I/F<br>Data transfer clock input for serial communication<br>Data transfer clock input for IIC communication (N-ch. open drain)                          |

| 14         | DI       | I/O    | Input                 | Host I/F<br>Data input for serial communication<br>Data input/output for IIC communication (N-ch. open cirain)                                                |

| 15         | DO       | I/O    | Input                 | Host I/F<br>Data output for serial communication<br>This pin must be pulled down to the 0V level or be pulled up to the DVDD level<br>IIC communication mode. |

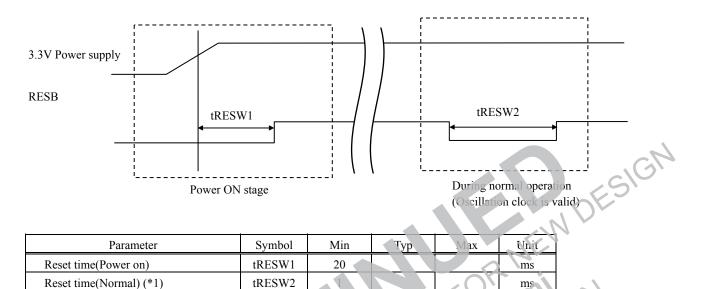

| 16         | RESB     | Ι      | Input                 | IC reset input (Low active)<br>This pin must be set low once after power is first applied.                                                                    |

| 17         | TEST     | Ι      | Input                 | Test input. This pin must be connected to the 0V level                                                                                                        |

| 10         |          |        |                       | Host I/F                                                                                                                                                      |

| 18         | BUSYB    | 0      | Low                   | BUSYB output(Hign : Con munication available)                                                                                                                 |

|            |          |        |                       | General purpose I/O port with pull down resistor                                                                                                              |

|            |          |        |                       | Digital audio output <s pdif=""></s>                                                                                                                          |

| 19         | CONT04   | I/O    | Input                 | FS384 clock output for Audio DAC                                                                                                                              |

|            |          |        |                       | Clock input/out out for CDTEXT interface (exclusive with CONT01 and CONT09                                                                                    |

|            |          |        |                       | Watch Deg Timer state monitor output                                                                                                                          |

| 20         | CONT05   | I/O    | Input                 | General purpose I/O port with pull down resistor                                                                                                              |

|            |          |        |                       | Serial data output for CDTEXT interface                                                                                                                       |

|            |          | , G    | ` cX                  | General purpose I/O port with pull down resistor<br>Digital a idio output <s pdif=""></s>                                                                     |

|            |          | 210    |                       | F S <sup>2</sup> <sup>2</sup> 4 clock output for Audio DAC                                                                                                    |

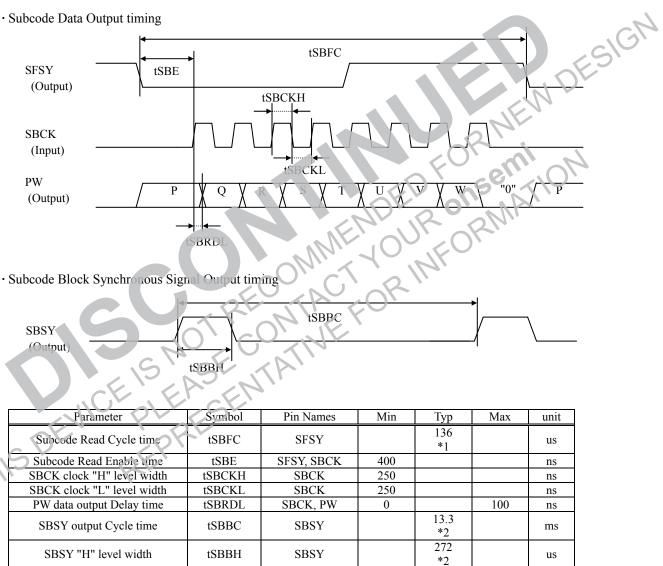

| 21         | CONT03   | 1/O    | Input                 | SBCK clock input for CD subcode data                                                                                                                          |

|            |          |        | - mp a                | Data request signal input for CDTEXT interface (exclusive with CONT00 and                                                                                     |

|            |          | X      | 24                    | CONT08)                                                                                                                                                       |

|            |          |        |                       | Watch Dog Timer state monitor output                                                                                                                          |

| . 0        | h        |        |                       | General purpose I/O port with pull down resistor                                                                                                              |

| 22         | CONT02   | 1/O    | Input                 | Data output for Digital Audio interface                                                                                                                       |

| 22         | 00002    | 1/0    | input                 | PW data output in CD subcode                                                                                                                                  |

|            |          |        |                       | Serial data output for CDTEXT interface                                                                                                                       |

|            |          |        |                       | General purpose I/O port with pull down resistor                                                                                                              |

| 22         | CONTOI   | L/O    | Turnet                | Bit clock output for CD data                                                                                                                                  |

| 23         | CONT01   | I/O    | Input                 | Bit clock input for CD data (exclusive with CONT09)<br>Frame synchronization signal (SFSY) output for CD subcode                                              |

|            |          |        |                       | Clock input/output for CDTEXT interface (exclusive with CONT04 and CONT09                                                                                     |

|            |          |        |                       | General purpose I/O port                                                                                                                                      |

|            |          |        |                       | LR clock output for CD data                                                                                                                                   |

| 24         | CONT00   | I/O    | Input                 | LR clock input for CD data (exclusive with CONT08)<br>Block synchronization signal (SBSY) output for CD subcode                                               |

|            |          |        | _                     | Data request signal input for CDTEXT interface (exclusive with CONT03 and                                                                                     |

|            |          | 1      |                       | 1 - 0 - r                                                                                                                                                     |

|            |          |        |                       | CONT08)                                                                                                                                                       |

| No.                                                                                                                     | Pin name                                                                                    | I/O                                    | State when<br>"Reset"                                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

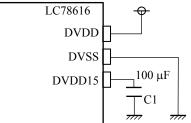

| 26                                                                                                                      | DVDD                                                                                        | -                                      | -                                                                                               | Digital system power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 27                                                                                                                      | DVSS                                                                                        | _                                      | -                                                                                               | Digital system ground. This pin must be connected to the 0V level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28                                                                                                                      | DVDD15                                                                                      | AO                                     | High                                                                                            | Capacitor connection pin for internal regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 29                                                                                                                      | SDDAT14                                                                                     | I/O                                    | Input(Low)                                                                                      | SDRAM data 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30                                                                                                                      | SDDAT13                                                                                     | I/O                                    | Input(Low)                                                                                      | SDRAM data 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 31                                                                                                                      | DVDD                                                                                        | _                                      |                                                                                                 | Digital system power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32                                                                                                                      | DVSS                                                                                        | _                                      |                                                                                                 | Digital system ground. This pin must be connected to the 0V level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 33                                                                                                                      | SDDAT12                                                                                     | I/O                                    | Input(Low)                                                                                      | SDRAM data 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 33                                                                                                                      | SDDAT12<br>SDDAT11                                                                          |                                        | · · ·                                                                                           | SDRAM data 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                         |                                                                                             | I/O                                    | Input(Low)                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 35                                                                                                                      | SDDAT10                                                                                     | I/O                                    | A \ /                                                                                           | SDRAM data 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 36                                                                                                                      | SDDAT09                                                                                     | I/O                                    | Input(Low)                                                                                      | SDRAM data 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 37                                                                                                                      | SDDAT08                                                                                     | I/O                                    | Input(Low)                                                                                      | SDRAM data 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

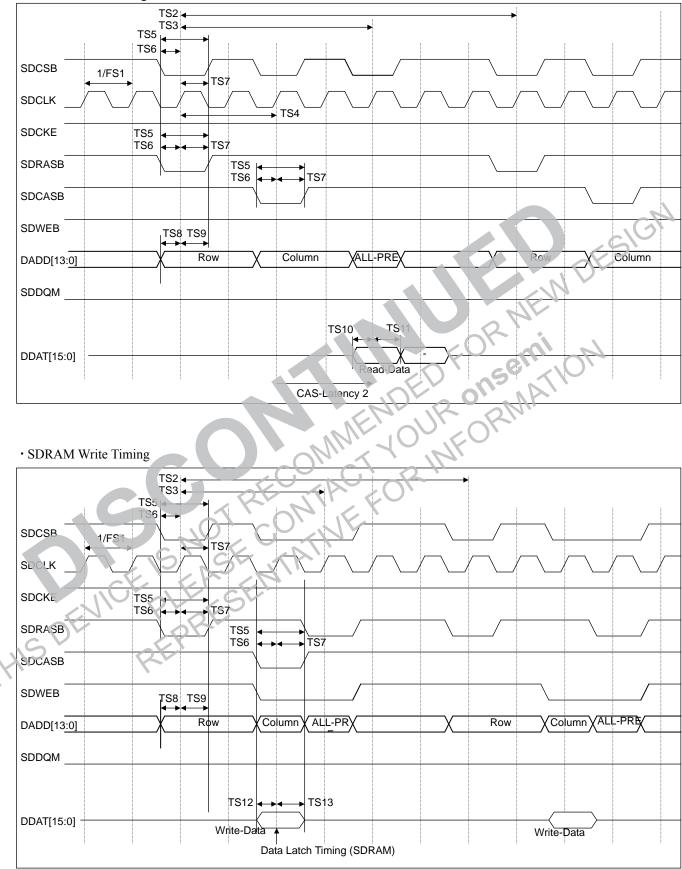

| 38                                                                                                                      | SDCLK                                                                                       | 0                                      | Low                                                                                             | SDRAM system clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 39                                                                                                                      | SDCKE                                                                                       | 0                                      | Low                                                                                             | SDRAM clock enable output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 40                                                                                                                      | SDADRS09                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 41                                                                                                                      | SDADRS08                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 42                                                                                                                      | SDADRS07                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 43                                                                                                                      | SDADRS06                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 44                                                                                                                      | SDADRS05                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 45                                                                                                                      | SDADRS03                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                         |                                                                                             |                                        |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 46                                                                                                                      | SDADRS03                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 47                                                                                                                      | SDADRS02                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 48                                                                                                                      | SDADRS01                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 49                                                                                                                      | SDADRS00                                                                                    | 0                                      | Low                                                                                             | SDRAM address output 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 50                                                                                                                      | SDADRS10                                                                                    | 0                                      | Low                                                                                             | SDPAM address output 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 51                                                                                                                      | MODE3                                                                                       | Ι                                      | Input                                                                                           | LSI mode set pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 52                                                                                                                      | SDBA                                                                                        | 0                                      | Low                                                                                             | SDRAM Bank select Address output<br>Connect SDRAM-BANK pin when 16Mbit SDRAM using<br>Connect SDRAM-BANK1 pin when 64Muit SDRAM using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 53                                                                                                                      | SDCSB                                                                                       | 0                                      | Low                                                                                             | SDRAM Chip Select cutput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 54                                                                                                                      | SDRASB                                                                                      | 0                                      | Low                                                                                             | SDRAM Row Ad ress Strobe ou put                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 55                                                                                                                      | SDCASB                                                                                      |                                        | Low                                                                                             | SDRAM Column Address Strebe output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 56                                                                                                                      | SDWEB                                                                                       |                                        | Low                                                                                             | SDRAM Write Enable output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 50                                                                                                                      |                                                                                             |                                        | <u> </u>                                                                                        | SDFAM Data Mas', Control output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 57                                                                                                                      | SDDQM                                                                                       |                                        | Low                                                                                             | Common both for 16M/64Mbit-SDRAM : Connect this pin both to SDRAM-DQMH(UDQM) and DQML(LDQM) pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 58                                                                                                                      | SDDAT07                                                                                     | I/O                                    | Input(Lov)                                                                                      | SDRAM data 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 59                                                                                                                      | SDDAT06                                                                                     | 1/O                                    | input(Low)                                                                                      | SDRAM data 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 60                                                                                                                      | SDDAT05                                                                                     | I/O                                    |                                                                                                 | SDRAM data 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 61                                                                                                                      | DVDD15                                                                                      | AC                                     | High                                                                                            | Capacitor connection pin for internal regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 62                                                                                                                      | DVSS                                                                                        | -                                      |                                                                                                 | Digital system ground. This pin must be connected to the 0V level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                         |                                                                                             |                                        | _                                                                                               | Digital system power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                         | סמעם                                                                                        |                                        |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 63                                                                                                                      | DVDD<br>SDDAT04                                                                             | -                                      | Input(Low)                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 63<br>64                                                                                                                | SDDAT04                                                                                     |                                        | Input(Low)                                                                                      | SDRAM data 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |