# Wideband Voice Capture and Noise Reduction Solution

#### Introduction

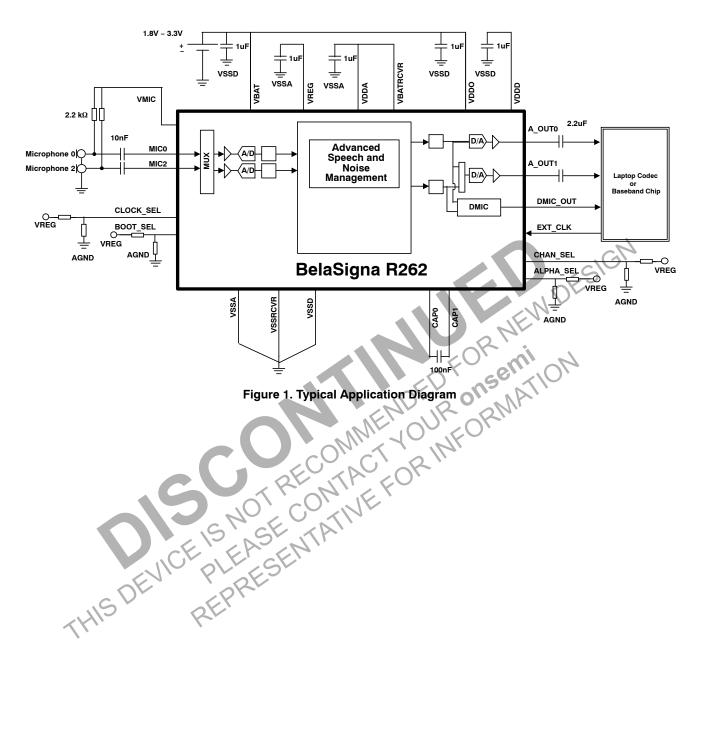

BelaSigna<sup>®</sup> R262 is a complete system-on-chip (SoC) solution that provides wideband advanced noise reduction in voice capture applications such as mobile phones, VoIP applications including webcams and tablet computers, two-way radios and other applications that can benefit from improved voice clarity.

Featuring a novel approach to removing mechanical, stationary and non-stationary noise, the chip preserves voice naturalness for greater voice clarity and speech intelligibility even when the talker is further away or not optimally aligned with the microphones, providing unmatched freedom of movement for end-users. Designed to be compatible with a wide range of codecs, baseband chips and microphones without the need for calibration, BelaSigna R262 is easy to integrate, improving manufacturers' time to market.

Additional features include the ability to provide two simultaneously processed outputs and to configure them depending on the needs of a manufacturer's device. The chip includes a highly optimized DSP-based application controller with industry-leading energy efficiency and is packaged in a highly compact 5.3 mm<sup>2</sup> WLCSPs to fit into even the most sized-constrained architectures while allowing the use of common industry printed circuit board design technologies.

#### Key Features and Benefits

- Drop-in Solution that Works without Special Tuning

- Consistently Captures Voice Regardless of Acoustic Environment or the Orientation of the Handheld Device While in Use

- 360° Voice Pick-up Adjustable From 5 cm to 5 m

- No Constraints on Industrial Design or Microphone Model

- Simultaneous Dual-configurable Outputs

- De-reverberation

- Low Power Consumption (17 mA active and 40 µA stand-by)

- Miniature Size Allows Easy Integration into Existing Industrial Designs

#### **Typical Applications**

- Mobile Phones

- Notebook and Tablet Computers

- Two-Way Radios and PTT Devices

- VoIP Applications

- Any Device that would Benefit from Improved Voice Pick-up

## **ON Semiconductor®**

www.onsemi.com

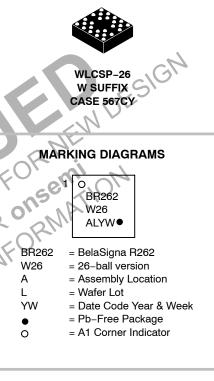

#### ORIENTATION

(Top View)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 22 of this data sheet.

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                                                                                                      | Min          | Max          | Unit |

|----------------------------------------------------------------------------------------------------------------|--------------|--------------|------|

| Power Supply (Applies on VBAT, VBATRCVR and VDDO for "Max" and for VS-SA, VSSRCVR and VSSD for "Min") (Note 1) | -0.3         | 4.0          | V    |

| Digital input pin voltage                                                                                      | VSSD – 0.3 V | VDDO + 0.3 V | V    |

| Operating temperature range                                                                                    | -40          | 85           | °C   |

| Storage temperature range                                                                                      | -40          | 85           | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Time limit at maximum voltage must be less than 100 ms.

NOTE: Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model (HBM) tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model (MM) tested per AEC-Q100-003 (EIA/JESD22-A115)

This device series incorporates latch-up immunity and is tested in accordance with JESD78.

#### **Electrical Performance Specifications**

#### Table 2. ELECTRICAL CHARACTERISTICS (The typical parameters in Table 2 were measured at 20°C with a clean 3.3 V supply voltage (unless noted differently). Parameters marked as screened are tested on each chip. Other parameters are qualified for all process corners but not tested on every part.) ٠.

DESIGN

| Parameter | Symbol | Test Conditions / Notes | Min | Тур Мах | Unit | Screened |

|-----------|--------|-------------------------|-----|---------|------|----------|

| OVERALL   |        |                         | EV  | nsortio |      |          |

|           |        |                         |     |         | 1    |          |

| Supply voltage                | VBAT  |                                                   | 1.65  | 3.3  | 3.63 | V  |  |

|-------------------------------|-------|---------------------------------------------------|-------|------|------|----|--|

| Maximum rise time             |       | Between 0 V and 1.8 V                             | 20.20 | DL.  | 10   | ms |  |

| Average current consumption   | C     | Active mode, VBAT = 3.3 V,<br>EXT_CLK = 2.048 MHz | 16:0  | 16.5 | 17.0 | mA |  |

|                               |       | Bypass mode, VBAT = 3.3 V,<br>EXT_CLK = 2.048 MHz | 16.0  | 16.5 | 17.0 | mA |  |

|                               | SNU   | Bypass mode, VBAT = 3.3 V,<br>Internal clock      | 2.7   | 2.8  | 2.9  | mA |  |

|                               | ELER  | Sleep mode, VBAT = 3.3 V                          | 39    | 40   |      | μA |  |

| Peak active current           | OVC   | VBAT = 3.63 V                                     |       | 19   | 21   | mA |  |

| VREG (1 µF External Capacitor | ) SPI |                                                   |       |      |      |    |  |

#### VREG (1 µF External Capacitor)

| Output voltage  | VREG | Without load, or with microphone attached (0 to 200 $\mu\text{A})$ | 0.95 | 1.00 | 1.05 | V     | • |

|-----------------|------|--------------------------------------------------------------------|------|------|------|-------|---|

| PSRR            |      | @ 1 kHz                                                            | 40   |      |      | dB    |   |

| Load regulation |      | @ 2 mA                                                             |      | 5    | 20   | mV/mA |   |

| Load current    |      |                                                                    |      |      | 2    | mA    |   |

| Line regulation |      |                                                                    | -1   |      | 5    | mV/V  |   |

#### VDDA (1 µF External Capacitor on VDDA + 100 nF External Capacitor on CAP0/CAP1)

| Output voltage                 | VDDA | Unloaded with VREG = 1 V | 1.8  | 2.0  | 2.1  | V     | ٠ |

|--------------------------------|------|--------------------------|------|------|------|-------|---|

| PSRR                           |      | @ 1 kHz                  | 45   |      |      | dB    |   |

| Load regulation                |      | @ 1 mA                   |      | 100  | 140  | mV/mA |   |

| Load current                   |      |                          |      |      | 1    | mA    |   |

| Line regulation                |      |                          |      |      | 2    | mV/V  |   |

| VDDD (1 µF External Capacitor) |      |                          |      |      |      |       |   |

| Output voltage                 | VDDD |                          | 1.62 | 1.70 | 1.98 | V     | ٠ |

Table 2. ELECTRICAL CHARACTERISTICS (continued) (The typical parameters in Table 2 were measured at 20°C with a clean 3.3 V supply voltage (unless noted differently). Parameters marked as screened are tested on each chip. Other parameters are qualified for all process corners but not tested on every part.)

| Parameter                                         | Symbol | Test Conditions / Notes                                                             | Min  | Тур    | Max  | Unit  | Screened |

|---------------------------------------------------|--------|-------------------------------------------------------------------------------------|------|--------|------|-------|----------|

| VMIC                                              |        |                                                                                     |      |        |      |       |          |

| Output voltage                                    |        | VMIC = VREG                                                                         | 0.95 | 1.00   | 1.05 | V     | •        |

|                                                   |        | VMIC = VDDA                                                                         | 1.8  | 2.0    | 2.1  | V     | •        |

| Load Regulation                                   |        | VMIC = VREG                                                                         |      | 25     | 40   | mV/mA |          |

|                                                   |        | VMIC = VDDA                                                                         |      | 100    | 150  | mV/mA |          |

| POWER ON RESET                                    | •      | •                                                                                   | •    |        |      |       |          |

| POR Threshold                                     |        | POR Release<br>(VBAT going up)                                                      | 1.52 | 1.60   | 1.71 | V     | •        |

|                                                   |        | POR Activation<br>(VBAT going down)                                                 | 1.52 | 1.60   | 1.65 | V     | •        |

| Boot Time                                         |        | NRST to DMIC active using<br>LSAD boot method                                       |      | 16.3   |      | ms    | 2        |

|                                                   |        | NRST to DMIC active using<br>SPI EEPROM boot method<br>(Default custom application) |      | 90     | NO   | ms    |          |

|                                                   |        | NRST to DMIC active using<br>I2C EEPROM boot method<br>(Default custom application) |      | 135    |      | ms    |          |

| INPUT STAGE                                       |        |                                                                                     | 10Y  | cel.   | ~0   | •     |          |

| Sampling frequency                                | Fs     | Defined by ROM-based application. (Note 2)                                          | ERC  | 21.333 |      | kHz   |          |

| Analog input voltage                              | Vin    | No preamp gain on Al1<br>and Al3                                                    | Doff | 20     | 2    | Vpp   |          |

|                                                   | Vin    | 24 dB preamp gain by default<br>on MIC0 and MIC2                                    | 20   |        | 125  | mVpp  |          |

| Preamplifier gain tolerance                       |        | 1 kHz                                                                               | -2   |        | 2    | dB    |          |

| Input impedance                                   | Rin    | 0 dB preamplifier gain                                                              |      | 250    |      | kΩ    |          |

|                                                   | · Sin  | All other gain settings                                                             | 510  |        | 585  | kΩ    | •        |

| Input offset voltage                              | FER    | 0 dB preamp gain                                                                    |      |        | 7    | mV    |          |

| EVIC                                              | Prof   | All other gains                                                                     |      |        | 3    | mV    |          |

| Channel cross coupling                            | LP1-   | Any 2 channels                                                                      |      | -84    | -60  | dB    |          |

| Analog Filter cut-off frequency                   | RV     | LPF enabled (default)                                                               | 10   | 20     | 30   | kHz   |          |

|                                                   |        | LPF disabled                                                                        | 50   |        |      | kHz   |          |

| Analog Filter passband flatness                   |        |                                                                                     | -1   |        | 1    | dB    |          |

| Analog filter stopband attenuation                |        |                                                                                     | 60   |        |      | dB    |          |

| Digital Filter cut-off frequency                  |        |                                                                                     |      | Fs/2   |      | kHz   |          |

| Digital Filter cut-off stopband attenuation       |        |                                                                                     | 80   |        |      | dB    |          |

| Total Harmonic Distortion +<br>Noise (Peak value) | THDN   | 24 dB preamplifier gain<br>VBAT = 3.3 V                                             | -67  | -70    |      | dB    |          |

| Dynamic Range                                     | DR     | 24 dB preamplifier gain<br>VBAT = 3.3 V                                             | 81   | 82.5   |      | dB    |          |

| Equivalent Input Noise                            | EIN    | 24 dB preamplifier gain<br>VBAT = 3.3 V                                             |      | 3.7    |      | μV    |          |

2. Processed bandwidth limited to 8 kHz.

Table 2. ELECTRICAL CHARACTERISTICS

(The typical parameters in Table 2 were measured at 20°C with a clean

3.3 V supply voltage (unless noted differently). Parameters marked as screened are tested on each chip. Other parameters are qualified for all process corners but not tested on every part.)

| Parameter                                         | Symbol            | Test Conditions / Notes                         | Min                          | Тур   | Max            | Unit | Screened |

|---------------------------------------------------|-------------------|-------------------------------------------------|------------------------------|-------|----------------|------|----------|

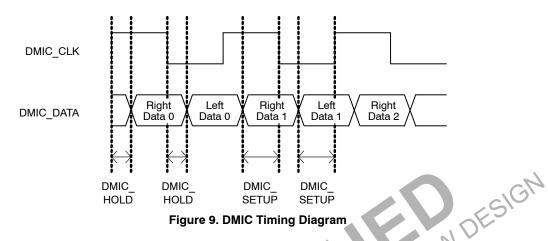

| DIGITAL MICROPHONE OUTPU                          | Т                 |                                                 |                              |       |                |      |          |

| DMIC input clock frequency                        |                   | With preset 0 selected on<br>CLOCK_SEL (Note 3) |                              | 2.048 |                | MHz  |          |

|                                                   |                   | With preset 3 selected on CLOCK_SEL (Note 3)    |                              | 2.4   |                | MHz  |          |

|                                                   |                   | With preset 4 selected on CLOCK_SEL (Note 3)    |                              | 2.8   |                | MHz  |          |

|                                                   |                   | With preset 5 selected on CLOCK_SEL (Note 3)    |                              | 3.072 |                | MHz  |          |

| Clock duty cycle                                  |                   | Any clock configuration                         | 40                           | 50    | 60             | %    |          |

| Input clock jitter                                |                   | Maximum allowed jitter on the DMIC_CLK          |                              |       | 10             | ns   | 1        |

| Clock to output transition time                   | DMIC_OUT          |                                                 | 10                           | 20    | 50             | ns   |          |

| ANALOG OUTPUT STAGE                               |                   |                                                 |                              |       | . 0            |      |          |

| Signal Range                                      | Vout              | One single ended DAC used                       | 0                            |       | 2              | Vpp  |          |

|                                                   |                   | Two DACs used as one differential output        | 0                            | RN    | 4              | Vpp  |          |

| Attenuator gain tolerance                         |                   |                                                 | -2                           | n.    | 2              | dB   |          |

| Output impedance                                  | Rout              | @ 12 dB output attenuation                      |                              | ns n  | 19             | kΩ   | •        |

|                                                   |                   | @ 0 dB output attenuation                       | R                            | SNI   | 3              | kΩ   |          |

| Channel cross coupling                            |                   | @1 kHz                                          | $\mathcal{V}'_{\mathcal{L}}$ | JL.   | -50            | dB   |          |

| Analog Filter cut-off frequency                   |                   | LPF Enabled (default)                           | 13.0                         |       | 13.5           | kHz  |          |

|                                                   |                   | LPF Disabled                                    | 25                           |       | 26             | kHz  |          |

| Analog Filter passband flatness                   |                   | RUNCFO                                          | -1                           |       | 1              | dB   |          |

| Analog filter stopband attenuation                |                   | > 60 kHz                                        | 90                           |       |                | dB   |          |

| Digital Filter cut-off frequency                  | P P               | or Jr.                                          |                              | Fs/2  |                | kHz  |          |

| Digital Filter cut-off stopband Cattenuation      | PLEE              | SEI                                             | 80                           |       |                | dB   |          |

| Total Harmonic Distortion +<br>Noise (Peak value) | THON              |                                                 | 63                           | 65    |                | dB   | •        |

| Dynamic Range                                     | DR                |                                                 | 78                           | 80    |                | dB   | •        |

| Noise Floor                                       |                   |                                                 |                              | 70    | 100            | μV   | •        |

| DIRECT DIGITAL OUTPUT (avai                       | ilable only throu | igh custom configuration)                       |                              |       |                |      |          |

| Supply voltage                                    | VBATRCVR          |                                                 | 1.8                          | 3.3   | 3.63           | V    |          |

| Signal Range                                      | Vout              | Differential Output @ 1 kHz                     | 0                            |       | 2*VBAT<br>RCVR | Vpp  |          |

|                                                   |                   | Single ended Output @ 1 kHz                     | 0                            |       | VBAT<br>RCVR   | Vpp  |          |

| Output Impedance                                  | Rout              | Load between<br>1 mA and 30 mA @ 0°C            |                              | 2.5   | 10             | Ω    |          |

| Maximum Current                                   |                   |                                                 |                              |       | 25             | mA   |          |

| Total Harmonic Distortion +<br>Noise (Peak value) | THDN              |                                                 | 64                           | 70    |                | dB   | •        |

3. Many other clock frequencies are available through custom configuration of the internal PLL and clocking subsystem. See later in this document and in the BelaSigna R262 Communications and Configuration Guide for more information on custom mode usage.

**Table 2. ELECTRICAL CHARACTERISTICS** (continued) (The typical parameters in Table 2 were measured at 20°C with a clean 3.3 V supply voltage (unless noted differently). Parameters marked as screened are tested on each chip. Other parameters are qualified for all process corners but not tested on every part.)

| Parameter                    | Symbol            | Test Conditions / Notes                                        | Min  | Тур     | Max      | Unit | Screened |

|------------------------------|-------------------|----------------------------------------------------------------|------|---------|----------|------|----------|

| DIRECT DIGITAL OUTPUT (ava   | ilable only throu | ugh custom configuration)                                      |      |         | <u> </u> |      |          |

| Dynamic Range                | DR                |                                                                | 80   | 86      |          | dB   | •        |

| Noise Floor                  |                   |                                                                |      | 50      | 75       | μV   | •        |

| LOW-SPEED A/D                |                   |                                                                |      |         |          |      | •        |

| Input voltage                | Vin               |                                                                | 0    |         | 2*VREG   | V    |          |

| Sampling frequency           |                   | For each LSAD channel                                          | 1.6  | MCLK/28 | 4.8      | kHz  |          |

| Input impedance              | Rin               |                                                                | 1    |         |          | MΩ   |          |

| Offset error                 |                   | Input at VREG                                                  | -10  |         | 10       | LSB  |          |

| Gain error                   |                   | Input to VSSA or 2*VREG                                        | -10  |         | 10       | LSB  |          |

| INL                          | INL               |                                                                | -4   |         | 4        | LSB  | 2        |

| DNL                          | DNL               |                                                                | -2   |         | 2        | LSB  |          |

| DIGITAL PADS (VDDO = 1.8 V)  |                   |                                                                |      |         |          |      |          |

| Voltage level for Low input  | VIL               |                                                                | -0.3 |         | 0.4      | V    |          |

| Voltage level for High input | VIH               |                                                                | 1.30 | 24      | 1.98     | V    |          |

| Pull-up resistance           |                   |                                                                | 63   | 114     | 162      | kΩ   |          |

| Pull-down resistance         |                   |                                                                | 87   | 153     | 205      | kΩ   |          |

| Rise and Fall Time           |                   | 20 pF load                                                     | 2    | 3       | 5        | ns   |          |

| DIGITAL PADS (VDDO = 3.3 V)  |                   |                                                                | ,R   | SUL     | -        |      |          |

| Voltage level for Low input  | VIL               |                                                                | -0.3 | DK      | 0.8      | V    | •        |

| Voltage level for High input | VIH               | ONIT Y                                                         | 1.8  |         | 3.6      | V    | •        |

| Pull-up resistance           |                   |                                                                | 34   | 46      | 74       | kΩ   | •        |

| Pull-down resistance         |                   | RUNICE                                                         | 29   | 56      | 86       | kΩ   | •        |

| Rise and Fall Time           |                   | 20 pF load                                                     | 1.0  | 1.5     | 2.0      | ns   |          |

| DIGITAL PADS (Common parar   | neters)           | SE TA                                                          |      |         |          |      |          |

| Drive Strength               | ELER              | CN                                                             |      | 12      |          | mA   |          |

| ESD Immunity                 | НВМ               | Human Body Model                                               | 2    |         |          | kV   |          |

| DE                           | MM                | Machine Model                                                  | 200  |         |          | V    |          |

| Latch-up Immunity            | 2Ei               | 25°C, V < GNDO, V > VDDO                                       | 150  |         |          | mA   |          |

| CLOCKING CIRCUITRY           |                   |                                                                |      |         |          |      |          |

| External clock frequency     | EXT_CLK           | With preset 6 selected on CLOCK_SEL (Note 3)                   |      | 26      |          | MHz  |          |

| Internal clock frequency     | INT_CLK           | With preset 7 selected on<br>CLOCK_SEL (Note 3)<br>Bypass Mode |      | 5.2     |          | MHz  |          |

|                              |                   | With preset 7 selected on<br>CLOCK_SEL (Note 3)<br>Active Mode |      | 48.2    |          | MHz  |          |

| Reference clock duty cycle   |                   |                                                                | 40   | 50      | 60       | %    |          |

| External Input clock jitter  |                   | Maximum allowed jitter on EXT_CLK                              |      |         | 10       | ns   |          |

| I <sup>2</sup> C INTERFACE   |                   |                                                                |      |         |          |      |          |

| Maximum speed                |                   |                                                                |      |         | 400      | kbps |          |

|                              |                   |                                                                |      |         |          |      |          |

3. Many other clock frequencies are available through custom configuration of the internal PLL and clocking subsystem. See later in this document and in the BelaSigna R262 Communications and Configuration Guide for more information on custom mode usage.

#### **Table 3. PIN CONNECTIONS**

|    | Pin Name           | Description                                                 | A/D/P | I/O              | Active | Pul |

|----|--------------------|-------------------------------------------------------------|-------|------------------|--------|-----|

| G1 | MICO               | First microphone input                                      | А     | I                |        |     |

| E1 | MIC2               | Second microphone input                                     | А     | I                |        |     |

| E3 | AI3/VMIC/LOUT0     | Direct audio input / microphone bias /<br>line-out preamp 0 | A     | I/O              |        |     |

| E7 | A_OUT1             | Audio output 1                                              | А     | 0                |        |     |

| G7 | CAP0               | Charge pump capacitor connection                            | А     | I/O              |        |     |

| F8 | CAP1               | Charge pump capacitor connection                            | А     | I/O              |        |     |

| A1 | DEBUG_RX           | RS232 debug port serial input                               | D     | I                | L      | U   |

| B2 | DEBUG_TX           | RS232 debug port serial output                              | D     | 0                | L      |     |

| F2 | RESERVED           | Reserved                                                    |       |                  |        |     |

| A3 | EXT_CLK            | External clock input                                        | D     | I                |        | U   |

| A7 | SPI_CLK/CLOCK_SEL  | SPI clock / Clock selection                                 | D/A   | O/I              | 45     |     |

| A9 | SPI_CS/BOOT_SEL    | SPI chip select / Booting method selection                  | D/A   | O/I              | 5      |     |

| B8 | SPI_SERO/CHAN_SEL  | SPI serial output / Channel selection                       | D/A   | 0/1              |        |     |

| C9 | SPI_SERI/ALPHA_SEL | SPI serial input / Mixing ratio selection                   | D/A   | <sup>©</sup> I/I |        | U/  |

| C7 | DMIC_OUT           | Digital microphone output                                   | D     | 0                |        |     |

| C3 | I2C_SDA            | I <sup>2</sup> C data                                       | D     | JO               | L      | U   |

| C1 | I2C_SCL            | I <sup>2</sup> C clock                                      | СD    | 00               | L      | U   |

| F6 | VBAT               | Power supply                                                | P     | I                |        |     |

| G9 | VBATRCVR           | Output driver power supply                                  | Р     | I                |        |     |

| G5 | VDDA               | Analog supply voltage                                       | Р     | 0                |        |     |

| B6 | VDDD               | Digital power supply                                        | Р     | 0                |        |     |

| B4 | VDDO               | Digital I/O power supply                                    | Р     | I                |        |     |

| G3 | VREG               | Analog supply voltage                                       | Р     | 0                |        |     |

| F4 | VSSA               | Analog ground                                               | Р     | I                |        |     |

| A5 | VSSD               | Digital ground                                              | Р     | I                |        |     |

|    | VSSBCVR            | Output driver ground                                        | Р     | I                |        |     |

O: Output

IO: Bi-directional

I/O & O/IL: Input or Output depending on the function being used

L: Active Low

H: Active High

U: Pulled up internally

D: Pulled down internally

#### **Application Diagrams**

#### Applications Information Recommended Circuit Design Guidelines

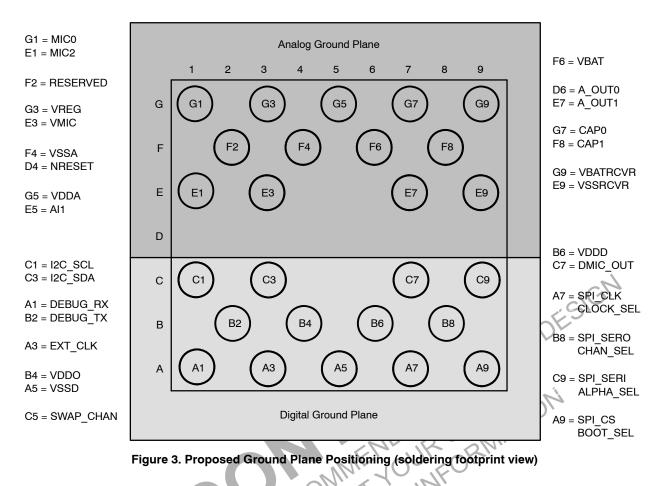

BelaSigna R262 is designed to allow both digital and analog processing in a single system. Due to the mixedsignal nature of this system, careful design consideration of the printed circuit board (PCB) layout is critical to maintain the high audio fidelity of BelaSigna R262. To avoid coupling noise into the audio signal path, keep the digital traces away from the analog traces. To avoid electrical feedback coupling, isolate the input traces from the output traces.

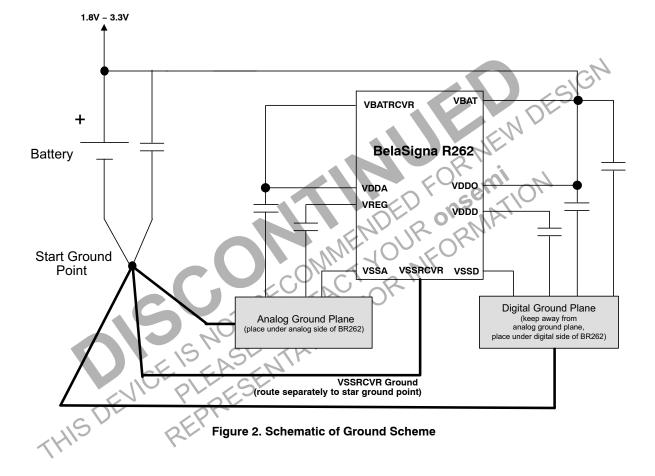

#### **Recommended Ground Design Strategy**

The ground plane should be partitioned into two parts: the analog ground plane (VSSA) and the digital ground plane (VSSD). These two planes should be connected together at a single point, known as the star point. The star point should be located close to the negative terminal of the power source, as illustrated in Figure 2.

All ground returns should be routed separately back to the appropriate ground plane, i.e. do not share a ground return.

Ensure that different ground and/or power planes do not overlap each other if located on different layers in the board.

The VSSD plane is used as the ground return for digital circuits and should be placed under digital circuits. The VSSA plane should be kept as noise–free as possible. It is used as the ground return for analog circuits and it should surround analog components and pins. It should not be connected to or placed under any noisy circuits such as RF chips, switching supplies or digital pads of BelaSigna R262 itself. Analog ground returns associated with the audio output stage should connect back to the star point on separate individual traces.

For details on which signals require special design consideration, see Table 4 and Table 5.

In some designs, space constraints may make separate ground planes impractical. In this case a star configuration strategy should be used. Each analog ground return should connect to the star point with separate traces.

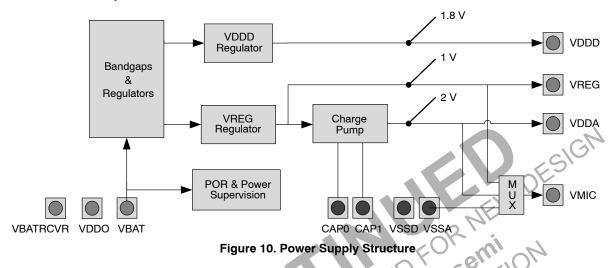

#### **Internal Power Supplies**

Power management circuitry in BelaSigna R262 generates separate digital (VDDD) and analog (VREG, VDDA) regulated supplies. Each supply requires an external decoupling capacitor, even if the supply is not used externally. Decoupling capacitors should be placed as close as possible to the power pads.

The digital I/O levels are defined by a separate power supply pin on BelaSigna R262 (VDDO). This pin must be externally connected by the application PCB, usually to VBAT.

Further details on these critical signals are provided in Table 4. Non-critical signals are outlined in Table 5. More information on the power supply architecture can be found in the Power Supply Unit section.

#### Table 4. CRITICAL SIGNALS

| Pin Name                                    | Description                                                   | Connection Guidelines                                                                                                                                                                                                                      |

|---------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT                                        | Power supply                                                  | Place 1 μF (min) decoupling capacitor close to pin<br>Connect negative terminal of capacitor to digital ground plane                                                                                                                       |

| VREG, VDDA                                  | Internal regulator for analog<br>blocks                       | Place separate 1 $\mu$ F decoupling capacitors close to each pin<br>Connect negative capacitor terminal to analog ground plane<br>Keep away from digital traces and output traces<br>VREG and VDDA may be used to generate microphone bias |

| VSSA                                        | Analog ground return                                          | Connect to analog ground plane                                                                                                                                                                                                             |

| VDDD                                        | Internal regulator for digital core                           | Place 1 µF decoupling capacitor close to pin<br>Connect negative terminal of capacitor to digital ground plane                                                                                                                             |

| VSSD                                        | Digital ground return                                         | Connect to digital ground plane                                                                                                                                                                                                            |

| VDDO                                        | Digital I/O power                                             | Place 1 μF decoupling capacitor close to pin<br>Connect negative terminal of capacitor to digital ground plane<br>Connect to VBAT, unless the pad ring must use different voltage levels                                                   |

| MIC0, MIC2,<br>Al1/LOUT1,<br>Al3/VMIC/LOUT0 | Audio inputs / Microphone bias                                | Keep traces as short as possible<br>Keep away from all digital traces and audio outputs<br>Avoid routing in parallel with other traces<br>Never connect Al3/VMIC/LOUT0 to ground                                                           |

| A_OUT0, A_OUT1                              | Audio outputs                                                 | Keep away from audio inputs<br>Differential traces should be of approximately the same length<br>Ideally, route lines parallel to each other                                                                                               |

| VSSRCVR                                     | Output stage ground return                                    | Connect to star ground point<br>Keep away from all analog audio inputs                                                                                                                                                                     |

| EXT_CLK                                     | External clock input                                          | Minimize trace length<br>Keep away from analog signals<br>If possible, surround with digital ground                                                                                                                                        |

| DMIC_OUT                                    | Digital Microphone Output                                     | Minimize trace length<br>Keep away from analog signals<br>If possible, surround with digital ground                                                                                                                                        |

| THISD                                       | EVICE IS NOT RU<br>EVICE IS NOT REPASE<br>PLEASE<br>REPRESENT | TATI                                                                                                                                                                                                                                       |

#### Table 5. NON-CRITICAL SIGNALS

| Pin Name                                             | Description                                                              | Connection Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAP0, CAP1                                           | Internal charge pump –<br>capacitor connection                           | Place 100 nF capacitor very close to pins                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I2C_SDA, I2C_SCL                                     | I <sup>2</sup> C port                                                    | Keep as short as possible. Place pull–up resistors (10 $k\Omega)$ to VDDO                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SWAP_CHAN                                            | Control GPIO                                                             | Not critical when used as GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLOCK SEL,<br>BOOT_SEL,<br>CHAN_SEL and<br>ALPHA_SEL | Low-speed A/D converters<br>(Multiplexed with SPI port)                  | Not critical when used as LSAD<br>Place resistive divider for hardware configuration of BelaSigna R262                                                                                                                                                                                                                                                                                                                                                                                     |

| SPI_CLK, SPI_CS,<br>SPI_SERO,<br>SPI_SERI            | Serial peripheral interface port<br>(Multiplexed with LSAD and<br>GPIOs) | Keep away from analog input lines when used as SPI signals                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NRESET                                               | Reset                                                                    | Not critical<br>Leave unconnected if unused                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DEBUG_RX,<br>DEBUG_TX                                | Debug Port                                                               | Not critical<br>If possible, connect to test points, otherwise connect DEBUG_RX to VDDO<br>and leave DEBUG_TX floating                                                                                                                                                                                                                                                                                                                                                                     |

| RESERVED                                             | Reserved pin                                                             | Leave unconnected or connect to VSSA if PCB routing constraints force it                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VBATRCVR                                             | Output driver power supply                                               | <ul> <li>If the output driver is being used:</li> <li>Place a separate 4.7 μF (min. 2.2 μF) decoupling capacitor close to pin</li> <li>Connect positive terminal of capacitor to VBAT &amp; VBATRCVR</li> <li>Connect negative terminal of capacitor to VSSRCVR</li> <li>If the analog outputs or the DMIC output are being used:</li> <li>Separate decoupling capacitor on VBATRCVR is not required</li> <li>Connect VBATRCVR to VDDA (which has its own decoupling capacitor)</li> </ul> |

#### Audio Inputs

The audio input traces should be as short as possible. The input impedance of each audio input pad (e.g., MICO, AI1, MIC2, AI3) is high (approximately 500  $k\Omega$  with preamplifiers enabled); therefore a 10 nF capacitor is sufficient to decouple the DC bias. This capacitor and the internal resistance form a first-order analog high pass filter whose cut-off frequency can be calculated by  $f_{3dB}$  (Hz) = 1/(R x C x  $2\pi$ ), which results in ~30 Hz for a 10 nF capacitor. This 10 nF capacitor value applies when the preamplifier is being used, in other words, when a non-unity gain is applied to the signals; for MIC0 and MIC2, the preamplifier is enabled by the ROM-based application. When the preamplifier is bypassed, the impedance is reduced; hence, the cut-off frequency of the resulting high-pass filter could be too high. In such a case, the use of a 30-40 nF serial capacitor is recommended. In cases where line-level analog inputs without DC bias are used, the capacitor may be omitted for transparent bass response. ON Semiconductor recommends the use of NPO/COG dielectric for SMT capacitors, as they have demonstrated better performance compared to other capacitors with X7R dielectric.

#### **Microphone Power Supply**

BelaSigna R262 provides a microphone power supply (VMIC) and ground (VSSA). In case VMIC cannot be used

because of PCB routing constraints, the power supplies VREG (1.0 V) or VDDA (2.0 V) can alternatively be used. Keep audio input traces strictly away from output traces. Audio outputs must be kept away from microphone inputs to avoid cross-coupling.

#### Audio Outputs

The audio output traces should be as short as possible. The trace length of the two signals should be approximately the same to provide matched impedances.

#### **Recommendation for Unused Pins**

Table 6 shows the connection details for each pin when they are not used.

#### Table 6. UNUSED PIN RECOMMENDATIONS

| Signal Name    | Connection Guidelines |

|----------------|-----------------------|

| A_OUT0         | Do not connect        |

| A_OUT1         | Do not connect        |

| AI3/VMIC/LOUT0 | Do not connect        |

| AI1/LOUT1      | Connect to VSSA       |

| DMIC_OUT       | Do not connect        |

| SWAP_CHAN      | Do not connect        |

| NRESET         | Do not connect        |

#### Architecture Detailed Information

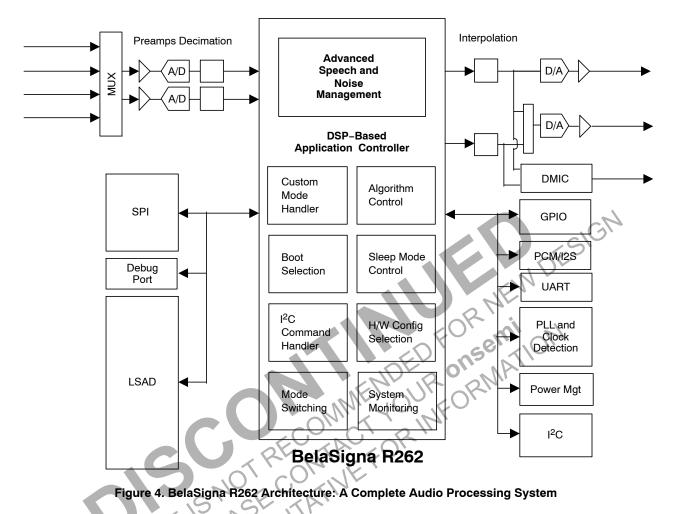

The architecture of BelaSigna R262 is shown in Figure 4.

## Algorithm Performance and Configuration

A detailed description of the functional blocks of the algorithm contained in BelaSigna R262, as well as performance metrics can be found in AND9109/D – Getting Started with BelaSigna R262.

For details on the configuration of the algorithm, refer to the BelaSigna R262 Communications and Configuration Guide.

#### Microphone Placement & Selection

The flexibility of the BelaSigna R262 noise reduction algorithm doesn't restrict microphone placements, but the default algorithm will operate optimally with omnidirectional microphones placed in the following configuration:

- The two microphones are facing the user's mouth

- The microphone centers are located within 10 to 25 mm from each other

As mentioned, other configurations that differ from the above guidelines are supported. For example, a 15 cm distance between the two microphones will not degrade the performance as long as the microphones are both facing the user's mouth. Alternatively, a configuration with one microphone at the front and one microphone at the back will not degrade the performance either, as long as the distance between the microphones is no more than 2 cm.

BelaSigna R262 does not require any acoustic microphone calibration procedure.

When selecting microphones to be used with BelaSigna R262, the following guidelines should be used:

- Two omni-directional microphones with similar characteristics should be used

- The microphone sensitivity should be approximately -42 dB (where 0 dB = 1 V/Pa, at 1 kHz)

- The microphones are two-terminal microphones

- The microphone power supply is either 1 V (recommended), or 2 V if it is to be provided by BelaSigna R262

- The dynamic range of BelaSigna R262 on its analog input channels is 2.0 V peak-to-peak, after amplification by the default gain value of 24 dB using BelaSigna R262's input preamplifiers

- When higher sensitivity microphones are used, the preamp gain should be adjusted to match the 2.0 Vpp input voltage swing on BelaSigna R262, but this will require special configuration of the ROM application, as described later. As an example, using microphones with a -22 dB sensitivity typically requires that the preamplifier gains be changed down to 12 dB.

- When MEMS microphone are to be used, a general increase of the algorithm performance can be expected due to the improved self noise of these microphones, compared to conventional electret microphones. For applications requiring microphone configurations differing significantly from the above recommendations, contact your local ON Semiconductor support representative.

#### **Operating Modes**

The default application stored in the ROM of BelaSigna R262 has four Operating Modes. The Operating Modes are summarized in Table 7.

| Operating<br>Mode | Switching                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active            | Active mode can be entered at boot time,<br>depending on the BOOT_SEL configuration and<br>when exiting Sleep mode. Active mode can also<br>be entered via an I <sup>2</sup> C command from another<br>mode.                                                                                                                                                                                         | In Active mode, the noise reduction algorithm is executed. While<br>in Active mode, BelaSigna R262 collects statistics on the input<br>signals that can be retrieved via I <sup>2</sup> C. These signal statistics can<br>be used for level calibration and other debugging. For more<br>information using Active mode for calibration and debugging see<br>the BelaSigna R262 Communications and Configuration Guide.                                                                |

| Bypass            | Bypass mode can be entered at boot time,<br>depending on the BOOT_SEL configuration. It<br>can also be entered via an I <sup>2</sup> C command from<br>another mode.                                                                                                                                                                                                                                 | In Bypass mode, no signal processing is done on the audio<br>inputs. The inputs are passed directly to the audio outputs. While<br>in Bypass mode, BelaSigna R262 collects statistics on the input<br>signals that can be retrieved via I <sup>2</sup> C. These signal statistics can<br>be used for level calibration and other debugging. For more<br>information using Bypass mode for calibration and debugging see<br>the BelaSigna R262 Communications and Configuration Guide. |

| Sleep             | Sleep mode can be entered via I <sup>2</sup> C commands.<br>When Sleep mode is entered via I <sup>2</sup> C, the chip will<br>exit Sleep mode only based on activity on the<br>I <sup>2</sup> C_SCL pin. Sleep mode will be automatically<br>entered if BelaSigna R262 detects that a required<br>external clock is no longer present. For more<br>information, see the Sleep Control section below. | In Sleep mode no signal processing is done. All analog blocks of<br>the chip are disabled and the digital core continues to run off an<br>internal low-speed oscillator, thereby allowing the external clock<br>to be disabled when the chip is asleep. This is BelaSigna R262's<br>lowest power operating mode.                                                                                                                                                                      |

| Stand-By          | Stand-By mode is an intermediate mode that is<br>only used when exiting sleep mode by an I <sup>2</sup> C<br>command.                                                                                                                                                                                                                                                                                | When I <sup>2</sup> C is used to exit Sleep mode, the application will transition to Stand–By mode, and will wait until the master I <sup>2</sup> C device issues a Switch_Mode command to enter another processing mode like Active or Bypass. If no such command is issued, BelaSigna R262 will return to Sleep mode and wait for a valid wake–up sequence.                                                                                                                         |

## Table 7. OPERATING MODES SUMMARY

# Boot Control, Hardware Configuration and Digital Control

At power–on–reset, BelaSigna R262 will normally execute the application stored in ROM. During the boot process, BelaSigna R262 will read voltage levels on four different pins, which will determine the algorithm and hardware configuration that will be executed. All the configuration options are described later in this section; the four pins are CLOCK\_SEL, BOOT\_SEL, CHAN\_SEL and ALPHA\_SEL.

The BOOT\_SEL pin controls the booting methods of BelaSigna R262. The signal on this pin is sampled by BelaSigna R262 during its booting process using a low-speed A/D converter (LSAD). Based on the actual voltage that the chip will read on this pin, it will automatically select a particular booting configuration, as described in Table 8.

| Preset | Voltage Level | Boot Method                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|---------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-2    | 0.65 – 1.00 V | External Boot Mode                                                                         | In this mode, BelaSigna R262 will not run the ROM based applica-<br>tion. It will start looking for an SPI EEPROM to bootload a custom<br>application from. If unsuccessful, it will look for an I <sup>2</sup> C EEPROM to<br>bootload a custom application; and lastly, if neither of the two previ-<br>ous operations to find an EEPROM are successful, it will enter a<br>wait loop, allowing a master I <sup>2</sup> C device to start downloading a cus-<br>tom application (e.g. a baseband controller). |

| 3      | 0.50 – 0.63 V | Active Mode<br>Talking distance selectable from<br>Near– to Far–Talk<br>(50 cm to 500 cm)  | The noise reduction algorithm is running and can be configured for talking distances between 50 cm (Near-Talk) and 5 m (Far-Talk)                                                                                                                                                                                                                                                                                                                                                                               |

| 4      | 0.36 – 0.49 V | Active Mode<br>Talking distance selectable from<br>Close– to Far–Talk<br>(5 cm to 500 cm)  | The noise reduction algorithm is running and can be configured for talking distances between 5 cm (Close-Talk) and 5 m (Far-Talk)                                                                                                                                                                                                                                                                                                                                                                               |

| 5      | 0.22 – 0.35 V | Active Mode<br>Talking distance selectable from<br>Close- to Near-Talk<br>(5 cm to 100 cm) | The noise reduction algorithm is running and can be configured for talking distances between 5 cm (Close-Talk) and 1 m (Near-Talk)                                                                                                                                                                                                                                                                                                                                                                              |

| 6      | 0.08 – 0.21 V | Bypass Diagnostic Mode<br>1 kHz sine wave play-out                                         | BelaSigna B262 outputs a pure tone on the two output channels.<br>This sine wave has a frequency of 1 kHz and an output level of<br>12 dB below full scale.                                                                                                                                                                                                                                                                                                                                                     |

| 7      | 0 – 0.07 V    | Bypass Diagnostic Mode<br>Full stereo passthrough                                          | BelaSigna R262 simply copies the input signals to the outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 8. | BOOT SELE | CTION OPTI | ONS (Note 4) |

|----------|-----------|------------|--------------|

|----------|-----------|------------|--------------|

4. For more details on the various operating modes of BelaSigna R262, please consult the BelaSigna R262 Communications and Configuration Guide.

#### Clocking, Channels & Algorithm Configuration

As mentioned in the Boot Control section, BelaSigna R262 is controlled by hardware configuration. Just like the BOOT\_SEL signal discussed earlier, the CLOCK SEL, CHAN SEL and ALPHA SEL pins are also sampled by BelaSigna R262 during its booting process

#### **Table 9. CLOCK CONFIGURATION OPTIONS**

using a low-speed A/D converters (LSAD). Based on the actual voltage that the chip reads on these pins, it will automatically select a particular clock, output stage, channels and algorithm configuration, as described in Tables 9, 10 and 11.

| Preset    | Voltage Level                                                                                                                                                                                                                                                                                                                                                            | Clock Frequency | Description                                                                               |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------|--|--|

| 0–2       | 0.65 – 1.00 V                                                                                                                                                                                                                                                                                                                                                            | 2.048 MHz       | A 2.048 MHz external clock is expected to be present on the EXT_CLK pin of BelaSigna R262 |  |  |

| 3         | 0.50 – 0.63 V                                                                                                                                                                                                                                                                                                                                                            | 2.4 MHz         | A 2.4 MHz external clock is expected to be present on the EXT_CLK pin of BelaSigna R262   |  |  |

| 4         | 0.36 – 0.49 V                                                                                                                                                                                                                                                                                                                                                            | 2.8 MHz         | A 2.8 MHz external clock is expected to be present on the EXT_CLK pin of BelaSigna R262   |  |  |

| 5         | 0.22 – 0.35 V                                                                                                                                                                                                                                                                                                                                                            | 3.072 MHz       | A 3.072 MHz external clock is expected to be present on the EXT_CLK pin of BelaSigna R262 |  |  |

| 6         | 0.08 – 0.21 V                                                                                                                                                                                                                                                                                                                                                            | 26 MHz          | A 26 MHz external clock is expected to be present on the EXT_CLK pin of BelaSigna R262    |  |  |

| 7         | 7       0 – 0.07 V       Internal Oscillator       BelaSigna R262 runs off its internal system clock. No clock signal must be present on the EXT_CLK pin. In this mode the sampling frequency can fluctuate slightly from one device to another; see the electrical characteristics for additional details. The performance of the algorithm itself is fully guaranteed. |                 |                                                                                           |  |  |

| Table 10. | Table 10. CHANNEL CONFIGURATION OPTIONS                                                                                                                                                                                                                                                                                                                                  |                 |                                                                                           |  |  |

# Table 10. CHANNEL CONFIGURATION OPTIONS

| Preset | Voltage Level | NR Outputs | Channel 0                                        | Channel 1                                        | Output Stage Configuration |

|--------|---------------|------------|--------------------------------------------------|--------------------------------------------------|----------------------------|

| 0–2    | 0.65 – 1.00 V | Single     | Start of Range<br>(as per BOOT_SEL)              | NACOP                                            | Mono,<br>Differential      |

| 3      | 0.50 – 0.63 V | Dual       | Start of Range<br>(as per BOOT_SEL)              | Mixed Output<br>(as per BOOT_SEL &<br>ALPHA_SEL) | Stereo,<br>Single Ended    |

| 4      | 0.36 – 0.49 V | Dual       | Mixed Output<br>(as per BOOT_SEL &<br>ALPHA_SEL) | End of Range<br>(as per BOOT_SEL)                | Stereo,<br>Single Ended    |

| 5      | 0.22 – 0.35 V | Single     | Mixed Output<br>(as per BOOT_SEL &<br>ALPHA_SEL) | N/A                                              | Mono,<br>Differential      |

| 6      | 0.08 - 0.21 V | Single     | Mixed Output<br>(as per BOOT_SEL &<br>ALPHA_SEL) | Algorithm Disabled                               | Stereo,<br>Single Ended    |

| 7      | 0 – 0.07 V    | Single     | Algorithm Disabled                               | Mixed Output<br>(as per BOOT_SEL &<br>ALPHA_SEL) | Stereo,<br>Single Ended    |

#### **Table 11. MIXER CONFIGURATION OPTIONS**

| Preset | Voltage Level | Mixing Ratio                         |  |

|--------|---------------|--------------------------------------|--|

| 0–2    | 0.65 – 1.00 V | 0% (Start of Range)                  |  |

| 3      | 0.50 – 0.63 V | 20% (Between Start and End of Range) |  |

| 4      | 0.36 – 0.49 V | 40% (Between Start and End of Range) |  |

| 5      | 0.22 – 0.35 V | 60% (Between Start and End of Range) |  |

| 6      | 0.08 – 0.21 V | 80% (Between Start and End of Range) |  |

| 7      | 0 – 0.07 V    | 100% (End of Range)                  |  |

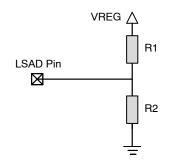

The use of a resistive divider as shown in Figure 5 allows the application to select the appropriate combination of clock, output stage and algorithm mode. The LSAD is using a voltage range between 0 and 1 V. The actual voltage levels that need to be guaranteed by the application circuitry are also mentioned in Figure 5. The figure proposes actual resistor values to reach the eight different presets.

| Preset | R1     | R2     | Voltage Range |

|--------|--------|--------|---------------|

| 0–2    | 10 kΩ  | -      | 0.65 – 1.00 V |

| 3      | 75 kΩ  | 100 kΩ | 0.50 – 0.63 V |

| 4      | 100 kΩ | 75 kΩ  | 0.36 – 0.49 V |

| 5      | 100 kΩ | 39 kΩ  | 0.22 – 0.35 V |

| 6      | 100 kΩ | 16 kΩ  | 0.08 – 0.21 V |

| 7      | -      | 10 kΩ  | 0 – 0.07 V    |

The configuration is only read by the chip at boot time. Consequently, if the voltage on any of the four LSAD inputs changes during operation, it will only have an impact at the next power cycle.

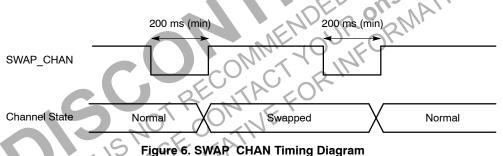

#### Channel Swapping

BelaSigna R262 has provisions to swap the two output channels by using an external GPIO pin (SWAP\_CHAN). The two output channels of BelaSigna R262 can be swapped whenever the digital signal on this pin transitions to low and stays low for at least 200 ms, as shown in Figure 6. The actual channel swapping can occur at any time during the 200 ms low period of the signal. This control mechanism has built-in button de-bouncing and will work with either a digital signal driven high or low by a host controller, or with a control signal provided by a mechanical button or switch.

#### **Sleep Control**

As described in Table 7, there are two methods to enter and exit from Sleep mode. Both of these methods are meant to be used independently, i.e. methods of putting the system into Sleep mode and waking it up from Sleep mode cannot be mixed in the same system design.

The first method for Sleep mode control is via the I<sup>2</sup>C interface. The *Switch\_Mode* command can be used directly to switch the system into and out of Sleep mode. If the *Switch\_Mode* command is used to put the chip into Sleep mode, only another *Switch\_Mode* command or a reset will take the system out of Sleep mode. When waking up by I<sup>2</sup>C commands, the following I<sup>2</sup>C operations have to be performed by the master I<sup>2</sup>C to ensure proper wake–up:

Send a NOP command to wake up the I<sup>2</sup>C interface. This command will not be interpreted by BelaSigna R262, so the master will have to deal with any I<sup>2</sup>C errors that result.

- 2. Send the *Get\_Status* command in a while–type loop, until a response from BelaSigna R262 is sent, and that confirms that the application is in Standby Mode.

- 3. Send a *Switch\_Mode* command to enter the desired mode (Active or Bypass).

When the *NOP* command is sent and the chip wakes up, the master has about one second to complete the above procedure before the chip goes back to Sleep mode. This mechanism was put in place to deal with  $I^{2}C$  bus traffic that would wake the chip up unintentionally (i.e. communications between the master and another slave on the  $I^{2}C$  bus).

The second mechanism for entering Sleep mode is considered a fail safe mechanism to maintain a graceful system shutdown in the event that the clock source suddenly disappears. In this circumstance, the chip will enter sleep mode to ensure proper shutdown. More information on this can be found in the System Monitoring section.

#### I<sup>2</sup>C Command Handler

The BelaSigna R262 ROM application contains an  $I^2C$ -based command and control interface, allowing many aspects of the chip's operation and hardware configuration to be controlled via  $I^2C$ . This  $I^2C$  interface is the recommended way to control the chip and to configure the application at run-time. The default  $I^2C$  address of BelaSigna R262 is 0x61. The  $I^2C$  interface protocol is fully supported by the SignaKlara Device Utility (SKDU) and other software tools provided by ON Semiconductor.

For more information on the  $I^2C$  interface, please refer to the  $I^2C$  interface section of this document, as well as the BelaSigna R262 Communications and Configuration Guide.

#### Reset

BelaSigna R262 can be forced to execute a power-on-reset by pulling the NRESET pin to ground for at least 100 ns. NRESET is not available on the 26-ball WLCSP package.

#### System Monitoring

The application software within BelaSigna R262 is equipped with a few blocks that monitor system sanity. A watchdog timer is used to ensure proper execution of the signal processing application. It is always active and is periodically acknowledged as a check that the application is still running. Once the watchdog times out, a hardware system reset will occur. System sanity is also monitored by the clock detection mechanism; the chip will automatically enter Sleep mode if it is in Active or Bypass mode and it detects that the external clock source (the signal on EXT\_CLK) is stopped. In this case, the system will only exit Sleep mode when it detects that the external clock source has been restored or a reset occurs.

The power supply blocks of the system also monitor for minimum supply voltages as part of the power supervision strategy, as described in the Power Management section.

#### **Analog Blocks**

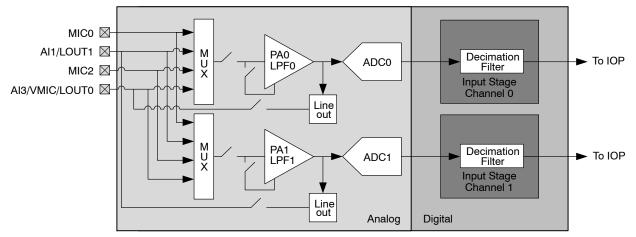

#### **Input Stages**

The BelaSigna R262 analog audio input stage is shown in Figure 7. The input stage is comprised of two individual channels. There are four configurable aspects of each channel - input multiplexing, preamplifier gain, filtering and line out. The input multiplexing allows one input to be selected from any of the four possible inputs and then routed to the input of the preamplifier. Each preamplifier can be configured for bypass or gain values of 12 to 30 dB in 3 dB steps. The filters can be configured as well; the DC removal high-pass filter can be bypassed, or set to a cut-off frequency of 5 Hz, 10 Hz or 20 Hz (default). The low-pass filter can be either enabled with a 20 kHz cut-off frequency (default), or bypassed. The lineout selection allows the preamplifier outputs to be routed back out via the auxiliary audio input pins. Note that the AI1/LOUT1 pin is not available on the 26-ball WLCSP package option.

Two analog-to-digital converters then convert the analog signals into the digital domain. The ADCs are running at a sampling rate of 21.3 kHz in Active mode and 16 kHz in Bypass mode. The sampling rate can potentially be changed using the  $I^2C$  interface. Changing the sampling rate in Active mode will cause the noise cancellation algorithm to stop operating properly, so this should not be done; however, the sampling rate in Bypass mode could be changed to other values. Contact your local technical support for more information.

Input signal amplitudes can also be adjusted in the digital domain; digital gain for both converted signals can be adjusted by using I<sup>2</sup>C commands.

The ROM-based application pre-configures all these parameters in the input stage such that the algorithm operates properly. These parameters can be changed using the  $I^2C$  interface, but careful design consideration should be taken when doing so, as this could alter the performance of the algorithm.

The AI3 pin is multiplexed with the microphone power supply (VMIC). The default mode for the microphone bias is to be used as a 2 V power supply. Consequently, any application that plans to use the AI3 input pin or the LOUT0 functionality has to change the VMIC setting to high-impedance mode, such as the pin can be properly used as an analog input or a line-out.

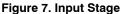

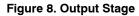

#### Output Stage

At all times, the application will produce two output channels. The content of each channel is determined by the hardware configuration.